DRV8886 ZHCSFZ1A – JANUARY 2017 – REVISED JULY 2018

# DRV8886 集成电流检测功能的 2A 步进电机驱动器

#### 1 特性

- 脉宽调制 (PWM) 微步进电机驱动器

- 最高 1/16 微步进

- 非循环和标准 ½ 步进模式

- 集成电流检测功能

- 无需感测电阻

- ±6.25% 满量程电流精度

- 慢速衰减和混合衰减选项

- 8V 至 37V 工作电源电压范围

- 低 R<sub>DS(ON)</sub>: 550mΩ HS + LS (在 24V 和 25℃ 条件下)

- 高电流容量

- 每条桥臂的峰值电流为 3A

- 每条桥臂的满量程电流为 2A

- 每条桥臂的均方根 (rms) 电流为 1.4A

- 固定关断时间脉宽调制 (PWM) 电流调节

- 简单的 STEP/DIR 接口

- 低电流休眠模式 (20μA)

- 小型封装尺寸

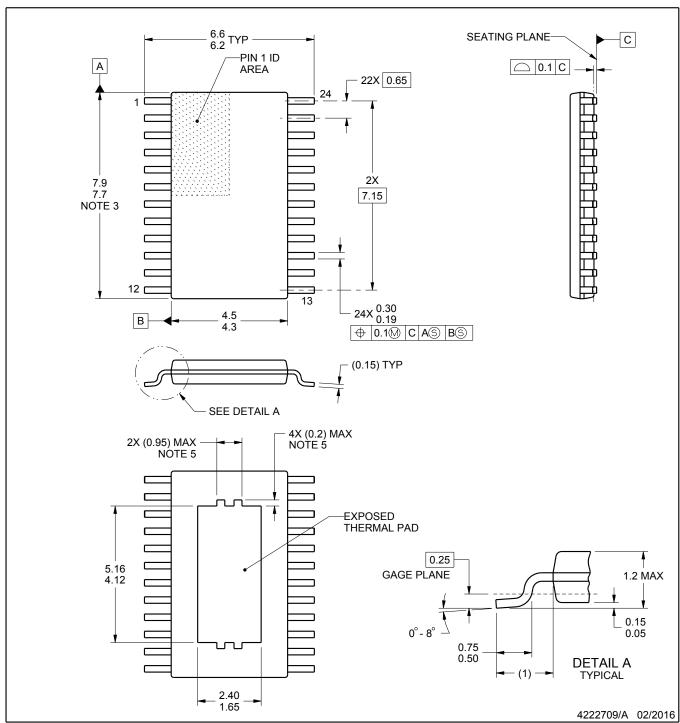

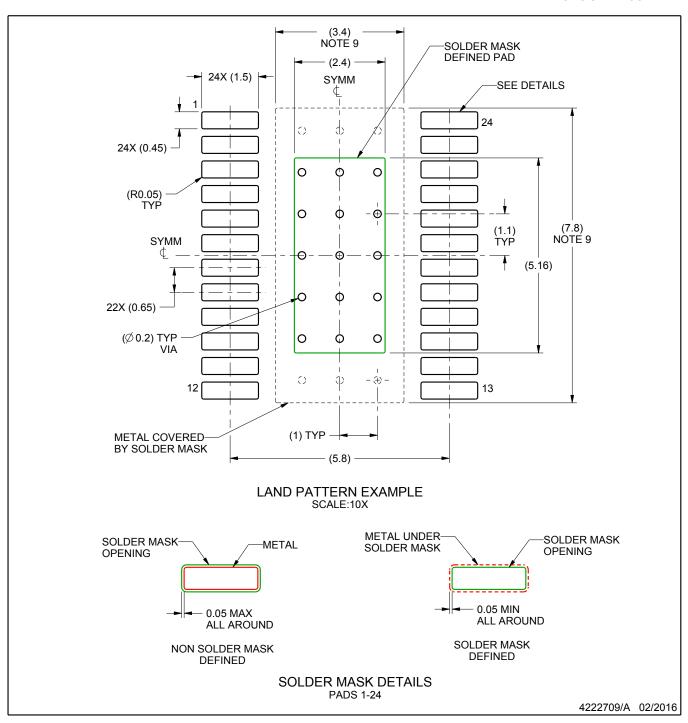

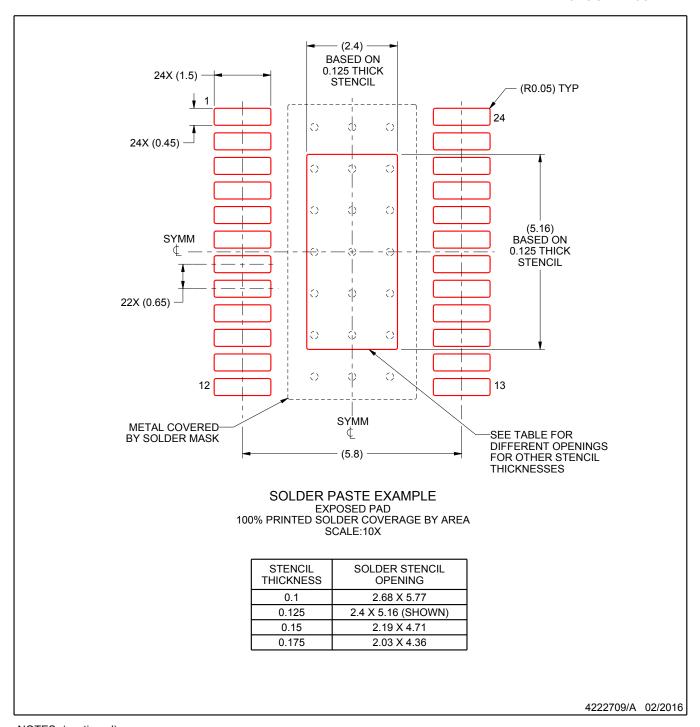

- 24 引脚散热薄型小外形尺寸 (HTSSOP)

PowerPAD™封装

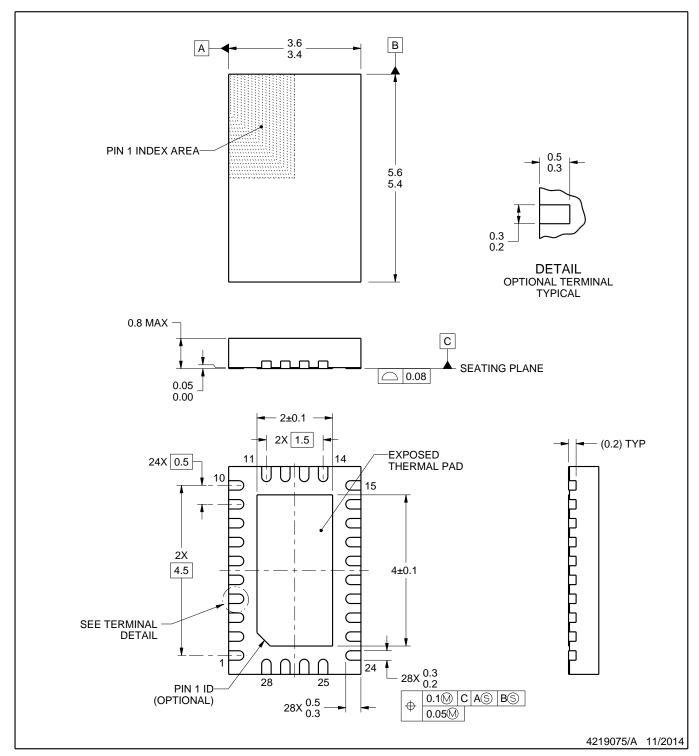

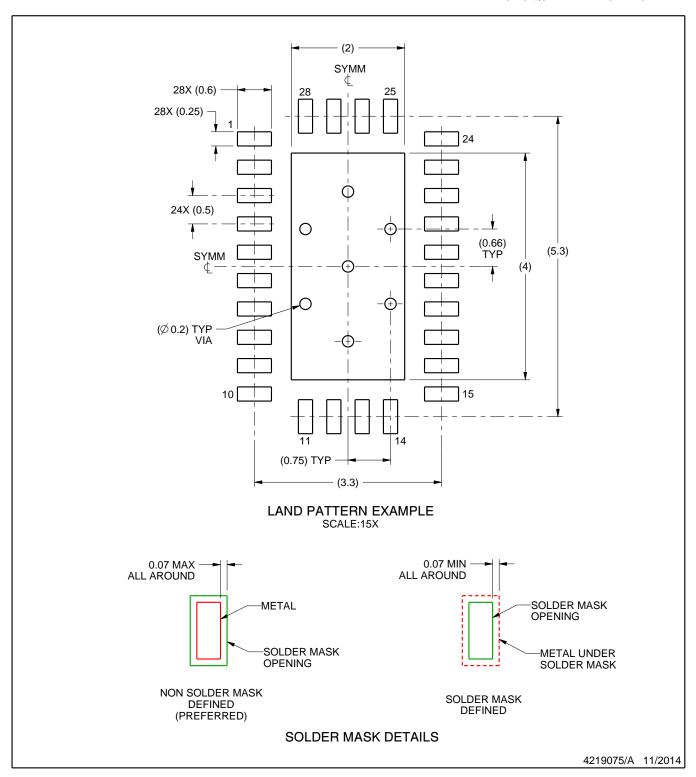

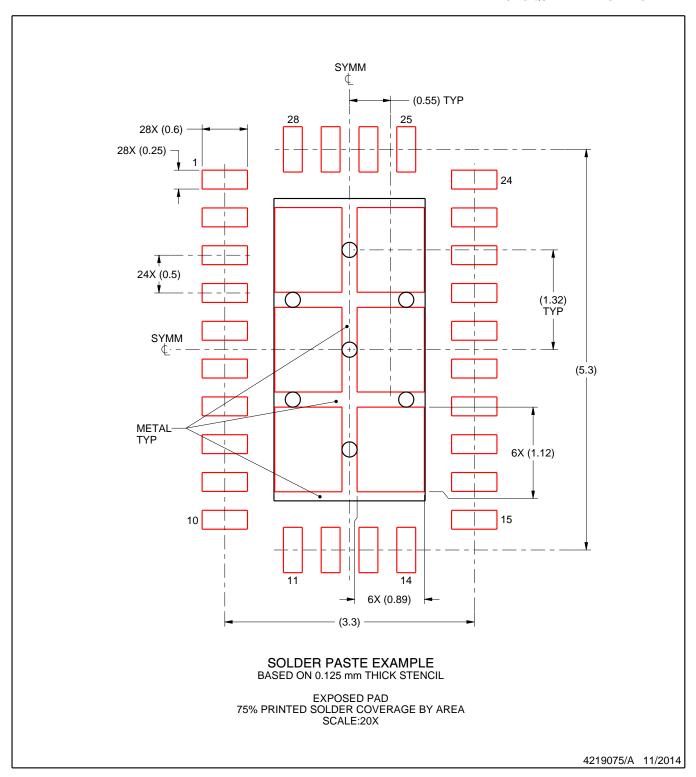

- 28 WQFN 封装

- 保护 特性

- VM 欠压闭锁 (UVLO)

- 电荷泵欠压 (CPUV)

- 过流保护 (OCP)

- 热关断 (TSD)

- 故障条件指示引脚 (nFAULT)

#### 2 应用

- 双极步进电机

- 多功能打印机和扫描仪

- 激光東打印机

- 3D 打印机

- 自动取款机和验钞机

- 视频安保摄像机

- 办公自动化设备

- 工厂自动化和机器人

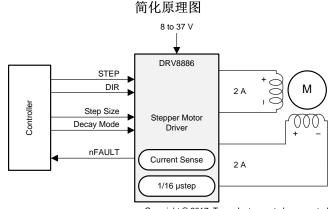

#### 3 说明

DRV8886 是一款适用于工业和消费类终端设备的 步进电机驱动器。该器件与两个 N 沟道功率金属氧化物半导体场效应晶体管 (MOSFET) H 桥驱动器、一个微步进分度器以及集成电流检测功能完全集成。DRV8886能够驱动高达 2A 的满量程电流或 1.4A rms 输出电流(电压为 24V 且 T<sub>A</sub> = 25°C,取决于印刷电路板(PCB)设计)。

DRV8886 采用内部电流检测架构,无需使用两个外部功率感测电阻,从而缩小 PCB 面积并削减系统成本。 DRV8886 使用内部固定关断时间 PWM 电流调节方案,可在慢速和混合衰减选项之间进行调节。

简易 STEP/DIR 接口允许外部控制器管理步进电机的方向和步进速率。该器件可以配置为不同步进模式,范围涵盖整步至 1/16 微步。凭借专用 nSLEEP 引脚,该器件可提供一种低功耗休眠模式,从而实现超低静态待机电流。

该器件的保护功能包括:电源欠压、电荷泵故障、过流、短路以及过热保护。故障状态通过 nFAULT 引脚指示。

#### 器件信息(1)

| 器件型号     | 封装                       | 封装尺寸 (标称值)     |  |

|----------|--------------------------|----------------|--|

| DD\/0006 | HTSSOP (24)              |                |  |

| DRV8886  | WQFN <sup>(2)</sup> (28) | 5.50mm × 3.5mm |  |

- (1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

- (2) 仅供预览。

Copyright © 2017, Texas Instruments Incorporated

# 目录

| 1 | 特性                                   |    | 7.4 Device Functional Modes    | 27 |

|---|--------------------------------------|----|--------------------------------|----|

| 2 | 应用 1                                 | 8  | Application and Implementation | 28 |

| 3 | 说明 1                                 |    | 8.1 Application Information    | 28 |

| 4 | 修订历史记录 2                             |    | 8.2 Typical Application        | 28 |

| 5 | Pin Configuration and Functions 3    | 9  | Power Supply Recommendations   | 31 |

| 6 | Specifications4                      |    | 9.1 Bulk Capacitance           | 31 |

| • | 6.1 Absolute Maximum Ratings 4       | 10 | Layout                         | 32 |

|   | 6.2 ESD Ratings                      |    | 10.1 Layout Guidelines         | 32 |

|   | 6.3 Recommended Operating Conditions |    | 10.2 Layout Example            | 32 |

|   | 6.4 Thermal Information              | 11 | 器件和文档支持                        | 33 |

|   | 6.5 Electrical Characteristics       |    | 11.1 文档支持                      | 33 |

|   | 6.6 Indexer Timing Requirements8     |    | 11.2 接收文档更新通知                  |    |

|   | 6.7 Typical Characteristics9         |    | 11.3 社区资源                      |    |

| 7 | Detailed Description 11              |    | 11.4 商标                        |    |

|   | 7.1 Overview 11                      |    | 11.5 静电放电警告                    |    |

|   | 7.2 Functional Block Diagram 12      |    | 11.6 术语表                       |    |

|   | 7.3 Feature Description              | 12 | 机械、封装和可订购信息                    | 33 |

|   |                                      |    |                                |    |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

# Changes from Original (January 2017) to Revision A Page • 己添加 WQFN 封装选项 1 • 已更改 the units of the High-Side and Low-Side R<sub>DS(ON)</sub> axis labels from mΩ to Ω in the high-side and low-side R<sub>DS(ON)</sub> over VM and over temperature graphs 9

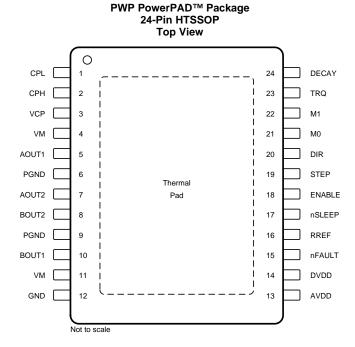

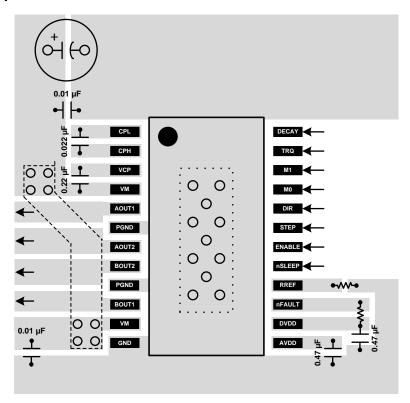

# 5 Pin Configuration and Functions

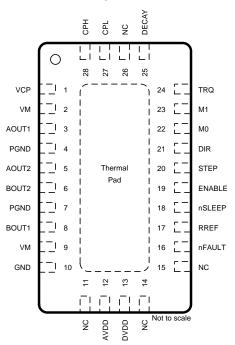

#### RHR Package 28-Pin WQFN With Exposed Thermal Pad Top View

#### **Pin Functions**

|        | PIN                  |    |         |                                                                                                                            |

|--------|----------------------|----|---------|----------------------------------------------------------------------------------------------------------------------------|

| NAME   | NAME NO. HTSSOP WQFN |    | TYPE(1) | DESCRIPTION                                                                                                                |

| NAME   |                      |    |         |                                                                                                                            |

| AOUT1  | 5                    | 3  | 0       | Winding A output. Connect to stepper motor winding.                                                                        |

| AOUT2  | 7                    | 5  | )       | winding A dulpat. Connect to stepper motor winding.                                                                        |

| AVDD   | 13                   | 12 | PWR     | Internal regulator. Bypass to GND with a X5R or X7R, 0.47-μF, 6.3-V ceramic capacitor.                                     |

| BOUT1  | 10                   | 8  | 0       | Winding B output. Connect to stepper motor winding.                                                                        |

| BOUT2  | 8                    | 6  | O       | winding B output. Connect to stepper motor winding.                                                                        |

| CPH    | 2                    | 28 | DWD     | Charge nump quitabing node Connect a VED as VZD 0.000 u.E. VM rated assemia connector from CDII to CDI                     |

| CPL    | 1                    | 27 | PWR     | Charge pump switching node. Connect a X5R or X7R, 0.022-µF, VM-rated ceramic capacitor from CPH to CPL.                    |

| DECAY  | 24                   | 25 | 1       | Decay-mode setting. Sets the decay mode (see the <i>Decay Modes</i> section). Decay mode can be adjusted during operation. |

| DIR    | 20                   | 21 |         | Direction input. Logic level sets the direction of stepping; internal pulldown resistor.                                   |

| DVDD   | 14                   | 13 | PWR     | Internal regulator. Bypass to GND with a X5R or X7R, 0.47-μF, 6.3-V ceramic capacitor.                                     |

| ENABLE | 18                   | 19 |         | Enable driver input. Logic high to enable device outputs; logic low to disable; internal pulldown resistor.                |

| GND    | 12                   | 10 | PWR     | Device ground. Connect to system ground.                                                                                   |

| MO     | 21                   | 22 | -       | Microstopping mode getting. Cate the step mode, tri level pine, acts the step mode, internal pulldown register.            |

| M1     | 22                   | 23 | ı       | Microstepping mode-setting. Sets the step mode; tri-level pins; sets the step mode; internal pulldown resistor.            |

|        |                      | 11 |         |                                                                                                                            |

| NO     |                      | 14 |         | No separat No internal connection                                                                                          |

| NC     |                      | 15 | _       | No connect. No internal connection                                                                                         |

|        |                      | 26 |         |                                                                                                                            |

| DCND   | 6                    | 4  | DWD     | Device around Connect to quoteen around                                                                                    |

| PGND   | 9                    | 7  | PWR     | Power ground. Connect to system ground.                                                                                    |

| RREF   | 16                   | 17 | I       | Current-limit analog input. Connect a resistor to ground to set full-scale regulation current.                             |

#### (1) I = input, O = output, PWR = power, OD = open-drain

#### Pin Functions (continued)

|               | PIN    |      |         |                                                                                                                     |

|---------------|--------|------|---------|---------------------------------------------------------------------------------------------------------------------|

| NAME          | NC     | ).   | TYPE(1) | DESCRIPTION                                                                                                         |

| INAIVIE       | HTSSOP | WQFN |         |                                                                                                                     |

| STEP          | 19     | 20   | I       | Step input. A rising edge causes the indexer to advance one step; internal pulldown resistor.                       |

| TRQ           | 23     | 24   | I       | Current-scaling control. Scales the output current; tri-level pin.                                                  |

| VCP           | 3      | 1    | PWR     | Charge pump output. Connect a X5R or X7R, 0.22-μF, 16-V ceramic capacitor to VM.                                    |

| \/ <b>\</b> / | 4      | 2    | PWR     | Power supply. Connect to motor supply voltage and bypass to GND with two 0.01-μF ceramic capacitors (one for        |

| VM            | 11     | 9    | PWK     | each pin) plus a bulk capacitor rated for VM.                                                                       |

| nFAULT        | 15     | 16   | OD      | Fault indication. Pulled logic low with fault condition; open-drain output requires an external pullup resistor.    |

| nSLEEP        | 17     | 18   | I       | Sleep mode input. Logic high to enable device; logic low to enter low-power sleep mode; internal pulldown resistor. |

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                                                             | MIN  | MAX      | UNIT |

|-----------------------------------------------------------------------------|------|----------|------|

| Power supply voltage (VM)                                                   | -0.3 | 40       | V    |

| Power supply voltage ramp rate (VM)                                         | 0    | 2        | V/µs |

| Charge pump voltage (VCP, CPH)                                              | -0.3 | VM + 7   | V    |

| Charge pump negative switching pin (CPL)                                    | -0.3 | VM       | V    |

| Internal regulator voltage (DVDD)                                           | -0.3 | 3.8      | V    |

| Internal regulator current output (DVDD)                                    | 0    | 1        | mA   |

| Internal regulator voltage (AVDD)                                           | -0.3 | 5.7      | V    |

| Control pin voltage (STEP, DIR, ENABLE, nFAULT, M0, M1, DECAY, TRQ, nSLEEP) | -0.3 | 5.7      | V    |

| Open drain output current (nFAULT)                                          | 0    | 10       | mA   |

| Current limit input pin voltage (RREF)                                      | -0.3 | 6.0      | V    |

| Continuous phase node pin voltage (AOUT1, AOUT2, BOUT1, BOUT2)              | -1.0 | VM + 1.0 | V    |

| Transient 100 ns phase node pin voltage (AOUT1, AOUT2, BOUT1, BOUT2)        | -3.0 | VM + 3.0 | V    |

| Peak drive current (AOUT1, AOUT2, BOUT1, BOUT2)                             | 0    | 3        | А    |

| Operating junction temperature, T <sub>J</sub>                              | -40  | 150      | °C   |

| Storage temperature, T <sub>stg</sub>                                       | -65  | 150      | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                              |                                                                     |                                                                   | VALUE | UNIT |

|------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------|-------|------|

| V                            |                                                                     | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 | \/   |

| <sup>V</sup> (ESD) discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500                                                              | V     |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                                               | MIN | MAX                | UNIT |

|-------------------|---------------------------------------------------------------|-----|--------------------|------|

| $V_{VM}$          | Power supply voltage (VM)                                     | 8   | 37                 | V    |

| VI                | Input voltage (DECAY, DIR, ENABLE, M0, M1, nSLEEP, STEP, TRQ) | 0   | 5.3                | V    |

| $f_{\sf PWM}$     | Applied STEP signal (STEP)                                    | 0   | 100 <sup>(1)</sup> | kHz  |

| I <sub>DVDD</sub> | External load current (DVDD)                                  | 0   | 1 <sup>(2)</sup>   | mA   |

| I <sub>FS</sub>   | Motor full-scale current (xOUTx)                              | 0   | 2 <sup>(2)</sup>   | Α    |

| I <sub>rms</sub>  | Motor RMS current (xOUTx)                                     | 0   | 1.4 <sup>(2)</sup> | Α    |

| T <sub>A</sub>    | Operating ambient temperature                                 | -40 | 125                | °C   |

<sup>(1)</sup> STEP input can operate up to 500 kHz, but system bandwidth is limited by the motor load(2) Power dissipation and thermal limits must be observed

#### 6.4 Thermal Information

|                      |                                              | DR           | /8886      |      |

|----------------------|----------------------------------------------|--------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | RHR (WQFN) | UNIT |

|                      |                                              | 24 PINS      | 28 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 33.8         | 33.2       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 18.0         | 23.1       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 7.7          | 12.2       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.2          | 0.3        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 7.8          | 12.0       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 1.3          | 3.3        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 6.5 Electrical Characteristics

at  $T_A = -40$  to 125°C,  $V_{VM} = 8$  to 37 V (unless otherwise noted)

|                                | PARAMETER                          | TEST CONDITIONS                                        | MIN      | TYP      | MAX   | UNIT |

|--------------------------------|------------------------------------|--------------------------------------------------------|----------|----------|-------|------|

| POWER                          | SUPPLIES (VM, DVDD, AVDD)          |                                                        |          |          |       |      |

| VVM                            | VM operating voltage               |                                                        | 8        |          | 37    | V    |

| $I_{VM}$                       | VM operating supply current        | ENABLE = 1, nSLEEP = 1, No motor load                  |          | 5        | 8     | mA   |

|                                |                                    | nSLEEP = 0; T <sub>A</sub> = 25°C                      |          |          | 20    |      |

| $I_{VMQ}$                      | VM sleep mode supply current       | nSLEEP = 0; T <sub>A</sub> = 125°C <sup>(1)</sup>      |          |          | 40    | μΑ   |

| t <sub>SLEEP</sub>             | Sleep time                         | nSLEEP = 0 to sleep-mode                               |          | 50       | 200   | μS   |

| t <sub>WAKE</sub>              | Wake-up time                       | nSLEEP = 1 to output transition                        |          | 0.85     | 1.5   | ms   |

| t <sub>ON</sub>                | Turn-on time                       | VM > UVLO to output transition                         |          | 0.85     | 1.5   | ms   |

| $V_{DVDD}$                     | Internal regulator voltage         | 0- to 1-mA external load                               | 2.9      | 3.3      | 3.6   | V    |

| $V_{AVDD}$                     | Internal regulator voltage         | No external load                                       | 4.5      | 5        | 5.5   | V    |

|                                | PUMP (VCP, CPH, CPL)               |                                                        |          |          | ·     |      |

| $V_{VCP}$                      | VCP operating voltage              |                                                        |          | VM + 5.5 |       | V    |

| LOGIC-L                        | EVEL INPUTS (STEP, DIR, ENABL      | E, nSLEEP, M1)                                         |          |          |       |      |

| V <sub>IL</sub>                | Input logic-low voltage            |                                                        | 0        |          | 0.8   | V    |

| V <sub>IH</sub>                | Input logic-high voltage           |                                                        | 1.6      |          | 5.3   | V    |

| V <sub>HYS</sub>               | Input logic hysteresis             |                                                        |          | 200      |       | mV   |

| I <sub>IL</sub>                | Input logic-low current            | VIN = 0 V                                              | -1       |          | 1     | μΑ   |

| I <sub>IH</sub>                | Input logic-high current           | VIN = 5 V                                              |          |          | 100   | μΑ   |

| R <sub>PD</sub>                | Pulldown resistance                | To GND                                                 | 100      |          |       | kΩ   |

| t <sub>PD</sub> <sup>(1)</sup> | Propagation delay                  | STEP to current change                                 |          |          | 1.2   | μS   |

|                                | EL INPUT (M0, TRQ)                 |                                                        |          |          |       |      |

| V <sub>IL</sub>                | Tri-level input logic low voltage  |                                                        | 0        |          | 0.65  | V    |

| V <sub>IZ</sub>                | Tri-level input Hi-Z voltage       |                                                        | 0.95     | 1.1      | 1.25  | V    |

| V <sub>IH</sub>                | Tri-level input logic high voltage |                                                        | 1.5      |          | 5.3   | V    |

| I <sub>IL</sub>                | Tri-level input logic low current  | VIN = 0 V                                              | -90      |          |       | μΑ   |

| I <sub>IH</sub>                | Tri-level input logic high current | VIN = 5 V                                              |          |          | 155   | μА   |

| R <sub>PD</sub>                | Tri-level pulldown resistance      | VIN = Hi-Z, to GND                                     |          | 65       |       | kΩ   |

| R <sub>PU</sub>                | Tri-level pullup resistance        | VIN = Hi-Z, to DVDD                                    |          | 130      |       | kΩ   |

| QUAD-LI                        | EVEL INPUT (DECAY)                 |                                                        |          |          |       |      |

| V <sub>I1</sub>                | Quad-level input voltage 1         | Can set with 1% 5 kΩ to GND                            | 0        |          | 0.14  | V    |

| V <sub>I2</sub>                | Quad-level input voltage 2         | Can set with 1% 15 kΩ to GND                           | 0.24     |          | 0.46  | V    |

| V <sub>I3</sub>                | Quad-level input voltage 3         | Can set with 1% 44.2 kΩ to GND                         |          |          | 1.24  | V    |

| V <sub>I4</sub>                | Quad-level input voltage 4         | Can set with 1% 133 kΩ to GND                          | 2.12 5.3 |          | 5.3   | V    |

| Io                             | Output current                     | To GND                                                 | 17       | 22       | 27.25 | μА   |

|                                | OL OUTPUTS (nFAULT)                |                                                        |          |          | l.    |      |

| V <sub>OL</sub>                | Output logic-low voltage           | $I_O = 1 \text{ mA}, R_{PULLUP} = 4.7 \text{ k}\Omega$ |          |          | 0.5   | V    |

| I <sub>OH</sub>                | Output logic-high leakage          | $V_O = 5 \text{ V}, R_{PULLUP} = 4.7 \text{ k}\Omega$  | -1       |          | 1     | μА   |

<sup>(1)</sup> Specified by design and characterization data

# **Electrical Characteristics (continued)**

at  $T_A$  = -40 to 125°C,  $V_{VM}$  = 8 to 37 V (unless otherwise noted)

|                               | PARAMETER                         | TEST CONDITIONS                                                               | MIN    | TYP    | MAX   | UNIT |

|-------------------------------|-----------------------------------|-------------------------------------------------------------------------------|--------|--------|-------|------|

| MOTOR DR                      | RIVER OUTPUTS (AOUT1, AOUT        | r2, BOUT1, BOUT2)                                                             |        |        | •     |      |

| R <sub>DS(ON)</sub>           | High-side FET on resistance       | VM = 24 V, I = 1.4 A, T <sub>A</sub> = 25°C                                   |        | 290    | 346   | mΩ   |

| R <sub>DS(ON)</sub>           | Low-side FET on resistance        | VM = 24 V, I = 1.4 A, T <sub>A</sub> = 25°C                                   |        | 260    | 320   | mΩ   |

| t <sub>RISE</sub> (1)         | Output rise time                  |                                                                               |        | 100    |       | ns   |

| t <sub>FALL</sub> (1)         | Output fall time                  |                                                                               |        | 100    |       | ns   |

| t <sub>DEAD</sub> (1)         | Output dead time                  |                                                                               |        | 200    |       | ns   |

| V <sub>d</sub> <sup>(1)</sup> | Body diode forward voltage        | I <sub>OUT</sub> = 0.5 A                                                      |        | 0.7    | 1     | V    |

| PWM CURF                      | RENT CONTROL (RREF)               |                                                                               |        |        | *     |      |

| A <sub>RREF</sub>             | RREF transimpedance gain          |                                                                               | 28.1   | 30     | 31.9  | kAΩ  |

| V <sub>RREF</sub>             | RREF voltage                      | RREF = 18 to 132 k $\Omega$                                                   | 1.18   | 1.232  | 1.28  | V    |

| t <sub>OFF</sub>              | PWM off-time                      |                                                                               |        | 20     |       | μS   |

| C <sub>RREF</sub>             | Equivalent capacitance on RREF    |                                                                               |        |        | 10    | pF   |

| t <sub>BLANK</sub>            | PWM blanking time                 | I <sub>RREF</sub> = 2.0 A, 63% to 100% current setting                        |        | 1.5    |       |      |

|                               |                                   | I <sub>RREF</sub> = 2.0 A, 0% to 63% current setting                          |        | 1      |       | μs   |

|                               |                                   | I <sub>RREF</sub> = 1.5 A, 10% to 20% current setting, 1% reference resistor  | -15%   |        | 15%   |      |

| $\Delta I_{TRIP}$             | Current trip accuracy             | I <sub>RREF</sub> = 1.5 A, 20% to 63% current setting, 1% reference resistor  | -10%   |        | 10%   |      |

|                               |                                   | I <sub>RREF</sub> = 1.5 A, 71% to 100% current setting, 1% reference resistor | -6.25% |        | 6.25% |      |

| PROTECTION                    | ON CIRCUITS                       |                                                                               |        |        |       |      |

|                               | V/M 1 D // O                      | VM falling, UVLO report                                                       | 7      |        | 7.8   | .,   |

| $V_{UVLO}$                    | VM UVLO                           | VM rising, UVLO recovery                                                      | 7.2    |        | 8     | V    |

| V <sub>UVLO,HYS</sub>         | Undervoltage hysteresis           | Rising to falling threshold                                                   |        | 200    |       | mV   |

| V <sub>CPUV</sub>             | Charge pump undervoltage          | VCP falling; CPUV report                                                      |        | VM + 2 |       | V    |

| ОСР                           | Overcurrent protection trip level | Current through any FET                                                       | 3      |        |       | Α    |

| t <sub>OCP</sub> (1)          | Overcurrent deglitch time         |                                                                               | 1.3    | 1.9    | 2.8   | μS   |

| t <sub>RETRY</sub>            | Overcurrent retry time            |                                                                               | 1      |        | 1.6   | ms   |

| T <sub>TSD</sub> (1)          | Thermal shutdown temperature      | Die temperature T <sub>J</sub>                                                | 150    |        |       | °C   |

| T <sub>HYS</sub> (1)          | Thermal shutdown hysteresis       | Die temperature T <sub>.1</sub>                                               |        | 20     |       | °C   |

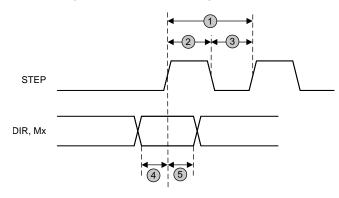

# 6.6 Indexer Timing Requirements

at  $T_A$  = -40 to 125°C,  $V_{VM}$  = 8 to 37 V (unless otherwise noted)

| NO. |                          |                                        | MIN | MAX | UNIT |

|-----|--------------------------|----------------------------------------|-----|-----|------|

| 1   | $f_{STEP}$ (1)           | Step frequency                         |     | 500 | kHz  |

| 2   | t <sub>WH(STEP)</sub>    | Pulse duration, STEP high              | 970 |     | ns   |

| 3   | t <sub>WL(STEP)</sub>    | Pulse duration, STEP low               | 970 |     | ns   |

| 4   | t <sub>SU(DIR, Mx)</sub> | Setup time, DIR or USMx to STEP rising | 200 |     | ns   |

| 5   | t <sub>H(DIR, Mx)</sub>  | Hold time, DIR or USMx to STEP rising  | 200 |     | ns   |

(1) STEP input can operate up to 500 kHz, but system bandwidth is limited by the motor load.

图 1. Timing Diagram

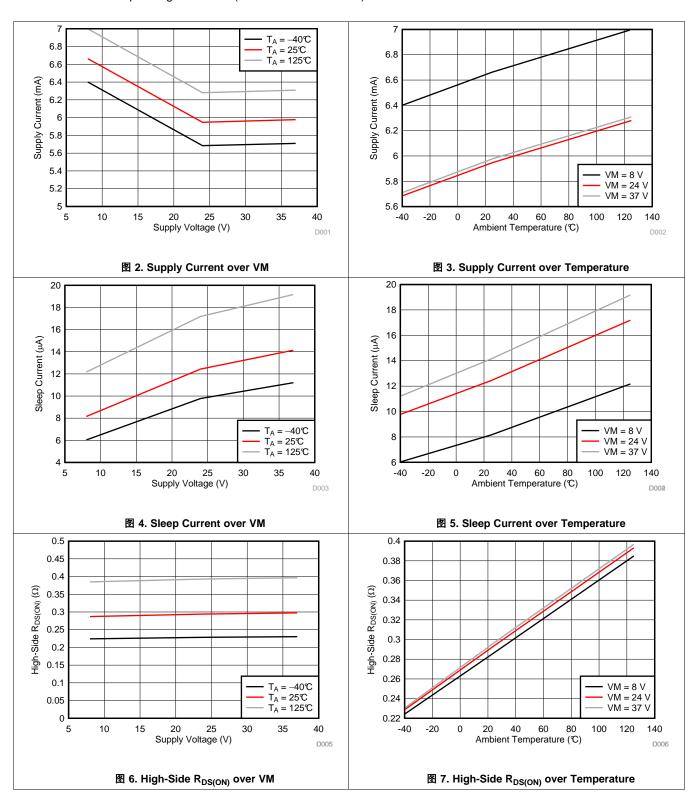

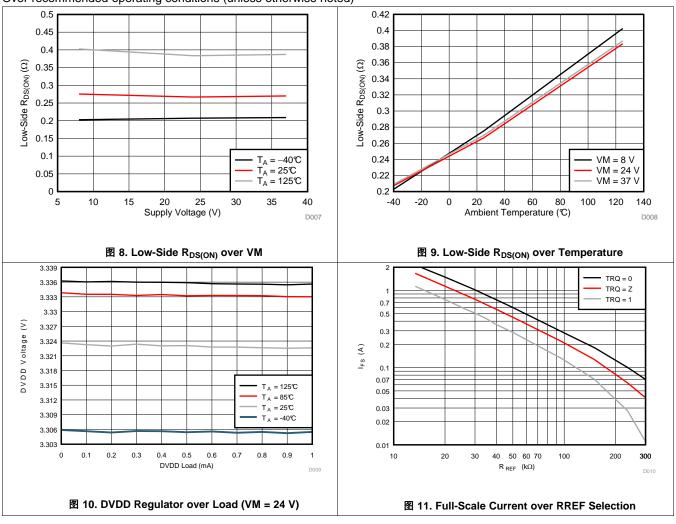

# 6.7 Typical Characteristics

Over recommended operating conditions (unless otherwise noted)

# TEXAS INSTRUMENTS

#### Typical Characteristics (接下页)

Over recommended operating conditions (unless otherwise noted)

#### 7 Detailed Description

#### 7.1 Overview

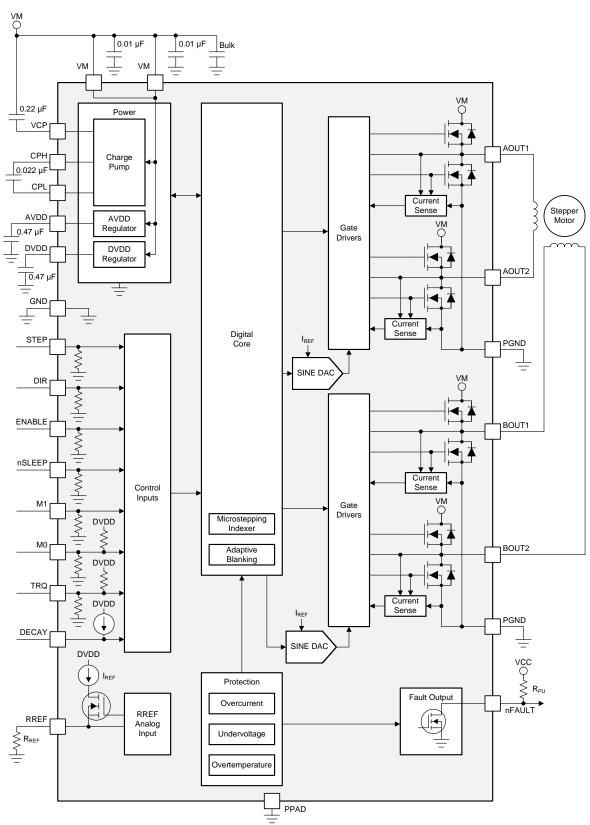

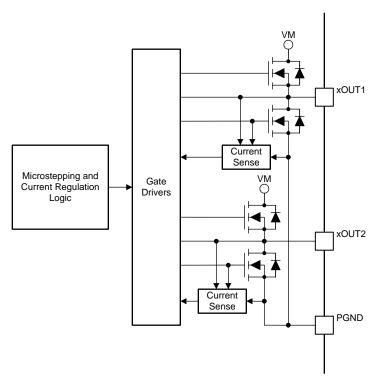

The DRV8886 device is an integrated motor-driver solution for bipolar stepper motors. The device integrates two N-channel power MOSFET H-bridges, integrated current sense and regulation circuitry, and a microstepping indexer. The DRV8886 device can be powered with a supply voltage from 8 to 37 V and is capable of providing an output current up to 3-A peak, 2-A full-scale, or 1.4-A root mean square (rms). The actual full-scale and rms current depends on the ambient temperature, supply voltage, and PCB thermal capability.

The DRV8886 device uses an integrated current-sense architecture which eliminates the need for two external power sense resistors. This architecture removes the power dissipated in the sense resistors by using a current mirror approach and using the internal power MOSFETs for current sensing. The current regulation set point is adjusted with a standard low-power resistor connected to the RREF pin. This features reduces external component cost, board PCB size, and system power consumption.

A simple STEP/DIR interface allows for an external controller to manage the direction and step rate of the stepper motor. The internal indexer can execute high-accuracy microstepping without requiring the external controller to manage the winding current level. The indexer is capable of full step, half step, and 1/4, 1/8, 1/16 microstepping. In addition to a standard half stepping mode, a non-circular half stepping mode is available for increased torque output at higher motor RPM.

The current regulation is configurable between several decay modes. The decay mode can be selected as a fixed slow, slow-mixed, or mixed decay current regulation scheme. The slow-mixed decay mode uses slow decay on increasing steps and mixed decay on decreasing steps.

An adaptive blanking time feature automatically scales the minimum drive time with output current level. This feature helps alleviate zero-crossing distortion by limiting the drive time at low-current steps.

A torque DAC feature allows the controller to scale the output current without needing to scale the RREF reference resistor. The torque DAC is accessed using a digital input pin which allows the controller to save system power by decreasing the motor current consumption when high output torque is not required.

A low-power sleep mode is included which allows the system to save power when not actively driving the motor.

# 7.2 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

#### 7.3 Feature Description

表 1 lists the recommended external components for the DRV8886 device.

表 1. DRV8886 External Components

| COMPONENT           | PIN 1   | PIN 2  | RECOMMENDED                                                                                                           |

|---------------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------|

| C <sub>VM1</sub>    | VM      | GND    | Two X5R or X7R, 0.01-µF, VM-rated ceramic capacitors                                                                  |

| C <sub>VM2</sub>    | VM      | GND    | Bulk, VM-rated capacitor                                                                                              |

| C <sub>VCP</sub>    | VCP     | VM     | X5R or X7R, 0.22-μF, 16-V ceramic capacitor                                                                           |

| C <sub>SW</sub>     | CPH     | CPL    | X5R or X7R, 0.022-µF, VM-rated ceramic capacitor                                                                      |

| C <sub>AVDD</sub>   | AVDD    | GND    | X5R or X7R, 0.47-μF, 6.3-V ceramic capacitor                                                                          |

| $C_{DVDD}$          | DVDD    | GND    | X5R or X7R, 0.47-μF, 6.3-V ceramic capacitor                                                                          |

| R <sub>nFAULT</sub> | VCC (1) | nFAULT | >4.7-kΩ resistor                                                                                                      |

| R <sub>REF</sub>    | RREF    | GND    | Resistor to limit chopping current must be installed. See the <i>Typical Application</i> section for value selection. |

<sup>(1)</sup> VCC is not a pin on the DRV8886 device, but a VCC supply voltage pullup is required for open-drain output nFAULT; nFAULT may be pulled up to DVDD

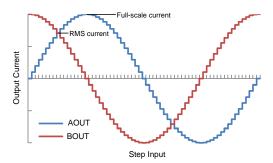

#### 7.3.1 Stepper Motor Driver Current Ratings

Stepper motor drivers can be classified using three different numbers to describe the output current: peak, rms, and full-scale.

#### 7.3.1.1 Peak Current Rating

The peak current in a stepper driver is limited by the overcurrent protection trip threshold, I<sub>OCP</sub>. The peak current describes any transient duration current pulse, for example when charging capacitance, when the overall duty cycle is very low. In general the minimum value of I<sub>OCP</sub> specifies the peak current rating of the stepper motor driver. For the DRV8886 device, the peak current rating is 3 A per bridge.

#### 7.3.1.2 rms Current Rating

The rms (average) current is determined by the thermal considerations of the device. The rms current is calculated based on the  $R_{DS(ON)}$ , rise and fall time, PWM frequency, device quiescent current, and package thermal performance in a typical system at 25°C. The actual operating rms current may be higher or lower depending on heatsinking and ambient temperature. For the DRV8886 device, the rms current rating is 1.4 A per bridge.

#### 7.3.1.3 Full-Scale Current Rating

The full-scale current describes the top of the sinusoid current waveform while microstepping. Because the sinusoid amplitude is related to the rms current, the full-scale current is also determined by the thermal considerations of the device. The full-scale current rating is approximately  $\sqrt{2} \times I_{RMS}$ . The full-scale current is set by the RREF pin and the torque DAC when configuring the DRV8886 device, for details see the *Current Regulation* section. For the DRV8886 device, the full-scale current rating is 2 A per bridge.

图 12. Full-Scale and rms Current

#### 7.3.2 PWM Motor Drivers

The DRV8886 device has drivers for two full H-bridges to drive the two windings of a bipolar stepper motor. Solve 13 shows a block diagram of the circuitry.

图 13. PWM Motor Driver Block Diagram

#### 7.3.3 Microstepping Indexer

Built-in indexer logic in the DRV8886 device allows a number of different step modes. The M1 and M0 pins are used to configure the step mode as shown in 表 2.

| 2(g - c-t-ppg - c-tg- |    |                                                 |  |  |  |  |

|-----------------------|----|-------------------------------------------------|--|--|--|--|

| M1                    | MO | STEP MODE                                       |  |  |  |  |

| 0                     | 0  | Full step (2-phase excitation) with 71% current |  |  |  |  |

| 0                     | 1  | 1/16 step                                       |  |  |  |  |

| 1                     | 0  | 1/2 step                                        |  |  |  |  |

| 1                     | 1  | 1/4 step                                        |  |  |  |  |

| 0                     | Z  | 1/8 step                                        |  |  |  |  |

| 1                     | Z  | Non-circular 1/2 step                           |  |  |  |  |

表 2. Microstepping Settings

表 3 shows the relative current and step directions for full-step through 1/16-step operation. The AOUT current is the sine of the electrical angle and the BOUT current is the cosine of the electrical angle. Positive current is defined as current flowing from the xOUT1 pin to the xOUT2 pin while driving.

At each rising edge of the STEP input the indexer travels to the next state in the table. The direction is shown with the DIR pin logic high. If the DIR pin is logic low, the sequence is reversed.

On power-up or when exiting sleep mode, keep the STEP pin logic low, otherwise the indexer advances one step.

注

If the step mode is changed from full, 1/2, 1/4, 1/8, or 1/16 to full, 1/2, 1/4, 1/8, or 1/16 while stepping, the indexer advances to the next valid state for the new step mode setting at the rising edge of STEP. If the step mode is changed from or to noncircular 1/2 step the indexer goes immediately to the valid state for that mode.

The home state is an electrical angle of 45°. This state is entered after power-up, after exiting logic undervoltage lockout, or after exiting sleep mode. 表 3 lists the home state in red.

表 3. Microstepping Relative Current Per Step (DIR = 1)

| FULL STEP | 1/2 STEP | 1/4 STEP | 1/8 STEP | 1/16 STEP | ELECTRICAL<br>ANGLE<br>(DEGREES) | AOUT<br>CURRENT (%<br>FULL-SCALE) | BOUT<br>CURRENT (%<br>FULL-SCALE) |

|-----------|----------|----------|----------|-----------|----------------------------------|-----------------------------------|-----------------------------------|

|           | 1        | 1        | 1        | 1         | 0.000°                           | 0%                                | 100%                              |

|           |          |          |          | 2         | 5.625°                           | 10%                               | 100%                              |

|           |          |          | 2        | 3         | 11.250°                          | 20%                               | 98%                               |

|           |          |          |          | 4         | 16.875°                          | 29%                               | 96%                               |

|           |          | 2        | 3        | 5         | 22.500°                          | 38%                               | 92%                               |

|           |          |          |          | 6         | 28.125°                          | 47%                               | 88%                               |

|           |          |          | 4        | 7         | 33.750°                          | 56%                               | 83%                               |

|           |          |          |          | 8         | 39.375°                          | 63%                               | 77%                               |

| 1         | 2        | 3        | 5        | 9         | 45.000°                          | 71%                               | 71%                               |

|           |          |          |          | 10        | 50.625°                          | 77%                               | 63%                               |

|           |          |          | 6        | 11        | 56.250°                          | 83%                               | 56%                               |

|           |          |          |          | 12        | 61.875°                          | 88%                               | 47%                               |

|           |          | 4        | 7        | 13        | 67.500°                          | 92%                               | 38%                               |

|           |          |          |          | 14        | 73.125°                          | 96%                               | 29%                               |

|           |          |          | 8        | 15        | 78.750°                          | 98%                               | 20%                               |

|           |          |          |          | 16        | 84.375°                          | 100%                              | 10%                               |

|           | 3        | 5        | 9        | 17        | 90.000°                          | 100%                              | 0%                                |

|           |          |          |          | 18        | 95.625°                          | 100%                              | -10%                              |

|           |          |          | 10       | 19        | 101.250°                         | 98%                               | -20%                              |

|           |          |          |          | 20        | 106.875°                         | 96%                               | -29%                              |

|           |          | 6        | 11       | 21        | 112.500°                         | 92%                               | -38%                              |

|           |          |          |          | 22        | 118.125°                         | 88%                               | -47%                              |

|           |          |          | 12       | 23        | 123.750°                         | 83%                               | -56%                              |

|           |          |          |          | 24        | 129.375°                         | 77%                               | -63%                              |

| 2         | 4        | 7        | 13       | 25        | 135.000°                         | 71%                               | -71%                              |

|           |          |          |          | 26        | 140.625°                         | 63%                               | -77%                              |

|           |          |          | 14       | 27        | 146.250°                         | 56%                               | -83%                              |

|           |          |          |          | 28        | 151.875°                         | 47%                               | -88%                              |

|           |          | 8        | 15       | 29        | 157.500°                         | 38%                               | -92%                              |

|           |          |          |          | 30        | 163.125°                         | 29%                               | -96%                              |

|           |          |          | 16       | 31        | 168.750°                         | 20%                               | -98%                              |

|           |          |          |          | 32        | 174.375°                         | 10%                               | -100%                             |

|           | 5        | 9        | 17       | 33        | 180.000°                         | 0%                                | -100%                             |

|           |          |          |          | 34        | 185.625°                         | -10%                              | -100%                             |

|           |          |          | 18       | 35        | 191.250°                         | -20%                              | -98%                              |

|           |          |          |          | 36        | 196.875°                         | -29%                              | -96%                              |

|           |          | 10       | 19       | 37        | 202.500°                         | -38%                              | -92%                              |

|           |          |          |          | 38        | 208.125°                         | -47%                              | -88%                              |

#### 表 3. Microstepping Relative Current Per Step (DIR = 1) (接下页)

| & of improstepping relative outlett of otep (birt = 1) (ix + x) |          |          |          |           |                                  |                                   |                                   |  |  |  |

|-----------------------------------------------------------------|----------|----------|----------|-----------|----------------------------------|-----------------------------------|-----------------------------------|--|--|--|

| FULL STEP                                                       | 1/2 STEP | 1/4 STEP | 1/8 STEP | 1/16 STEP | ELECTRICAL<br>ANGLE<br>(DEGREES) | AOUT<br>CURRENT (%<br>FULL-SCALE) | BOUT<br>CURRENT (%<br>FULL-SCALE) |  |  |  |

|                                                                 |          |          | 20       | 39        | 213.750°                         | -56%                              | -83%                              |  |  |  |

|                                                                 |          |          |          | 40        | 219.375°                         | -63%                              | -77%                              |  |  |  |

| 3                                                               | 6        | 11       | 21       | 41        | 225.000°                         | -71%                              | -71%                              |  |  |  |

|                                                                 |          |          |          | 42        | 230.625°                         | -77%                              | -63%                              |  |  |  |

|                                                                 |          |          | 22       | 43        | 236.250°                         | -83%                              | -56%                              |  |  |  |

|                                                                 |          |          |          | 44        | 241.875°                         | -88%                              | -47%                              |  |  |  |

|                                                                 |          | 12       | 23       | 45        | 247.500°                         | -92%                              | -38%                              |  |  |  |

|                                                                 |          |          |          | 46        | 253.125°                         | -96%                              | -29%                              |  |  |  |

|                                                                 |          |          | 24       | 47        | 258.750°                         | -98%                              | -20%                              |  |  |  |

|                                                                 |          |          |          | 48        | 264.375°                         | -100%                             | -10%                              |  |  |  |

|                                                                 | 7        | 13       | 25       | 49        | 270.000°                         | -100%                             | 0%                                |  |  |  |

|                                                                 |          |          |          | 50        | 275.625°                         | -100%                             | 10%                               |  |  |  |

|                                                                 |          |          | 26       | 51        | 281.250°                         | -98%                              | 20%                               |  |  |  |

|                                                                 |          |          |          | 52        | 286.875°                         | -96%                              | 29%                               |  |  |  |

|                                                                 |          | 14       | 27       | 53        | 292.500°                         | -92%                              | 38%                               |  |  |  |

|                                                                 |          |          |          | 54        | 298.125°                         | -88%                              | 47%                               |  |  |  |

|                                                                 |          |          | 28       | 55        | 303.750°                         | -83%                              | 56%                               |  |  |  |

|                                                                 |          |          |          | 56        | 309.375°                         | -77%                              | 63%                               |  |  |  |

| 4                                                               | 8        | 15       | 29       | 57        | 315.000°                         | -71%                              | 71%                               |  |  |  |

|                                                                 |          |          |          | 58        | 320.625°                         | -63%                              | 77%                               |  |  |  |

|                                                                 |          |          | 30       | 59        | 326.250°                         | -56%                              | 83%                               |  |  |  |

|                                                                 |          |          |          | 60        | 331.875°                         | -47%                              | 88%                               |  |  |  |

|                                                                 |          | 16       | 31       | 61        | 337.500°                         | -38%                              | 92%                               |  |  |  |

|                                                                 |          |          |          | 62        | 343.125°                         | -29%                              | 96%                               |  |  |  |

|                                                                 |          |          | 32       | 63        | 348.750°                         | -20%                              | 98%                               |  |  |  |

|                                                                 |          |          |          | 64        | 354.375°                         | -10%                              | 100%                              |  |  |  |

|                                                                 | 1        | 1        | 1        | 1         | 360.000°                         | 0%                                | 100%                              |  |  |  |

表 4 shows the noncircular 1/2-step operation. This stepping mode consumes more power than circular 1/2-step operation, but provides a higher torque at high motor rpm.

#### 表 4. Non-Circular 1/2-Stepping Current

|                       |                                | •                              |                               |

|-----------------------|--------------------------------|--------------------------------|-------------------------------|

| NON-CIRCULAR 1/2-STEP | AOUT CURRENT<br>(% FULL-SCALE) | BOUT CURRENT<br>(% FULL-SCALE) | ELECTRICAL ANGLE<br>(DEGREES) |

| 1                     | 0                              | 100                            | 0                             |

| 2                     | 100                            | 100                            | 45                            |

| 3                     | 100                            | 0                              | 90                            |

| 4                     | 100                            | -100                           | 135                           |

| 5                     | 0                              | -100                           | 180                           |

| 6                     | -100                           | -100                           | 225                           |

| 7                     | -100                           | 0                              | 270                           |

| 8                     | -100                           | 100                            | 315                           |

#### 7.3.4 Current Regulation

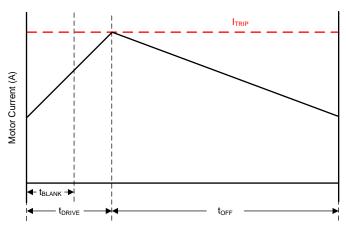

The current through the motor windings is regulated by an adjustable, fixed-off-time PWM current-regulation circuit. When an H-bridge is enabled, current rises through the winding at a rate dependent on the supply voltage, inductance of the winding, and the magnitude of the back EMF present. When the current hits the current regulation threshold, the bridge enters a decay mode for a fixed  $20~\mu s$ , period of time to decrease the current. After the off time expires, the bridge is re-enabled, starting another PWM cycle.

图 14. Current Chopping Waveform

The PWM regulation current is set by a comparator which monitors the voltage across the current sense MOSFETs in parallel with the low-side power MOSFETs. The current sense MOSFETs are biased with a reference current that is the output of a current-mode sine-weighted DAC whose full-scale reference current is set by the current through the RREF pin. An external resistor is placed from the RREF pin to GND to set the reference current. In addition, the TRQ pin can further scale the reference current.

Use 公式 1 to calculate the full-scale regulation current.

$$I_{FS} (A) = \frac{A_{RREF} (kA\Omega)}{RREF (k\Omega)} \times TRQ (\%) = \frac{30 (kA\Omega)}{RREF (k\Omega)} \times TRQ (\%)$$

(1)

For example, if a 30-k $\Omega$  resistor is connected to the RREF pin, the full-scale regulation current is 1 A (TRQ at 100%).

The TRQ pin is the input to a DAC used to scale the output current. 表 5 lists the current scalar value for different inputs.

表 5. Torque DAC Settings

| TRQ | CURRENT SCALAR (TRQ) |

|-----|----------------------|

| 0   | 100%                 |

| Z   | 75%                  |

| 1   | 50%                  |

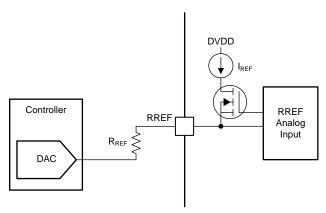

#### 7.3.5 Controlling RREF With an MCU DAC

In some cases, the full-scale output current may need to be changed between many different values, depending on motor speed and loading. The reference current of the RREF pin can be adjusted in the system by tying the RREF resistor to a DAC output instead of GND.

In this mode of operation, as the DAC voltage increases, the reference current decreases and therefore the full-scale regulation current decreases as well. For proper operation, the output of the DAC should not rise above  $V_{RREF}$ .

图 15. Controlling RREF With a DAC Resource

Use 公式 2 to calculate the full-scale regulation current as controlled by a controller DAC.

$$I_{FS}(A) = \frac{A_{RREF}(kA\Omega) \times \left[V_{RREF}(V) - V_{DAC}(V)\right]}{V_{RREF}(V) \times RREF(k\Omega)} \times TRQ(\%)$$

(2)

For example, if a 20-k $\Omega$  resistor is connected from the RREF pin to the DAC, and the DAC outputs 0.74 V, the chopping current is 600 mA (TRQ at 100%)

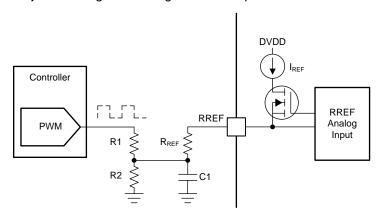

The RREF pin can also be adjusted using a PWM signal and low-pass filter.

图 16. Controlling RREF With a PWM Resource

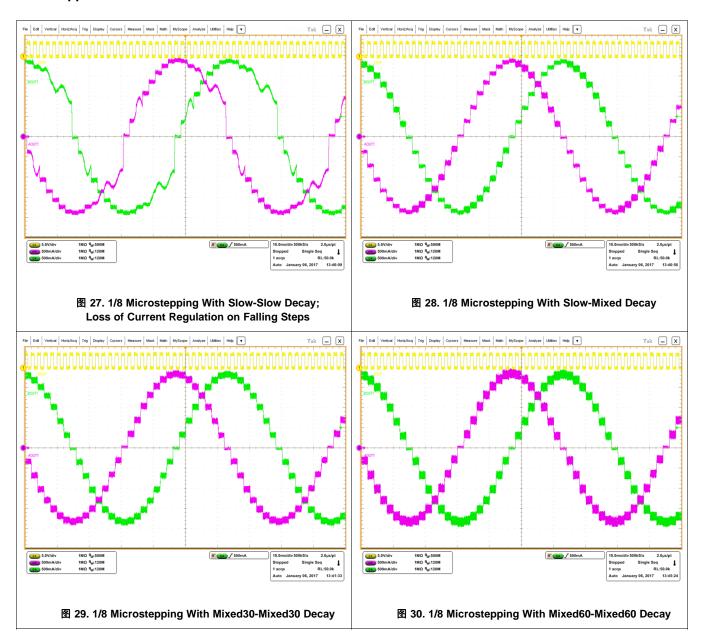

#### 7.3.6 Decay Modes

Can be tied to DVDD

The DRV8886 decay mode is selected by setting the quad-level DECAY pin to the voltage range listed in 表 6. The decay mode setting can be modified during device operation.

| 2, 0, 2, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, |                       |                       |  |  |  |  |  |

|-------------------------------------------------|-----------------------|-----------------------|--|--|--|--|--|

| DECAY                                           | INCREASING STEPS      | DECREASING STEPS      |  |  |  |  |  |

| 100 mV<br>Can be tied to ground                 | Slow decay            | Mixed decay: 30% fast |  |  |  |  |  |

| 300 mV, 15 k $\Omega$ to GND                    | Mixed decay: 30% fast | Mixed decay: 30% fast |  |  |  |  |  |

| 1 V, 45 kΩ to GND                               | Mixed decay: 60% fast | Mixed decay: 60% fast |  |  |  |  |  |

| 2.9 V                                           | Olassa da a sas       | Olassa da assa        |  |  |  |  |  |

Slow decay

Slow decay

表 6. Decay Mode Settings

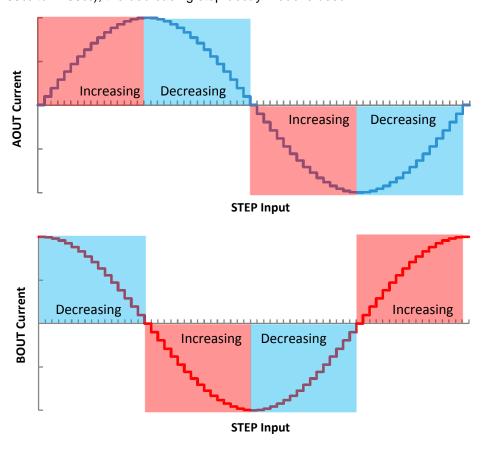

₹ 17 defines increasing and decreasing current. For the slow-mixed decay mode, the decay mode is set as slow during increasing current steps and mixed decay during decreasing current steps. In full step mode the decreasing steps decay mode is always used. In noncircular 1/2-step mode the increasing step decay mode is used after a level transition (0% to 100% and 0% to −100%). When the level transition is to a similar level (100% to 100% and −100% to −100%), the decreasing step decay mode is used.

图 17. Definition of Increasing and Decreasing Steps

#### 7.3.6.1 Mode 1: Slow Decay for Increasing Current, Mixed Decay for Decreasing Current

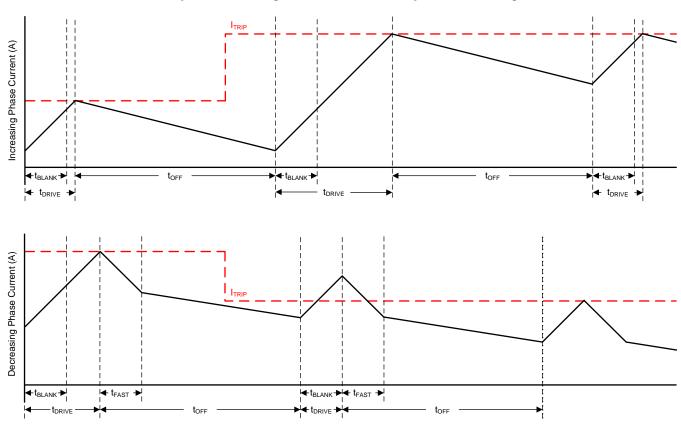

图 18. Slow-Mixed Decay Mode

Mixed decay begins as fast decay for a time, followed by slow decay for the remainder of the  $t_{OFF}$  time. In this mode, mixed decay only occurs during decreasing current. Slow decay is used for increasing current.

This mode exhibits the same current ripple as slow decay for increasing current because for increasing current, only slow decay is used. For decreasing current, the ripple is larger than slow decay, but smaller than fast decay. On decreasing current steps, mixed decay will settle to the new I<sub>TRIP</sub> level faster than slow decay.

#### 7.3.6.2 Mode 2: Mixed Decay for Increasing and Decreasing Current

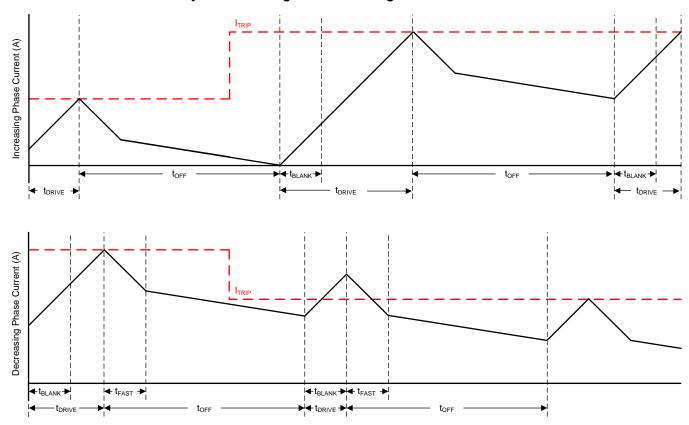

图 19. Mixed-Mixed Decay Mode

Mixed decay begins as fast decay for a time, followed by slow decay for the remainder of  $t_{OFF}$ . In this mode, mixed decay occurs for both increasing and decreasing current steps.

This mode exhibits ripple larger than slow decay, but smaller than fast decay. On decreasing current steps, mixed decay settles to the new I<sub>TRIP</sub> level faster than slow decay.

In cases where current is held for a long time (no input in the STEP pin) or at very low stepping speeds, slow decay may not properly regulate current because no back-EMF is present across the motor windings. In this state, motor current can rise very quickly, and requires an excessively large off-time. Increasing or decreasing mixed decay mode allows the current level to stay in regulation when no back-EMF is present across the motor windings.

#### 7.3.6.3 Mode 3: Slow Decay for Increasing and Decreasing Current

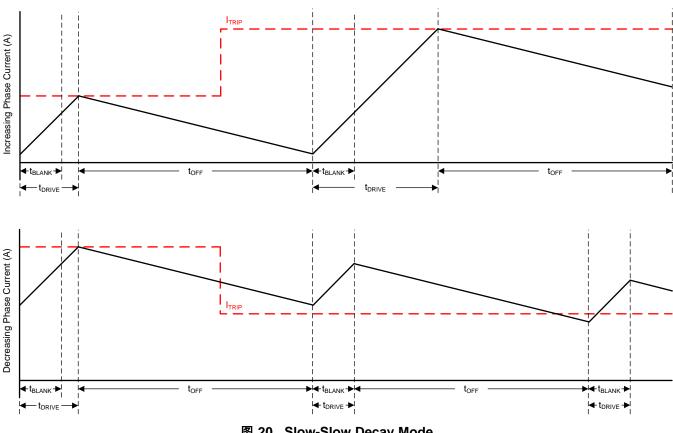

图 20. Slow-Slow Decay Mode

During slow decay, both of the low-side MOSFETs of the H-bridge are turned on, allowing the current to be recirculated.

Slow decay exhibits the least current ripple of the decay modes for a given  $t_{\text{OFF}}$ . However, on decreasing current steps, slow decay takes a long time to settle to the new I<sub>TRIP</sub> level because the current decreases very slowly.

#### 7.3.7 Blanking Time

After the current is enabled in an H-bridge, the current sense comparator is ignored for a period of time ( $t_{BLANK}$ ) before enabling the current-sense circuitry. The blanking time also sets the minimum drive time of the PWM. 表 7 shows the blanking time based on the sine table index and the torque DAC setting. The torque DAC index is not the same as one step as given in 表 3.

表 7. Adaptive Blanking Time over Torque DAC and Microsteps

t<sub>blank</sub> = 1.5 μs t<sub>blank</sub> = 1 μs

| CINE INDEV | TORQUE DAC (TRQ) |       |       |  |  |  |  |

|------------|------------------|-------|-------|--|--|--|--|

| SINE INDEX | 100%             | 75%   | 50%   |  |  |  |  |

| 16         | 100%             | 75%   | 50%   |  |  |  |  |

| 15         | 98%              | 73.5  | 49%   |  |  |  |  |

| 14         | 96%              | 72%   | 48%   |  |  |  |  |

| 13         | 92%              | 69%   | 46%   |  |  |  |  |

| 12         | 88%              | 66%   | 44%   |  |  |  |  |

| 11         | 83%              | 62.3% | 41.5% |  |  |  |  |

| 10         | 77%              | 57.8% | 38.5% |  |  |  |  |

| 9          | 71%              | 53.3% | 35.5% |  |  |  |  |

| 8          | 63%              | 47.3% | 31.5% |  |  |  |  |

| 7          | 56%              | 42%   | 28%   |  |  |  |  |

| 6          | 47%              | 35.3  | 23.5% |  |  |  |  |

| 5          | 38%              | 28.5  | 19%   |  |  |  |  |

| 4          | 29%              | 21.8% | 14.5% |  |  |  |  |

| 3          | 20%              | 15%   | 10%   |  |  |  |  |

| 2          | 10%              | 7.5%  | 5%    |  |  |  |  |

| 1          | 0%               | 0%    | 0%    |  |  |  |  |

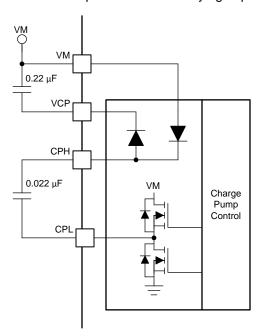

#### 7.3.8 Charge Pump

A charge pump is integrated to supply a high-side N-channel MOSFET gate-drive voltage. The charge pump requires a capacitor between the VM and VCP pins to act as the storage capacitor. Additionally a ceramic capacitor is required between the CPH and CPL pins to act as the flying capacitor.

图 21. Charge Pump Block Diagram

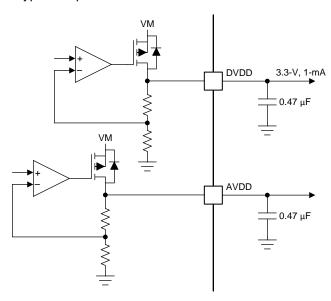

#### 7.3.9 Linear Voltage Regulators

An linear voltage regulator is integrated into the DRV8886 device. The DVDD regulator can be used to provide a reference voltage. For proper operation, bypass the DVDD pin to GND using a ceramic capacitor.

The DVDD output is nominally 3.3 V. When the DVDD LDO current load exceeds 1 mA, the output voltage drops significantly.

The AVDD pin also requires a bypass capacitor to GND. This LDO is for DRV8886 internal use only.

图 22. Linear Voltage Regulator Block Diagram

If a digital input must be tied permanently high (that is, Mx, DECAY or TRQ), tying the input to the DVDD pin instead of an external regulator is preferred. This method saves power when the VM pin is not applied or in sleep mode: the DVDD regulator is disabled and current does not flow through the input pulldown resistors. For reference, logic level inputs have a typical pulldown of 100 k $\Omega$ , and tri-level inputs have a typical pulldown of 60 k $\Omega$ .

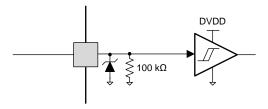

#### 7.3.10 Logic and Multi-Level Pin Diagrams

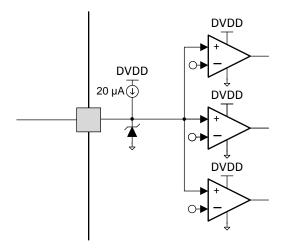

图 23 shows the input structure for the logic-level pins STEP, DIR, ENABLE, nSLEEP, and M1.

图 23. Logic-Level Input Pin Diagram

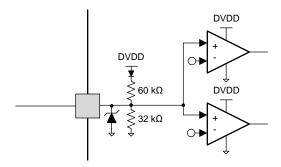

The tri-level logic pins, M0 and TRQ, have the structure shown in \textstyle 24.

图 24. Tri-Level Input Pin Diagram

The quad-level logic pin, DECAY, has the structure shown in ₹ 25.

图 25. Quad-Level Input Pin Diagram

#### 7.3.11 Protection Circuits

The DRV8886 device is fully protected against supply undervoltage, charge pump undervoltage, output overcurrent, and device overtemperature events.

#### 7.3.11.1 VM Undervoltage Lockout (UVLO)

If at any time the voltage on the VM pin falls below the VM undervoltage-lockout threshold voltage ( $V_{UVLO}$ ), all MOSFETs in the H-bridge are disabled, the charge pump is disabled, the logic is reset, and the nFAULT pin is driven low. Operation resumes when the VM voltage rises above the  $V_{UVLO}$  threshold. The nFAULT pin is released after operation resumes. Decreasing the VM voltage below this undervoltage threshold resets the indexer position.

#### 7.3.11.2 VCP Undervoltage Lockout (CPUV)

If at any time the voltage on the VCP pin falls below the charge-pump undervoltage-lockout threshold voltage  $(V_{CPUV})$ , all MOSFETs in the H-bridge are disabled and the nFAULT pin is driven low. Operation resumes when the VCP voltage rises above the  $V_{CPUV}$  threshold. The nFAULT pin is released after operation resumes.

#### 7.3.11.3 Overcurrent Protection (OCP)

An analog current-limit circuit on each MOSFET limits the current through the MOSFET by removing the gate drive. If this analog current limit persists for longer than  $t_{\rm OCP}$ , all MOSFETs in the H-bridge are disabled and the nFAULT pinis driven low.

The driver is re-enabled after the OCP retry period ( $t_{RETRY}$ ) has passed. The nFAULT pin becomes high again at after the retry time. If the fault condition is still present, the cycle repeats. If the fault is no longer present, normal operation resumes and nFAULT remains deasserted.

#### 7.3.11.4 Thermal Shutdown (TSD)

If the die temperature exceeds  $T_{TSD}$  level, all MOSFETs in the H-bridge are disabled and the nFAULT pin is driven low. When the die temperature falls below the  $T_{TSD}$  level, operation automatically resumes. The nFAULT pin is released after operation resumes.

表 8. Fault Condition Summary

| FAULT                   | CONDITION                                        | ERROR<br>REPORT | H-BRIDGE | CHARGE<br>PUMP | INDEXER   | DVDD      | AVDD      | RECOVERY                                                                   |

|-------------------------|--------------------------------------------------|-----------------|----------|----------------|-----------|-----------|-----------|----------------------------------------------------------------------------|

| VM undervoltage (UVLO)  | VM < V <sub>UVLO</sub><br>(max 7.8 V)            | nFAULT          | Disabled | Disabled       | Disabled  | Operating | Disabled  | VM > V <sub>UVLO</sub><br>(max 8 V)                                        |

| VCP undervoltage (CPUV) | $VCP < V_{CPUV}$<br>(typ VM + 2 V)               | nFAULT          | Disabled | Operating      | Operating | Operating | Operating | $VCP > V_{CPUV}$<br>(typ VM + 2.7 V)                                       |

| Overcurrent (OCP)       | I <sub>OUT</sub> > I <sub>OCP</sub> (min 3 A)    | nFAULT          | Disabled | Operating      | Operating | Operating | Operating | t <sub>RETRY</sub>                                                         |

| Thermal shutdown (TSD)  | T <sub>J</sub> > T <sub>TSD</sub><br>(min 150°C) | nFAULT          | Disabled | Operating      | Operating | Operating | Operating | $T_{J} < T_{TSD} - $ $T_{HYS}$ $(T_{HYS} \text{ typ } 20^{\circ}\text{C})$ |

#### 7.4 Device Functional Modes

The DRV8886 device is active unless the nSLEEP pin is brought logic low. In sleep mode the charge pump is disabled, the H-bridge MOSFETs are disabled Hi-Z, and the regulators are disabled.

注

The t<sub>SLEEP</sub> time must elapse after a falling edge on the nSLEEP pin before the device is in sleep mode. The DRV8886 device is brought out of sleep mode automatically if nSLEEP is brought logic high.

The t<sub>WAKE</sub> time must elapse before the outputs change state after wake-up.

TI recommends to keep the STEP pin logic low when coming out of nSLEEP or when applying power.

If the ENABLE pin is brought logic low, the H-bridge outputs are disabled, but the internal logic is still active. A rising edge on STEP advances the indexer, but the outputs do not change state until the ENABLE pin is asserted.

表 9 lists a summary of the functional modes.

#### 表 9. Functional Modes Summary

| С                 | ONDITION                                            | H-BRIDGE  | CHARGE PUMP | INDEXER   | DVDD      | AVDD      |

|-------------------|-----------------------------------------------------|-----------|-------------|-----------|-----------|-----------|

| Operating         | 8 V < VM < 40 V<br>nSLEEP pin = 1<br>ENABLE pin = 1 | Operating | Operating   | Operating | Operating | Operating |

| Disabled          | 8 V < VM < 40 V<br>nSLEEP pin = 1<br>ENABLE pin = 0 | Disabled  | Operating   | Operating | Operating | Operating |

| Sleep mode        | 8 V < VM < 40<br>nSLEEP pin = 0                     | Disabled  | Disabled    | Disabled  | Disabled  | Disabled  |

|                   | VM undervoltage (UVLO)                              | Disabled  | Disabled    | Disabled  | Operating | Disabled  |

| Fault encountered | VCP undervoltage (CPUV)                             | Disabled  | Operating   | Operating | Operating | Operating |

|                   | Overcurrent (OCP)                                   | Disabled  | Operating   | Operating | Operating | Operating |

|                   | Thermal Shutdown (TSD)                              | Disabled  | Operating   | Operating | Operating | Operating |

# 8 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The DRV8886 device is used in bipolar stepper control.

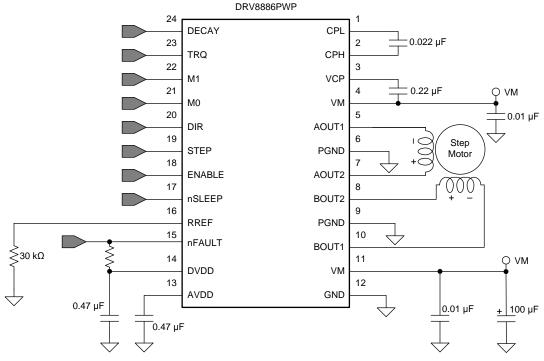

#### 8.2 Typical Application

The following design procedure can be used to configure the DRV8886 device.

Copyright © 2017, Texas Instruments Incorporated

图 26. Typical Application Schematic

#### 8.2.1 Design Requirements

表 10 lists the design input parameters for system design.

表 10. Design Parameters

| DESIGN PARAMETER           | REFERENCE           | EXAMPLE VALUE |

|----------------------------|---------------------|---------------|

| Supply voltage             | VM                  | 24 V          |

| Motor winding resistance   | $R_{L}$             | 2.6 Ω/phase   |

| Motor winding inductance   | L <sub>L</sub>      | 1.4 mH/phase  |

| Motor full step angle      | $\theta_{\sf step}$ | 1.8°/step     |

| Target microstepping level | n <sub>m</sub>      | 1/8 step      |

| Target motor speed         | V                   | 120 rpm       |

| Target full-scale current  | I <sub>FS</sub>     | 2 A           |

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Stepper Motor Speed

The first step in configuring the DRV8886 device requires the desired motor speed and microstepping level. If the target application requires a constant speed, then a square wave with frequency  $f_{\text{step}}$  must be applied to the STEP pin.

If the target motor speed is too high, the motor does not spin. Make sure that the motor can support the target speed.

Use 公式 3 to calculate  $f_{\text{step}}$  for a desired motor speed (v), microstepping level (n<sub>m</sub>), and motor full step angle ( $\theta_{\text{step}}$ ).

$$f_{\text{step}} \text{ (steps/s)} = \frac{\text{v (rpm)} \times 360 (^{\circ}/\text{rot})}{\theta_{\text{step}} (^{\circ}/\text{step}) \times n_{\text{m}} \text{ (steps/microstep)} \times 60 \text{ (s/min)}}$$

(3)

The value of  $\theta_{\text{step}}$  can be found in the stepper motor data sheet, or written on the motor.

For the DRV8886 device, the microstepping level is set by the Mx pins and can be any of the settings listed in  $\frac{1}{5}$  11. Higher microstepping results in smoother motor motion and less audible noise, but increases switching losses and requires a higher  $f_{\text{step}}$  to achieve the same motor speed.

|    | Z : me. eetepping maeker eetinge |                                                 |  |  |  |  |  |

|----|----------------------------------|-------------------------------------------------|--|--|--|--|--|

| M1 | МО                               | STEP MODE                                       |  |  |  |  |  |

| 0  | 0                                | Full step (2-phase excitation) with 71% current |  |  |  |  |  |

| 0  | 1                                | 1/16 step                                       |  |  |  |  |  |

| 1  | 0                                | 1/2 step                                        |  |  |  |  |  |

| 1  | 1                                | 1/4 step                                        |  |  |  |  |  |

| 0  | Z                                | 1/8 step                                        |  |  |  |  |  |

| 1  | Z                                | Non-circular 1/2 step                           |  |  |  |  |  |

表 11. Microstepping Indexer Settings

For example, the motor is 1.8°/step for a target of 120 rpm at 1/8 microstep mode.

$$f_{\text{step}} \text{ (steps/s)} = \frac{120 \text{ rpm} \times 360^{\circ}/\text{rot}}{1.8^{\circ}/\text{step} \times 1/8 \text{ steps/microstep} \times 60 \text{ s/min}} = 3.2 \text{ kHz}$$

(4)

#### 8.2.2.2 Current Regulation

In a stepper motor, the full-scale current ( $I_{FS}$ ) is the maximum current driven through either winding. This quantity depends on the RREF resistor and the TRQ setting. During stepping,  $I_{FS}$  defines the current chopping threshold ( $I_{TRIP}$ ) for the maximum current step.

$$I_{FS} (A) = \frac{A_{RREF} (kA\Omega)}{RREF (k\Omega)} = \frac{30 (kA\Omega) \times TRQ\%}{RREF (k\Omega)}$$

(5)

注

The  $I_{FS}$  current must also follow  $\Delta \vec{\pm}$  6 to avoid saturating the motor. VM is the motor supply voltage, and  $R_L$  is the motor winding resistance.

$$I_{FS}(A) < \frac{VM(V)}{R_L(\Omega) + 2 \times R_{DS(ON)}(\Omega)}$$

(6)

#### 8.2.2.3 Decay Modes

The DRV8886 device supports three different decay modes: slow decay, slow-mixed decay, and all mixed decay. The current through the motor windings is regulated using an adjustable fixed-time-off scheme which means that after any drive phase, when a motor winding current has hit the current chopping threshold ( $I_{TRIP}$ ), the DRV8886 places the winding in one of the three decay modes for  $I_{OFF}$ . After  $I_{OFF}$ , a new drive phase starts.

The blanking time,  $t_{BLANK}$ , defines the minimum drive time for the PWM current chopping.  $I_{TRIP}$  is ignored during  $t_{BLANK}$ , so the winding current may overshoot the trip level.

#### 8.2.3 Application Curves

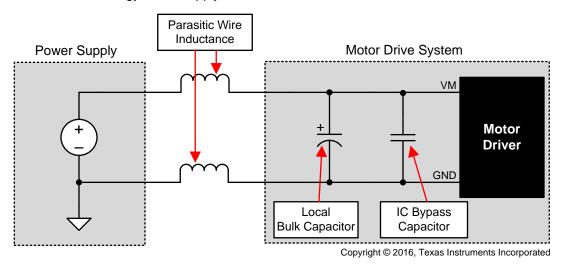

# 9 Power Supply Recommendations

The DRV8886 device is designed to operate from an input voltage supply (VM) range from 8 V to 37 V. A 0.01µF ceramic capacitor rated for VM must be placed at each VM pin as close to the DRV8886 device as possible. In addition, a bulk capacitor must be included on VM.

#### 9.1 Bulk Capacitance

Having appropriate local bulk capacitance is an important factor in motor drive system design. It is generally beneficial to have more bulk capacitance, while the disadvantages are increased cost and physical size.

The amount of local capacitance needed depends on a variety of factors, including:

- · The highest current required by the motor system

- The power supply's capacitance and ability to source current

- · The amount of parasitic inductance between the power supply and motor system

- · The acceptable voltage ripple

- The type of motor used (brushed DC, brushless DC, stepper)

- · The motor braking method

The inductance between the power supply and motor drive system will limit the rate current can change from the power supply. If the local bulk capacitance is too small, the system will respond to excessive current demands or dumps from the motor with a change in voltage. When adequate bulk capacitance is used, the motor voltage remains stable and high current can be quickly supplied.

The data sheet generally provides a recommended value, but system-level testing is required to determine the appropriate sized bulk capacitor.

The voltage rating for bulk capacitors should be higher than the operating voltage, to provide margin for cases when the motor transfers energy to the supply.

图 31. Example Setup of Motor Drive System With External Power Supply

#### 10 Layout

#### 10.1 Layout Guidelines

The VM pin should be bypassed to GND using a low-ESR ceramic bypass capacitor with a recommended value of 0.01  $\mu$ F rated for VM. This capacitor should be placed as close to the VM pin as possible with a thick trace or ground plane connection to the device GND pin.

The VM pin must be bypassed to ground using a bulk capacitor rated for VM. This component can be an electrolytic capacitor.

A low-ESR ceramic capacitor must be placed between the CPL and CPH pins. A value of 0.022 µF rated for VM is recommended. Place this component as close to the pins as possible.

A low-ESR ceramic capacitor must be placed between the VM and VCP pins. A value of 0.22 µF rated for 16 V is recommended. Place this component as close to the pins as possible.

Bypass the AVDD and DVDD pins to ground with a low-ESR ceramic capacitor rated 6.3 V. Place this bypass capacitor as close to the pin as possible.

#### 10.2 Layout Example

图 32. Layout Recommendation

#### 11 器件和文档支持

#### 11.1 文档支持

#### 11.1.1 相关文档

请参阅如下相关文档:

- 德州仪器 (TI), 《计算电机驱动器的功耗》应用报告

- 德州仪器 (TI), 《电流再循环和衰减模式》应用报告

- 德州仪器 (TI), 《DRV8886 评估模块用户指南》

- 德州仪器 (TI), 《使用数模转换器 (DAC) 调整满量程电流》应用报告

- 德州仪器 (TI), 《工业电机驱动解决方案指南》

- 德州仪器 (TI), 《PowerPAD™ 速成》应用报告

- 德州仪器 (TI), 《PowerPAD™ 热增强型封装》应用报告