**FPC402** ZHCSLX3C - JUNE 2017 - REVISED SEPTEMBER 2020

# FPC402 四端口控制器

## 1 特性

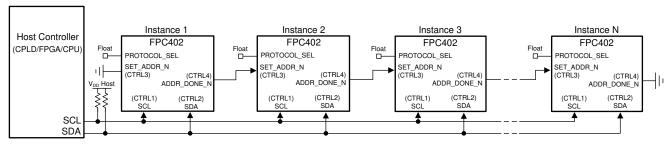

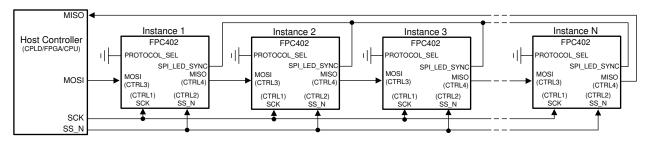

- 跨四个端口进行控制信号管理和 I2C 聚合

- 结合多个 FPC402,通过单个主机接口总共控制 56 个端口

- 无需使用分立式 I2C 多路复用器、LED 驱动器和高 引脚数 FPGA/CPLD 控制器件

- 通过处理接近端口的全部低速控制信号来降低 PCB 布线复杂性

- 可选 I2C(高达 1MHz)或 SPI(高达 10MHz)主 机控制接口

- 从模块中自动预取用户指定的重要数据

- 在广播模式下可以对所有 FPC402 控制器的全部端 口同时执行写操作

- 用于端口状态指示的高级 LED 功能,包括可编程闪 烁和调光功能

- 可定制中断事件

- 单独的主机侧 I/O 电压:1.8V 至 3.3V

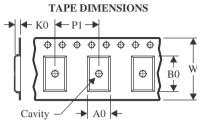

- 采用小型 WQFN 封装,能够放置在 PCB 底部、端 口下方

## 2 应用

- ToR/聚合/核心交换机和路由器

- 无线基础设施基带单元和远程射频单元

- 视频交换机和路由器

- 存储卡和存储机架

- SFP、QSFP、QSFP-DD、OSFP、Mini-SAS HD 端口管理

## 3 说明

FPC402 四端口控制器用作低速信号聚合器,适用于 SFP、QSFP 和 Mini-SAS HD 等通用端口类型。 FPC402 能够跨四个端口聚合所有低速控制和 I2C 信号,并为主机提供一个易于使用的管理接口(I2C 或 SPI)。使用连接到主机的公共控制接口,多个 FPC402 可用于高端口数应用。FPC402 所采用的设 计允许放置在 PCB 底部、压合连接器下方,这样可 以简化布线。凭借这种对端口中低速信号的本地控制方 法,可以使用 IO 数更少的控制器件(FPGA、CPLD 和 MCU)并减少布线层拥塞,从而降低系统 BOM 成 本。

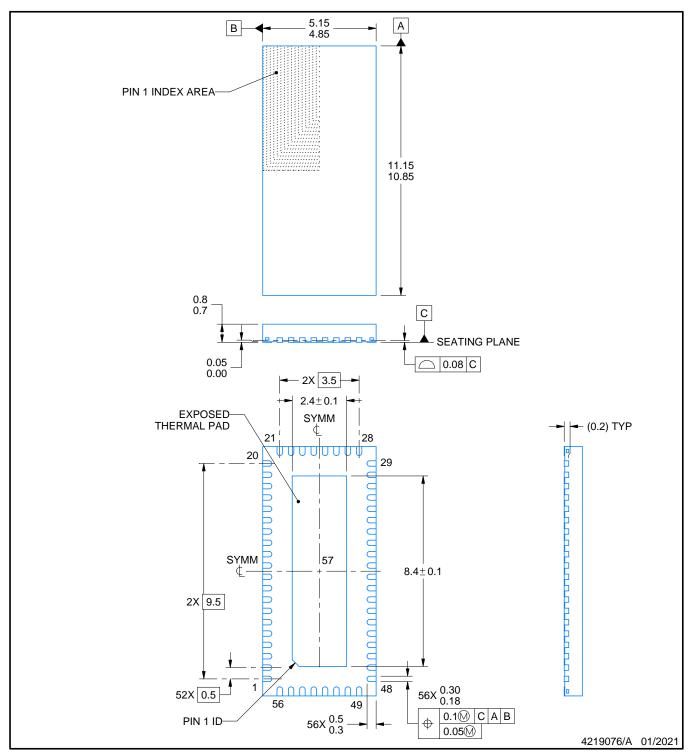

#### 器件信息(1)

| 器件型号   | 封装        | 封装尺寸 ( 标称值 )     |

|--------|-----------|------------------|

| FPC402 | WQFN (56) | 5.00mm × 11.00mm |

要了解所有可用封装,请参阅产品说明书末尾的可订购产品附

#### 器件比较

| 器件型号   | 可访问下游地址          | 引脚兼容 |

|--------|------------------|------|

| FPC402 | 所有有效 I2C 地址      | 是    |

| FPC401 | MSA 地址:0xA0、0xA2 | 是    |

简化版方框图

English Data Sheet: SNLS582

## Table of Contents

|                                                             | iable of       | Contents                                |                 |

|-------------------------------------------------------------|----------------|-----------------------------------------|-----------------|

| 1 特性                                                        | 1              | 8.4 Device Functional Modes             | 22              |

| 2 应用                                                        | 1              | 8.5 Programming                         | 28              |

| 3 说明                                                        |                | 9 Application and Implementation        |                 |

| 4 Revision History                                          | <mark>2</mark> | 9.1 Application Information             |                 |

| 5 说明(续)                                                     |                | 9.2 Typical Application                 | <mark>29</mark> |

| 6 Pin Configuration and Functions                           | 4              | 10 Power Supply Recommendations         |                 |

| Pin Functions                                               |                | 10.1 Power Supply Sequencing            |                 |

| 7 Specifications                                            | <b>7</b>       | 11 Layout                               |                 |

| 7.1 Absolute Maximum Ratings                                |                | 11.1 Layout Guidelines                  |                 |

| 7.2 ESD Ratings                                             |                | 11.2 Layout Example                     |                 |

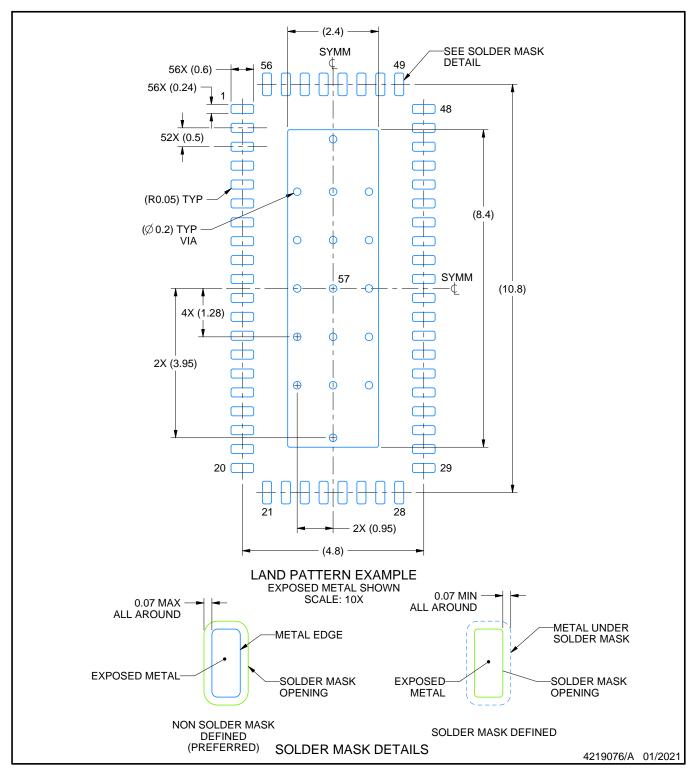

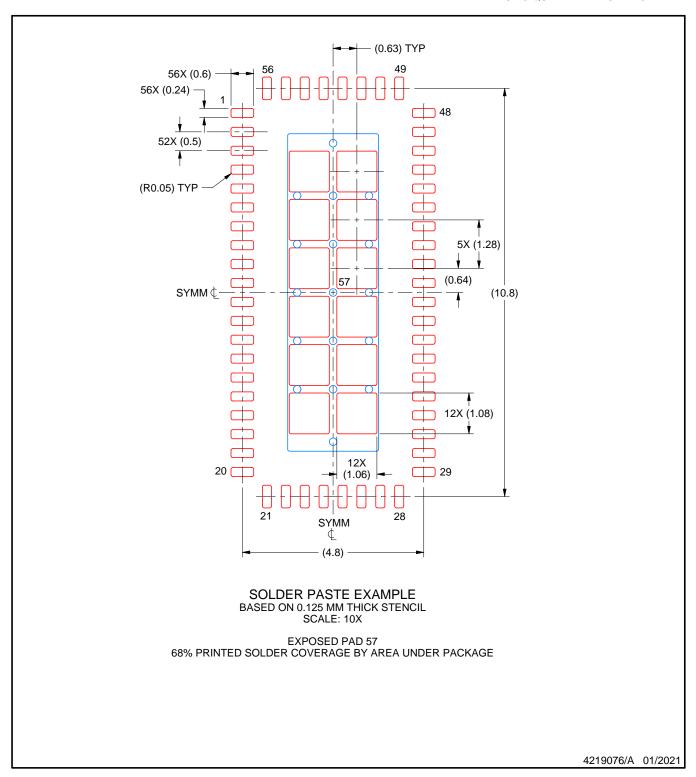

| 7.3 Recommended Operating Conditions                        |                | 11.3 Recommended Package Footprint      |                 |

| 7.4 Thermal Information                                     |                | 12 Device and Documentation Support     |                 |

| 7.5 Electrical Characteristics                              | 8              | 12.1 Documentation Support              |                 |

| 7.6 Timing Requirements                                     | 10             | 12.2 接收文档更新通知                           |                 |

| 7.7 Switching Characteristics                               |                | 12.3 支持资源                               | 38              |

| 7.8 Typical Characteristics                                 |                | 12.4 Trademarks                         | 38              |

| 8 Detailed Description                                      |                | 12.5 静电放电警告                             | 38              |

| 8.1 Overview                                                |                | 12.6 术语表                                | 38              |

| 8.2 Functional Block Diagram                                | 13             | 13 Mechanical, Packaging, and Orderable |                 |

| 8.3 Feature Description                                     |                | Information                             | 38              |

| 4 Revision History Changes from Revision B (August 2018) to | Revision       | C (September 2020)                      | Page            |

|                                                             |                |                                         |                 |

|                                                             |                |                                         |                 |

|                                                             |                |                                         |                 |

| Added the recommended foot print for RH                     | U package      |                                         | 37<br>          |

| Changes from Revision A (October 2017) t                    | o Revisior     | n B (August 2018)                       | Page            |

| Changed MOD_SDA[0] pin number from:                         | 16 to: 35      |                                         | 4               |

|   |             |            |              |            | <br> | <br> |

|---|-------------|------------|--------------|------------|------|------|

| • | Changed MOD | SDA[0] pin | number from: | 16 to: 35  | <br> | <br> |

| • | Changed MOD | SDA[1] pin | number from: | 5 to: 48   | <br> | <br> |

| • | Changed MOD | SDA[2] pin | number from: | 48 to: 5   | <br> | <br> |

| • | Changed MOD | SDA[3] pin | number from: | 35 to: 16. | <br> | <br> |

| C | hanges from Revision * (June 2017) to Revision A (October 2017) | Page |

|---|-----------------------------------------------------------------|------|

| • | 将"预告信息"更改为"量产数据"                                                | 1    |

| • | Updated T <sub>POR</sub> (max)                                  | 10   |

# 5 说明(续)

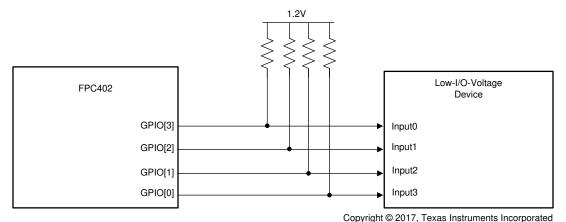

FPC402 能够与标准的 SFF-8431、SFF-8436 和 SFF-8449 低速管理接口(包括连接每个端口的专用 100/400kHz I2C 接口)兼容。该器件还提供有其他通用引脚来驱动端口状态 LED 或控制电源开关。LED 驱动程序器具有便利的功能,例如可编程闪烁和调光功能。连接主机控制器的接口可在 1.8V 至 3.3V 的单独电源电压下运行,以支持低压 I/O。

FPC402 可以从每个模块中用户指定的寄存器中预取数据,这样方便主机通过一个快速 I2C(速度高达 1MHz)或 SPI(速度高达 10MHz)接口来访问数据。此外,当发生与受控端口相关联的用户可配置关键事件时,FPC402 还可以触发主机中断。这样一来,便无需再持续轮询模块。

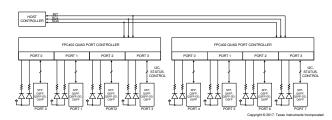

# **6 Pin Configuration and Functions**

图 6-1. RHU Package 56-Pin WQFN Top View

## **Pin Functions**

| PIN  |         | I/O | DESCRIPTION                               |  |

|------|---------|-----|-------------------------------------------|--|

| NAME | AME NO. |     | DESCRIPTION                               |  |

| CAPL | 32      | 0   | Connect a single 2.2-µF capacitor to GND. |  |

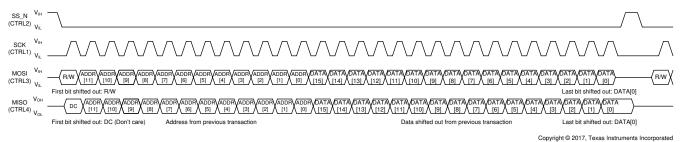

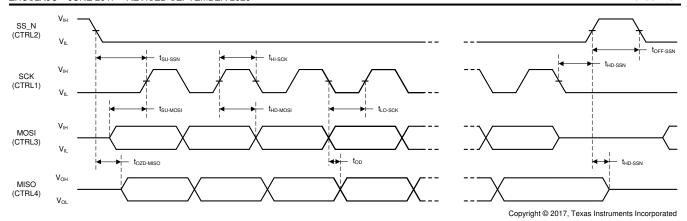

PIN I/O DESCRIPTION NAME NO. CTRL1 23 I/O Host-side control interface. These pins are used to implement I2C or SPI depending on the CTRL2 24 I/O PROTOCOL SEL pin configuration. I2C mode (PROTOCOL\_SEL = Float or High): I. Weak CTRL3 28 internal CTRL1: SCL - I2C Clock input / open-drain output pullup CTRL2: SDA - I2C Data input / open-drain output CTRL3: SET ADDR N - input, address assignment enable. Also used to receive external LED clock. CTRL4: ADDR DONE N - output, address assignment complete. Also used to transmit LED CTRL4 21 0 SPI mode (PROTOCOL SEL = GND): CTRL1: SCK - Serial clock input CTRL2: SS\_N - Active-low slave select input CTRL3: MOSI - Master output or slave input CTRL4: MISO - Master input or slave output Device enable. When EN = 0, the FPC402 is in a power-down state and does not respond to the host-side control bus, nor does it perform port-side I2C accesses. When EN=VDD2 or I, Weak ΕN 22 Float, the FPC402 is fully enabled and will respond to the host-side control bus provided VDD1 internal and VDD2 power has been stable for at least T<sub>POR</sub>. V<sub>IH</sub> for this pin is referenced to VDD2. pullup The minimum required assert and deassert time is 12.5 µs. GPIO[0] 42 GPIO[1] 53 General-purpose I/O. Output high voltage ( $V_{OH}$ ) and input high voltage ( $V_{IH}$ ) are based on I/O VDD1. Configured as input (high-Z) by default. GPIO[2] 8 GPIO[3] 19 Ground reference. The GND pins must be connected through a low-resistance path to the GND 27, DAP Power board GND plane. Open-drain 3.3-V tolerant active-low interrupt output. It asserts low to interrupt the host. O, Open-The events which trigger an interrupt are programmable through registers. This pin can be HOST\_INT\_N 25 Drain connected in a wired-OR fashion with other FPC402s' interrupt pins. A single pullup resistor to VDD1 or VDD2 in the 2-k $\Omega$  to 5-k $\Omega$  range is adequate for the entire net. IN A[0] 41 Low-speed port status input A. Example usage: IN\_A[1] 50 I, Weak internal IN A[2] 55 SFP: Mod ABS[3:0] pullup IN A[3] 10 QSFP: ModPrsL[3:0] IN\_B[0] 39 Low-speed port status input B. IN B[1] 47 Example usage: I. Weak internal IN\_B[2] 1 SFP: Tx Fault[3:0] pullup IN B[3] 12 QSFP: IntL[3:0] IN C[0] 37 Low-speed port status input C. IN C[1] 46 Example usage: I. Weak internal IN\_C[2] 3 SFP: Rx\_LOS[3:0] pullup IN\_C[3] 14 QSFP: N/A

| PIN                      |                   | 1/0                               | DECODINE OF                                                                                                                                                            |  |  |  |

|--------------------------|-------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                     | NO.               | - I/O                             | DESCRIPTION                                                                                                                                                            |  |  |  |

| MOD_SCL[0]               | 36                |                                   |                                                                                                                                                                        |  |  |  |

| MOD_SCL[1]               | 49                | I/O,                              | I2C clock open-drain output to the module. External 2-k $\Omega$ to 5-k $\Omega$ pullup resistor is required.                                                          |  |  |  |

| MOD_SCL[2]               | 4                 | <ul><li>Open-<br/>Drain</li></ul> | This pin is 3.3-V LVCMOS tolerant.                                                                                                                                     |  |  |  |

| MOD_SCL[3]               | 15                |                                   |                                                                                                                                                                        |  |  |  |

| MOD_SDA[0]               | 35                |                                   |                                                                                                                                                                        |  |  |  |

| MOD_SDA[1] 48 I/O, Open- |                   |                                   | C data input or open-drain output to the module. External 2-kΩ to 5-kΩ pullup resistor is                                                                              |  |  |  |

|                          |                   |                                   | required. This pin is 3.3-V LVCMOS tolerant.                                                                                                                           |  |  |  |

| MOD_SDA[3]               | 16                | Diam                              |                                                                                                                                                                        |  |  |  |

| OUT_A[0]                 | 40                |                                   | Low-speed port control output A. OUT_A is disabled by default (high-Z) and when enabled                                                                                |  |  |  |

| OUT_A[1]                 | 44                | 1                                 | drives high logic unless reprogrammed. A 10-kΩ pullup or pulldown resistor is recommended to                                                                           |  |  |  |

| OUT_A[2]                 | 56                |                                   | set a default logic value before this output is enabled. See 节 8.3.3 for more details.                                                                                 |  |  |  |

| 001_/ ([2]               |                   | 0                                 | Example usage:                                                                                                                                                         |  |  |  |

| OLUT AFOI                | 44                |                                   | SFP: Tx_Disable[3:0]                                                                                                                                                   |  |  |  |

| OUT_A[3]                 | 11                |                                   |                                                                                                                                                                        |  |  |  |

|                          | QSFP: ResetL[3:0] |                                   |                                                                                                                                                                        |  |  |  |

| OUT_B[0]                 | 38                |                                   | Low-speed port control output B. Output is disabled by default (high-Z) and when enabled                                                                               |  |  |  |

| OUT_B[1]                 | 45                |                                   | drives low logic unless reprogrammed. A 10-kΩ pullup or pulldown resistor is recommended to                                                                            |  |  |  |

| OUT_B[2]                 | 2                 |                                   | set a default logic value before this output is enabled. See 节 8.3.3 for more details.                                                                                 |  |  |  |

|                          |                   | 0                                 | Example usage:                                                                                                                                                         |  |  |  |

| OUT_B[3] 13              |                   |                                   | SFP: RS[3:0]                                                                                                                                                           |  |  |  |

|                          |                   |                                   | QSFP: LPMode[3:0]                                                                                                                                                      |  |  |  |

| OUT_C[0]                 | 34                |                                   | Low-speed port control output C. Can be used to drive port status LED. Special LED driving                                                                             |  |  |  |

| OUT_C[1]                 | 51                |                                   | features are available on this output. This output is enabled and high logic by default at power                                                                       |  |  |  |

| OUT_C[2]                 | 6                 | +                                 | up. See 节 8.3.2 for more details.                                                                                                                                      |  |  |  |

| 001_0[2]                 |                   | +                                 | Example usage:                                                                                                                                                         |  |  |  |

|                          |                   | 0                                 | SFP: LED_GRN[3:0]                                                                                                                                                      |  |  |  |

| OUT CI21                 | 47                |                                   |                                                                                                                                                                        |  |  |  |

| OUT_C[3]                 | 17                |                                   | QSFP: LED_GRN[3:0]                                                                                                                                                     |  |  |  |

|                          |                   |                                   | This pin requires a series resistor with a value of at least 33 Ω. The LED current-limiting                                                                            |  |  |  |

|                          |                   |                                   | resistor can serve for this purpose.                                                                                                                                   |  |  |  |

| OUT_D[0]                 | 33                |                                   | Low-speed port control output D. Can be used to drive port status LED. Special LED driving                                                                             |  |  |  |

| OUT_D[1]                 | 52                |                                   | features are available on this output. This output is enabled and high logic by default at power                                                                       |  |  |  |

| OUT_D[2]                 | 7                 |                                   | up. See 节 8.3.2 for more details.  Example usage:                                                                                                                      |  |  |  |

|                          |                   | 0                                 |                                                                                                                                                                        |  |  |  |

|                          |                   |                                   | SFP: LED_YLW[3:0]                                                                                                                                                      |  |  |  |

| OUT_D[3]                 | 18                |                                   | QSFP: N/A                                                                                                                                                              |  |  |  |

|                          |                   |                                   | This pin requires a series resistor with a value of at least 33 $\Omega$ . The LED current-limiting                                                                    |  |  |  |

|                          |                   |                                   | resistor can serve for this purpose.                                                                                                                                   |  |  |  |

|                          |                   | I, Weak                           | Used to select between I2C and SPI host-side control interface.                                                                                                        |  |  |  |

| PROTOCOL_SEL             |                   |                                   |                                                                                                                                                                        |  |  |  |

|                          |                   | pullup                            | GND: Serial Peripheral Interface (SPI)                                                                                                                                 |  |  |  |

|                          |                   |                                   | LED clock synchronization pin for SPI mode only.                                                                                                                       |  |  |  |

|                          |                   |                                   | When using SPI as the host-side control interface (PROTOCOL_SEL=GND), connect all FPC402 SPI_LED_CLK pins together. This ensures LED synchronization across all FPC402 |  |  |  |

| SPI_LED_SYNC             | C 30 I/O          | I/O                               | devices.                                                                                                                                                               |  |  |  |

|                          |                   |                                   | When using I2C as the host-side control interface, this pin can be floating. LED                                                                                       |  |  |  |

|                          |                   |                                   | synchronization is ensured by other means in I2C mode.                                                                                                                 |  |  |  |

|                          | 1                 | 1                                 |                                                                                                                                                                        |  |  |  |

| PIN    |           | I/O                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                |  |  |

|--------|-----------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   |           |                               |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| TEST_N | 29        | I, Weak<br>internal<br>pullup | TI test mode. Float or High: Normal operation GND: TI Test Mode                                                                                                                                                                                                                                                                                            |  |  |

| VDD1   | 9, 43, 54 | Power                         | Main power supply, VDD1 = $3.3 \text{ V} \pm 5\%$ . TI recommends connecting at least one 1- $\mu$ F and one 0.1- $\mu$ F decoupling capacitors per VDD1 pin as close to the pin as possible.                                                                                                                                                              |  |  |

| VDD2   | 20, 26    | Power                         | Power supply for host-side interface I/Os (CTRL[4:1]). VDD2 can be 1.8 V to 3.3 V $\pm$ 5%. If the host-side interface operates at 3.3 V, then VDD1 and VDD2 can be connected to the same 3.3-V $\pm$ 5% supply. TI recommends connecting at least one 1- $\mu$ F and one 0.1- $\mu$ F decoupling capacitors per VDD2 pin as close to the pin as possible. |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                         |                                                      | MIN  | MAX | UNIT |

|-----------------------------------------|------------------------------------------------------|------|-----|------|

| VDD1 <sub>ABSMAX</sub>                  | Supply voltage (VDD1)                                | -0.5 | 5   | V    |

| VDD2 <sub>ABSMAX</sub>                  | Supply voltage (VDD2)                                | -0.5 | 5   | V    |

| VIO <sub>VDD1</sub> , <sub>ABSMAX</sub> | 3.3-V LVCMOS I/O voltage (all pins except CTRL[4:1]) | -0.5 | 5   | V    |

| VIO <sub>VDD2</sub> , <sub>ABSMAX</sub> | VDD2 LVCMOS I/O voltage (CTRL[4:1] pins only)        | -0.5 | 5   | V    |

| T <sub>J</sub> , <sub>ABSMAX</sub>      | Junction temperature                                 |      | 150 | °C   |

| T <sub>stg</sub>                        | Storage temperature                                  | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|        |               |                                                                                | VALUE | UNIT |

|--------|---------------|--------------------------------------------------------------------------------|-------|------|

| V      | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2500 | V    |

| V(ESD) | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1500 | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted).

|                        |                                                                                                                         | MIN   | NOM              | MAX   | UNIT |

|------------------------|-------------------------------------------------------------------------------------------------------------------------|-------|------------------|-------|------|

| VDD1                   | Supply voltage, VDD1 to GND. DC plus AC power should not exceed these limits.                                           | 3.135 | 3.3              | 3.465 | V    |

| VDD2                   | Host-side interface supply voltage, VDD2 to GND. 1.8 to 3.3 V typical. DC plus AC power should not exceed these limits. | 1.71  | 1.8, 2.5,<br>3.3 | 3.465 | V    |

| t <sub>Ramp-VDD1</sub> | VDD1 supply ramp time, from 0 V to 3.135 V                                                                              | 1     |                  |       | ms   |

| t <sub>Ramp-VDD2</sub> | VDD2 supply ramp time, from 0 V to VDD2 – $5\%$                                                                         | 1     |                  |       | ms   |

| T <sub>A</sub>         | Operating ambient temperature                                                                                           | -40   |                  | 85    | °C   |

| TJ                     | Operating junction temperature                                                                                          | -40   |                  | 125   | °C   |

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

## 7.4 Thermal Information

|                       |                                              | FPC402     |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC(1)                            | RHU (WQFN) | UNIT |

|                       |                                              | 56 PINS    |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 30.1       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 13.3       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 6.5        | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.3        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 6.4        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.0        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics

$T_J$  = -40°C to 125°C, VDD1 = 3.3 V ± 5%, VDD2 = 3.3 V ± 5% (unless otherwise noted).

|                         | PARAMETER                                            | TEST CONDITIONS                                                                                                          | MIN           | TYP | MAX   | UNIT |

|-------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------|-----|-------|------|

| POWER                   | SUPPLY                                               |                                                                                                                          |               |     |       |      |

|                         |                                                      | VDD1 = VDD2 = 3.3 V, Outputs<br>sourcing maximum current, OUT_C<br>and OUT_D are OFF (V <sub>out</sub> = High)           |               | 90  | 110   | mW   |

| W <sub>TOTAL</sub>      | Total device power dissipation                       | VDD1 = 3.3 V, VDD2 = 2.5 V, Outputs sourcing maximum current, OUT_C and OUT_D are OFF (V <sub>out</sub> = High)          |               | 100 | 110   |      |

|                         |                                                      | VDD1 = 3.3 V, VDD2 = 1.8 V, Outputs sourcing maximum current, OUT_C and OUT_D are OFF (V <sub>out</sub> = High)          |               | 100 | 120   |      |

|                         |                                                      | VDD1 = VDD2 = 3.3 V, OUT_C and OUT_D are OFF (V <sub>out</sub> = High)                                                   |               | 26  | 31    |      |

| I <sub>VDD1</sub>       | Current consumption for VDD1 supply                  | VDD1 = VDD2 = 2.5 V, OUT_C and OUT_D are OFF (V <sub>out</sub> = High)                                                   |               | 27  | 32    | mA   |

|                         |                                                      | VDD1 = 3.3 V, VDD2 = 1.8 V,<br>OUT_C and OUT_D are OFF (V <sub>out</sub><br>= High)                                      |               | 29  | 34    |      |

| I <sub>VDD2</sub>       | Current consumption for VDD2 supply                  | VDD1 = VDD2 = 3.3 V, Outputs<br>sourcing maximum current, OUT_C<br>and OUT_D are OFF (V <sub>out</sub> = High)           |               | 0.2 | 0.35  |      |

|                         |                                                      | VDD1 = 3.3 V, VDD2 = 2.5 V,<br>Outputs sourcing maximum current,<br>OUT_C and OUT_D are OFF (V <sub>out</sub> =<br>High) |               | 0.1 | 0.3   | mA   |

|                         |                                                      | VDD1 = 3.3 V, VDD2 = 1.8 V,<br>Outputs sourcing maximum current,<br>OUT_C and OUT_D are OFF (V <sub>out</sub> =<br>High) |               | 0.1 | 0.25  |      |

| I <sub>total-idle</sub> | Total device supply current consumption in idle mode |                                                                                                                          |               |     | 6.5   | mA   |

| LVCMOS                  | I/O DC SPECIFICATIONS                                |                                                                                                                          |               |     | 1     |      |

|                         | High level input voltage                             | Applies to IN_A, IN_B, IN_C, PROTOCOL_SEL, and GPI0[3:0]                                                                 | 2             |     | 3.465 |      |

| V <sub>IH</sub>         |                                                      | Applies to EN                                                                                                            | 0.7 ×<br>VDD2 |     | VDD2  | V    |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

$T_{\perp}$  = -40°C to 125°C, VDD1 = 3.3 V ± 5%, VDD2 = 3.3 V ± 5% (unless otherwise noted).

|                     | PARAMETER                                                                                            | TEST CONDITIONS                                                                            | MIN           | TYP | MAX           | UNIT |  |

|---------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------|-----|---------------|------|--|

| V <sub>IL</sub>     | Low level input voltage                                                                              | Applies to IN_A, IN_B, IN_C, PROTOCOL_SEL, GPIO[3:0], and EN                               | -0.3          |     | 0.8           | V    |  |

| .,                  |                                                                                                      | Applies to OUT_A, OUT_B, and GPIO[3:0], I <sub>OH</sub> = –2 mA                            | 2.8           |     | 3.465         | V    |  |

| V <sub>OH</sub>     | High level output voltage                                                                            | Applies to OUT_C and OUT_D, I <sub>OH</sub><br>= –50 μA                                    | 2.5           |     |               | V    |  |

| .1                  | Low level output voltage                                                                             | Applies to OUT_A, OUT_B, and GPIO[3:0], I <sub>OL</sub> = 2 mA                             | GND           |     | 0.4           | V    |  |

| / <sub>OL</sub>     | Low level output voltage                                                                             | Applies to OUT_C and OUT_D, I <sub>OL</sub> = 18 mA                                        | GND           |     | 0.4           | V    |  |

| IH                  | High level input current                                                                             | Applies to IN_A, IN_B, IN_C, and GPIO[3:0]                                                 | -1            |     | 1             | μΑ   |  |

|                     | L L L                                                                                                | Applies to IN_A, IN_B, IN_C                                                                | -220          |     | -170          | ^    |  |

| IL                  | Low level input current                                                                              | Applies to GPIO[3:0]                                                                       | <b>–1</b>     |     | 1             | μA   |  |

| SP-LS               | Pulse width of spikes that are suppressed by FPC402 input deglitch filter on all IN_* low-speed pins | Pulses shorter than min are suppressed, and pulses longer than the max are not suppressed. | 30            |     | 50            | μs   |  |

| DOWNS               | TREAM MASTER I2C ELECTRICAL CH                                                                       | ARACTERISTICS (MOD_SCL AND MO                                                              | DD_SDA)       |     |               |      |  |

| V <sub>OL</sub>     | Low level output voltage                                                                             | I <sub>OL</sub> = 3 mA                                                                     | GND           |     | 0.4           | V    |  |

| / <sub>IL</sub>     | Low level input voltage                                                                              |                                                                                            | -0.3          |     | 1.04          | V    |  |

| / <sub>IH</sub>     | High level input voltage                                                                             |                                                                                            | 2.19          |     | 3.465         | V    |  |

| C <sub>b</sub> (1)  | I2C bus capacitive load                                                                              | 1.6 kΩ pull-up resistor max                                                                |               |     | 200           | pF   |  |

| HOST-SI             | DE I2C ELECTRICAL CHARACTERISTI                                                                      | CS (PROTOCOL_SEL = FLOAT/HIGH                                                              | )             |     |               |      |  |

| V <sub>IH</sub>     | Input high level voltage                                                                             | SDA (CTRL2) and SCL (CTRL1)                                                                | 0.7 ×<br>VDD2 |     | VDD2          | V    |  |

| V <sub>IL</sub>     | Input low level voltage                                                                              | SDA (CTRL2) and SCL (CTRL1)                                                                |               | V   |               | V    |  |

| C <sub>IN</sub> (1) | Input pin capacitance                                                                                | SDA (CTRL2) and SCL (CTRL1)                                                                |               | 0.5 | 1             | pF   |  |

| V <sub>OL</sub>     | Low level output voltage                                                                             | SDA (CTRL2) or SCL (CTRL1), I <sub>OL</sub> = 3 mA                                         | GND           |     | 0.4           | V    |  |

| L                   | IL Leakage current                                                                                   | SDA (CTRL2) or SCL (CTRL1), VIN = VDD2                                                     | -1            |     | 1             | μΑ   |  |

| C <sub>b</sub> (1)  | I2C bus capacitive load                                                                              |                                                                                            |               |     | 550           | pF   |  |

| HOST-SI             | DE SPI ELECTRICAL CHARACTERISTI                                                                      | CS (PROTOCOL_SEL = GND)                                                                    |               |     |               |      |  |

| V <sub>IH</sub>     | Input high level voltage                                                                             | SCK (CTRL1), SS_N (CTRL2), and MOSI (CTRL3)                                                | 0.7 ×<br>VDD2 |     |               | V    |  |

| V <sub>IL</sub>     | Input low level voltage                                                                              | SCK (CTRL1), SS_N (CTRL2), and MOSI (CTRL3)                                                |               |     | 0.3 ×<br>VDD2 | V    |  |

| C <sub>IN</sub> (1) | Input pin capacitance                                                                                | SCK (CTRL1), SS_N (CTRL2), and MOSI (CTRL3)                                                |               | 0.5 |               | pF   |  |

| V <sub>OH</sub>     | High level output voltage                                                                            | MISO (CTRL4) pin, I <sub>OH</sub> = –4 mA                                                  | 0.7 ×<br>VDD2 |     |               | V    |  |

| V <sub>OL</sub>     | Low level output voltage                                                                             | MISO (CTRL4) pin, I <sub>OL</sub> = 4 mA                                                   | GND           |     | 0.4           | V    |  |

|                     |                                                                                                      | MOSI (CTRL3)                                                                               | -220          |     | -170          | μA   |  |

|                     | Leakage current                                                                                      | SCK (CTRL1), SS_N (CTRL2), and                                                             | <b>–1</b>     |     | 1             |      |  |

| lL                  | -                                                                                                    | MISO (CTRL4)                                                                               | -1            |     | '             |      |  |

<sup>(1)</sup> These parameters are not production tested.

# 7.6 Timing Requirements

|                       |                                                                                              |                                                                                                                                                                                                | MIN | NOM                    | MAX  | UNIT |  |

|-----------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|------|------|--|

| GENERAL               | TIMING REQUIREMENTS                                                                          |                                                                                                                                                                                                |     |                        |      |      |  |

| T <sub>POR</sub>      | Internal power-on reset (PoR) time                                                           | Time between stable VDD1 power supply (VDD1 ≥ 3.3V - 5%) and deassertion of internal PoR. The portside and host-side control interfaces (I2C and/or SPI) are not operational during this time. | 30  |                        | 60   | ms   |  |

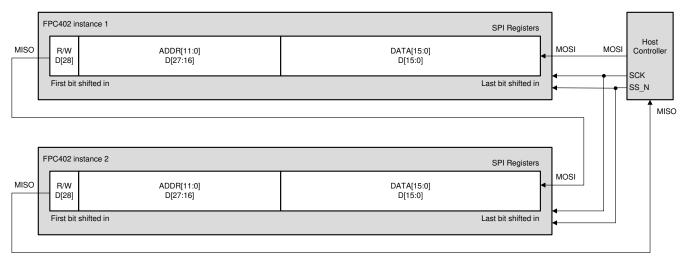

| HOST-SID              | E SPI TIMING REQUIREMENTS (PRO                                                               | TOCOL_SEL = GND) (1) (2)                                                                                                                                                                       |     |                        |      |      |  |

| f <sub>SPI</sub>      |                                                                                              |                                                                                                                                                                                                | 0.1 |                        | 10   | MHz  |  |

| t <sub>HI-SCK</sub>   |                                                                                              |                                                                                                                                                                                                |     | 0.4 ÷ f <sub>SPI</sub> |      | ns   |  |

| t <sub>LO-SCK</sub>   |                                                                                              |                                                                                                                                                                                                |     | 0.4 ÷ f <sub>SPI</sub> |      | ns   |  |

| t <sub>HD-MOSI</sub>  |                                                                                              |                                                                                                                                                                                                |     | 1                      |      | ns   |  |

| t <sub>SU-MOSI</sub>  |                                                                                              |                                                                                                                                                                                                |     | 1                      |      | ns   |  |

| t <sub>HD-SSN</sub>   |                                                                                              |                                                                                                                                                                                                |     | 4                      |      | ns   |  |

| t <sub>SU-SSN</sub>   |                                                                                              |                                                                                                                                                                                                |     | 1.2                    |      | ns   |  |

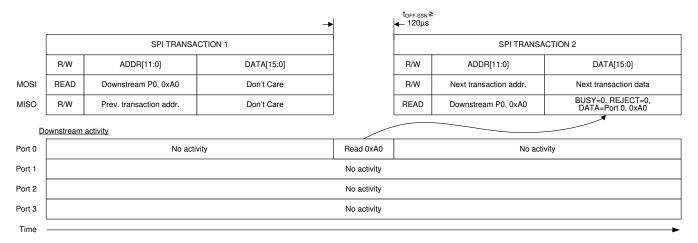

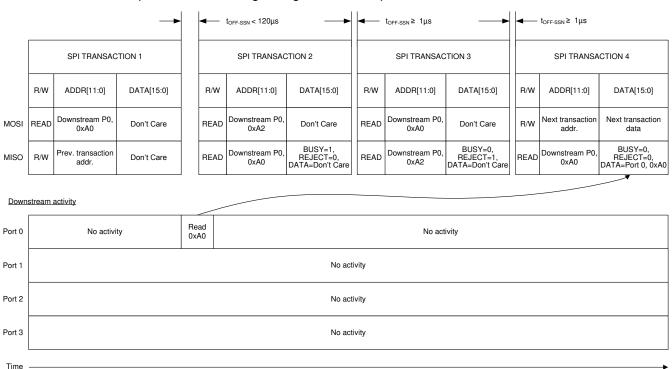

|                       |                                                                                              | For writes and local FPC402 register reads                                                                                                                                                     |     | 1                      |      |      |  |

| t <sub>OFF-SSN</sub>  |                                                                                              | For consecutive downstream (remote) register reads on the same port, assuming 400-KHz I2C                                                                                                      |     | 170                    |      | μs   |  |

|                       |                                                                                              | For consecutive downstream (remote) register reads on the same port, assuming 100-KHz I2C                                                                                                      |     | 620                    |      |      |  |

| t <sub>ODZ-MISO</sub> | MISO (CTRL4) driven-to-TRI_STATE time                                                        |                                                                                                                                                                                                |     | 32                     |      | ns   |  |

| t <sub>OZD-MISO</sub> | MISO (CTRL4) TRI_STATE-to-driven time                                                        |                                                                                                                                                                                                |     | 10                     |      | ns   |  |

| t <sub>OD</sub>       | MISO (CTRL4) output delay time                                                               |                                                                                                                                                                                                |     | 15                     |      | ns   |  |

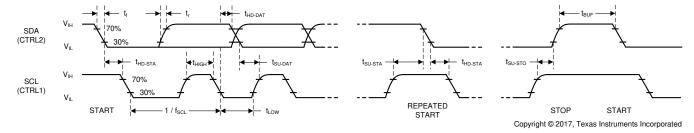

| HOST-SID              | E I2C TIMING REQUIREMENTS (PRO                                                               | TOCOL_SEL = FLOAT OR HIGH)(2) (3)                                                                                                                                                              | (4) |                        |      |      |  |

| f <sub>SCL</sub>      | Host-side I2C clock frequency (CTRL1) in I2C mode                                            |                                                                                                                                                                                                | 100 |                        | 1000 | kHz  |  |

| t <sub>BUF</sub>      | Bus free time between STOP and START condition                                               |                                                                                                                                                                                                | 0.5 |                        |      | μs   |  |

| t <sub>HD-STA</sub>   | Hold time after (repeated) START condition. After this period, the first clock is generated. | After this period, the first clock can be generated by the master.                                                                                                                             | 0.3 |                        |      | μs   |  |

| t <sub>SU-STA</sub>   | Repeated START condition setup time                                                          |                                                                                                                                                                                                | 0.3 |                        |      | μs   |  |

| t <sub>su-sto</sub>   | STOP condition setup time                                                                    |                                                                                                                                                                                                | 0.3 |                        |      | μs   |  |

| t <sub>HD-DAT</sub>   | SDA (CTRL2) hold time                                                                        |                                                                                                                                                                                                | 32  |                        |      | ns   |  |

|                       |                                                                                              | Applies to standard-mode I2C, 100 kHz                                                                                                                                                          | 250 |                        |      | ns   |  |

| t <sub>SU-DAT</sub>   | SDA (CTRL2) setup time                                                                       | Applies to fast-mode I2C, 400 kHz                                                                                                                                                              | 100 |                        |      | ns   |  |

|                       |                                                                                              | Applies to fast-mode plus I2C, 1000 kHz                                                                                                                                                        | 50  |                        |      | ns   |  |

| t <sub>LOW</sub>      | SCL (CTRL1) clock low time                                                                   |                                                                                                                                                                                                | 0.5 |                        |      | μs   |  |

| t <sub>HIGH</sub>     | SCL (CTRL1) clock high time                                                                  |                                                                                                                                                                                                | 0.3 |                        |      | μs   |  |

|                |                             |                                         | MIN | NOM MAX | UNIT |

|----------------|-----------------------------|-----------------------------------------|-----|---------|------|

|                |                             | Applies to standard-mode I2C, 100 kHz   |     | 1000    | ns   |

| t <sub>R</sub> | SDA (CTRL2) rise time, read | Applies to fast-mode I2C, 400 kHz       | 20  | 300     | ns   |

|                |                             | Applies to fast-mode plus I2C, 1000 kHz |     | 120     | ns   |

|                | SDA (CTRL2) fall time, read | Applies to standard-mode I2C, 100 kHz   |     | 300     | ns   |

| t <sub>F</sub> |                             | Applies to fast-mode I2C, 400 kHz       | 4.4 | 300     | ns   |

|                |                             | Applies to fast-mode plus I2C, 1000 kHz | 4.4 | 120     | ns   |

- (1) SPI operation is available T<sub>POR</sub> milliseconds after VDD1 power up, provided EN = high or float and VDD2 is stable.

- (2) These parameters are not production tested.

- (3) I2C operation is available T<sub>POR</sub> milliseconds after VDD1 power up, provided EN = high or float and VDD2 is stable.

- (4) These specifications support I2C Rev 6 specifications

## 7.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                         |                                                                  |                                                                                           | MIN | TYP | MAX | UNIT |  |

|-------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|--|

| DOWNST                  | REAM MASTER I2C SWITCHING CHA                                    | ARACTERISTICS                                                                             |     |     |     |      |  |

| f <sub>SCL</sub>        | SCL clock frequency                                              | Applies to standard-mode I2C, 100 kHz                                                     | 66  | 83  | 100 | kHz  |  |

|                         | , ,                                                              | Applies to fast-mode I2C, 400 kHz                                                         | 264 | 332 | 400 |      |  |

| t <sub>LOW-SCL</sub>    | SCL clock pulse width low period                                 |                                                                                           | 1.3 |     |     | μs   |  |

| t <sub>HIGH-SCL</sub>   | SCL clock pulse width high period                                |                                                                                           | 0.6 |     |     | μs   |  |

| t <sub>BUF</sub>        | Time bus free before new transmission starts                     | Between STOP and START and between ACK and RESTART                                        | 20  |     |     | μs   |  |

| t <sub>HD-STA</sub>     | Hold time START operation                                        |                                                                                           | 0.6 |     |     | μs   |  |

| t <sub>SU-STA</sub>     | Setup time START operation                                       |                                                                                           | 0.6 |     |     | μs   |  |

| t <sub>HD-DAT</sub>     | Data hold time                                                   |                                                                                           | 0   |     |     | μs   |  |

| t <sub>SU-DAT</sub>     | Data setup time                                                  |                                                                                           | 0   |     |     | μs   |  |

|                         | SCL and SDA rise time                                            | 100-KHz operation. From V <sub>IL</sub> (Max) – 0.15 V to V <sub>IH</sub> (Min) + 0.15 V. |     |     | 300 |      |  |

| t <sub>R</sub>          |                                                                  | 100-KHz operation. From V <sub>IL</sub> (Max) – 0.15 V to V <sub>IH</sub> (Min) + 0.15 V. |     |     | 300 | ns   |  |

|                         | COL and CDA fall time                                            | 100-KHz operation. From V <sub>IH</sub> (Min) + 0.15 V to V <sub>IL</sub> (Max) – 0.15 V. |     |     | 300 |      |  |

| t <sub>F</sub>          | SCL and SDA fall time                                            | 400-KHz operation. From $V_{IH}$ (Min) + 0.15 V to $V_{IL}$ (Max) – 0.15 V.               |     |     | 300 | ns   |  |

| t <sub>SU-STO</sub>     | STOP condition setup time                                        |                                                                                           | 0.6 |     |     | μs   |  |

| t <sub>SP-I2C</sub> (1) | Pulse width of spikes that are suppressed by FPC402 input filter |                                                                                           | 0   |     | 50  | ns   |  |

(1) These parameters are not production tested.

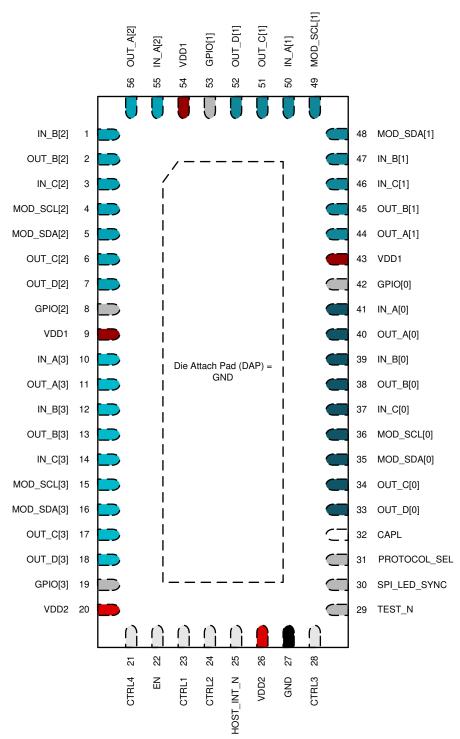

## 7.8 Typical Characteristics

## **8 Detailed Description**

### 8.1 Overview

The FPC402 is designed to interface with four ports and aggregate the I2C and low-speed control and status signals associated with these ports into a single host-side interface (I2C or SPI). Multiple FPC402s can be combined to support up to 56 total ports, all of which are controlled via the same host-side interface. This greatly reduces the number of signals which route to the host controller, saving valuable I/O resources, board routing space, and bill of materials (BOM) cost.

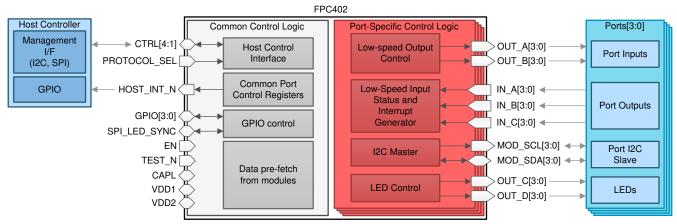

Functionally, the FPC402 is organized as shown in † 8.2. Two types of host-side control interfaces are supported (I2C and SPI) for controlling and monitoring the downstream ports. The FPC402 has two special outputs per downstream port (OUT C and OUT D) which can be used to drive port status LEDs.

## 8.2 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

### 8.3 Feature Description

The features of the FPC402 quad port controller include:

- Host-Side Control Interface

- LED Control

- Low-Speed Output Signal Control

- · Low-Speed Input Status and Interrupt Generation

- Downstream (Port-Side) I2C Master

- Data Prefetch From Modules

- Scheduled Write

- · Protocol Timeouts

- · General-Purpose Inputs and Outputs

- Hot-Plug Support

#### 8.3.1 Host-Side Control Interface

The FPC402 has a single host-side interface which can be configured as one of two available protocols, depending on the pin strap value of the PROTOCOL SEL pin:

- Inter-Integrated Circuit (I2C) up to 1-MHz Fast-mode Plus

- Serial Peripheral Interface (SPI) up to 10 MHz

These represent the two functional modes of operation for which the FPC402 can be configured. Refer to  $\dagger$  8.4 for more details.

#### 8.3.2 LED Control

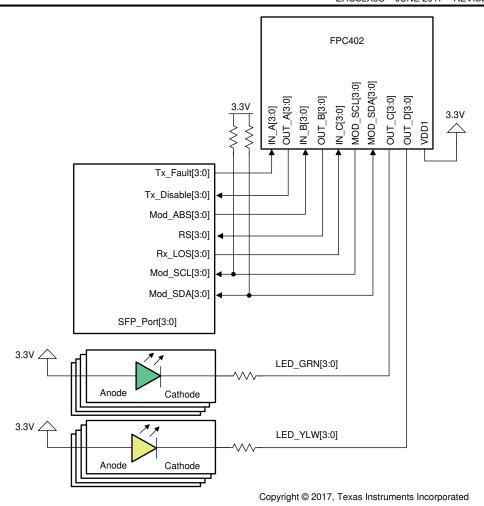

The FPC402 uses two sets of outputs, OUT\_C[3:0] and OUT\_D[3:0], to drive LEDs associated with the ports under its control. Most SFP and QSFP applications use one yellow and one green LED per port to indicate different link status such as link up, link down, and other link states.

LEDs must be connected to the FPC402 in an active-low fashion as shown in  $\[mathbb{R}\]$  8-1 below. When the OUT\_C or OUT\_D pin drives a low voltage (V<sub>OL</sub>), the LED is illuminated. When the OUT\_C or OUT\_D pin drives a high voltage (V<sub>OH</sub>), the LED is off. Bi-color LEDs can be connected in a similar fashion, and each LED must have its own current-limiting resistor. The current-limiting resistor value is selected by choosing the desired maximum current through the LED and the corresponding voltage drop from the LED's current vs. voltage plot. The sum of forward voltage drop of the LED, the voltage drop across the series resistor, and the maximum V<sub>OL</sub> (0.5-V maximum for currents between 2 and 18 mA) is equal to the LED supply voltage. Note that OUT\_C and OUT\_D are tri-stated while the device is held in reset (during POR or while the EN pin is low), and are enabled during normal operation and drive a high voltage by default.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

图 8-1. Example Connection Between OUT\_C/OUT\_D and Active-Low LEDs

Each port controlled by the FPC402 has a set of registers that allow the user to configure each LED into one of the following states:

- ON

- OFF

- PWM (ON with programmable intensity)

- BLINK (with programmable blink duty cycle, frequency, and ON intensity)

LED blinking is configured by setting an on and an off time. Each of these times is configured separately and have a minimum value of 2.5 ms and a maximum value of 637.5 ms for a maximum blinking period of 1.275 seconds. The pulse width modulation (PWM) duty cycle has 256 settings where 0 is completely off, and 255 is maximum brightness. Note that the PWM is 0 by default and must be configured for the LEDs to be visible in BLINK or PWM modes.

LED blinking can be synchronized across all four ports controlled by the FPC402, and the blinking can be synchronized across all ports in the system. For SPI, cross-device synchronization uses the SPI\_LED\_SYNC pin. One device is configured to forward its internal LED clock to this pin, and all other devices are configured to receive an external LED clock on this pin. For I2C, the first device in the CTRL4 to CTRL3 pin daisy chain is configured to output the internal LED clock to the CTLR4 pin. All other devices are configured to receive an external LED clock from the CTRL3 pin and to output the clock to the CTRL4 pin.

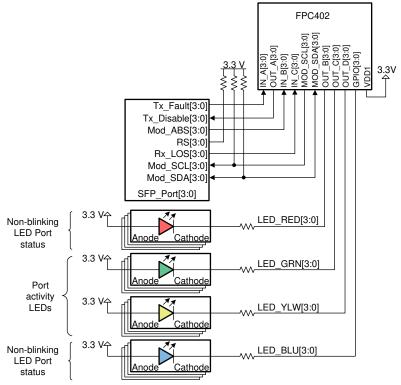

In some applications, it may be desirable to control more than two LEDs per port. In cases where the additional LEDs are relatively static in nature and blinking is not required, the GPIO and OUT\_B pins of the FPC402 can be allocated for driving these LEDs in an active-low configuration. OUT\_C and OUT\_D must be connected to LEDs

requiring blinking, dimming, or both, and up to two additional LEDs can be controlled per port from the GPIO and OUT\_B pins. OUT\_B is optionally used to drive RS0/RS1 in SFP ports or LPMode in QSFP ports. These module pins are often not used in a system and are instead pulled to 3.3 V (SFP) or GND (QSFP). The module functionality affected by these pins is anyway controllable through software. 图 8-2 shows an example of how up to four LEDs can be controlled per port.

Copyright © 2017, Texas Instruments Incorporated

图 8-2. Example Configuration for Driving Four LEDs Per Port

#### 8.3.3 Low-Speed Output Signal Control

The FPC402 has two general-purpose outputs per port which can be used to drive the low-speed inputs to the module. The host controller can change the state of these outputs for each port individually, for all ports connected to a given FPC402 device simultaneously, or for all ports in the system simultaneously.

There are two configuration registers for these outputs. One register configures the enable state of the OUT\_A and OUT\_B pins for every port, and by default both OUT\_A and OUT\_B pins are disabled (tri-stated). The second register controls the output value for all OUT\_A and OUT\_B pins, where OUT\_A has default value of 1 and OUT\_B has a default value of 0. The output values must be configured before the outputs are enabled. If a default value is desired during boot up before these pins are enabled, a  $10\text{-k}\Omega$  pullup or pulldown resistor is recommended (note that SFP and QSFP modules have internal pullup and pulldowns on certain inputs). Note that if the VDD1 rail does not have power and there is an externally powered pullup resistor connected to an output pin, the output pin will be pulled low until VDD1 is supplied.

表 8-1 provides an example signal connection. OUT\_A and OUT\_B are not restricted to this port pin assignment, and they can be used to drive any 3.3-V signal required for the application, provided the  $I_{OH}$  and  $I_{OL}$  limits are met.

表 8-1. Example Connections for Low-Speed FPC402 Outputs to SFP/QSFP ports

| PIN NAME | EXAMPLE CO | COMMENT |         |

|----------|------------|---------|---------|

| PIN NAME | SFP        | QSFP    | COMMENT |

| OUT_A    | Tx_Disable | ResetL  |         |

| 表 8-1. Example Connections for Low-S | peed FPC402 Outputs to | SFP/QSFP ports (continued) |

|--------------------------------------|------------------------|----------------------------|

|                                      |                        |                            |

| PIN NAME | EXAMPLE CO  | COMMENT |                                                    |

|----------|-------------|---------|----------------------------------------------------|

| PIN NAME | SFP         | QSFP    | COMMENT                                            |

| OUT_B    | RS0 and RS1 | LPMode  | RS0 and RS1 will both be driven to the same level. |

### 8.3.4 Low-Speed Input Status and Interrupt Generation

The FPC402 has three general-purpose inputs per port which can be used to monitor the low-speed outputs from the module. The host controller can monitor the status of these signals for each port by reading the appropriate registers in the FPC402. In addition, the FPC402 can be configured to generate an interrupt to the host through the HOST\_INT\_N signal whenever one or more of the low-speed input signals change state. The interrupt can be configured to trigger on the falling edge, the rising edge, or both the falling and rising edges. A single register stores flags for which inputs and edges are responsible for the trigger.

The recommended signal connection is as follows. IN\_A, IN\_B, and IN\_C are not restricted to this port pin assignment, and in fact they can be used to monitor the status of any low-speed 3.3-V signal required for the application.

表 8-2. Example Connections for Low-Speed FPC402 Inputs to SFP/QSFP ports

| PIN NAME | EXAMPLE CO | COMMENT |                                                                                            |

|----------|------------|---------|--------------------------------------------------------------------------------------------|

| FIN NAME | SFP        | QSFP    | COMMENT                                                                                    |

| IN_A     | Tx_Fault   | IntL    |                                                                                            |

| IN_B     | Mod_ABS    | ModPrsL |                                                                                            |

| IN_C     | Rx_LOS     | _       | This pin is unused in QSFP applications, or it can be utilized as a general-purpose input. |

The events which trigger an active-low interrupt on the HOST\_INT\_N pin are user-configurable. The HOST\_INT\_N pins from multiple FPC402 devices can be connected together in a wired-or fashion. Interrupt generation can be configured as follows:

表 8-3. Host-Side Interrupt Options

| INTERRUPT-TRIGGERING   | PIN(S) MONITORED    | EXAMPLE APPLICATION <sup>(1)</sup>                                                                                                                    |

|------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| EVENT                  | FIN(S) MONTORED     | EXAMIFEE AFFEIGATION                                                                                                                                  |

|                        | IN_A                | Indicates deassertion of port-side interrupt (Tx_Fault or IntL).                                                                                      |

|                        | IN_B                | Indicates that a module has been removed.                                                                                                             |

| Rising edge            | IN_C                | Indicates loss of optical signal (Rx_LOS) for SFP applications.                                                                                       |

|                        | IN_A, IN_B, or IN_C | Indicates deassertion of port-side interrupt, removal of module, or loss of optical signal (Rx_LOS).                                                  |

|                        | IN_A                | Indicates assertion of port-side interrupt (Tx_Fault or IntL).                                                                                        |

|                        | IN_B                | Indicates that a module has been inserted.                                                                                                            |

| Falling edge           | IN_C                | Indicates presence of optical signal (Rx_LOS) for SFP applications.                                                                                   |

|                        | IN_A, IN_B, or IN_C | Indicates assertion of port-side interrupt, insertion of module, or presence of optical signal (Rx_LOS).                                              |

|                        | IN_A                | Indicates assertion or deassertion of port-side interrupt (Tx_Fault or IntL).                                                                         |

|                        | IN_B                | Indicates that a module has been inserted/removed.                                                                                                    |

| Rising or falling edge | IN_C                | Indicates presence or absence of optical signal (Rx_LOS) for SFP applications.                                                                        |

|                        | IN_A, IN_B, or IN_C | Indicates assertion or deassertion of port-side interrupt, the insertion or removal of module, or the presence or absence of optical signal (Rx_LOS). |

<sup>(1)</sup> Example applications assume that IN\_A, IN\_B, and IN\_C are connected to the downstream ports as per the example connection table, 表 8-2.

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

The FPC402 is also able to generate an interrupt based on prefetched data. This is known as a data-driven interrupt. The FPC402 monitors up to four bytes within the prefetched range for each port. For each of the bytes, the register offset address is programmed to a local FPC402 register as well as the enable bit fields which will trigger the interrupt. When one of the enabled bits of the four monitored bytes changes state from a 0 to a 1 and stays a 1 for two consecutive periodic prefetch cycles  $(0\rightarrow 1\rightarrow 1)$ , the interrupt is generated and the periodic prefetch operation is halted. The FPC402 has four port-specific registers which contain the sampled data from the bytes being monitored after the interrupt is triggered. To clear the interrupt, the sampled data register of the trigger source byte is read. The periodic prefetch must be restarted after the interrupt is cleared with an I2C command. Because it takes two periodic prefetch cycles to trigger this interrupt, it may take up to 10 ms for the host to see the trigger after the monitored bit field of the downstream module changes for the fastest periodic prefetch setting.

The FPC402 also has the ability to generate an interrupt if there is a mishap in the downstream I2C bus. The SDA bus and the SCL bus each have timers that will trigger an interrupt if they are held in a low state too long due to excessive clock stretching or a port error. Once the interrupt is triggered, it is cleared by issuing a port reset on the relevant port. These interrupts are known as SCL Stuck and SDA Stuck interrupts and can be configured individually for each port. By default, the SCL Stuck interrupt will trigger after the SCL bus is held low for 35 ms (typical). This value is configurable individually by port. The SDA Stuck interrupt will trigger after the SDA is held low for 1 s (typical). The user may issue a port reset sequence (9 consecutive SCL clock cycles with the last being an I2C stop condition) or module reset to restore the module to a known state.

When a host-side interrupt is triggered, the host must determine the source and cause of the interrupt. The recommended procedure for identifying the source and cause of an interrupt is as follows:

- 1. Read the FPC402 aggregated port interrupt flags of the first FPC402 instance to see which, if any, downstream port triggered the interrupt.

- 2. If this instance of the FPC402 has any aggregated port interrupts flagged, read all of the status registers to determine the source of the interrupt and clear it. If an SCL Stuck or SDA Stuck interrupt is triggered, a port reset must be issued and the periodic prefetch must be restarted. The host may also perform other housekeeping activities based on the interrupt, such as change the state of the LEDs after a module is no longer present.

- 3. Repeat steps 1 and 2 for the next FPC402 instance, until the HOST INT N bus is cleared.

This procedure applies to every FPC402 device which is wire-or'ed to the host-side interrupt signal. The total time required for the host to identify the source and cause of the interrupt for an implementation consisting of N total FPC402s, where all N HOST\_INT\_N outputs are wire-or'ed together, is as follows:

$T_{interrupt}$  = Delay between the IN\_\* pin changing state and the corresponding FPC402 device triggering an interrupt (50 µs maximum).

$T_{read}$  = Time required to read a single register from N FPC402 devices.

For I2C mode,  $T_{read} = (9 \times 4 \times N)/F_{I2C}$ , where  $F_{I2C}$  is the SCL clock frequency.

For SPI mode,  $T_{read}$  = (29 × 2 × N)/ $F_{SPI}$  +  $T_{OFF-SSN}$ , where  $F_{SPI}$  is the SCK clock frequency, and  $T_{OFF-SSN}$  is the SS N off time.

$T_{total} = T_{interrupt} + 4 \times T_{read}$

表 8-4 gives some examples of T<sub>total</sub> for different I2C/SPI frequencies and different values of N.

表 8-4. Example Calculations for Determining the Source and Cause of a Host-Side Interrupt

| F <sub>I2C</sub> | F <sub>SPI</sub>                                               | N                                                                           | T <sub>read</sub> (ms)                                                   | T <sub>total</sub> (ms)                                                                                                                                                                                      |

|------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 100 kHz          | _                                                              | 1                                                                           | 0.36                                                                     | 1.5                                                                                                                                                                                                          |

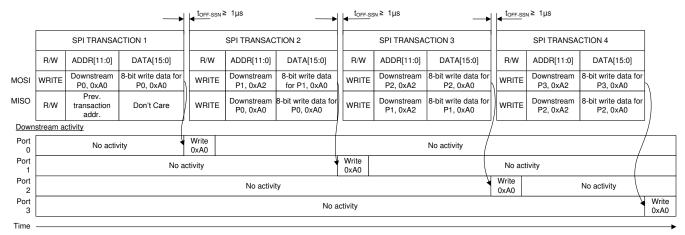

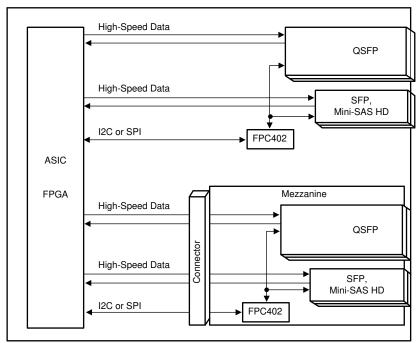

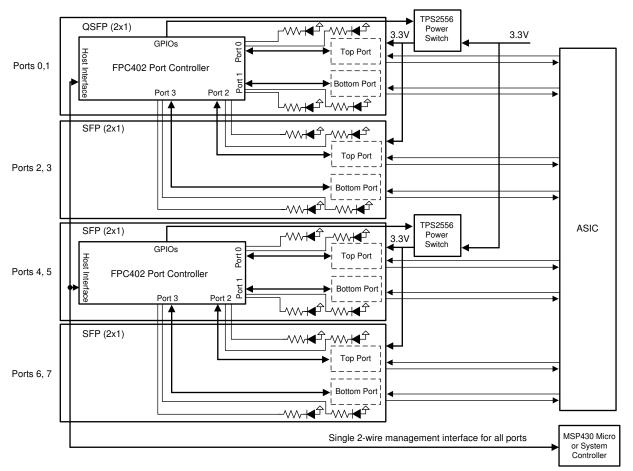

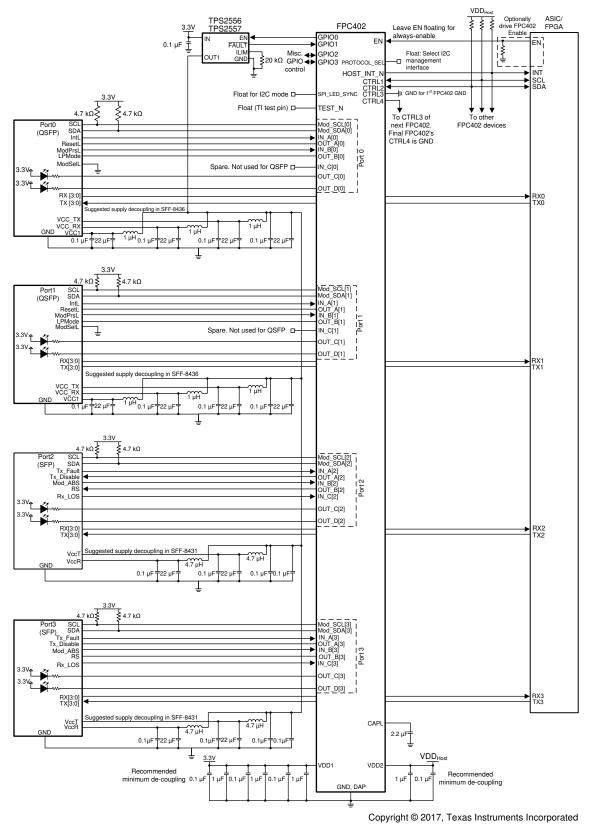

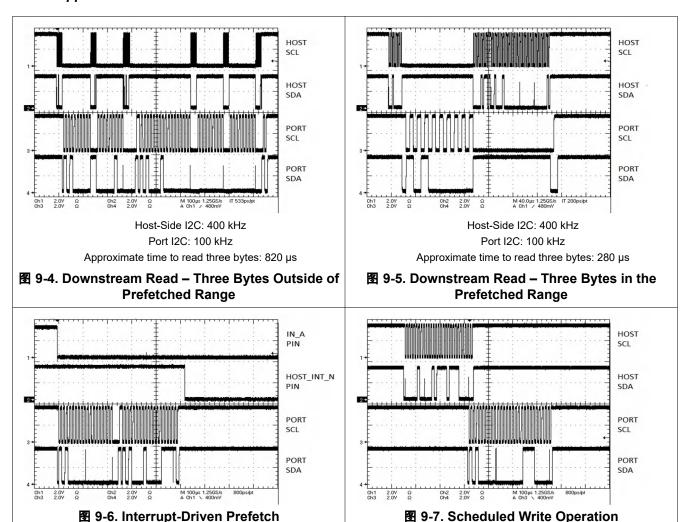

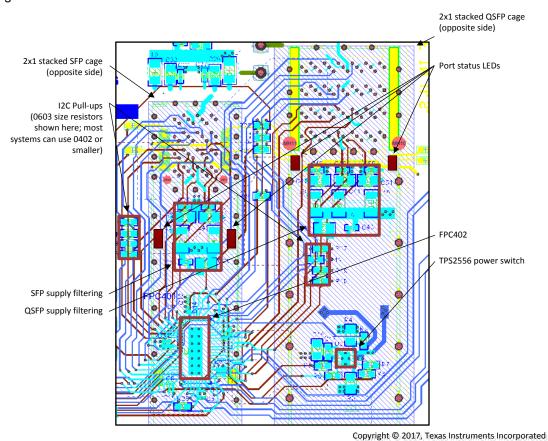

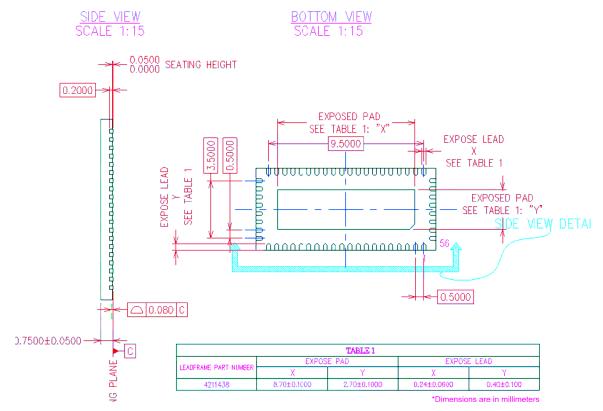

| 100 kHz          | _                                                              | 4                                                                           | 1.44                                                                     | 5.8                                                                                                                                                                                                          |