# LM48413 Boomer<sup>™</sup> Audio Power Amplifier Series Ultra Low EMI, Filterless, 1.2W Stereo Class D Audio Power Amplifier with E<sup>2</sup>S and Texas Instruments 3D Enhancement

Check for Samples: LM48413

#### **FEATURES**

- E<sup>2</sup>S System Reduces EMI Preserving Audio Quality and Efficiency

- Output Short Circuit Protection

- Stereo Class D Operation

- No Output Filter Required

- Texas Instruments 3D Enhancement

- Minimum External Components

- Click and Pop Suppression

- Micro-Power Shutdown

- Available in Space-Saving Approximately 2mm x 2.2mm DSBGA Package

#### **APPLICATIONS**

- Mobile Phones

- PDAs

- Laptops

### **KEY SPECIFICATIONS**

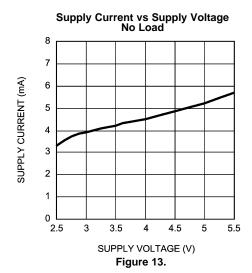

- Quiescent Power Supply Current at 3.6V Supply 4mA (Typ)

- Power Output at V<sub>DD</sub> = 5V, R<sub>L</sub> = 8Ω, THD ≤ 1%

1.2 W (Typ)

- Shutdown Current 0.03µA (Typ)

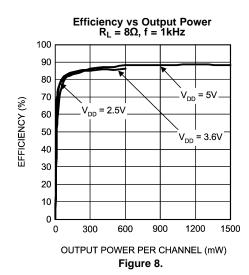

- Efficiency at 3.6V, 100mW into 8Ω 80% (Typ)

- Efficiency at 3.6V, 500mW into 8Ω 80% (Typ)

- Efficiency at 5V, 1W into 8Ω 86% (Typ)

#### DESCRIPTION

The LM48413 is a single supply, high efficiency, 1.2W/channel, filterless switching audio amplifier. The LM48413 features Texas Instruments' Enhanced Emissions Suppression (E²S) system - a unique patented ultra low EMI, spread spectrum, PWM architecture. It significantly reduces RF emission while preserving audio quality and efficiency. The E²S system improves battery life, reduces external component count, board area consumption, system cost and product design cycle time. The LM48413TL is available in a micro-SMD package, further saving space.

The LM48413 is designed to meet the demands of mobile phones and other portable communication devices. Operating from a single 5V supply, the device is capable of delivering 1.2W/channel of continuous output power to a  $8\Omega$  load with less than 1% THD+N. Flexible power supply requirements allow operation from 2.4V to 5.5V. The wide band spread spectrum architecture of the LM48413 reduces EMI-radiated emissions due to the modulator frequency.

The LM48413 features high efficiency compared with conventional Class AB amplifiers. The E²S system includes an advanced, patent-pending edge rate control (ERC) architecture that further reduce emissions by minimizing the high frequency components of the device output, while maintaining its high quality audio reproduction and high efficiency ( $\eta=85\%$  at  $V_{DD}=3.6V,\,P_{O}=500\text{mW}$ ). The LM48413 also includes Texas Instruments' 3D audio enhancement that improves stereo sound quality. In devices where the left and right speakers are in close proximity, 3D enhancement affects channel specialization, widening the perceived soundstage.

Output short circuit protection prevents the device from being damaged during fault conditions. Superior click and pop suppression eliminates audible transients on power up/down and during shutdown. Shutdown control also provided to maximizes power savings.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Boomer is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

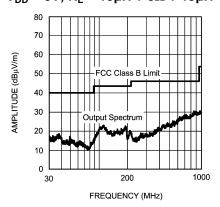

# **EMI Plot Using 6 inch Speaker Cables**

Figure 1. EMI Radiation vs Frequency  $V_{DD}=3V,\,R_L=15\mu H+8\Omega+15\mu H$

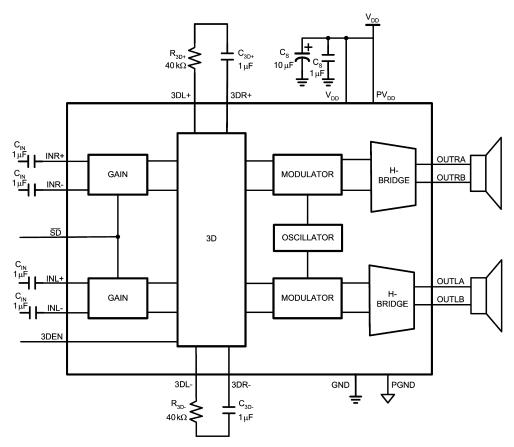

# **Typical Application**

Figure 2. Typical Audio Amplifier Application Circuit

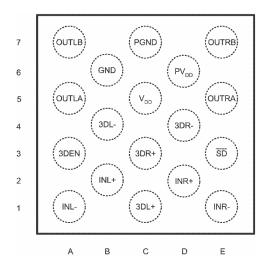

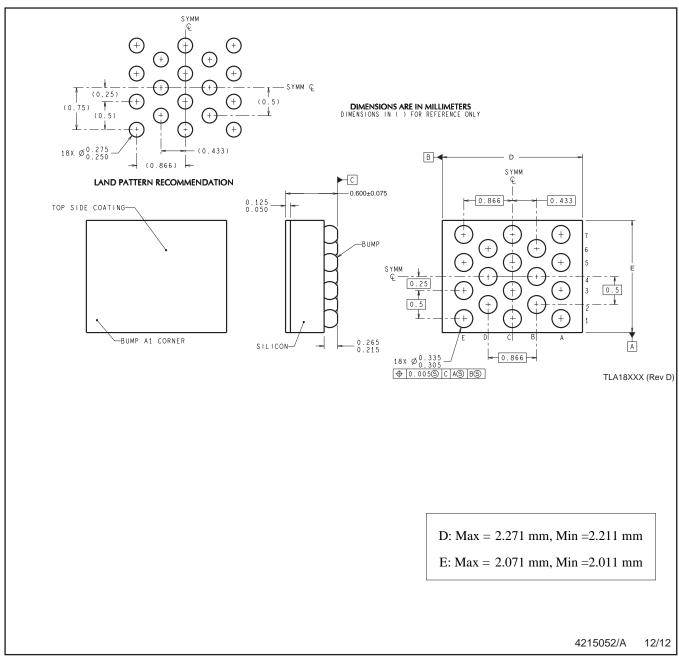

# **Connection Diagram**

Figure 3. 18 bump DSBGA package Top View See Package Number YZR0018

#### **BUMP DESCRIPTIONS**

| Bump | Name      | Description                                                                                              |

|------|-----------|----------------------------------------------------------------------------------------------------------|

| A1   | INL-      | Left Channel Inverting Input                                                                             |

| A3   | 3DEN      | 3D Enable Input                                                                                          |

| A5   | OUTLA     | Left Channel Non-Inverting Output                                                                        |

| A7   | OUTLB     | Left Channel Inverting Output                                                                            |

| B2   | INL+      | Left Channel Non-Inverting Input                                                                         |

| B4   | 3DL-      | Left Channel inverting 3D connection. Connect to 3DR- through C <sub>3D</sub> and R <sub>3D</sub> .      |

| B6   | GND       | Ground                                                                                                   |

| C1   | 3DL+      | Left Channel non-inverting 3D connection. Connect to 3DR+ through C <sub>3D+</sub> and R <sub>3D+</sub>  |

| C3   | 3DR+      | Right Channel non-inverting 3D connection. Connect to 3DL+ through C <sub>3D+</sub> and R <sub>3D+</sub> |

| C5   | $V_{DD}$  | Power Supply. Connect to PV <sub>DD</sub> supplying same voltage.                                        |

| C7   | PGND      | Power Ground                                                                                             |

| D2   | INR+      | Right Channel Non-inverting Input                                                                        |

| D4   | 3DR-      | Right Channel inverting 3D connection. Connect to 3DL- through C <sub>3D</sub> and R <sub>3D</sub> .     |

| D6   | $PV_{DD}$ | Amplifier Power Supply                                                                                   |

| E1   | INR-      | Right Channel Inverting Input                                                                            |

| E3   | SD        | Connect to GND for disabling the device. Connect to V <sub>DD</sub> for normal operation.                |

| E5   | OUTRA     | Right Channel Non-inverting Output                                                                       |

| E7   | OUTRB     | Right Channel Inverting Output                                                                           |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **Absolute Maximum Ratings**(1)(2)(3)

| Supply Voltage <sup>(1)</sup> |                                 | 6.0V            |  |  |  |  |  |

|-------------------------------|---------------------------------|-----------------|--|--|--|--|--|

| Storage Temperature           |                                 | −65°C to +150°C |  |  |  |  |  |

| Input Voltage                 | -0.3V to V <sub>DD</sub> + 0.3V |                 |  |  |  |  |  |

| Power Dissipation (4)         | Internally Limited              |                 |  |  |  |  |  |

| ESD Rating <sup>(5)</sup>     | 2000V                           |                 |  |  |  |  |  |

| ESD Rating <sup>(6)</sup>     |                                 | 200V            |  |  |  |  |  |

| Junction Temperature          |                                 | 150°C           |  |  |  |  |  |

| Thermal Resistance            | $\theta_{JA}$                   | 47°C/W          |  |  |  |  |  |

- (1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified.

- (2) The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (4) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation is P<sub>DMAX</sub> = (T<sub>JMAX</sub> T<sub>A</sub>) / θ<sub>JA</sub> or the number given in *Absolute Maximum Ratings*, whichever is lower.

- (5) Human body model, applicable std. JESD22-A114C.

- (6) Machine model, applicable std. JESD22-A115-A. The ESD Machine Model rating of device bump E3 = 150V.

# Operating Ratings<sup>(1)(2)</sup>

| Tomporatura Banga | $T_{MIN} \le T_A \le T_{MAX}$                        | -40°C ≤ T <sub>A</sub> ≤ 85°C |

|-------------------|------------------------------------------------------|-------------------------------|

| Temperature Range | Supply Voltage (V <sub>DD</sub> , PV <sub>DD</sub> ) | 2.4V ≤ V <sub>DD</sub> ≤ 5.5V |

- (1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditionsindicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified.

- (2) The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

# Electrical Characteristics $V_{DD} = PV_{DD} = 3.6V^{(1)(2)}$

The following specifications apply for  $R_L = 8\Omega^{(3)}$ , f = 1kHz, unless otherwise specified. Limits apply for  $T_A = 25$ °C.

|                   | 3 - 1 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 |                                                                                                                                                                                | LM48       |              |                      |  |  |  |

|-------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|----------------------|--|--|--|

| Symbol            | Parameter                                 | Conditions                                                                                                                                                                     | Typical    | Limit        | Units<br>(Limits)    |  |  |  |

|                   |                                           |                                                                                                                                                                                | (4)        | (5)          |                      |  |  |  |

| Vos               | Differential Output Offset Voltage        | $V_{IN} = 0$ , $V_{DD} = 2.4V$ to 5.0V                                                                                                                                         | 3          |              | mV                   |  |  |  |

| I <sub>DD</sub>   | Quiescent Power Supply Current            | $V_{IN} = 0$ , No Load, $V_{SD} = V_{DD}$ ,<br>$V_{DD} = 3.6V$<br>$V_{DD} = 5V$                                                                                                | 4.3<br>5.2 | 5.5<br>7     | mA (max)<br>mA (max) |  |  |  |

| I <sub>SD</sub>   | Shutdown Current                          | V <sub>SD</sub> = GND                                                                                                                                                          | 0.03       | 1            | μA (max)             |  |  |  |

| V <sub>IH</sub>   | Logic Input High Voltage                  |                                                                                                                                                                                |            | 1.4          | V (min)              |  |  |  |

| V <sub>IL</sub>   | Logic Input Low Voltage                   |                                                                                                                                                                                |            | 0.4          | V (max)              |  |  |  |

| T <sub>WU</sub>   | Wake-Up Time                              |                                                                                                                                                                                | 4          |              | ms                   |  |  |  |

| A <sub>V</sub>    | Gain                                      |                                                                                                                                                                                | 24         | 23.5<br>24.5 | dB (min)<br>dB (max) |  |  |  |

| R <sub>IN</sub>   | Input Resistance                          |                                                                                                                                                                                | 20         |              | kΩ                   |  |  |  |

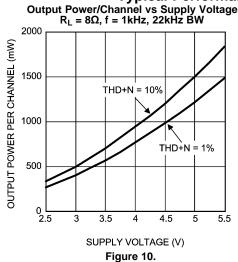

|                   |                                           | THD ≤ 10%, f = 1kHz, 22kHz BW                                                                                                                                                  |            |              |                      |  |  |  |

|                   | Output Power (Per Channel)                | $V_{DD} = 5V$                                                                                                                                                                  | 1.5        |              | W                    |  |  |  |

|                   |                                           | $V_{DD} = 3.6V$                                                                                                                                                                | 720        | 600          | mW (min)             |  |  |  |

| D                 |                                           | $V_{DD} = 2.5V$                                                                                                                                                                | 320        |              | mW                   |  |  |  |

| P <sub>O</sub>    |                                           | THD $\leq$ 1%, f = 1kHz, 22kHz BW                                                                                                                                              |            |              |                      |  |  |  |

|                   |                                           | $V_{DD} = 5V$                                                                                                                                                                  | 1.2        |              | W                    |  |  |  |

|                   |                                           | $V_{DD} = 3.6V$                                                                                                                                                                | 600        |              | mW                   |  |  |  |

|                   |                                           | $V_{DD} = 2.5V$                                                                                                                                                                | 260        |              | mW                   |  |  |  |

| THD+N             | Total Harmonic Distortion + Noise         | $P_O = 500$ mW/Ch, $f = 1$ kHz, 22kHz BW                                                                                                                                       | 0.03       |              | %                    |  |  |  |

| I DD+N            | Total Harmonic Distortion + Noise         | $P_O = 300$ mW/Ch, f = 1kHz,<br>22kHz BW                                                                                                                                       | 0.03       |              | %                    |  |  |  |

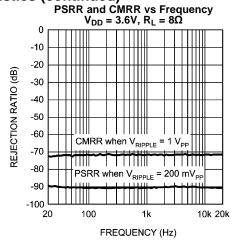

| PSRR              | Power Supply Rejection Ratio              | $V_{RIPPLE} = 200 \text{mV}_{P-P} \text{ Sine,}$<br>Inputs AC GND,<br>$C_{IN} = 1 \mu \text{F, input referred}$<br>$f_{RIPPLE} = 217 \text{Hz}$<br>$f_{RIPPLE} = 1 \text{KHz}$ | 91<br>90   |              | dB<br>dB             |  |  |  |

| CMRR              | Common Mode Rejection Ratio               | $V_{RIPPLE} = 1V_{P-P}$<br>$f_{RIPPLE} = 217Hz$                                                                                                                                | 72         |              | dB                   |  |  |  |

| η                 | Efficiency                                | $P_O = 1W/Ch$ , $f = 1kHz$ ,<br>$R_L = 8\Omega$ , $V_{DD} = 5V$                                                                                                                | 86         |              | %                    |  |  |  |

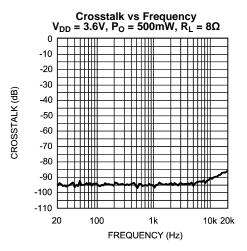

| X <sub>TALK</sub> | Crosstalk                                 | $P_O = 500$ mW/Ch, $f = 1$ kHz                                                                                                                                                 | 93         |              | dB                   |  |  |  |

| SNR               | Signal-to-Noise Ratio                     | V <sub>DD</sub> = 5V, P <sub>O</sub> = 1W                                                                                                                                      | 88         |              | dB                   |  |  |  |

| ε <sub>OS</sub>   | Output Noise                              | Input referred, A-Weighted                                                                                                                                                     | 5          |              | μV                   |  |  |  |

<sup>&</sup>quot;Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified.

The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

$R_L$  is a resistive load in series with two inductors to simulate an actual speaker load. For  $R_L = 8\Omega$ , the load is  $15\mu H + 8\Omega + 15\mu H$ . Typical values represent most likely parametric norms at  $T_A = +25^{\circ}C$ , and at the *Recommended Operation Conditions* at the time of product characterization and are not ensured.

Datasheet min/max specification limits are ensured by test or statistical analysis.

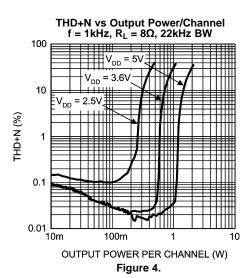

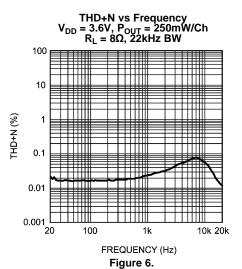

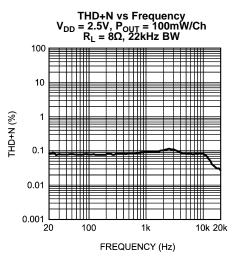

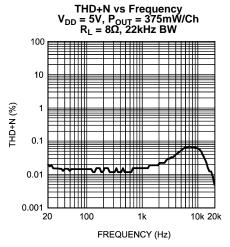

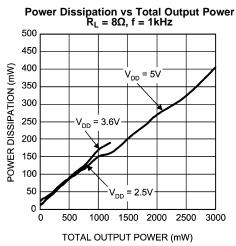

# **Typical Performance Characteristics**

Figure 5.

Figure 7.

Figure 9.

# Typical Performance Characteristics (continued)

Figure 11.

Figure 12.

Figure 16.

#### APPLICATION INFORMATION

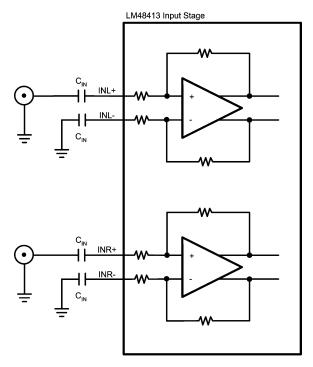

#### **GENERAL AMPLIFIER FUNCTION**

The LM48413 stereo Class D audio power amplifier features a filterless modulation scheme that reduces external component count, conserving board space and reducing system cost. The outputs of the device transition from  $PV_{DD}$  to GND with a 390kHz switching frequency. With no signal applied, the outputs switch with a 50% duty cycle, in phase, causing the two outputs to cancel. This cancellation results in no net voltage across the speaker, thus there is no current to the load in the idle state.

When an input signal is applied, the duty cycle (pulse width) of the LM48413 output's change. For increasing output voltage, the duty cycle of one side of each output increases, while the duty cycle of the other side of each output decreases. For decreasing output voltages, the converse occurs. The difference between the two pulse widths yields the differential output voltage.

#### SHUTDOWN FUNCTION

The LM48413 features a low current shutdown mode. Set  $\overline{SD} = GND$  to disable the amplifier and reduce supply current to  $0.03\mu A$ .

Switch  $\overline{SD}$  between GND and  $V_{DD}$  for minimum current consumption in shutdown. The LM48413 may be disabled with shutdown voltages in between GND and  $V_{DD}$ , but the idle current will be greater than the typical value. The LM48413 shutdown input has an internal  $300k\Omega$  pull-down resistor. The purpose of this resistor is to eliminate any unwanted state changes when this pin is floating. To minimize shutdown current, it should be driven to GND or left floating. If it is not driven to GND, or floating, a small increase in shutdown supply current will be noticed.

#### **SPREAD SPECTRUM**

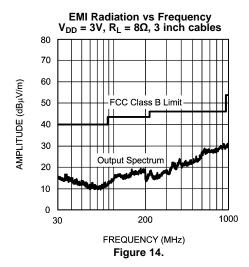

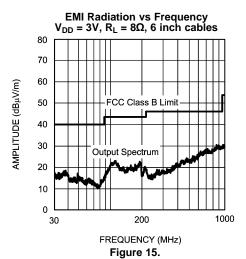

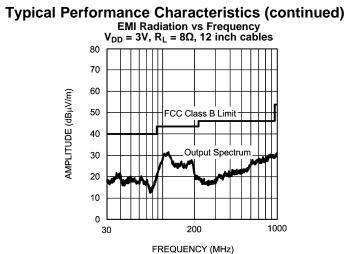

The LM48413 outputs are modulated in spread spectrum scheme eliminating the need for output filters, ferrite beads or chokes. During its operation, the switching frequency varies randomly by 30% about a 390kHz center frequency, reducing the wideband spectral content and improving EMI emissions radiated by the speaker and associated cables and traces. A fixed frequency class D exhibits large amounts of spectral energy at multiples of the switching frequency. The spread spectrum architecture of the LM48413 spreads the same energy over a larger bandwidth. The cycle-to-cycle variation of the switching period does not affect the audio reproduction, efficiency, or PSRR.

#### ENHANCED EMISSIONS SUPPRESSION SYSTEM (E<sup>2</sup>S)

The LM48413 features Texas Instruments' patented E<sup>2</sup>S system that further reduces EMI, while maintaining high quality audio reproduction and efficiency. The advanced edge rate control (ERC) embedded within the E2S system works simultaneously with the spread spectrum already activated. The LM48413 ERC greatly reduces the high frequency components of the output square waves by controlling the output rise and fall times, slowing the transitions to reduce RF emissions, while maximizing THD+N and efficiency performance.

#### DIFFERENTIAL AMPLIFIER EXPLANATION

As logic supplies continue to shrink, system designers are increasingly turning to differential analog signal handling to preserve signal to noise ratios with restricted voltage swings. The LM48413 features two fully differential speaker amplifiers. A differential amplifier amplifies the difference between the two input signals. Traditional audio power amplifiers have typically offered only single-ended inputs resulting in a 6dB reduction of SNR relative to differential inputs. The LM48413 also offers the possibility of DC input coupling which eliminates the input coupling capacitors. A major benefit of the fully differential amplifier is the improved common mode rejection ratio (CMRR) over single-ended input amplifiers. The increased CMRR of the differential amplifier reduces sensitivity to ground offset related noise injection, especially important in noisy systems.

#### POWER DISSIPATION AND EFFICIENCY

The major benefit of a Class D amplifier is increased efficiency versus a Class AB. The efficiency of the LM48413 is attributed to the region of operation of the transistors in the output stage. The Class D output stage acts as current steering switches, consuming negligible amounts of power compared to a Class AB amplifier. Most of the power loss associated with the output stage is due to the IR loss of the MOSFET on-resistance, along with switching losses due to gate charge.

#### PROPER SELECTION OF EXTERNAL COMPONENTS

#### Power Supply Bypassing/Filtering

Proper power supply bypassing is important for low noise performance and high PSRR. Place the  $1\mu F$  supply bypass capacitor as close to the device as possible. Traditionally, a pair of bypass capacitors with typical value  $0.1\mu F$  and  $10\mu F$  are applied to the supply rail for increasing stability. Nevertheless, these capacitors do not eliminate the need for bypassing of the LM48413 supply pins.

#### Input Capacitor Selection

Input capacitors may be required for some applications, or when the audio source is single-ended. Input capacitors block the DC component of the audio signal, eliminating any conflict between the DC component of the audio source and the bias voltage of the LM48413. The input capacitors create a high-pass filter with the input resistance R<sub>IN</sub>. The -3dB point of the high-pass filter is found using Equation 1 below.

$$f = 1 / 2\pi R_{IN} C_{IN} \quad (Hz)$$

The input capacitors can also be used to remove low frequency content from the audio signal. When the LM48413 is using a single-ended source, power supply noise on the ground is seen as an input signal. Setting the high-pass filter point above the power supply noise frequencies, 217Hz in a GSM phone, for example, filters out the noise such that it is not amplified and heard on the output. Capacitors with a tolerance of 10% or better are recommended for impedance matching and improved CMRR and PSRR.

#### **Texas Instruments 3D Enhancement**

The LM48413 features Texas Instruments' 3D enhancement effect that widens the perceived soundstage of a stereo audio signal. The 3D enhancement increases the apparent stereo channel separation, improving audio reproduction whenever the left and right speakers are too close to one another.

An external RC network shown in Figure 2 is required to enable the 3D effect. Because the LM48413 is a fully differential amplifier, there are two separate RC networks, one for each stereo input pair (INL+ and INR+, and INL- and INR-). Set 3DEN high to enable the 3D effect. Set 3DEN low to disable the 3D effect.

The 3D RC network acts as a high-pass filter. The amount of the 3D effect is set by the  $R_{3D}$  resistor. Decreasing the value of R3D increases the 3D effect. The  $C_{3D}$  capacitor sets the frequency at which the 3D effect occurs. Increasing the value of  $C_{3D}$  decreases the low frequency cutoff point, extending the 3D effect over a wider bandwidth. The low frequency cutoff point is given by Equation 2:

$$f_{3D(-3dB)} = 1 / 2\pi (R_{3D})(C_{3D})$$

(Hz) (2)

Enabling the 3D effect increase the gain by a factor of  $(1+40k\Omega/R_{3D})$ . Setting  $R_{3D}$  to  $40k\Omega$  results in a gain increase of 6dB whenever the 3D effect is enabled. The Equation 2 holds for both differential and single-end configuration. The recommended tolerance of the resistor value and capacitor value of the two RC networks are 5% and 10% respectively. Tolerance out of this range may affect the 3D gain and low frequency cut-off point too much. The desired sound quality of the 3D effect may not be obtained consequently.

#### SINGLE-ENDED AUDIO AMPLIFIER CONFIGURATION

The LM48413 is compatible with single-ended sources. When configured for single-ended inputs, input capacitors must be used to block and DC component at the input of the device. Figure 17 shows the typical single-ended applications circuit.

Figure 17. Single-Ended Circuit Diagram

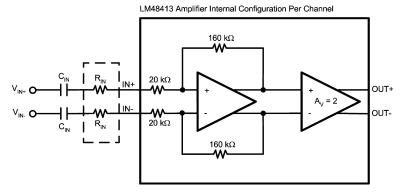

#### **AUDIO AMPLIFIER GAIN**

The LM48413 has a fix gain value 24dB which is suitable for ordinary audio applications. To reduce the amplifier gain, insert two pairs of external input resistors with same value before the IC's input signal pins. Figure 18 show the configuration of these input resistors and the amplifier's internal gain setting. Accordingly, the overall amplifier gain is given by Equation 3:

$$A_V = 2 * (160k) / (20k + R_{IN})$$

(3)

For example, if the gain to be set is 12dB, then  $A_V$  is equal to 4. Thus, Equation 3 the input resistors' value  $R_{IN} = [(2 * 160k)/4] - 20k = 60k\Omega$ .

Figure 18. Audio Amplifier Gain Setting

#### **PCB LAYOUT GUIDELINES**

As output power increases, interconnect resistance (PCB traces and wires) between the amplifier, load and power supply create a voltage drop. The voltage loss due to the traces between the LM48413 and the load results in lower output power and decreased efficiency. Higher trace resistance between the supply and the LM48413 has the same effect as a poorly regulated supply, increasing ripple on the supply line, and reducing peak output power. The effects of residual trace resistance increases as output current increases due to higher output power, decreased load impedance or both. To maintain the highest output voltage swing and corresponding peak output power, the PCB traces that connect the output pins to the load and the supply pins to the power supply should be as wide as possible to minimize trace resistance.

The use of power and ground planes will give the best THD+N performance. In addition to reducing trace resistance, the use of power planes creates parasitic capacitors that help to filter the power supply line.

The inductive nature of the transducer load can also result in overshoot on one or both edges, clamped by the parasitic diodes to GND and  $V_{DD}$  in each case. From an EMI standpoint, this is an aggressive waveform that can radiate or conduct to other components in the system and cause interference. It is essential to keep the power and output traces short and well shielded if possible. Use of ground planes beads and micros-strip layout techniques are all useful in preventing unwanted interference.

As the distance from the LM48413 and the speaker increases, the amount of EMI radiation increases due to the output wires or traces acting as antennas. The EMI output spectrums of LM48413 evaluation board connected with different speaker cable lengths to an  $8\Omega$  load were measured (See Typical Performance Characteristics). Lengths from 3 inches to 12 inches are shown all fall within the limit of the FCC Class B requirement.

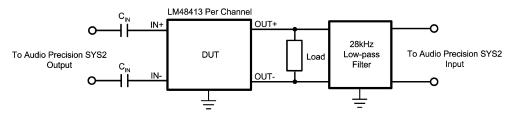

#### THD+N MEASUREMENT

Class D amplifiers, by design, switch their output power devices at a much higher frequency than the accepted audio range (20Hz - 22kHz). Alternately switching the output voltage between  $V_{DD}$  and GND allows the LM48413 to operate at much higher efficiency. However, it also increases the out-of-band noise. Since THD+N measurement is a bandwidth limited measurement, it can be significantly affected by out-of-band noise, resulting in a higher than expected THD+N measurement. To achieve a more accurate measurement of THD+N, the test equipment's input bandwidth must be limited. The input filter limits the out-of-band noise resulting in a more relevant THD+N value. A low-pass filter with a cut-off at 28kHz was used in addition to the internal filter of the THD+N measurement equipment (See Figure 19).

In real applications, the output filters are not necessary since the speakers will act as low-pass filters blocking the remaining switching noise and smoothing the output signals. Instead of connecting the LM48413's BTL outputs to speakers during measurements, the 28kHz low-pass filter is used as shown in Figure 19. This measurement technique also applies to measurements such as PSRR, CMRR, and output power.

Figure 19. THD+N Measurement Test Setup

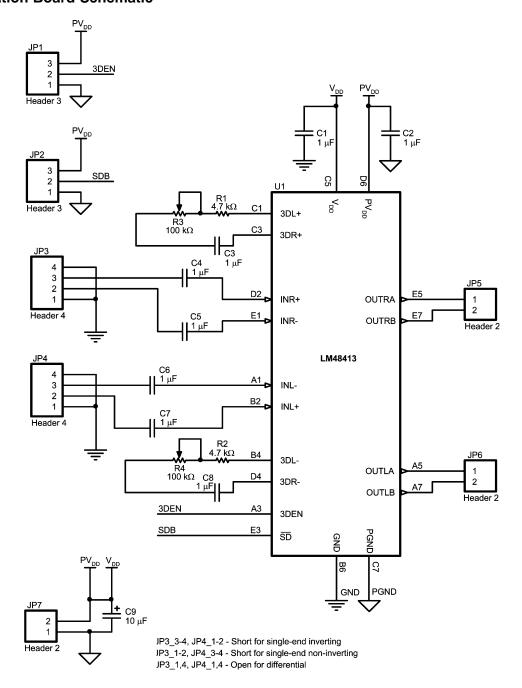

# **Bill Of Materials**

# Table 1. LM48413 Demonstration Board Bill of Materials

| Item | Designator     | Description                     | Part Number        | Qty | Value                    | Recommended<br>Supplier |

|------|----------------|---------------------------------|--------------------|-----|--------------------------|-------------------------|

| 1    | U1             | Stereo Class-D                  | LM48413TL          | 1   |                          | Texas<br>Instruments    |

| 2    | R1, R2         | Resistor (0603)                 |                    | 2   | $4.7$ k $\Omega \pm 5$ % | Towa                    |

| 3    | C1, C2, C3, C8 | Ceramic Capacitor<br>(0603) X7R | GRM188R71C105KA01D | 4   | 1μF ± 10%, 25V           | Murata                  |

| 4    | C4, C5, C6, C7 | Ceramic Capacitor<br>(1206) X7R | C3216X741H105K     | 4   | 1μF ± 10%, 25V           | TDK                     |

| 5    | C9             | Tantium Capacitor (1210)        | 594D106X0025B2T    | 1   | 10μF ± 10%, 25V          | Vishay                  |

| 6    | JP5, JP6, JP7  | Header 2-pin                    |                    | 3   |                          |                         |

| 7    | JP1, JP2       | Header 3-pin                    |                    | 2   |                          |                         |

| 8    | JP3, JP4       | Header 4-pin                    |                    | 2   |                          |                         |

| 9    | R3, R4         | Potentiometer                   | ST-4EB100k         | 2   | 100kΩ                    | Copal Electronics       |

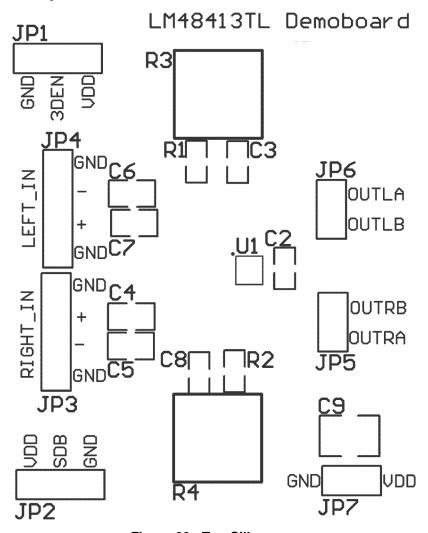

# **Demonstration Board Schematic**

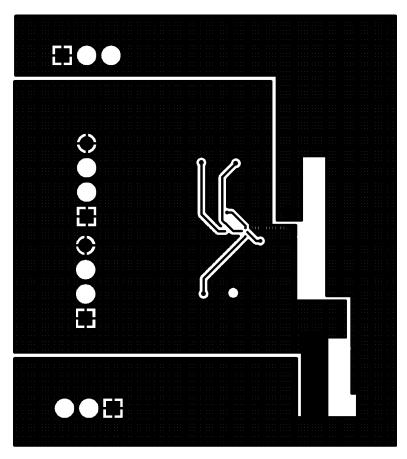

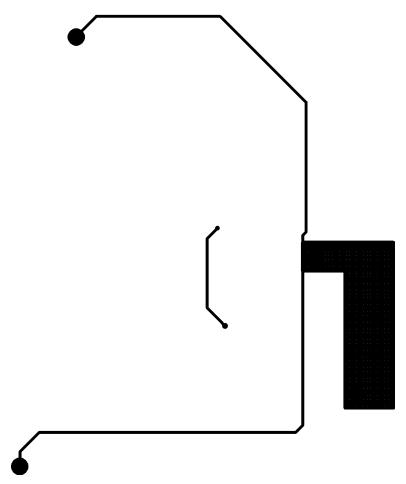

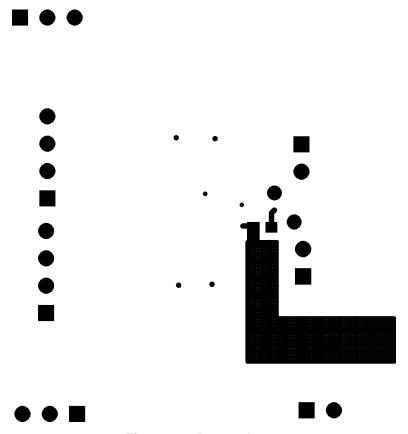

# **Demonstration Board Layout**

Figure 20. Top Silkscreen

Copyright © 2008–2013, Texas Instruments Incorporated

Figure 21. Top Layer

Figure 22. Middle Layer 1

Figure 23. Middle Layer 2

Figure 24. Bottom Layer

# **Revision Table**

| Rev  | Date       | Description                                        |

|------|------------|----------------------------------------------------|

| 1.0  | 11/19/08   | Initial release.                                   |

| 1.01 | 01/08/09   | Text edits.                                        |

| В    | 03/21/2013 | Changed layout of National Data Sheet to TI format |

www.ti.com 23-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|------------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                  |                       |                 | (4)                           | (5)                        |              |                  |

| LM48413TL/NOPB        | Active | Production    | DSBGA (YZR)   18 | 250   SMALL T&R       | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 85    | GL2              |

| LM48413TL/NOPB.A      | Active | Production    | DSBGA (YZR)   18 | 250   SMALL T&R       | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 85    | GL2              |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 1-Nov-2025

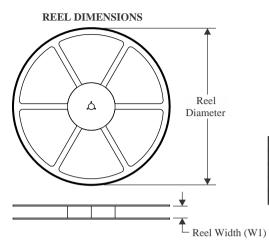

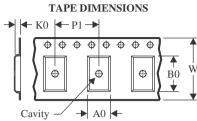

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

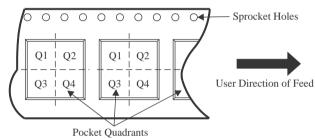

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |    | SPQ | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|----|-----|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM48413TL/NOPB | DSBGA           | YZR                | 18 | 250 | 178.0                    | 8.4                      | 2.29       | 2.59       | 0.76       | 4.0        | 8.0       | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 1-Nov-2025

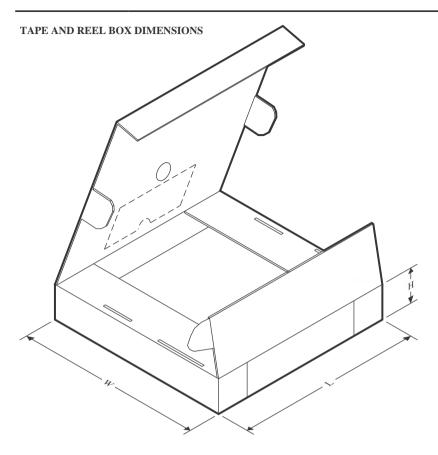

### \*All dimensions are nominal

| Ì | Device         | Package Type | Package Drawing | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |  |

|---|----------------|--------------|-----------------|------|-----|-------------|------------|-------------|--|

| ı | LM48413TL/NOPB | DSBGA        | YZR             | 18   | 250 | 208.0       | 191.0      | 35.0        |  |

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994. B. This drawing is subject to change without notice.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025