# 3 Gbps, HD, SD, DVB-ASI SDI Deserializer with Loopthrough and LVDS Interface

Check for Samples: LMH0041, LMH0051, LMH0071, LMH0341

### **FEATURES**

- 5-Bit LVDS Interface

- No External VCO or Clock Required

- Reclocked Serial Loopthrough With Cable Driver

- Powerdown Mode

- 3.3V SMBus Configuration Interface

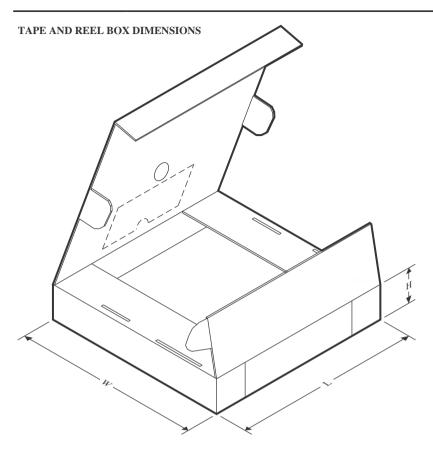

- Small 48-Pin WQFN Package

- Industrial Temperature range: -40°C to +85°C

#### **APPLICATIONS**

- SDI Interfaces for:

- Video Cameras

- DVRs

- Video Switchers

- Video Editing Systems

## **KEY SPECIFICATIONS**

- Output compliant with SMPTE 259M-C, SMPTE 292M, SMPTE 424M and DVB-ASI (See Table 1)

- Typical power dissipation: 590 mW (loopthrough disabled, 3G datarate)

- 0.6 UI Minimum Input Jitter Tolerance

#### DESCRIPTION

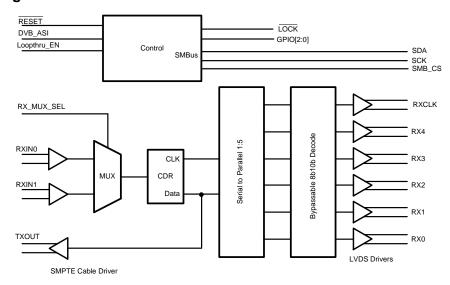

The LMH0341/0041/0071/0051 SDI Deserializers are part of TI's family of FPGA-Attach SER/DES products supporting 5-bit LVDS interfaces with FPGAs. When paired with a host FPGA the LMH0341 automatically detects the incoming data rate and decodes the raw 5-bit data words compliant to any of the following standards: DVB-ASI, SMPTE 259M, SMPTE 292M, or SMPTE 424M. See Table 1 for details on which Standards are supported per device.

The interface between the LMH0341 and the host FPGA consists of a 5-bit wide LVDS bus, an LVDS clock and an SMBus interface. No external VCOs or clocks are required. The LMH0341 CDR detects the frequency from the incoming data stream, generates a clean clock and transmits both clock and data to the host FPGA. The LMH0341, LMH0041 and LMH0071 include a serial reclocked loopthrough with integrated SMPTE compliant cable driver. Refer to Table 1 for a complete listing of single channel deserializers offered in this family.

The FPGA-Attach SER/DES product family is supported by a suite of IP which allows the design engineer to quickly develop video applications using the SER/DES products. The product is packaged in a physically small 48 pin WQFN package.

#### **General Block Diagram**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TRI-STATE is a registered trademark of National Semiconductor Corporation.

All other trademarks are the property of their respective owners.

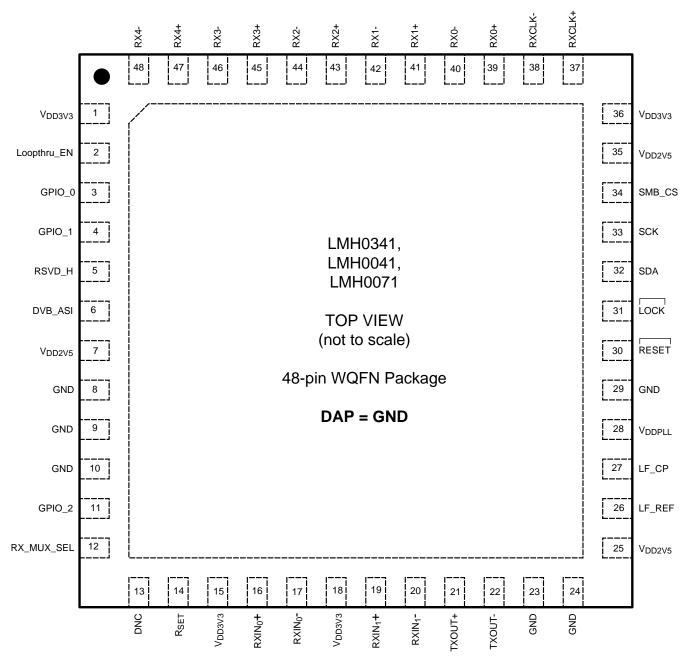

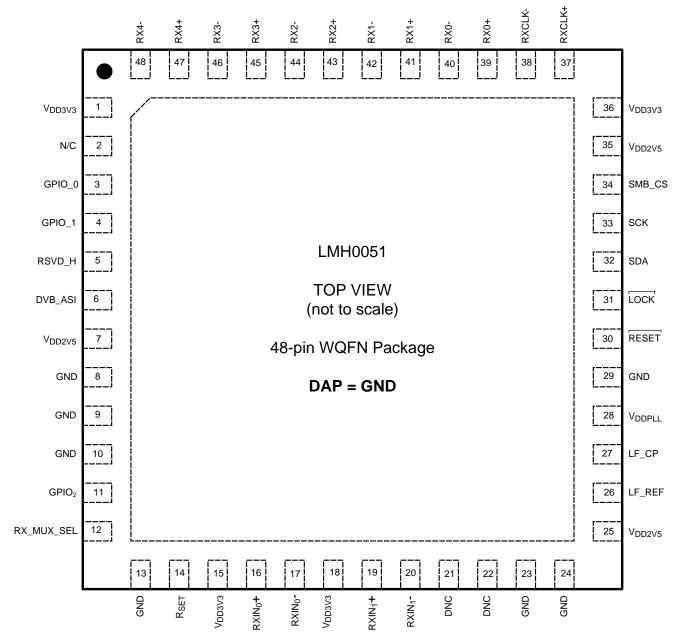

## **Connection Diagrams**

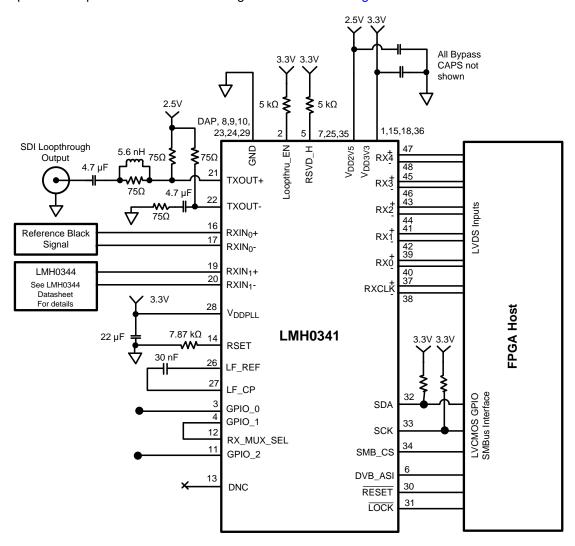

Figure 1. Connection Diagram for LMH0341 / LMH0041 / LMH0071

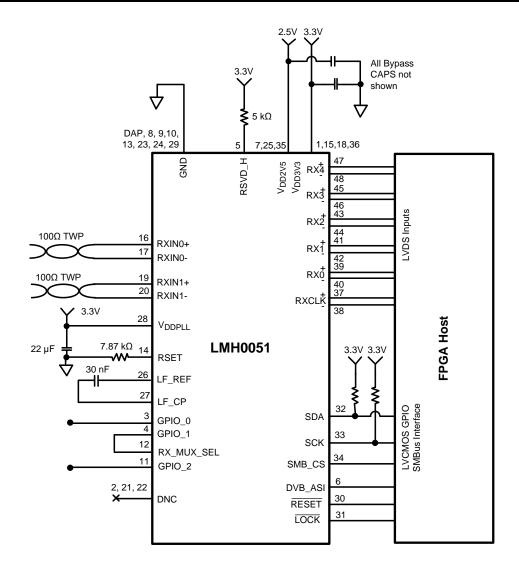

Figure 2. Connection Diagram for LMH0051

### **PIN DESCRIPTIONS**

| PIN DESCRIPTIONS                           |                     |                                                                                                                                                                         |  |  |  |  |

|--------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name                                   | Туре                | Description                                                                                                                                                             |  |  |  |  |

| LVDS Input Interf                          | ace                 |                                                                                                                                                                         |  |  |  |  |

| RX[4:0]+<br>RX[4:0]-                       | Output, LVDS        | LVDS Data Output Pins Five channel wide DDR interface.                                                                                                                  |  |  |  |  |

| RXCLK+<br>RXCLK-                           | Output, LVDS        | LVDS Clock Output Pins DDR Interface.                                                                                                                                   |  |  |  |  |

| Serial Data Inputs                         | S                   |                                                                                                                                                                         |  |  |  |  |

| RXIN <sub>0</sub> +<br>RXIN <sub>0</sub> - | Input, Differential | Serial differential input Pins<br>Channel 0                                                                                                                             |  |  |  |  |

| RXIN <sub>1</sub> +<br>RXIN <sub>1</sub> - | Input, Differential | Serial differential input Pins<br>Channel 1                                                                                                                             |  |  |  |  |

| Loopthrough Ser                            | ial Output          | ·                                                                                                                                                                       |  |  |  |  |

| TXOUT+                                     | Output, CML         | Serial Digital Interface Output Pin<br>Non-Inverting Output                                                                                                             |  |  |  |  |

| TXOUT-                                     | Output, CML         | Serial Digital Interface Output Pin<br>Inverting Output                                                                                                                 |  |  |  |  |

| SMBus Interface                            |                     |                                                                                                                                                                         |  |  |  |  |

| SDA                                        | I/O, LVCMOS         | SMBus Data I/O Pin                                                                                                                                                      |  |  |  |  |

| SCK                                        | Input, LVCMOS       | SMBus Clock Input Pin                                                                                                                                                   |  |  |  |  |

| SMB_CS                                     | Input, LVCMOS       | SMBus Chip Select Input Pin Device is selected when High.                                                                                                               |  |  |  |  |

| Control and Conf                           | iguration Pins      |                                                                                                                                                                         |  |  |  |  |

| RESET                                      | Input, LVCMOS       | Reset Input Pin H = normal mode L = device in RESET                                                                                                                     |  |  |  |  |

| LOCK                                       | Output, LVCMOS      | PLL LOCK Status Output H = unlock condition L = PLL is Locked                                                                                                           |  |  |  |  |

| DVB_ASI                                    | Input, LVCMOS       | DVB_ASI Select Input H = DVB_ASI Mode enabled L = Normal Mode enabled                                                                                                   |  |  |  |  |

| Loopthru_EN                                | Input, LVCMOS       | Loopthrough enable Input H=Reclocked Loopthrogh active L=Reclocked Loopthrough disabled                                                                                 |  |  |  |  |

| RX_MUX_SEL                                 | Input, LVCMOS       | Input multiplexer select H=RXIN <sub>1</sub> selected L=RXIN <sub>0</sub> selected                                                                                      |  |  |  |  |

| GPIO[2:0]                                  | I/O, LVCMOS         | General Purpose Input / Output<br>Software configurable I/O pins.                                                                                                       |  |  |  |  |

| RSVD_H                                     | Input, LVCMOS       | Configuration Input – <b>Must tie High</b> Pull High via 5 k $\Omega$ resistor to $V_{DD3V3}$                                                                           |  |  |  |  |

| Analog Inputs                              |                     |                                                                                                                                                                         |  |  |  |  |

| R <sub>SET</sub>                           | Input               | Serial Loopthrough Output Amplitude Control Resistor connected from this pin to ground to set the signal amplitude. Nominally $7.87k\Omega$ for $800mV$ output (SMPTE). |  |  |  |  |

| LF_CP                                      | Input               | Loop Filter Connection                                                                                                                                                  |  |  |  |  |

| LF_REF                                     |                     | Loop Filter Reference                                                                                                                                                   |  |  |  |  |

| DNC                                        |                     | Do Not Connect – Leave Open                                                                                                                                             |  |  |  |  |

| Power Supply and                           | d Ground            |                                                                                                                                                                         |  |  |  |  |

| V <sub>DD3V3</sub>                         | Power               | 3.3V Power Supply connection                                                                                                                                            |  |  |  |  |

| V <sub>DDPLL</sub>                         | Power               | 3.3V PLL Power Supply connection                                                                                                                                        |  |  |  |  |

| V <sub>DD2V5</sub>                         | Power               | 2.5V Power Supply connection                                                                                                                                            |  |  |  |  |

| GND                                        | Ground              | Ground connection – The DAP (large center pad) is the primary GND connection for the                                                                                    |  |  |  |  |

|                                            | Citatia             | device and must be connected to Ground along with the GND pins.                                                                                                         |  |  |  |  |

## **Table 1. Feature Table**

| Device  | SMPTE 424M<br>Support | SMPTE 292M<br>Support | SMPTE 259M<br>Support | DVB-ASI Support | Active Loopthrough |

|---------|-----------------------|-----------------------|-----------------------|-----------------|--------------------|

| LMH0341 | ×                     | ×                     | ×                     | ×               | ×                  |

| LMH0041 |                       | ×                     | ×                     | ×               | ×                  |

| LMH0071 |                       |                       | ×                     | ×               | ×                  |

| LMH0051 |                       | ×                     | ×                     | ×               |                    |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

**Absolute Maximum Ratings** (1)(2)

| Supply Voltage (V <sub>DD3V3</sub> ) Supply Voltage(V <sub>DD2V5</sub> ) LVCMOS input voltage | -0.3V to +4.0V<br>-0.3V to +3.0V<br>-0.3V to (V <sub>DD3V3</sub> +0.3V) |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| LVCMOS input voltage                                                                          | -0.3V to (V <sub>DD3V3</sub> +0.3V)                                     |

|                                                                                               | . =====                                                                 |

|                                                                                               | 0.01/4= (1/                                                             |

| LVCMOS output voltage                                                                         | $-0.3V$ to $(V_{DD3V3}+0.3V)$                                           |

| SMBus I/O Voltage                                                                             | -0.3V to +3.6V                                                          |

| LVDS Input Voltage                                                                            | 0.3V to 3.6V                                                            |

| Junction Temperature                                                                          | +150°C                                                                  |

| Storage Temperature                                                                           | −65° to 150°C                                                           |

| Lead Temperature—Soldering 4 seconds                                                          | +260°C                                                                  |

| Thermal Resistance— Junction to Ambient—θ <sub>JA</sub>                                       | 26°C/W                                                                  |

| ESD Rating—Human Body Model, 1.5 KΩ, 100 pF                                                   | ≥±8KV                                                                   |

<sup>(1) &</sup>quot;Absolute Maximum Ratings" are the ratings beyond which the safety of the device cannot be ensured. It is not implied that the device will operate up to these limits.

## **Recommended Operating Conditions**

| Parame                                                | ter                               | Min   | Тур  | Max   | Units      |

|-------------------------------------------------------|-----------------------------------|-------|------|-------|------------|

| Supply Voltage (V <sub>DD3V3</sub> -GND)              |                                   | 3.135 | 3.3  | 3.465 | V          |

| Supply Voltage (V <sub>DD2V5</sub> -GND)              |                                   | 2.375 | 2.5  | 2.625 | V          |

| Supply noise amplitude (10 Hz to 50 MHz)              |                                   |       |      | 100   | $mV_{P-P}$ |

| Ambient Temperature                                   |                                   | -40   | +25  | +85   | °C         |

| Case Temperature                                      |                                   |       |      | 102   | °C         |

| Input Data Rate                                       | LMH0341                           | 270   |      |       | Mbps       |

|                                                       | LMH0041                           | 270   |      |       | Mbps       |

|                                                       | LMH0071                           | 270   |      | 270   | Mbps       |

|                                                       | LMH0051                           | 270   |      | 1485  | Mbps       |

| LVDS PCB board trace length (mismatch <2              | %)                                |       |      | 25    | cm         |

| R <sub>STERM</sub> — SMBus termination resistor value |                                   |       | 1000 |       | Ω          |

| Loopthrough Output Driver Pullup Resistor T           | ermination Voltage <sup>(1)</sup> |       | 2.5  | 2.625 | V          |

<sup>(1)</sup> Maximum termination voltage should be identical to the device supply voltage.

<sup>(2)</sup> If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

### **Electrical Characteristics**

Over supply and Operating Temperature ranges unless otherwise specified. (1)

| Symbol             | Parameter                                           | Condition                                          | Min | Тур | Max | Units |

|--------------------|-----------------------------------------------------|----------------------------------------------------|-----|-----|-----|-------|

| I <sub>DD2.5</sub> | 2.5V supply current for LMH0341,<br>LMH041, LMH0071 | 2.97 Gbps<br>LT off                                |     | 67  | 77  | mA    |

|                    |                                                     | 1.485 Gbps<br>LT off <sup>(2)</sup>                |     | 52  | 59  | mA    |

|                    |                                                     | 270 Mbps<br>LT off <sup>(2)</sup>                  |     | 40  | 46  | mA    |

|                    |                                                     | 2.97 Gbps<br>LT on                                 |     | 99  | 108 | mA    |

|                    |                                                     | 1.486 Gbps<br>LT on <sup>(2)</sup>                 |     | 84  | 92  | mA    |

|                    |                                                     | 270 Mbps<br>LT on <sup>(2)</sup>                   |     | 65  | 71  | mA    |

|                    | 2.5V supply current for LMH0051                     | 1.485 Gbps                                         |     | 52  |     | mA    |

|                    |                                                     | 270 Mbps                                           |     | 40  |     | mA    |

| I <sub>DD3.3</sub> | 3.3V supply current for LMH0341,                    | LT off <sup>(2)</sup>                              |     | 106 | 120 | mA    |

|                    | LMH0041, LMH0071                                    | LT on <sup>(2)</sup>                               |     | 112 | 127 | mA    |

|                    | 3.3V supply current for LMH0051                     |                                                    |     | 106 | 119 | mA    |

| P <sub>D</sub>     | Power Consumption                                   | 2.97 Gbps, loopthrough enabled                     |     | 617 | 710 | mW    |

|                    |                                                     | 1.485 Gbps, loopthrough enabled <sup>(2)</sup>     |     | 580 | 670 | mW    |

|                    |                                                     | 270 Mbps, Loopthrough enabled <sup>(2)</sup>       |     | 532 | 620 | mW    |

|                    |                                                     | 2.97 Gbps, Loopthrough Disabled (2)                |     | 517 | 610 | mW    |

|                    |                                                     | 1.485 Gbps, Loopthrough<br>Disabled <sup>(2)</sup> |     | 480 | 560 | mW    |

|                    |                                                     | 270 Mbps, Loopthrough<br>Disabled <sup>(2)</sup>   |     | 450 | 530 | mW    |

- Typical Parameters measured at  $V_{DD}$ =3.3V,  $T_A$ =25°C. They are for reference purposes and are not production tested. Specification ensured by Characterization for LMH0341, other variants production tested

#### **Control Pin Electrical Characteristics**

Over supply and Operating Temperature ranges unless otherwise specified. Applies to DVB\_ASI, RESET and LOCK, GPIO Pins, RX\_MUX\_SEL, Loopthru\_EN(1)

| Symbol          | Parameter                    | Condition                                                                                  | Min  | Тур  | Max                        | Units |

|-----------------|------------------------------|--------------------------------------------------------------------------------------------|------|------|----------------------------|-------|

| V <sub>IH</sub> | High Level Input Voltage     |                                                                                            | 2.0  |      | V <sub>DD3V3</sub><br>+0.3 | V     |

| $V_{IL}$        | Low Level Input Voltage      |                                                                                            | -0.3 |      | 0.8                        | V     |

| V <sub>OH</sub> | High Level Output Voltage    | I <sub>OH</sub> = −0.4 mA                                                                  | 2.7  | 3.25 |                            | V     |

|                 |                              | I <sub>OH</sub> = −2 mA                                                                    | 2.7  | 3.2  |                            | V     |

| $V_{OL}$        | Low Level Output Voltage     | I <sub>OL</sub> = 2 mA                                                                     |      | 0.1  | 0.3                        | V     |

| V <sub>CL</sub> | Input Clamp Voltage          | I <sub>CL</sub> = −18 mA                                                                   |      | 0.9  | -1.5                       | V     |

| I <sub>IN</sub> | Input Current                | V <sub>IN</sub> = 0.4V, 2.5V or V <sub>DD</sub> Pullup and pulldown resistors not enabled. | -40  |      | 40                         | μA    |

| Ios             | Output Short Circuit Current | V <sub>OUT</sub> = 0V                                                                      |      | -44  |                            | mA    |

<sup>(1)</sup> Typical Parameters measured at V<sub>DD</sub>=3.3V, T<sub>A</sub>=25°C. They are for reference purposes and are not production tested.

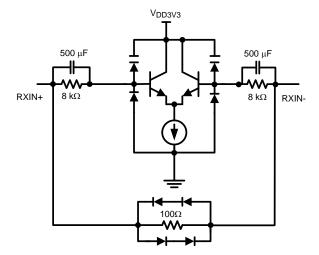

### **SDI Input Electrical Characteristics**

Over supply and Operating Temperature ranges unless otherwise specified. (1)

| Symbol             | Parameter                                    | Condition                                                            | Min  | Тур                                     | Max  | Units                   |

|--------------------|----------------------------------------------|----------------------------------------------------------------------|------|-----------------------------------------|------|-------------------------|

| V <sub>ID</sub>    | Input Differential Voltage                   | DC Coupled, $V_{CM} = 0.05V$ to $V_{DD}$ -0.05V <sup>(2)</sup>       | 230  |                                         | 2200 | mV                      |

| I <sub>IN</sub>    | Input Current                                | 0V < V <sub>IN</sub> < 2.4V                                          | -350 |                                         | 50   | μΑ                      |

| R <sub>IT</sub>    | Input Termination                            |                                                                      | 84   | 100                                     | 116  | Ω                       |

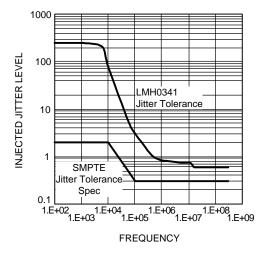

| TOL <sub>JIT</sub> | Input Jitter Tolerance                       | Frequency < f2 (From SMPTE<br>RP 184)                                |      | 6                                       |      | UI                      |

|                    |                                              | Frequency <f3< td=""><td></td><td>0.6</td><td></td><td>UI</td></f3<> |      | 0.6                                     |      | UI                      |

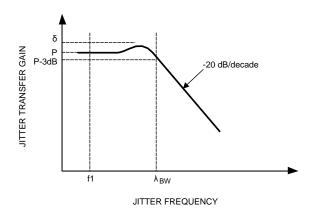

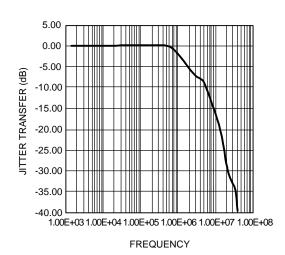

| $\lambda_{BW}$     | Jitter Transfer Function 3 dB loop bandwidth | See Figure 9                                                         |      | 0.13%                                   |      | Fraction of<br>Datarate |

| δ                  | Jitter Peaking                               | See Figure 9                                                         |      | 0.05                                    |      | dB                      |

| RL                 | Input Return Loss                            | Measured on 'ALP' evaluation board (2)                               |      | >25dB to<br>1.5GHz<br>>12dB to<br>3 GHz |      | dB                      |

Typical Parameters measured at  $V_{DD}$ =3.3V,  $T_A$ =25°C. They are for reference purposes and are not production tested. Specification ensured by characterization

## **LVDS Output Electrical Characteristics**

Over supply and Operating Temperature ranges unless otherwise specified. (1)

| Symbol          | Parameter                                                     | Condition                       | Min         | Тур  | Max   | Units |

|-----------------|---------------------------------------------------------------|---------------------------------|-------------|------|-------|-------|

| $V_{OD}$        | Differential Output Voltage                                   | $R_L = 100\Omega$               | 230         |      | 310   | mV    |

| $\Delta V_{OD}$ | Change in V <sub>OD</sub> between complementary output states |                                 |             |      | 35    | mV    |

| V <sub>OS</sub> | Offset Voltage                                                |                                 | 1.125       | 1.25 | 1.375 | V     |

| $\Delta V_{OS}$ | Change in V <sub>OS</sub> between complementary output states |                                 |             |      | 35    | mV    |

| Ios             | Output Short Circuit Current                                  | $V_{OUT} = 0V, R_L = 100\Omega$ | <b>—</b> 50 |      |       | mA    |

<sup>(1)</sup> Typical Parameters measured at  $V_{DD}$ =3.3V,  $T_A$ =25°C. They are for reference purposes and are not production tested.

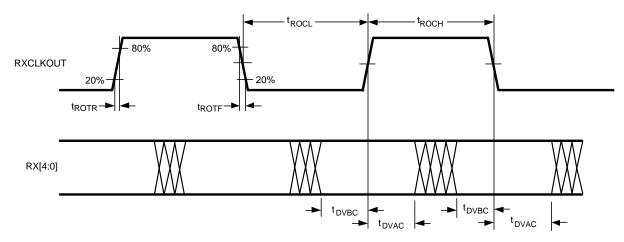

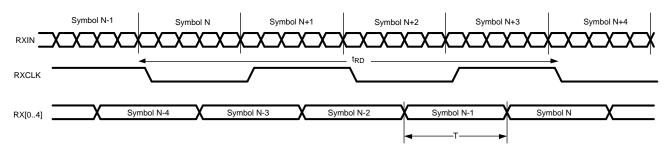

## **LVDS Switching Characteristics**

Over supply and Operating Temperature ranges unless otherwise specified. (1)

| Symbol            | Parameter                              | Condition                                                                                                                | Min  | Тур  | Max | Units |

|-------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|------|-----|-------|

| t <sub>ROTR</sub> | LVDS Low to High Transition time       | See Figure 3 LVDS Switching                                                                                              |      | 300  |     | ps    |

| t <sub>ROTF</sub> | LVDS High to Low Transition time       | times                                                                                                                    |      | 300  |     | ps    |

| t <sub>ROCP</sub> | Receiver output clock period           | RxCLKOUT is DDR. If divide by 4 is enabled, the output clock period will be doubled                                      |      | 2T   |     | ns    |

| t <sub>RODC</sub> | RxCLKOUT Duty Cycle                    |                                                                                                                          | 45   | 50   | 55  | %     |

| t <sub>ROCH</sub> | RxCLKOUT high time                     | See Receiver timing                                                                                                      | 1.51 |      |     | ns    |

| t <sub>ROCL</sub> | RxCLKOUT low time                      | specifications                                                                                                           | 1.51 |      |     | ns    |

| t <sub>RBIT</sub> | Receiver output bit width              |                                                                                                                          |      | Т    |     | ns    |

| t <sub>DVBC</sub> | RX data transition to RXCLK transition | See Receiver timing                                                                                                      | 650  |      |     | ps    |

| t <sub>DVAC</sub> | RXCLK transition to RX data transition | specifications <sup>(2)</sup>                                                                                            | 650  |      |     | ps    |

| t <sub>ROJR</sub> | Receiver output Random Jitter          | Receiver output intrinsic random jitter. Bit error rate ≤ 10 <sup>-15</sup> . Alternating 10 pattern. RMS <sup>(3)</sup> |      | 2.5  |     | ps    |

| t <sub>ROJT</sub> | Peak-to-Peak Receiver Output Jitter    | (3)                                                                                                                      |      | 70   | 125 | ps    |

| t <sub>RD</sub>   | Receiver Propagation Delay             | See Figure 5 Receiver (LVDS Interface) Propagation Delay                                                                 |      | 12 T |     |       |

| t <sub>RLA</sub>  | Receiver Link Acquisition Time         | From device reset or change in input data rate to locked condition                                                       |      |      | 24  | ms    |

| t <sub>LVSK</sub> | LVDS Output Skew                       | LVDS Differential Output Skew between + and - pins                                                                       |      | 20   |     | ps    |

- Typical Parameters measured at  $V_{DD}$ =3.3V,  $T_A$ =25°C. They are for reference purposes and are not production tested. Specification Characterized at 2.97 Gbps, 1.485 Gbps and 270 Mbps, production tested at 270 Mbps only

- Specification ensured by characterization

Figure 3. LVDS Switching Times

## SMBus Input Electrical Characteristics

Over supply and Operating Temperature ranges unless otherwise specified. (1)

| Symbol              | Parameter                          | Condition            | Min   | Тур | Max       | Units |

|---------------------|------------------------------------|----------------------|-------|-----|-----------|-------|

| V <sub>SIL</sub>    | Data, Clock Input Low Voltage      |                      |       |     | 0.8       | V     |

| V <sub>SIH</sub>    | Data, Clock Input High Voltage     |                      | 2.1   |     | $V_{SDD}$ | V     |

| V <sub>SDD</sub>    | Nominal Bus Voltage                |                      | 2.375 |     | 3.465     | V     |

| V <sub>OL</sub>     | Output Low voltage                 | I <sub>OL</sub> =2mA |       |     | 0.3       | V     |

| I <sub>SLEAKB</sub> | Input Leakage per bus segment      | See (2)              | -200  |     | 200       | μΑ    |

| I <sub>SLEAKP</sub> | Input Leakage per pin              | SCK and SDA pins     | -10   |     | 10        | μΑ    |

| C <sub>SI</sub>     | Capacitance for SMBdata and SMBclk | See (2) (3)          |       |     | 10        | pF    |

- Typical Parameters measured at  $V_{DD}$ =3.3V,  $T_A$ =25°C. They are for reference purposes and are not production tested. Recommended value—Parameter is not tested.

- Recommended maximum capacitance load per bus segment is 400 pF.

## **SMBus Switching Characteristics**

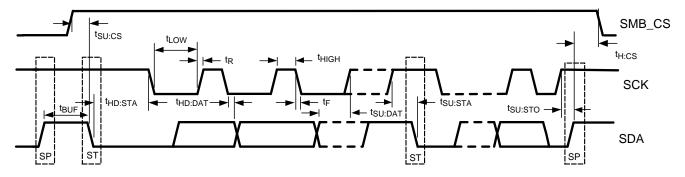

Over supply and Operating Temperature ranges unless otherwise specified. (1)

| Symbol              | Parameter                                                                                   | Condition                     | Min | Тур | Max | Units |

|---------------------|---------------------------------------------------------------------------------------------|-------------------------------|-----|-----|-----|-------|

| f <sub>SMB</sub>    | Bus Operating Frequency                                                                     |                               | 10  |     | 100 | kHz   |

| t <sub>BUF</sub>    | Bus free time between stop and start condition                                              |                               | 4.7 |     |     | μs    |

| t <sub>SU:CS</sub>  | Minimum time between SMB_CS being active and Start condition                                | (2)                           | 30  |     |     | ns    |

| t <sub>H:CS</sub>   | Minimum time between stop condition and releasing SMB_CS                                    | (2)                           | 100 |     |     | ns    |

| t <sub>HD:STA</sub> | Hold time after (repeated) start condition. After this period, the first clock is generated | At I <sub>SPULLUP</sub> = MAX | 4.0 |     |     | μs    |

| t <sub>SU:STA</sub> | Repeated Start condition setup time                                                         |                               | 4.7 |     |     | μs    |

| t <sub>SU:STO</sub> | Stop Condition setup time                                                                   |                               | 4.0 |     |     | μs    |

| t <sub>HD:DAT</sub> | Data hold time                                                                              |                               | 300 |     |     | ns    |

| t <sub>SU:DAT</sub> | Data setup time                                                                             |                               | 250 |     |     | ns    |

| t <sub>LOW</sub>    | Clock Low Period                                                                            |                               | 4.7 |     |     | μs    |

| t <sub>HIGH</sub>   | Clock high time                                                                             |                               | 4.0 |     | 50  | μs    |

| t <sub>POR</sub>    | Time in which a device must be operational after power on                                   |                               |     |     | 500 | ms    |

- Typical Parameters measured at V<sub>DD</sub>=3.3V, T<sub>A</sub>=25°C. They are for reference purposes and are not production tested.

- Specification ensured by characterization

Figure 4. SMBus Timing Parameters

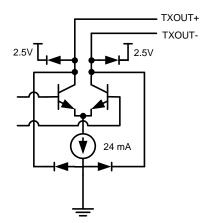

## SDI Output Switching Characteristics (LMH0341 / LMH0041 / LMH0071)

Over supply and Operating Temperature ranges unless otherwise specified. (1)

| Symbol          | Parameter                              | Condition                                 | Min | Тур              | Max  | Units |

|-----------------|----------------------------------------|-------------------------------------------|-----|------------------|------|-------|

|                 | SDI Output Datarate                    |                                           | 270 |                  | 2970 | MHz   |

| t <sub>r</sub>  | SDI Output Rise Time                   | DR=2.97 Gbps <sup>(2)</sup>               |     |                  | 135  | ps    |

|                 |                                        | DR=1.485 Gbps <sup>(2)</sup>              |     |                  | 145  |       |

|                 |                                        | DR=270 Mbps <sup>(2)</sup>                | 400 |                  | 1000 |       |

| t <sub>f</sub>  | SDI Output Fall Time                   | DR=2.97 Gbps <sup>(2)</sup>               |     |                  | 135  | ps    |

|                 |                                        | DR=1.485 Gbps <sup>(2)</sup>              |     |                  | 145  | ps    |

|                 |                                        | DR = 270 Mbps <sup>(2)</sup>              | 400 |                  | 1000 | ps    |

| $\Delta t_t$    | Mismatch between Rise and Fall times   | 2.97 Gbps <sup>(2)</sup>                  |     |                  | 25   | ps    |

|                 |                                        | 1.485 Gbps <sup>(2)</sup>                 |     |                  | 30   | ps    |

|                 |                                        | 270 Mbps <sup>(2)</sup>                   |     |                  | 100  | ps    |

| t <sub>SD</sub> | Propagation Delay Latency              |                                           |     | t <sub>CIP</sub> |      | ns    |

| t <sub>J</sub>  | Peak to Peak Output Jitter             | 2.97 Gbps <sup>(2) (3)</sup>              |     | 25               | 40   |       |

|                 |                                        | 1.485 Gbps <sup>(2) (3)</sup>             |     | 35               | 50   |       |

|                 |                                        | 270 Mbps <sup>(2) (3)</sup>               |     | 65               | 110  |       |

| V <sub>OD</sub> | SDI Output Voltage(Loopthrough Output) | Into 75Ω Load                             | 720 | 800              | 880  | mV    |

| RL              | Output Return Loss                     | Measured 5 MHz to 1483 MHz <sup>(2)</sup> |     | 15               |      | dB    |

| tos             | Output Overshoot                       | (2)                                       |     |                  | 5    | %     |

- (1) Typical Parameters measured at V<sub>DD</sub>=3.3V, T<sub>A</sub>=25°C. They are for reference purposes and are not production tested.

- (2) Specification ensured by characterization

- (3) Measured in accordance with SMPTE RP184.

Figure 5. Receiver (LVDS Interface) Propagation Delay

#### FUNCTIONAL DESCRIPTION

#### **DEVICE OPERATION**

The DES is used in digital video signal origination equipment. It is intended to be operated in conjunction with an FPGA host which processes data received by the SER, and converts the five bit output data to an appropriate parallel video format — usually 10 or 20 bits wide. In most applications, the input data to the DES will be data compliant with DVB ASI, SMPTE 259M-C, SMPTE 292M or SMPTE 424M, and the decoding will be done by the IP provided by TI or similar IP to result in a decoded output. TI offers IP in source code format to perform the appropriate decoding of the data, as well as evaluation platforms to assist in the development of target applications. For more information please contact your local TI Sales Office/Distributor

#### **POWER SUPPLIES**

The DES has several power supply pins, at 2.5V as well as 3.3V. It is important that these pins all be connected, and properly bypassed. Bypassing should consist of parallel  $4.7\mu F$  and  $0.1\mu F$  capacitors as a minimum, with a  $0.1\mu F$  capacitor on each power pin. The device has a large contact in the center of the bottom of the package. This contact must be connected to the system GND as it is the major ground connection for the device. A 22  $\mu F$  capacitor is required on the  $V_{DDPLL}$  pin which is connected to the 3.3V rail

Discrete bypassing is ineffective above 30 MHz to 50 MHz in power plane-based distribution systems. Above this frequency range, the intrinsic capacitance of the power-ground system can be used to provide additional RF bypassing. To make the best use of this, make certain that there are PCB layers dedicated to the Power supplies and to GND, and that they are placed next to each other to provide a distributed capacitance between power and GND.

The DES will work best when powered from linear regulators. The output of linear regulators is generally cleaner with less noise than switching regulators. Output filtering and power system frequency compensation are generally simpler and more effective with linear regulators. Low dropout linear regulators are available which can usually operate from lower input voltages such as logic power supplies, thereby reducing regulator power dissipation. Cascading of low dropout regulators should not be done since this places the entire supply current load of both load systems on the first regulator in the cascade and increases its loading and thermal output.

#### **POWER UP**

The 3.3V power supply should be brought up before the 2.5V supply. The timing of the supply sequencing is not important. The device has a power on reset sequence which takes place once both power supplies are brought up. This sequence will reset all register contents to their default values, and will place the PLLs into link acquisition mode, attempting to lock on the RXINoinput.

#### RESET

There are three ways in which the device may be reset. There is an automatic reset which happens on power-up; there is a reset pin, which when brought low will reset the device, with normal operation resuming when the pin is driven high again. The third way to reset the device is a soft reset, implemented via a write to the reset register. This reset will put all of the register values back to their default values, except it will not affect the address register value if the SMBus default address has been changed.

#### LVDS OUTPUTS

The DES has LVDS outputs, compatible with ANSI/TIA/EIA-644. LVDS outputs expect to drive a  $100\Omega$  transmission line which is properly terminated at the host FPGA inputs. It is recommended that the PCB trace between the FPGA and the receiver be less than 25 cm. Longer PCB traces may introduce signal degradation as well as channel skew which could cause serialization errors.

The LVDS outputs on the DES have a programmable output swing. The default condition is for the smaller size swing, in order to save power. If a larger amplitude output swing is desired, this can be effected through the use of register 0x27h

#### LVDS OUTPUT TIMING

The DES output timing, in it's default condition, is described in LVDS Switching Characteristics. The user has the ability to adjust the LVDS output timing to make it easier to latch into the host FPGA if desired. This is done via register 0x28h where both the clock to data timing may be adjusted, as well as changing the RXCLK from being a DDR clock to a clock at the rate of DDR/2

#### **LOOP FILTER**

The DES has an internal PLL which is used to recover the embedded clock from the input data. The loop filter for this PLL has external components, and for optimum results in Serial Digital Interface applications, a capacitor and a resistor in series should be connected between pins 26 and 27 as shown in the typical interface circuit.

#### **DVB-ASI MODE**

DVB-ASI mode is enabled when the DVB-ASI pin is brought to a high state. When the DVB-ASI mode is enabled, an internal framer and 8b10b decoder is engaged such that the data appearing on RX0-RX3 will represent a nibble of the decoded 8b10b data. RX4 is an Idle character detect and can be used as an enable to allow the receiver to not write data into an external FIFO. RX4 is high if the data being presented on RX0-RX3 represents the idle character. The Least Significant Nibble of data is presented on the rising edge of RXCLK, and the most significant on the falling edge of RXCLK.

The internal 8b10b decoder needs to receive up to 110 consecutive K28.5 characters to properly initialize and frame the data so that the decoded 8b10b data presented at the output of the device is correct.

#### SDI INPUT INTERFACING

The device has two inputs, one of which is selected via a multiplexer with the RX\_MUX\_SEL pin. Whichever input is selected will be routed to the clock recovery portion of the deserializer, and once it is reclocked, the signal will be fed to the loopthrough outputs. Most SDI interfaces require an equalizer to meet performance requirements. For HD-SDI and SD-SDI applications, the LMH0044 is an ideal equalizer to use for this. The LMH0044 is packaged in a small compact package and the outputs can be connected directly to the RXIN inputs of the LMH0041. The LMH0344 is pin compatible with the LMH0044 and will support 3 Gbps data, making it an ideal choice to accompany the LMH0341.

Figure 6. Simplified SDI Input Circuit

### **SWITCHING SDI INPUTS**

When the input to the DES is switched from one source to another, either via the internal 2:1 multiplexor on the inputs, or via an external crosspoint switch, there are a variety of behaviors possible If the input switch is between two signals operating at the same datarate, then in most cases, the DES will not lose lock. There will be a small number of words with corrupted data as the PLL slews it's phase to match the new input signal. Under some circumstances (dependent on phase difference between the inputs, temperature, etc) it is possible that the

PLL will lose lock, and then reacquire lock. This condition can be seen by monitoring the  $\overline{\text{LOCK}}$  pin where a high going pulse will indicate a loss of lock condition. If a loss of lock happens, it will be for a time period of approximately 5ms before lock is reattained. In the invent that the switch on the input is between signals at different datarates — for example from a 270 Mbps signal to a 1.485 Gbps input, then the lock procedure is much more complex, and the lock time will be significantly longer. In either case, the IP that is processing the received signal will need to reestablish the proper framing of the words.

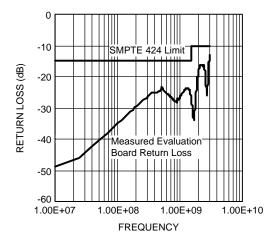

#### SDI OUTPUT INTERFACING

The serial loopthrough outputs provide low-skew complementary or differential signals. The output buffer is a current mode design, and as such has a high impedance output. To drive a  $75\Omega$  transmission line, a  $75\Omega$  resistor from each of the output pins to  $V_{DD2V5}$  should be connected. This resistor has two functions—it converts the current output to a voltage, which is used to drive the cable, and it acts as the back termination resistor for the transmission line. The output driver automatically adjusts its slew rate depending on the input datarate so that it will be in compliance with SMPTE 259M, SMPTE292M or SMPTE 424M as appropriate. In addition to output amplitude and rise/fall time specifications, the SMPTE specs require that SDI outputs meet an Output Return Loss (ORL) specification. There are parasitic capacitances that will be present both at the output pin of the device and on the application printed circuit board. To optimize the return loss, these must be compensated for, usually with a series network comprising a parallel inductor and resistor. The actual values for these components will vary from application to application, but the typical interface circuit shows values that would be a good starting point.

Figure 7. Simplified SDI Output Circuit

#### JITTER MANAGEMENT

SMPTE 424M (the 3 Gbps standard) relaxed the requirements of SDI transmitters from 0.2UI to 0.3UI, which means that the challenge of receiving these signals error free is very difficult. The parameter of importance to determine if the DES will be able to receive the signal error free is the Jitter Tolerance. Figure 10 shows the LMH0341 Jitter tolerance curve with a 2.97 Gbps input — any signal which has less jitter than what is on the upper curve of Figure 10 will be able to be received by the DES. The lower line in the curve shows the SMPTE requirement for any receiver. There is a slight dip in the level at frequencies abive about 10MHz which is an artifact of the test equipment that was used to capture the data. Once the signal is received, the next concern as far as jitter goes is how much of the jitter that was on the input signal will be passed through to the RXCLK output. This is answered by the Jitter transfer characteristics. The Jitter transfer function is the ratio of the input jitter to the output jitter, measured as a function of frequency. The specification tables show two of the parameters related to this curve —  $\delta$  is the jitter peaking and indicates what the maximum gain of the jitter is. Ideally  $\delta$  is 0, but a lower number is better. If several devices are used in a system, and the frequency at which  $\delta$  is maximum is the same for all of them, then the gains will multiply, and there is a risk that there will be excessive jitter accumulating at that frequency. The LMH0341 has very low Jitter peaking, so this should not be a concern. The other parameter of interest is  $\lambda$  which is the jitter transfer bandwidth. Jitter on the input at the

frequency  $\lambda$  is attenuated by 3dB, and any jitter at frequencies greater than  $\lambda$  is attenuated by more than this. From a design standpoint, it means that you primarily only need to worry about the jitter at frequencies below  $\lambda$ . The LMH0341 adjusts it's loop bandwidth dependent on datarate, so for the lower datarates, it has a lower loop bandwidth. Figure 10 shows the jitter transfer curve of an LMH0341 with a 2.97 Gbps signal input, 0.5UI of input jitter, and nominal power supplies and temperature.

Figure 8. Jitter Tolerance Curve

Figure 9. Jitter Transfer Curve Parameters

Figure 10. Jitter Transfer Curve

#### **SMBus INTERFACE**

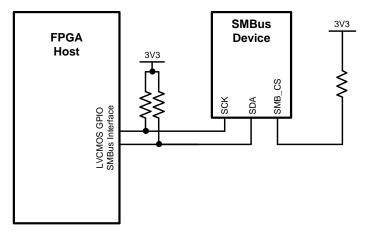

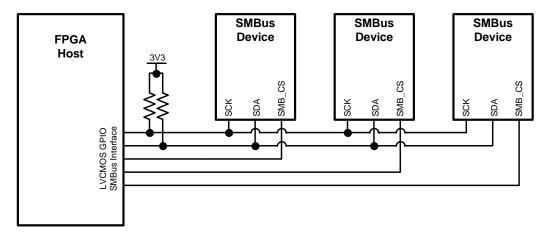

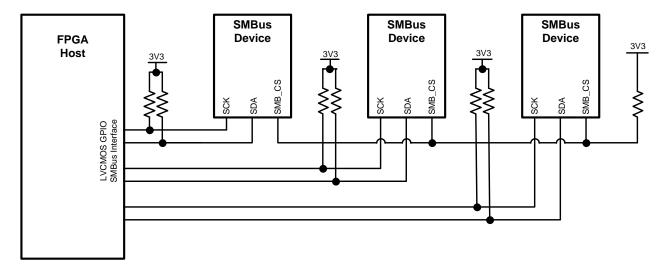

The configuration bus conforms to the System Management Bus (SMBus) 2.0 specification. SMBus 2.0 includes multiple options. The optional ARP (Address Resolution Protocol) feature is not supported. The I/O rail is 3.3V only and is not 5V tolerant. The use of the SMB\_CS signal is recommended for applications with multi-drop applications (multiple devices to a host).

The System Management Bus (SMBus) is a two wire interface designed for the communication between various system component chips. By accessing the control functions of the circuit via the SMBus, pin count is kept to a minimum while allowing a maximum amount of versatility. The SMBus has three pins to control it, there is an SMBus CS pin which enables the SMBus interface for the device, a Clock and a Data line. In applications where there might be several devices, the SDA and SCK pins can be bussed together and the individual devices to be communicated with may be selected via the CS pin The SCL and SDA are both open drain and are pulled high by external pullup resistors. The DES has several internal configuration registers which may be accessed via the SMBus. These registers are listed in Table 2.

#### Transfer Of Data To The Device Via The SMBus

During normal operation the data on SDA must be stable during the time when SCK is high.

START / STOP / IDLE conditions-

There are three unique states for the SMBus:

START A HIGH to LOW transition on SDA while SCK is high indicates a message START condition,

STOP A LOW to HIGH transition on SDA while SCK is high indicates a message STOP condition.

**IDLE** If SCK and SDA are both high for a time exceeding t<sub>BUF</sub> from the last detected STOP condition or if they are high for a total exceeding the maximum specification for t<sub>HIGH</sub> then the bus will transfer to the IDLE state.

#### **SMBus Transactions**

A transaction begins with the host placing the DES SMBus into the START condition, then a byte (8 bits) is transferred, MSB first, followed by a ninth ACK bit. ACK bits are '0' to signify an ACK, or '1' to signify NACK, after this the host holds the SCL line low, and waits for the receiver to raise the SDA line as an ACKnowledge that the byte has been received.

#### WRITING TO REGISTERS VIA THE SMBus INTERFACE

To write a data value to a register in the DES, the host writes three bytes, the first byte is the device address—the device address is a 7 bit value, and if writing to the DES the last bit (LSB) is set to '0' to signify that the operation is a write. The second byte written is the register address, and the third byte written is the data to be written into the addressed register. If additional data writes are performed, the register address is automatically incremented. At the end of the write cycle the host places the bus in the STOP state.

#### READING FROM REGISTERS VIA THE SMBus INTERFACE

To read the data value from a register, first the host writes the device address with the LSB set to a '0' denoting a write, then the register address is written to the device. The host then reasserts the START condition, and writes the device address once again, but this time with the LSB set to a '1' denoting a read, and following this the DES will drive the SDA line with the data from the addressed register. The host indicates that it has finished reading the data by asserting a '1' for the ACK bit. After reading the last byte, the host will assert a '0' for NACK to indicate to the DES that it does not require any more data.

Figure 11. SMBus Configuration 1 — Host to single device

Figure 12. SMBus Configuration 2 — Host to multiple devices with SMB\_CS signals

Figure 13. SMBus Configuration 3 — Host to multiple devices with multiple SMBus Interfaces

## **GENERAL PURPOSE I/O PINS (GPIO)**

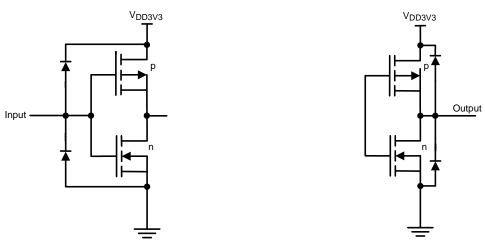

The DES has three pins which can be configured to provide direct access to certain register values via a dedicated pin. For example if a particular application required fast action to the condition of the deserializer losing it's input signal, the PCLK detect status bit could be routed directly to an external pin where it might generate an interrupt for the host processor. GPIO pins can be configured to be in TRI-STATE® (High Impedance) mode, the buffers can be disabled, and when used as inputs can be configured with a pullup resistor, a pulldown resistor or no input pin biasing at all.

Each of the GPIO pins has a register to control it. For each of these registers, the upper 4 bits are used to define what function is desired of the GPIO pin with options being slightly different for each of the three GPIO pins. The pins can be used to monitor the status of various internal states of the LMH0040 device, to serve as an input from some external stimulus, and for output to control some external function.

#### GPIO<sub>0</sub> Functions

- Allow for the output of a signal programmed by the SMBus

- Allow the monitoring of an external signal via the SMBus

- Monitor the status of the signal on input 0

#### GPIO₁ Functions

Monitor Power On Reset

- Allow for the output of a signal programmed by the SMBus

- Allow the monitoring of an external signal via the SMBus Monitor the status of the signal on input 1

- Monitor Lock condition of the input clock recovery PLL

#### GPIO<sub>2</sub> Functions

- Allow for the output of a signal programmed by the SMBus

- · Allow the monitoring of an external signal via the SMBus

- Provides a constant clock signal

- LVDS TX Clock at 1/20 full rate

- CDR Clock at 1/20 full rate

Bits 2 and 3 are used to determine the status of the internal pullup/pulldown resistors on the device—they are loaded according to the following truth table:

- 00: pullup and pulldown disabled

- 01: pulldown enabled

- 10: pullup enabled

- 11: reserved

Bit 1 is used to enable or disable the input buffer. If the GPIO pin is to be used as an output pin, then this bit must be set to a '0' disabling the output.

The LSB is used to switch the output between normal output state and high impedance mode. If the GPIO is to be used as an input pin, this bit must be set to '0' placing the output in high Z mode.

As an example, if you wanted to use the GPIO<sub>0</sub> pin to monitor the status of the input signal on input 0, you would load register 02h with the value 0010 0001b

Figure 14. Simplified LVCMOS Input Circuit

Figure 15. Simplified LVCMOS Output Circuit

#### POTENTIAL APPLICATIONS FOR GPIO PINS

In addition to being useful debug tools while bringing a DES design up, there are other practical uses to which the GPIO pins can be put:

#### Automatic Switching To Secondary Input If The Signal On The Primary Input Is Lost

By setting GPIO<sub>0</sub> to monitor the status of input0 when there is a signal present on input 0, the GPIO<sub>0</sub> pin will go low when there is no signal present on the Input0 pin, if this signal is inverted and then used to drive the RX MUX SEL then if the input on Input0 is lost, the device will automatically switch to Input1.

Another possible use of the GPIO pins is to provide access to external signals such as the CD output from an equalizer or the LOCK output from the DES itself via the SMBus, helping to minimize the number of connections between the DES and the FPGA.

#### APPLICATION INFORMATION

#### PCB LAYOUT RECOMMENDATIONS

In almost all applications, the inputs to the DES will be driven by the output of an equalizer such as the LMH0044. You should follow the recommendations on the equalizer datasheet for the interface between the input connector and the equalizer—the DES will be placed between the equalizer and the FPGA. If the DES is too close to the equalizer, then there is a risk of crosstalk between the high speed digital outputs of the DES and the equalizer inputs. Conversely, if too far away then the interconnect between the equalizer and the DES may either pick up stray noise, or may broadcast noise since this is a very high speed signal. Be certain to treat the signal from the equalizer to the DES as a differential trace. If there is skew between the two conductors of the differential trace, not only might this cause difficulties for the DES receive circuitry, but having a phase difference between the sides of the pair makes the signal look and radiate like a common mode signal.

If the loopthrough output is going to be used, it is advised that the DES be placed close to the Loopthrough output BNC connector, and the equalizer be placed close to the SDI Input BNC connector. This will minimize the lengths of the most critical connections.

The DES includes a cable driver for the loopthrough output. The SMPTE Serial specifications have very stringent requirements for output return loss on drivers. The output return loss will be degraded by non-idealities in the connection between the DES and the output connector. All efforts should be taken to minimize the trace lengths for this area, and to assure that the characteristic impedance of this trace is  $75\Omega$ . The  $75\Omega$  termination resistor should be placed as close to the loopthrough output pin as is practicable.

It is recommended that the PCB traces between the host FPGA and the DES be no longer than 10 inches (25cm) and that the traces be routed as differential pairs, with very tight matching of line lengths and coupling within a pair, as well as equal length traces for each of the six pairs.

#### PCB DESIGN DO'S AND DON'TS

**DO** Whenever possible dedicate an entire layer to each power supply whenever possible—this will reduce the inductance in the supply plane.

**DO** use surface mount components whenever possible.

**DO** place bypass capacitors close to each power pin.

**DON'T** create ground loops—pay attention to the cutouts that are made in your power and ground planes to make sure that there are not opportunities for loops.

**DON'T** allow discontinuities in the ground planes—return currents will follow the path of least resistance—for high frequency signals this will be the path of least inductance.

**DO** place the Loopthrough outputs as close as possible to the edge of the PCB where it will connect to the outside world.

**DO** make sure to match the trace lengths of all differential traces, both between the sides of an individual pair, and from pair to pair.

**DO** remember that VIAs have significant inductance—when using a via to connect to a power supply or ground layer, two in parallel are better than one.

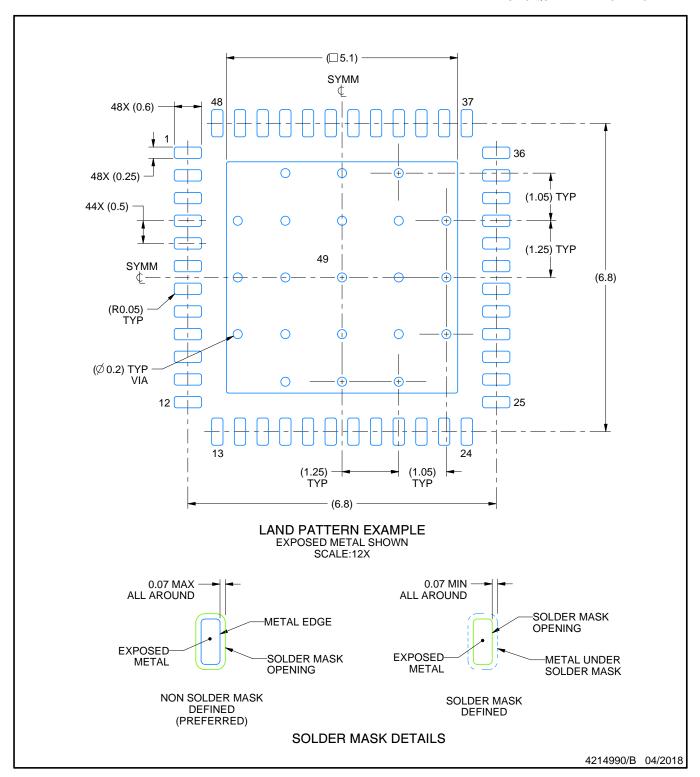

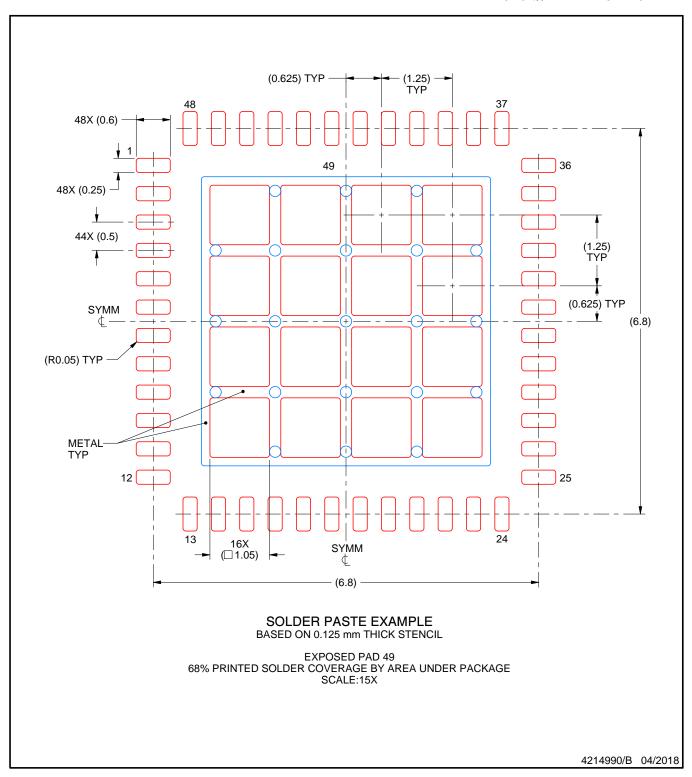

**DO** connect the slug on the bottom of the package to a solid Ground connection. This contact is used for the major GND connection to the device as well as serving as a thermal via to keep the die at a low operating temperature.

Figure 16. Evaluation Board Loopthrough Output Return Loss

### TYPICAL SMPTE APPLICATIONS CIRCUIT

A typical application circuit for the DES is shown in Figure 17. This circuit shows the LMH0341 3 Gbps deserializer, alternately this could employ the LMH0041 or LMH0071 deserializers in lower data rate SMPTE applications.

The RX interface between the DES and the host FPGA is composed of a 5-bit LVDS Data bus and its LVDS clock. This is a point-to-point interface. Line termination should be provided by the FPGA device. If not, and external  $100\Omega$  resistor maybe used and should be located as close to the FPGA as possible to minimize stub lengths. Pairs should be of equal length to minimize any skew impact. The LVDS clock (RXCLK) uses both edges to transfer the data.

An SMBus is also connected from the host FPGA to the DES. If the SMBus is shared, a chip select signal is used to select the device being addressed. The SCK and SDA signals require a pull up resistor. The SMB\_CS is driven by a GPO signal from the FPGA. Depending on the FPGA I/O it may also require a pull up unless it is a push / pull output.

<u>Depending</u> upon the application, several other Host GPIO signals maybe used. This includes the <u>DVB\_ASI</u> and <u>RESET</u> input signals. If these pins are not used, then must be tied off to the desired state. The <u>LOCK</u> signal maybe used to monitor the <u>DES</u>. If it is unused, leave the pin as a NC (or route to a test point).

Note also in this circuit, the LMH0341 GPIO\_1 pin has been configured to provide the status of RXIN\_1. When there is a signal present coming from the LMH0340, then RXIN\_1 will be selected. If that signal is lost, the input MUX will automatically switch over to provide the system reference black signal as the input from RXIN\_0.

The DES includes a SMPTE compliant cable driver for the Loopthrough function. While this is a differential driver, it is commonly used single-endedly to drive 75  $\Omega$  coax cables. External 75  $\Omega$  pull up resistors are used to the 2.5V rail. The active output(s) also includes a matching network to meet the required Output Return Loss SMPTE specification. While application specific, in general a series 75  $\Omega$  resistor shunted by a 6.8 nH inductor will provide a starting value to design with. The signal is then AC coupled to the cable with a 4.7  $\mu$ F capacitor. If the complementary output is not used, simply terminate it after its AC coupling capacitor to ground. This output (even though its inverting) may still be used for a loop back or 1:2 function due to the nature of the NRZI coding that the SMPTE standards require. The output voltage amplitude of the cable driver is set by the R<sub>SET</sub> resistor. For single-ended applications, an 7.87k $\Omega$  resistor is connected between this pin and ground to set the swing to 800mV.

The PLL loop filter is external for the SER. A capacitor is connected between the LF\_CP and LF\_REF pins. Typical value is 30 nF.

There are several configuration pins that requiring setting to the proper level. The RSVD\_H pins should be pulled High to the 3.3V rail with a 5 k $\Omega$  resistor. Depending upon the application the DVB\_ASI pin may be tied off or driven.

There are three supply connections (see bypass discussion in POWER SUPPLIES and also PIN DESCRIPTIONS for recommendations). The two main supplies are the 3.3V rail and the 2.5V rail. There is also a 3.3V connection for the PLL circuitry.

There are multiple Ground connections for the device. The main ground connection for the SER is through the large center DAP pad. This **must** be connected to ground for proper device operation. In addition, multiple other inputs are required to be connected to ground as show in Figure 17 and listed in PIN DESCRIPTIONS.

Figure 17. Typical SMPTE Application Circuit

Figure 18. Typical CML Application Circuit (LMH0051)

## **REGISTER DESCRIPTIONS**

Table 2 provides details on the device's configuration registers.

## **Table 2. DES Register Detail Table**

| ADD 'h   | Name                      | Bits                                                                                                                                                                                                                                           | Field                                                                                                                                                                                               | R/W          | Default         | Description                                                                                                                     |  |  |  |  |  |

|----------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 00       | device_identificati<br>on | may be                                                                                                                                                                                                                                         |                                                                                                                                                                                                     | SB of this r | egister must    | s address for the device. The default value is 0x58h, but this always be '0' Note that since the address is shifted over by B0h |  |  |  |  |  |

|          |                           | 7:1                                                                                                                                                                                                                                            | device_id r/w 058h SMBus Device ID                                                                                                                                                                  |              | SMBus Device ID |                                                                                                                                 |  |  |  |  |  |

|          |                           | 0                                                                                                                                                                                                                                              | reserved                                                                                                                                                                                            |              | 0               |                                                                                                                                 |  |  |  |  |  |

| 01       | reset                     | If a '1' is written into the LSB of register 0x01h then the device will do a soft reset, restoring it's internal state to the same as at powerup with the exception of the contents of register 0x00h, which if modified will remain unchanged |                                                                                                                                                                                                     |              |                 |                                                                                                                                 |  |  |  |  |  |

| İ        |                           | 7:1                                                                                                                                                                                                                                            | reserved                                                                                                                                                                                            |              |                 |                                                                                                                                 |  |  |  |  |  |

| <u> </u> |                           | 0                                                                                                                                                                                                                                              | sw_rst                                                                                                                                                                                              | r/w          | 0'b             | Software Reset                                                                                                                  |  |  |  |  |  |

| 02       | GPIO_0<br>Configuration   |                                                                                                                                                                                                                                                |                                                                                                                                                                                                     |              |                 | s to be used as an input, then the output must be TRI-<br>he input buffer must be disabled (bit[1]='0').                        |  |  |  |  |  |

|          |                           | 7:4                                                                                                                                                                                                                                            | GPIO_0_mode[3:0]                                                                                                                                                                                    | r/w          | 0000'b          | 0000: GPout register<br>0001: signal detect 0<br>all others: reserved                                                           |  |  |  |  |  |

|          |                           | 3:2                                                                                                                                                                                                                                            | GPIO_0_ren[1:0                                                                                                                                                                                      | r/w          | 01'b            | 00: pullup and pulldown disabled<br>01: pulldown enabled<br>10: pullup enabled<br>11: Reserved                                  |  |  |  |  |  |

|          |                           | 1                                                                                                                                                                                                                                              | GPIO_0_sleepz                                                                                                                                                                                       | r/w          | 0'b             | 0: input buffer disabled 1: input buffer enabled                                                                                |  |  |  |  |  |

|          |                           | 0                                                                                                                                                                                                                                              | GPout0 enable                                                                                                                                                                                       | r/w          | 1'b             | 0: output TRI-STATE 1: output enabled                                                                                           |  |  |  |  |  |

| 03       | GPIO_1<br>Configuration   |                                                                                                                                                                                                                                                | This register configures GPIO_1. Note, if this pin is to be used as an input, then the output mus STATE (bit[0]='0') and if used as an output, then the input buffer must be disabled (bit[1]='0'). |              |                 |                                                                                                                                 |  |  |  |  |  |

|          |                           | 7:4                                                                                                                                                                                                                                            | GPIO_0_mode[3 :0]                                                                                                                                                                                   | r/w          | 0000'b          | 0000: POR<br>0001: GP_OUT[1]<br>0010:signal detect 1<br>0011:cdr_lock<br>all others: reserved                                   |  |  |  |  |  |

|          |                           | 3:2                                                                                                                                                                                                                                            | GPIO_0_ren[1:0                                                                                                                                                                                      | r/w          | 01'b            | 00: pullup and pulldown disabled<br>01: pulldown enabled<br>10: pullup enabled<br>11: Reserved                                  |  |  |  |  |  |

|          |                           | 1                                                                                                                                                                                                                                              | GPIO_0_sleepz                                                                                                                                                                                       | r/w          | 0'b             | 0: input buffer disabled 1: input buffer enabled                                                                                |  |  |  |  |  |

|          |                           | 0                                                                                                                                                                                                                                              | GPout0 enable                                                                                                                                                                                       | r/w          | 1'b             | 0: output TRI-STATE 1: output enabled                                                                                           |  |  |  |  |  |

| 04       | GPIO_2<br>Configuration   | This register configures GPIO_2. Note, if this pin is to be used as an input, then the output must be TRI-STATE (bit[0]='0') and if used as an output, then the input buffer must be disabled (bit[1]='0').                                    |                                                                                                                                                                                                     |              |                 |                                                                                                                                 |  |  |  |  |  |

|          |                           | 7:4                                                                                                                                                                                                                                            | GPIO_0_mode[3 :0]                                                                                                                                                                                   | r/w          | 0000'b          | 0000: GPout [2]register<br>0001:Always ON clock<br>0010: LVDS TX CLK<br>0011:CDR_CLK<br>all others: reserved                    |  |  |  |  |  |

|          |                           | 3:2                                                                                                                                                                                                                                            | GPIO_0_ren[1:0]                                                                                                                                                                                     | r/w          | 01'b            | 00: pullup and pulldown disabled<br>01: pulldown enabled<br>10: pullup enabled<br>11: Reserved                                  |  |  |  |  |  |