# LMH2191 Dual Channel 52 MHz Clock Tree Driver

Check for Samples: LMH2191

### **FEATURES**

- One Input Clock, Two Output Clocks

- 1.8V Square Wave Clock Outputs

- Inverted Clock Outputs

- Independent Clock Requests

- . High Isolation of Supply Noise to Clock Input

- High Output-to-Output Isolation

- Integrated 1.8V Low-Dropout Regulator

- Low Output-Noise Voltage

- 10 mA Load Current

- EMI Filtering

- Ultra Low Standby Current

- V<sub>BAT</sub> Range = 2.5V to 5.5V

- 8-Bump DSBGA Package

#### **APPLICATIONS**

- Mobile Handsets

- Portable Equipment

## Destable Environe

## **DESCRIPTION**

The LMH2191 is a dual-channel clock tree driver that supplies a digital system clock to peripherals in mobile handsets or other applications. It provides a solution to clocking issues such as limited drive capability for fanout or longer traces. It also provides protection of the master clock from varying loads and frequency pulling effects, isolation from noisy modules, and crosstalk isolation. It has very low phase noise which enables it to drive sensitive modules such as Wireless LAN and Bluetooth.

The LMH2191 can be clocked up to 52 MHz and has an independent clock request pin for each clock output which allows the peripheral to control the clock. It features an integrated LDO which provides an ultra low-noise voltage supply with 10 mA external load current which can be used to supply the TCXO or other clock source. The LMH2191 dual clock distributor is offered in a tiny 1.61 mm x 1.063 mm 8-bump DSBGA package. Its small size and low supply current make it ideal for portable applications.

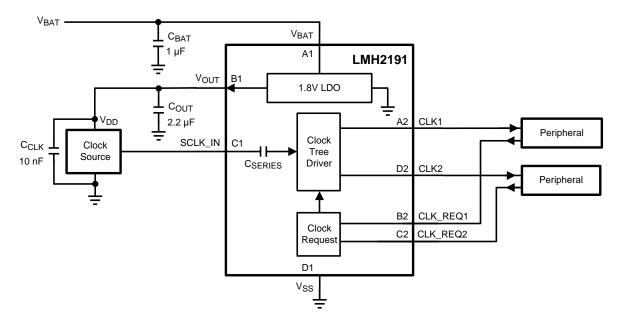

## **Typical Application**

A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### **ABSOLUTE MAXIMUM RATINGS**(1)(2)

| Supply Valtage                               | V <sub>BAT</sub> - V <sub>SS</sub> | -0.3V to 6V                        |

|----------------------------------------------|------------------------------------|------------------------------------|

| Supply Voltage                               | LVCMOS port IO voltage             | -0.3V to (V <sub>OUT</sub> + 0.3V) |

|                                              | Human Body Model                   | 2000V                              |

| ESD Tolerance <sup>(3)</sup>                 | Machine Model                      | 200V                               |

|                                              | Charge Device Model                | 1000V                              |

| Output Short Circuit Duration (4)            | LDO                                | infinite                           |

| Output Short Circuit Duration <sup>(4)</sup> | Clock Output                       | infinite                           |

| For Soldering Information see http://ww      | w.ti.com/lit/SNOA549               |                                    |

| Storage Temperature Range                    |                                    | -65°C to 150°C                     |

| Junction Temperature (5)                     | 150°C                              |                                    |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not specified. For specifications and the test conditions, see the Electrical Characteristics Tables.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (3) Human body model, applicable std. MIL-STD-883, Method 3015.7. Machine model, applicable std. JESD22–A115–A (ESD MM std of JEDEC). Field-Induced Charge-Device Model, applicable std. JESD22–C101–C. (ESD FICDM std. of JEDEC)

- (4) Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C.

- (5) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$  and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board.

#### OPERATING RATINGS(1)

| Supply Voltage (V <sub>BAT</sub> - V <sub>SS</sub> )      | Supply Voltage (V <sub>BAT</sub> - V <sub>SS</sub> ) |                  |

|-----------------------------------------------------------|------------------------------------------------------|------------------|

| Innut Clark SCLV IN                                       | Frequency                                            | 10 MHz to 52 MHz |

| Input Clock, SCLK_IN                                      | Duty Cycle                                           | 45% to 55%       |

| Temperature Range                                         |                                                      | -40°C to +85°C   |

| Package Thermal Resistance θ <sub>JA</sub> <sup>(2)</sup> | Board specification: 4LCELLPHONE                     |                  |

| Package YFX                                               | 153 °C/W                                             |                  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not specified. For specifications and the test conditions, see the Electrical Characteristics Tables.

- (2) The maximum power dissipation is a function of T<sub>J(MAX)</sub>, θ<sub>JA</sub> and T<sub>A</sub>. The maximum allowable power dissipation at any ambient temperature is P<sub>D</sub> = (T<sub>J(MAX)</sub> T<sub>A</sub>)/θ<sub>JA</sub>. All numbers apply for packages soldered directly onto a PC board.

# 3.5 V ELECTRICAL CHARACTERISTICS(1)

Unless otherwise specified, all limits are specified at  $T_J = 25$ °C,  $V_{BAT} = 3.5$ V,  $C_{BAT} = 1\mu$ F,  $C_{OUT} = 2.2 \mu$ F<sup>(2)</sup>,  $f_{SCLK\ IN} = 26 \ MHz$ ,  $I_{OUT} = 1$ mA, **Boldface** limits apply at the temperature extremes.

| Symbol                | Parameter                                    | Condition                                                                                          |                          | Min <sup>(3)</sup> | Typ <sup>(4)</sup> | Max <sup>(3)</sup>  | Units |

|-----------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------|--------------------|--------------------|---------------------|-------|

| Supply Cu             | rrent <sup>(5)(6)</sup>                      |                                                                                                    | ·                        |                    |                    | •                   |       |

| I <sub>DD</sub>       | Supply Current                               | Active Mode SCLK_IN = both clock outputs togglin CLK1/2 = 0pF; I <sub>OUT</sub> = 0m               | g; C <sub>LOAD</sub>     |                    | 1.4                | 1.65<br><b>1.7</b>  | mA    |

|                       |                                              | Active Mode SCLK_IN = both clock outputs togglin CLK1/2 = 33.5pF; I <sub>OUT</sub> =               | g; C <sub>LOAD</sub> for |                    | 3.7                | 4.45<br><b>4.50</b> | mA    |

|                       |                                              | Active Mode SCLK_IN = clock outputs toggling, C <sub>L</sub> CLK1/2 = 0pF, I <sub>OUT</sub> =0mA   | <sub>OAD</sub> for       |                    | 1.9                | 2.15<br><b>2.25</b> | mA    |

|                       |                                              | Active Mode SCLK_IN = clock outputs toggling, C <sub>L</sub> CLK1/2 = 33.5 pF, I <sub>OUT</sub> =0 | <sub>.OAD</sub> for      |                    | 5                  | 5.80<br><b>5.95</b> | mA    |

|                       |                                              | In shutdown. Input clock I CLK_REQ1/2=Low                                                          |                          | 0.1                | 1                  | μA                  |       |

|                       |                                              | In shutdown. Input clock to CLK_REQ1/2=Low                                                         | oggling.                 |                    | 0.1                | 1                   | uA    |

| C <sub>PD</sub>       | Power Dissipation Capacitance per CLK output | C <sub>LOAD</sub> for CLK1,2 = 0pF, respect to V <sub>OUT</sub> = 1.8V                             | Defined with             |                    | 20                 | 23.0<br><b>24.0</b> | pF    |

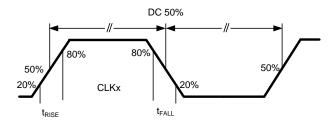

| Clock Out             | puts (CLK1/2) Figure 1, Figure 2             |                                                                                                    |                          |                    |                    |                     |       |

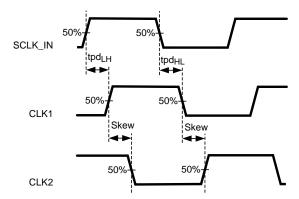

| t <sub>PD_LH</sub>    | Propagation Delay - Low to High              | 50% to 50%;<br>C <sub>LOAD</sub> = 33 pF; measured                                                 | d on CLK1                |                    | 6.1                | 10.5                |       |

| t <sub>PD_HL</sub>    | Propagation Delay - High to Low              | 50% to 50%;<br>C <sub>LOAD</sub> = 33 pF; measured                                                 | d on CLK1                |                    | 6.1                | 10.5                | ns    |

| t <sub>SKEW</sub>     | Skew Between Outputs (Either Edge)           | CLK1 to CLK2. 50% to 50                                                                            | )%                       |                    | 1.5                | 3.1                 |       |

| t <sub>RISE</sub>     | Rise Time <sup>(7)</sup>                     | For C <sub>L</sub> between 33.5 pF - 80%; typical value based                                      | 2.1                      | 3.7                | 5.9                |                     |       |

| t <sub>FALL</sub>     | Fall Time <sup>(7)</sup>                     | For C <sub>L</sub> between 33.5 pF - 80%; typical value based                                      | 2                        | 3.5                | 5                  | ns                  |       |

| CLK_DC                | Output Clock Duty Cycle                      | For C <sub>L</sub> between 33.5 pF -                                                               | 50 pF                    | 42                 | 50                 | 58                  | %     |

| Jitter <sub>RMS</sub> | Additive RMS period Jitter                   | f <sub>SCLK-IN</sub> = 26 MHz, BW =                                                                |                          | 95                 |                    | fo                  |       |

|                       |                                              | 100 Hz to 1MHz                                                                                     |                          | 110                |                    | fs                  |       |

<sup>(1)</sup> Electrical Table values apply only for factory testing (ATE) conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ .

<sup>(2)</sup> C<sub>BAT</sub>, C<sub>OUT</sub>: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) used in setting electrical characteristics.

Limits are 100% production tested at 25°C. Limits over temperature range are specified through correlations using statistical quality control (SQC) method.

<sup>(4)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

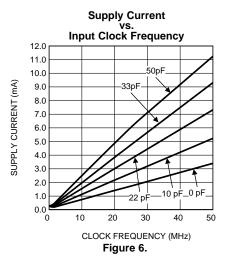

Supply current depends on switching frequency and load.

Positive current is current flowing into the device.

This parameter is specified by design and/or characterization and is not tested in production.

# 3.5 V ELECTRICAL CHARACTERISTICS<sup>(1)</sup> (continued)

Unless otherwise specified, all limits are specified at  $T_J = 25^{\circ}C$ ,  $V_{BAT} = 3.5V$ ,  $C_{BAT} = 1\mu F$ ,  $C_{OUT} = 2.2~\mu F^{(2)}$ ,  $f_{SCLK\_IN} = 26~MHz$ ,  $I_{OUT} = 1mA$ , **Boldface** limits apply at the temperature extremes.

| Symbol               | Parameter                              | Condition                                                |              | Min <sup>(3)</sup> | Typ <sup>(4)</sup> | Max <sup>(3)</sup> | Units   |

|----------------------|----------------------------------------|----------------------------------------------------------|--------------|--------------------|--------------------|--------------------|---------|

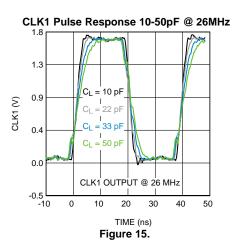

| CLK1                 | Additive Phase Noise                   | All outputs enabled at 26                                | f = 100 Hz   |                    | -128               |                    |         |

| Phase<br>Noise       |                                        | MHz                                                      | f = 1 kHz    |                    | -144               |                    |         |

| INOISE               |                                        |                                                          | f = 10 kHz   |                    | -150               |                    |         |

|                      |                                        |                                                          | f = 100 kHz  |                    | -160               |                    |         |

|                      |                                        |                                                          | f = 1 MHz    |                    | -163               |                    |         |

|                      |                                        | All outputs enabled at                                   | f = 100 Hz   |                    | -127               |                    |         |

|                      |                                        | 19.2 MHz                                                 | f = 1 kHz    |                    | -146               |                    |         |

|                      |                                        |                                                          | f = 10 kHz   |                    | -153               |                    |         |

|                      |                                        |                                                          | f = 100 kHz  |                    | -161               |                    |         |

|                      |                                        |                                                          | f = 1 MHz    |                    | -163               |                    | 15 // 1 |

| CLK2                 | Additive Phase Noise                   | All outputs enabled at 26                                | f = 100 Hz   |                    | -127               |                    | dBc/Hz  |

| Phase<br>Noise       |                                        | MHz                                                      | f = 1 kHz    |                    | -142               |                    |         |

| Noise                |                                        |                                                          | f = 10 kHz   |                    | -148               |                    |         |

|                      |                                        |                                                          | f = 100 kHz  |                    | -160               |                    |         |

|                      |                                        |                                                          | f = 1 MHz    |                    | -162               |                    |         |

|                      |                                        | All outputs enabled at                                   | f = 100 Hz   |                    | -129               |                    |         |

|                      |                                        | 19.2 MHz                                                 | f = 1 kHz    |                    | -144               |                    |         |

|                      |                                        |                                                          | f = 10 kHz   |                    | -151               |                    |         |

|                      |                                        |                                                          | f = 100 kHz  |                    | -163               |                    |         |

|                      |                                        |                                                          | f = 1 MHz    |                    | -164               |                    |         |

| V <sub>OH</sub>      | CLK1/2 Output Voltage High Level       | $I_{OH}$ = -2mA (equivalent or 800 $\Omega$ )            | utput load   | 1.6                |                    |                    | V       |

| V <sub>OL</sub>      | CLK1/2 Output Voltage Low Level        | I <sub>OL</sub> = 2mA                                    |              |                    |                    | 0.2                |         |

| R <sub>OFF</sub>     | Ouput Impedance when disabled          | with other output enabled enabled)                       | (LDO         |                    | grounded           |                    |         |

|                      |                                        | Both outputs disabled (LD                                | OO disabled) | C                  | liode to grour     | nd                 | -       |

| System CI            | ock Input (SCLK_IN)                    |                                                          |              |                    |                    |                    | +       |

| V <sub>I-pp</sub>    | SCLK_IN peak- to- peak input level (7) | For duty cycle variation <                               | 1%           | 0.6                | 1                  | 1.8                | V       |

| I <sub>IH</sub>      | Current into SCLK_IN pin (Input HIGH)  | SCLK_IN = 1.8V, CLK_R                                    | EQ1/2=Low    |                    | 0                  | 0.1                |         |

| I <sub>IL</sub>      | Current into SCLK_IN pin (Input LOW)   | SCLK_IN = 0V, CLK_REG                                    | Q1/2=Low     | -0.1               | 0                  |                    | μΑ      |

| C <sub>IN</sub>      | Input Capacitance (8)                  | CLK_REQ1/2=High                                          |              |                    | 7.5                | 13                 | pF      |

| R <sub>IN</sub>      | Input Resistance <sup>(8)</sup>        | CLK_REQ1/2=High<br>see Application Note: Input Impedance |              |                    | 14                 | 20                 | kΩ      |

| Switching            | Characteristics: System Clock Inp      | ut                                                       |              |                    |                    |                    |         |

| f <sub>SCLK_IN</sub> | System Clock                           |                                                          |              | 10                 | 26                 | 52                 | MHz     |

| CLK_DC               | Input Clock Duty Cycle                 |                                                          |              | 45                 | 50                 | 55                 | %       |

<sup>(8)</sup> This parameter is specified by design and/or characterization and is not tested in production.

# 3.5 V ELECTRICAL CHARACTERISTICS(1) (continued)

Unless otherwise specified, all limits are specified at  $T_J = 25$ °C,  $V_{BAT} = 3.5$ V,  $C_{BAT} = 1\mu F$ ,  $C_{OUT} = 2.2 \ \mu F^{(2)}$ ,  $f_{SCLK\ IN} = 26 \ MHz$ ,  $I_{OUT} = 1$ mA, **Boldface** limits apply at the temperature extremes.

| Symbol              | Parameter                                                      | Condition                                                      | 1                                        | Min <sup>(3)</sup> | Typ <sup>(4)</sup> | Max <sup>(3)</sup> | Units             |

|---------------------|----------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------|--------------------|--------------------|--------------------|-------------------|

| Clock Red           | uest Inputs (CLK_REQ1/2)                                       |                                                                |                                          |                    |                    |                    | 1                 |

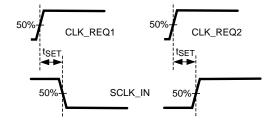

| t <sub>SET</sub>    | Setup Time from CLK_REQx to SCLK_IN, to enable CLKx (Figure 3) |                                                                |                                          | 12                 | 6.2                |                    | ns                |

| V <sub>IH</sub>     | CLK_REQ1/2 logic HIGH input                                    | V <sub>BAT</sub> = 2.5V                                        |                                          | 1.4                |                    |                    |                   |

|                     | level. (clock output = ON) <sup>(9)</sup>                      | V <sub>BAT</sub> = 3.5V                                        |                                          | 1.4                |                    |                    | V                 |

|                     |                                                                | $V_{BAT} = 5.5V$                                               |                                          | 1.4                |                    |                    |                   |

| $V_{IL}$            | CLK_REQ1/2 logic LOW input                                     | $V_{BAT} = 2.5V$                                               |                                          |                    |                    | 0.4                |                   |

|                     | level. (clock output = OFF)                                    | $V_{BAT} = 3.5V$                                               |                                          |                    |                    | 0.4                | V                 |

|                     |                                                                | $V_{BAT} = 5.5V$                                               |                                          |                    |                    | 0.4                |                   |

| I <sub>IH</sub>     | Current into CLK_REQ pin                                       | $V_{IH}$ = 1.8V, 200 k $\Omega$ pull c (Input HIGH)            | lown resistor                            |                    | 8.5                | 14                 | μΑ                |

| I <sub>IL</sub>     | Current into CLK_REQ pin                                       | V <sub>IL</sub> = V <sub>SS</sub> , (Input LOW)                |                                          | -0.2               | 0                  |                    | μA                |

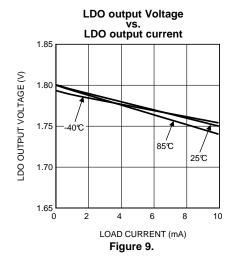

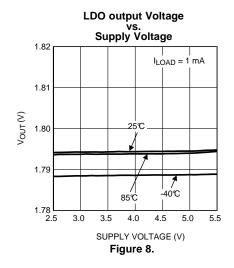

| LDO                 |                                                                |                                                                |                                          |                    | •                  |                    | •                 |

| V <sub>OUT</sub>    | Output Voltage                                                 | I <sub>OUT</sub> = 1mA                                         |                                          | 1.73               | 1.8                | 1.88               | V                 |

| I <sub>LOAD</sub>   | Load Current <sup>(10)</sup>                                   | V <sub>OUT</sub> > 1.7V                                        |                                          | 0                  |                    | 10                 | mA                |

| $V_{DO}$            | Dropout Voltage <sup>(11)</sup>                                | I <sub>OUT</sub> = 10 mA Vout=1.7V                             | I <sub>OUT</sub> = 10 mA Vout=1.7V       |                    | 125                |                    | mV                |

| I <sub>SC</sub>     | Short Circuit Current Limit                                    |                                                                |                                          |                    | 300                |                    | mA                |

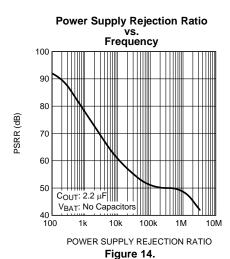

| PSRR                | Power Supply Rejection Ratio                                   | V <sub>BAT</sub> ripple = 200 mV <sub>PP</sub> ,               | f = 100 Hz                               |                    | 92                 |                    |                   |

|                     |                                                                | $I_{OUT} = 10 \text{ mA}$                                      | f = 217.5 Hz                             |                    | 90                 |                    |                   |

|                     |                                                                |                                                                | f = 1 kHz                                |                    | 78                 |                    |                   |

|                     |                                                                |                                                                | f = 10 kHz                               |                    | 60                 |                    | dB                |

|                     |                                                                |                                                                | f = 100 kHz                              |                    | 50                 |                    |                   |

|                     |                                                                |                                                                | f = 1 MHz                                |                    | 50                 |                    | _                 |

|                     |                                                                |                                                                | f = 3.25 MHz                             |                    | 42                 |                    |                   |

| E <sub>N</sub>      | Output Noise Voltage (12)                                      | BW = 10 Hz to 100 kHz,<br>CLK_REQ1/2=High, Inpu<br>active      | it clock not                             |                    | 18                 |                    | μV <sub>RMS</sub> |

| T <sub>SHTDWN</sub> | Thermal Shutdown                                               | Temperature                                                    |                                          |                    | 160                |                    | °C                |

|                     |                                                                | Hysteresis                                                     |                                          |                    | 20                 |                    |                   |

| $\Delta V_{OUT}$    | Line Transient                                                 | $V_{BAT} = 2.8V \text{ to } 3.4V \text{ in } 3000 \text{ m/s}$ | ) µs, I <sub>OUT</sub> =                 | -1                 |                    |                    |                   |

|                     |                                                                | $V_{BAT} = 3.4V \text{ to } 2.8V \text{ in } 300 \text{ m/s}$  | ) µs, I <sub>OUT</sub> =                 |                    |                    | 1                  | mV                |

|                     | Load Transient                                                 | I <sub>OUT</sub> = 0mA to 10 mA in                             | 10 µs                                    | -15                |                    |                    | m=\ /             |

|                     |                                                                | I <sub>OUT</sub> = 10 mA to 0mA in                             | I <sub>OUT</sub> = 10 mA to 0mA in 10 μs |                    |                    | 10                 | mV                |

|                     | Overshoot on Startup                                           |                                                                |                                          |                    |                    | 20                 | mV                |

| R <sub>OUT</sub>    | DC Output Resistance                                           |                                                                |                                          |                    | 5                  |                    | Ω                 |

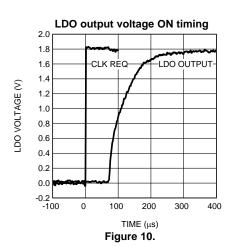

| T <sub>ON</sub>     | Turn on Time                                                   | From rising edge of CLK of V <sub>OUT</sub> (NOM)              | _REQ1 to 95%                             |                    | 200                | 260<br><b>350</b>  | μs                |

<sup>(9)</sup> Clock Request Inputs can tolerate logic high input levels up to V<sub>BAT</sub>.

(10) The device maintains stable, regulated output voltage without a load.

(11) Dropout voltage is the voltage difference between the input and the output at which the output voltage drops to 100 mV below its nominal value.

<sup>(12)</sup> The noise figure is the noise of the LDO only; harmonics of the output clocks are excluded.

### **TIMING DIAGRAMS**

Figure 1. Rise / Fall time and Duty Cycle Waveform for Clock Outputs

Figure 2. Clock Output Timing Waveforms

Figure 3. Clock Request Timing Waveforms

Submit Documentation Feedback

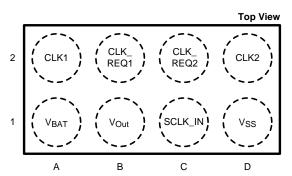

# **Connection Diagram**

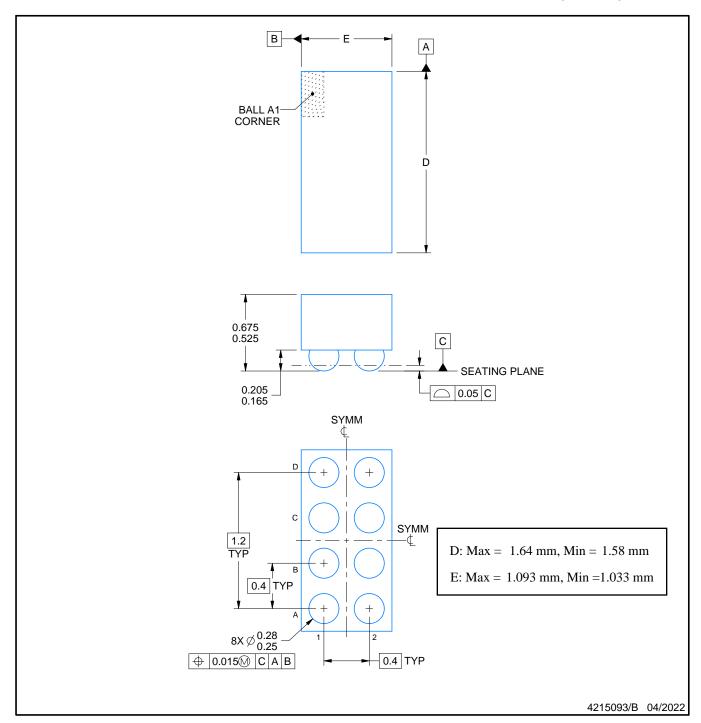

Figure 4. 8-Bump DSBGA See YFX0008 Package

### **PIN DESCRIPTIONS**

| Pin | Pin Name         | Port /<br>Direction | Type <sup>(1)</sup> | Description                                     |  |  |  |

|-----|------------------|---------------------|---------------------|-------------------------------------------------|--|--|--|

| C1  | SCLK_IN          | Host                | Input               | Source Clock Input                              |  |  |  |

| A2  | CLK1             | Peripheral          | Output              | Clock Output 1                                  |  |  |  |

| B2  | CLK_REQ1         | Peripheral          | Input               | Clock Request Input 1 Clock1 = ON at high level |  |  |  |

| D2  | CLK2             | Peripheral          | Output              | Clock Output 2                                  |  |  |  |

| C2  | CLK_REQ2         | Peripheral          | Input               | Clock Request Input 2 Clock2 = ON at high level |  |  |  |

| A1  | V <sub>BAT</sub> | Battery /<br>Input  | Power               | Power Supply                                    |  |  |  |

| B1  | Vout             | LDO /<br>Output     | Power               | Power Supply to Clock Source and clock outputs  |  |  |  |

| D1  | V <sub>SS</sub>  | Ground              | Ground              | Ground Pin                                      |  |  |  |

<sup>(1)</sup> I = Input, O = Output, I/O = Input / Output

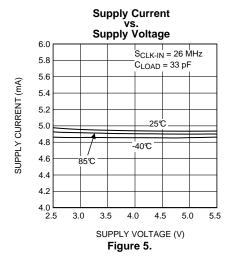

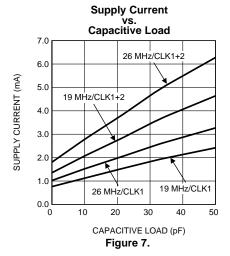

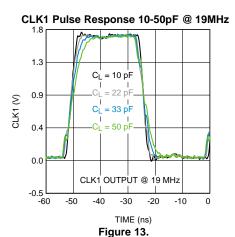

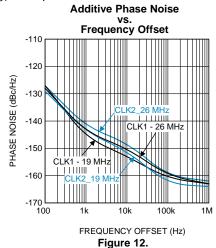

#### TYPICAL PERFORMANCE CHARACTERISTICS

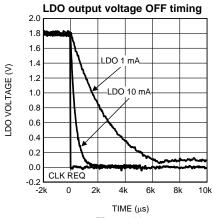

Unless otherwise specified,  $T_A$  = 25°C,  $V_{BAT}$  = 3.5V,  $f_{SCLK\_IN}$  = 26 MHz,  $C_{OUT}$  = 2.2  $\mu F$

Submit Documentation Feedback

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Unless otherwise specified,  $T_A$  = 25°C,  $V_{BAT}$  = 3.5V,  $f_{SCLK\_IN}$  = 26 MHz,  $C_{OUT}$  = 2.2  $\mu F$

Figure 11.

Submit Documentation Feedback

#### APPLICATION INFORMATION

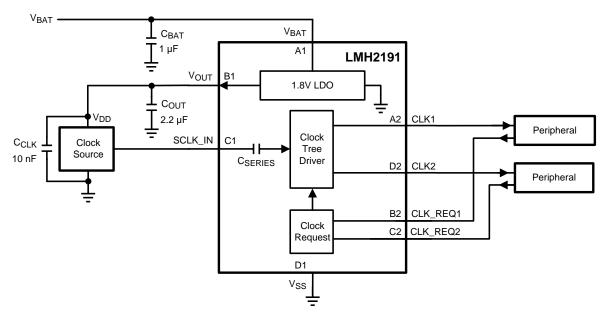

The LMH2191 is a complete 52 MHz clocking conditioner and clock tree driver. The LMH2191 is used to supply a common clock to mobile phone peripherals such as Bluetooth, Wireless LAN, and/or Digital Video Broadcast-H (DVB-H). The high isolation between the clock outputs ensures that the peripherals don't disrupt each other. Its excellent phase noise characteristics prevent the clock quality from deteriorating. A typical LMH2191 setup is depicted in Figure 17.

Figure 17. LMH2191 Typical Application Schematic

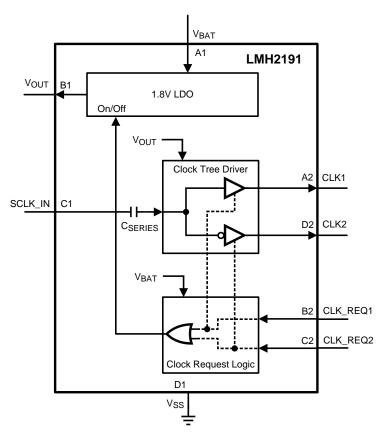

The internal structure of the LMH2191 is depicted in the block diagram of Figure 18.

Figure 18. Block Diagram

The LMH2191 clock distribution circuit is comprised of 3 blocks:

- Clock tree driver

- Clock request logic

- Low Dropout Regulator (LDO)

The clock tree driver provides a clean clock to 2 separately connected peripheral devices. Independent clock request inputs allow the peripheral to control when the particular clock should be enabled. Furthermore, both clock request inputs control the LDO output voltage, e.g., when both request inputs are low (no CLK1 and no CLK2 output required), the LDO voltage is disabled. The LDO provides a low-noise, high-PSRR supply voltage that enables low phase noise on the clock outputs, and low quiescent current for portable applications. It can also be used to supply the TCXO. The following sections provide a detailed description of each block.

#### **CLOCK TREE DRIVER**

The clock tree driver consists of one input that drives 2 outputs. It is supplied by a high-precision voltage regulator of 1.8V, the LDO. The Clock outputs are enabled when the appropriate Clock Request inputs are logic high.

#### **Clock Tree Driver Input**

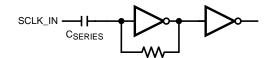

The source clock input (SCLK\_IN) is the input for the clock tree driver. This input has an internally connected coupling capacitor ( $C_{SERIES}$ ) with a value of 33pF. In shutdown mode (when both CLK\_REQ inputs are low), the input stage is completely switched off to prevent unnecessary power consumption when the source clock is still present.

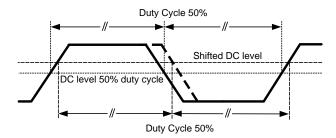

Due to the internal coupling capacitor, the clock signal is DC biased, since the coupling capacitor prevents the internal biasing of the input circuitry to be affected by the external DC voltage. Because of the coupling capacitor, the minimum clock frequency is 10 MHz. It is assumed that the input signal is a sine wave or a typical TCXO waveform (the signal from a TCXO has slow edges), enabling the control loop to adjust to a duty cycle of 50% if the input signal differs slightly from 50% duty cycle. The duty cycle is an important timing parameter for the peripheral equipment. The circuit that adjust the duty cycle is shown in Figure 19.

Figure 19. Clock Duty Cycle Regulation

Figure 20. Duty Cycle adjust levels

In order to achieve a duty cycle of 50%, the edges of the incoming clock signal (SCLK\_IN) are used to move the switching point to the level that is needed to create the 50% duty cycle. The simplified input circuit consists of an inverter and a feedback resistor. Together with the input series capacitor of about 30 pF, the circuit creates a DC level depending on the duty cycle of the incoming clock signal. When the duty cycle is exactly 50%, the DC level is in the middle of the upper and lower pulse level. When the duty cycle differs from 50%, the DC level shifts slightly to maintain the duty cycle level at 50%. (See Duty Cycle adjust levels of Figure 20.) As explained above, the slow edges of the SCLK IN signal are important to make the control loop work.

#### Input Impedance

The input impedance can be split up into two parts: the DC input resistance and the AC input impedance. Due to the used series capacitor in the input signal path the DC resistance is infinite. The AC input impedance is formed by the circuit drawn in Figure 19. This circuit consists of an inverter and a feedback resistor. A signal fed to the input pin is connected to the inverter input which has a high input impedance and is in parallel to the feedback resistor of 30 k $\Omega$ . The other pin of the feedback resistor is connected to the output of the inverter which means that the input current is higher than it would be if it were connected to a decoupled supply connection. For this reason the AC input resistance can be much lower than the connected feedback resistor of 30 k $\Omega$ . The input resistance is dependant on the amplitude of the input signal. When an input amplitude of 1.8V is used (the same amplitude as the output of the inverter), the input impedance is theoretical half the value of the feedback resistor. When the amplitude of the input signal lowers, the input resistance becomes lower too. With an input signal of  $10 \, \mathrm{k}\Omega$ .

### **Clock Tree Driver Outputs**

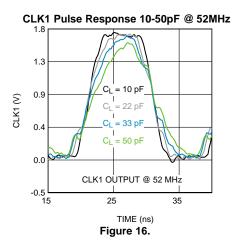

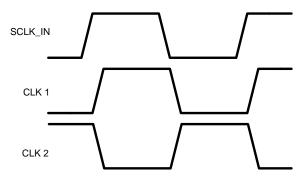

The LMH2191's clock tree driver outputs have a drive strength that make each output capable of driving a capacitive load up to 50 pF, together with a minimum of EMI. Further reduction of EMI is achieved by the inversion of the CLK2 output. (See Figure 21.) Both the drive strength and the capacitive load make the edges of the output pulse relative slow which is favorable for EMI reduction.

Figure 21. Clock Outputs

#### **CLOCK REQUEST LOGIC**

A clock request input is provided for each clock output. This allows the peripheral device to control when it wants to receive a clock. In case the application does not have clock request functionality, the CLKx\_REQ can be hard wired to a logic high level to enable the clock output continuously. The clock request inputs have logic levels compatible with 1.8V logic, but can tolerate logic high levels up to V<sub>BAT</sub>.

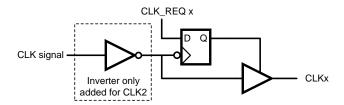

Figure 22. Enabling the output

The clock request logic enables an independent control of the clock tree driver outputs, CLK1 and CLK2, as well as an LDO disable when both request inputs are low.

The on and off switching of the clock output drivers is done synchronously with the clock input in order to prevent glitches at the clock output. For this the clock request signal is connected to the D input of a latch. The Q output of this latch enables the clock output driver (see Figure 22). For the CLK1 output the CLK input signal is connected via an inverter to the clock input of the latch. In this way the latch enables and disables the CLK1 output buffer on the falling edge of the clock signal. For the CLK2 output an extra inverter is inserted prior to the latch circuit, and the CLK2 output buffer is enabled and disabled on the rising edge of the clock input signal (equal to the falling edge of the CLK2 output signal).

### LOW DROPOUT REGULATOR

The linear and Low-Dropout regulator (LDO) is used to regulate the input voltage,  $V_{BAT}$ , thus generating a well-defined ultra low noise 1.8V supply voltage. This allows the LMH2191 to suppress  $V_{BAT}$  supply voltage ripple and noise for the TCXO and the internal Clock Path. Voltage ripple and noise would distort clock edges causing extra phase noise on the distributed clock signal.

The LDO is powered up whenever a Clock Request is active; it supports overheating detection and will switch off in case overheating occurs. The recommended sequence for powering up the LDO is to raise a clock request to a high level with the supply already powered up. Thus the LDO stays in shutdown mode with sub  $\mu$ A current consumption until an output clock is actually needed. The LDO will power up within the turn-on time of about 200  $\mu$ s (as specified in the data sheet tables). Alternatively, the clock request input can be hard wired to  $V_{BAT}$  which powers up the LDO simultaneously with  $V_{BAT}$ . A drawback is that the LDO and clock path (and if connected, the TCXO) will always draw current when  $V_{BAT}$  is powered up. Also, in this setup, care should be taken with supplies with an excessive long startup time of more than about 25 ms. Under this condition the LDO could exhibit excessive long turn-on delay (order of seconds.)

#### LAYOUT RECOMMENDATIONS

As with any other device, careful attention must be paid to the board layout. If the board isn't properly designed, the performance of the device can be less than desired. Care should be taken that the SCLK\_IN input trace and the output traces of CLK1 and CLK2 are as short as possible to reduce extra capacitive load observed by the clock outputs. Also proper de-coupling close to the device is necessary. Table 1 depicts the advised component values. TI suggests to use the evaluation board, available from the Texas Instruments web site www.ti.com, as a guide for layout and as an aid in device testing and characterization.

**Table 1. Recommended Component Values**

| Symbol                          | Parameter                     | Min  | Тур | Max | Units |

|---------------------------------|-------------------------------|------|-----|-----|-------|

| C <sub>BAT</sub> <sup>(1)</sup> | Capacitor on V <sub>BAT</sub> | 0.47 | 1   |     |       |

| C <sub>OUT</sub> <sup>(1)</sup> | Capacitor on V <sub>OUT</sub> | 1    | 2.2 |     | μF    |

| ESR                             | Equivalent Series Resistance  | 5    |     | 500 | mΩ    |

(1) C<sub>BAT</sub>, C<sub>OUT</sub>: Low-ESR Surface-Mount Ceramic Capacitors (MLCC's) used in setting electrical characteristics.

# **REVISION HISTORY**

| Changes from Revision C (April 2013) to Revision D  Changed layout of National Data Sheet to TI format |                                                    |     |   |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----|---|

| •                                                                                                      | Changed layout of National Data Sheet to TI format | . 1 | 2 |

11-Nov-2025 www.ti.com

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                 |                       |      | (4)                           | (5)                        |              |                  |

| LMH2191TME/NOPB       | Active | Production    | DSBGA (YFX)   8 | 250   SMALL T&R       | Yes  | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 85    | 5                |

| LMH2191TME/NOPB.A     | Active | Production    | DSBGA (YFX)   8 | 250   SMALL T&R       | Yes  | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 85    | 5                |

| LMH2191TMX/NOPB       | Active | Production    | DSBGA (YFX)   8 | 3000   LARGE T&R      | Yes  | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 85    | 5                |

| LMH2191TMX/NOPB.A     | Active | Production    | DSBGA (YFX)   8 | 3000   LARGE T&R      | Yes  | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 85    | 5                |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 26-Oct-2024

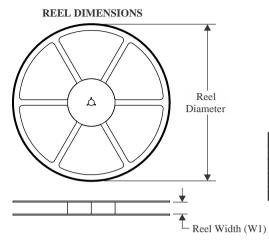

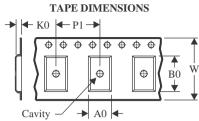

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

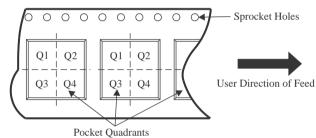

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMH2191TME/NOPB | DSBGA           | YFX                | 8 | 250  | 178.0                    | 8.4                      | 1.24       | 1.7        | 0.76       | 4.0        | 8.0       | Q1               |

| LMH2191TMX/NOPB | DSBGA           | YFX                | 8 | 3000 | 178.0                    | 8.4                      | 1.24       | 1.7        | 0.76       | 4.0        | 8.0       | Q1               |

www.ti.com 26-Oct-2024

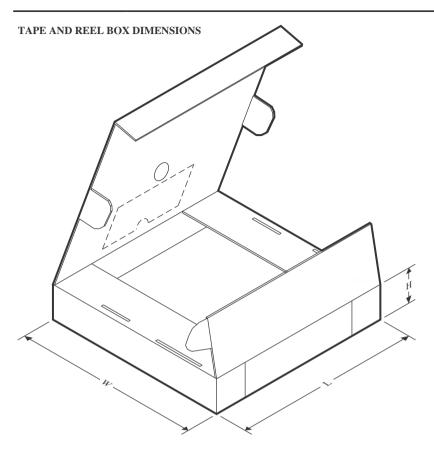

### \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMH2191TME/NOPB | DSBGA        | YFX             | 8    | 250  | 208.0       | 191.0      | 35.0        |

| LMH2191TMX/NOPB | DSBGA        | YFX             | 8    | 3000 | 208.0       | 191.0      | 35.0        |

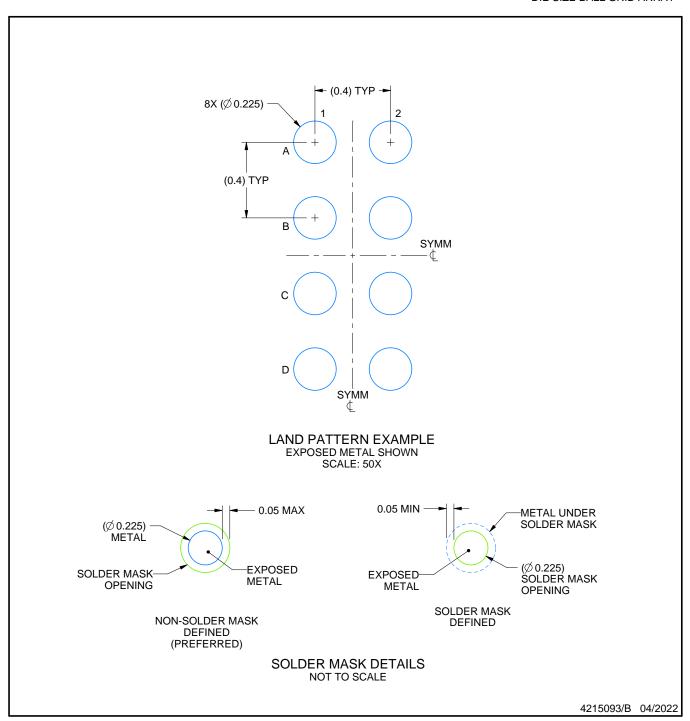

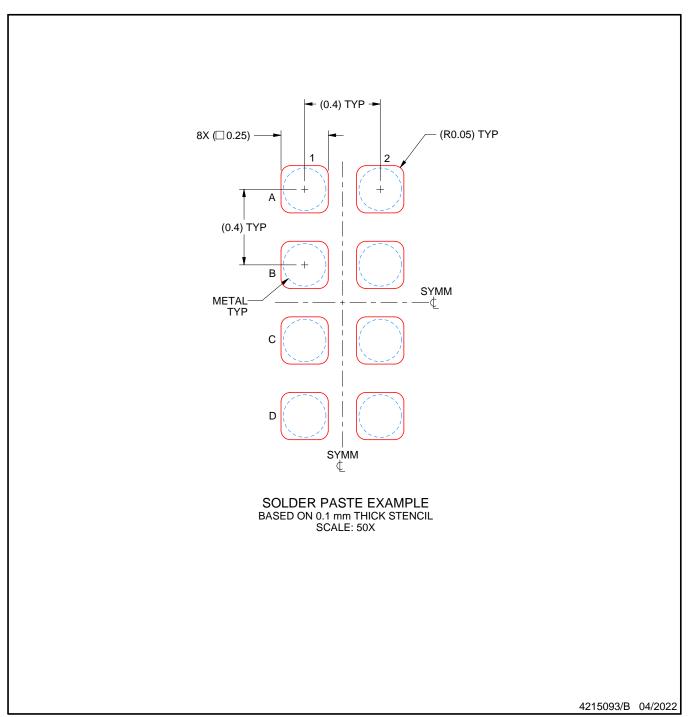

DIE SIZE BALL GRID ARRAY

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

DIE SIZE BALL GRID ARRAY

NOTES: (continued)

Final dimensions may vary due to manufacturing tolerance considerations and also routing constraints. See Texas Instruments Literature No. SNVA009 (www.ti.com/lit/snva009).

DIE SIZE BALL GRID ARRAY

#### NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025