# STEREO AUDIO CODEC WITH USB INTERFACE, SINGLE-ENDED ANALOG INPUT/OUTPUT AND S/PDIF

#### **FEATURES**

- PCM2904: Without S/PDIF

- PCM2906: With S/PDIF

- On-Chip USB Interface:

- With Full-Speed Transceivers

- Fully Compliant With USB 1.1 Specification

- Certified by USB-IF

- Partially Programmable Descriptors (1)

- USB Adaptive Mode for Playback

- USB Asynchronous Mode for Record

- Bus Powered

- 16-Bit Delta-Sigma ADC and DAC

- · Sampling Rate:

- DAC: 32, 44.1, 48 kHz

- ADC: 8, 11.025, 16, 22.05, 32, 44.1, 48 kHz

- On-Chip Clock Generator With Single 12-MHz Clock Source

- Single Power Supply: 5 V Typical (V<sub>BUS</sub>)

- Stereo ADC

- Analog Performance at V<sub>BUS</sub> = 5 V

- THD+N = 0.01%

- SNR = 89 dB

- Dynamic Range = 89 dB

- Decimation Digital Filter

- Pass-Band Ripple = ±0.05 dB

- Stop-Band Attenuation = -65 dB

- Single-Ended Voltage Input

- Antialiasing Filter Included

- Digital LCF Included

- Stereo DAC:

- Analog Performance at V<sub>BUS</sub> = 5 V

- THD+N = 0.005%

- SNR = 96 dB

- Dynamic Range = 93 dB

- Oversampling Digital Filter

- (1) The descriptor can be modified by changing a mask.

- Pass-Band Ripple = ±0.1 dB

- Stop-Band Attenuation = -43 dB

- Single-Ended Voltage Output

- Analog LPF Included

- Multifunctions:

- Human Interface Device (HID) Volume ± Control and Mute Control

- Suspend Flag

- Package: 28-Pin SSOP

#### **APPLICATIONS**

- USB Audio Speaker

- USB Headset

- USB Monitor

- USB Audio Interface Box

#### DESCRIPTION

The PCM2904/2906 is Texas Instruments single-chip USB stereo audio codec with USB-compliant full-speed protocol controller and S/PDIF (PCM2906 only). The USB protocol controller works with no software code, but the USB descriptors can be modified in some areas (for example, vendor ID/product ID). The PCM2904/2906 employs SpAct™ architecture, TI's unique system that recovers the audio clock from USB packet data. On-chip analog PLLs with SpAct enable playback and record with low clock jitter and with independent playback and record sampling rates.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SpAct is a trademark of Texas Instruments.

System Two, Audio Precision are trademarks of Audio Precision, Inc.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGING ORDERING INFORMATION

| PRODUCT     | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA |

|-------------|--------------|-----------------------|-----------------------------------|--------------------|--------------------|--------------------|

| PCM2904DB   | 28-lead SSOP | 28DB                  | –25°C to 85°C                     | PCM2904            | PCM2904DB          | Rails              |

| FCW2904DB   | 20 1044 0001 | 2006                  | 23 0 10 03 0                      | F CIVI2904         | PCM2904DBR         | Tape and reel      |

| PCM2906DB   | 28-lead SSOP | 28DB                  | –25°C to 85°C                     | PCM2906            | PCM2906DB          | Rails              |

| PCIVIZ906DB | Zo-lead SSOP | 2008                  | -25°C 10 85°C                     | PGIVI2906          | PCM2906DBR         | Tape and reel      |

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                   |                                                                                                    | PCM2904/PCM2906                      | UNIT    |

|-------------------|----------------------------------------------------------------------------------------------------|--------------------------------------|---------|

| Supply voltage,   | V <sub>BUS</sub>                                                                                   | -0.3 to 6.5                          | V       |

| Ground voltage    | differences, AGNDC, AGNDP, AGNDX, DGND, DGNDU                                                      | ±0.1                                 | V       |

| Digital input     | SEL0, SEL1, TEST0 (DIN) <sup>(2)</sup>                                                             | -0.3 to 6.5                          |         |

| voltage           | D+, D-, HID0, HID1, HID2, XTI, XTO, TEST1 (DOUT)(2), SSPND                                         | -0.3 to (V <sub>DDI</sub> + 0.3) < 4 | V       |

| Analog input      | V <sub>IN</sub> L, V <sub>IN</sub> R, V <sub>COM</sub> , V <sub>OUT</sub> R, V <sub>OUT</sub> L    | $-0.3$ to $(V_{CCCI} + 0.3) < 4$     | V       |

| voltage           | V <sub>CCCI</sub> , V <sub>CCP1I</sub> , V <sub>CCP2I</sub> , V <sub>CCXI</sub> , V <sub>DDI</sub> | -0.3 to 4                            | \ \ \   |

| Input current (an | y pins except supplies)                                                                            | ±10                                  | mA      |

| Ambient tempera   | ature under bias                                                                                   | -40 to 125                           | °C      |

| Storage tempera   | iture, T <sub>stg</sub>                                                                            | -55 to 150                           | °C      |

| Junction tempera  | ature, T <sub>J</sub>                                                                              | 150                                  | °C      |

| Lead temperatur   | e (soldering)                                                                                      | 260                                  | °C, 5 s |

| Package temper    | ature (IR reflow, peak)                                                                            | 250                                  | °C      |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) (): PCM2906

#### **ELECTRICAL CHARACTERISTICS**

All specifications at  $T_A = 25$ °C,  $V_{BUS}$ , = 5 V,  $f_S = 44.1$  kHz,  $f_{IN} = 1$  kHz, 16-bit data (unless otherwise noted)

|                                        | PARAMETER                         | TEST CONDITIONS                    | PCM2904D         | B, PCM2               | 906DB  | UNIT     |

|----------------------------------------|-----------------------------------|------------------------------------|------------------|-----------------------|--------|----------|

|                                        | PARAMETER                         | TEST CONDITIONS                    | MIN              | TYP                   | MAX    | UNIT     |

| DIGITAL INPUT                          | OUTPUT                            |                                    |                  |                       |        |          |

|                                        | Host interface                    | Apply USB Revision 1.1, full speed |                  |                       |        |          |

|                                        | Audio data format                 | USB isochronous data format        |                  |                       |        |          |

| INPUT LOGIC                            |                                   |                                    |                  |                       |        |          |

| V <sub>IH</sub> <sup>(1)</sup>         |                                   |                                    | 2                |                       | 3.3    |          |

| V <sub>IL</sub> <sup>(1)</sup>         |                                   |                                    |                  |                       | 0.8    |          |

| V <sub>IH</sub> (2) (3)                |                                   |                                    | 2.52             |                       | 3.3    |          |

| V <sub>IL</sub> <sup>(2)(3)</sup>      | Input logic level                 |                                    |                  |                       | 0.9    | Vdo      |

| V <sub>IH</sub> (4)                    | Input logic level                 |                                    | 2                |                       | 5.25   | Vdc      |

| V <sub>IL</sub> <sup>(4)</sup>         |                                   |                                    |                  |                       | 0.8    |          |

| V <sub>IH</sub> <sup>(5)</sup>         |                                   |                                    | 2.52             |                       | 5.25   |          |

| V <sub>IL</sub> <sup>(5)</sup>         |                                   |                                    |                  |                       | 0.9    |          |

| I <sub>IH</sub> <sup>(1)</sup> (2) (4) |                                   | V <sub>IN</sub> = 3.3 V            |                  |                       | ±10    |          |

| I <sub>IL</sub> <sup>(1)</sup> (2) (4) |                                   | V <sub>IN</sub> = 0 V              |                  |                       | ±10    | μΑ       |

| I <sub>IH</sub> <sup>(3)</sup>         | Input logic current               | V <sub>IN</sub> = 3.3 V            |                  | 50                    | 80     |          |

| I <sub>IL</sub> (3)                    |                                   | V <sub>IN</sub> = 0 V              |                  |                       | ±10    |          |

| I <sub>IH</sub> <sup>(5)</sup>         |                                   | V <sub>IN</sub> = 3.3 V            |                  | 65                    | 100    |          |

| I <sub>IL</sub> (5)                    |                                   | V <sub>IN</sub> = 0 V              |                  |                       | ±10    |          |

| OUTPUT LOGIC                           |                                   |                                    | •                |                       |        |          |

| V <sub>OH</sub> <sup>(1)</sup>         |                                   |                                    | 2.8              |                       |        |          |

| V <sub>OL</sub> <sup>(1)</sup>         |                                   |                                    |                  |                       | 0.3    |          |

| V <sub>OH</sub> <sup>(6)</sup>         | Output la rie laurel              | $I_{OH} = -4 \text{ mA}$           | 2.8              |                       |        | V/-I-    |

| V <sub>OL</sub> <sup>(6)</sup>         | Output logic level                | I <sub>OL</sub> = 4 mA             |                  |                       | 0.5    | Vdc      |

| V <sub>OH</sub> <sup>(7)</sup>         |                                   | $I_{OH} = -2 \text{ mA}$           | 2.8              |                       |        |          |

| V <sub>OL</sub> <sup>(7)</sup>         |                                   | I <sub>OL</sub> = 2 mA             |                  |                       | 0.5    |          |

| CLOCK FREQU                            | ENCY                              |                                    | •                |                       |        |          |

|                                        | Input clock frequency, XTI        |                                    | 11.994           | 12                    | 12.006 | MHz      |

| ADC CHARACT                            | ERISTICS                          |                                    | •                |                       |        |          |

|                                        | Resolution                        |                                    |                  | 8, 16                 |        | bits     |

|                                        | Audio data channel                |                                    |                  | 1, 2                  |        | channel  |

| CLOCK FREQU                            | IENCY                             |                                    | •                |                       |        |          |

| f <sub>s</sub>                         | Sampling frequency                |                                    | 8, 11.025,<br>44 | , 16, 22.0<br>4.1, 48 | 5, 32, | kHz      |

| DC ACCURACY                            | (                                 |                                    |                  |                       |        |          |

|                                        | Gain mismatch, channel-to-channel |                                    |                  | ±1                    | ±5     | % of FSR |

|                                        | Gain error                        |                                    |                  | ±2                    | ±10    | % of FSF |

|                                        | Bipolar zero error                |                                    |                  | ±0                    |        | % of FSR |

<sup>(1)</sup> Pins 1, 2: D+, D-

<sup>(2)</sup> (3) Pin 21: XTI

<sup>(3)</sup> Pins 5, 6, 7: HID0, HID1, HID2 (4) Pins 8, 9: SEL0, SEL1

<sup>(5)</sup> Pin 24: DIN (6) Pin 25: DOUT (7) Pin 28: SSPND

## **ELECTRICAL CHARACTERISTICS (Continued)**

All specifications at  $T_A = 25$ °C,  $V_{BUS}$ , = 5 V,  $f_S = 44.1$  kHz,  $f_{IN} = 1$  kHz, 16-bit data (unless otherwise noted)

|                | DADAMETED                              | TEST CONDITIONS                                             | PCM2904              | IDB, PCM29            | 06DB                 | UNIT     |

|----------------|----------------------------------------|-------------------------------------------------------------|----------------------|-----------------------|----------------------|----------|

|                | PARAMETER                              |                                                             | MIN                  | TYP                   | MAX                  | UNIT     |

| DYNAMI         | C PERFORMANCE <sup>(1)</sup>           |                                                             |                      |                       |                      |          |

|                |                                        | $V_{IN} = -0.5 \text{ dB}^{(2)}, V_{CCCI} = 3.67 \text{ V}$ |                      | 0.01%                 | 0.02%                |          |

| THD+N          | Total harmonic distortion plus noise   | $V_{IN} = -0.5 \text{ dB}^{(3)}$                            |                      | 0.1%                  |                      |          |

|                |                                        | $V_{IN} = -60 \text{ dB}$                                   |                      | 5%                    |                      |          |

|                | Dynamic range                          | A-weighted                                                  | 81                   | 89                    |                      | dB       |

|                | S/N ratio                              | A-weighted                                                  | 81                   | 89                    |                      | dB       |

|                | Channel separation                     |                                                             | 80                   | 85                    |                      | dB       |

| ANALOG         | S INPUT                                |                                                             |                      |                       |                      |          |

|                | Input voltage                          |                                                             |                      | 0.6 V <sub>CCCI</sub> |                      | Vp-p     |

|                | Center voltage                         |                                                             |                      | 0.5 V <sub>CCCI</sub> |                      | V        |

|                | Input impedance                        |                                                             |                      | 30                    |                      | kΩ       |

|                | A sticling in a filter for a superior  | -3 dB                                                       |                      | 150                   |                      | kHz      |

|                | Antialiasing filter frequency response | f <sub>IN</sub> = 20 kHz                                    |                      | -0.08                 |                      | dB       |

| DIGITAL        | FILTER PERFORMANCE                     |                                                             |                      |                       |                      |          |

|                | Pass band                              |                                                             |                      |                       | 0.454 f <sub>s</sub> | Hz       |

|                | Stop band                              |                                                             | 0.583 f <sub>s</sub> |                       |                      | Hz       |

|                | Pass-band ripple                       |                                                             |                      |                       | ±0.05                | dB       |

|                | Stop-band attenuation                  |                                                             | -65                  |                       |                      | dB       |

| t <sub>d</sub> | Delay time                             |                                                             |                      | 17.4/f <sub>s</sub>   |                      | S        |

|                | LCF frequency response                 | -3 dB                                                       |                      | 0.078 <sub>fs</sub>   |                      | MHz      |

| DAC CH         | ARACTERISTICS                          |                                                             |                      |                       |                      |          |

|                | Resolution                             |                                                             |                      | 8, 16                 |                      | bits     |

|                | Audio data channel                     |                                                             |                      | 1, 2                  |                      | channel  |

| CLOCK I        | FREQUENCY                              |                                                             |                      |                       |                      |          |

| $f_s$          | Sampling frequency                     |                                                             | 3                    | 2, 44.1, 48           |                      | kHz      |

| DC ACC         | URACY                                  |                                                             |                      |                       |                      |          |

|                | Gain mismatch, channel-to-channel      |                                                             |                      | ±1                    | ±5                   | % of FSR |

|                | Gain error                             |                                                             |                      | ±2                    | ±10                  | % of FSR |

|                | Bipolar zero error                     |                                                             |                      | ±2                    |                      | % of FSR |

| DYNAMI         | C PERFORMANCE <sup>(4)</sup>           |                                                             |                      |                       |                      |          |

| THD+N          | Total harmonic distortion plus noise   | V <sub>OUT</sub> = 0 dB                                     |                      | 0.005%                | 0.016%               |          |

| I LD+IN        | rotal narmonic distortion plus noise   | V <sub>OUT</sub> = -60 dB                                   |                      | 3%                    |                      |          |

|                | Dynamic range                          | EIAJ, A-weighted                                            | 87                   | 93                    |                      | dB       |

| SNR            | Signal-to-noise ratio                  | EIAJ, A-weighted                                            | 90                   | 96                    |                      | dB       |

|                | Channel separation                     |                                                             | 86                   | 92                    |                      | dB       |

<sup>(1)</sup>  $f_{IN} = 1 \text{ kHz}$ , using the System Two<sup>TM</sup> audio measurement system by Audio Precision<sup>TM</sup> in RMS mode with 20-kHz LPF, 400-Hz HPF in calculation.

<sup>(2)</sup> Using external voltage regulator for V<sub>CCCI</sub> (as shown in Figure 36 and Figure 37, using REG103xA-A)

(3) Using internal voltage regulator for V<sub>CCCI</sub> (as shown in Figure 38 and Figure 39)

<sup>(4)</sup> f<sub>OUT</sub> = 1 kHz, using the System Two audio measurement system by Audio Precision in RMS mode with 20-kHz LPF, 400-Hz HPF.

#### **ELECTRICAL CHARACTERISTICS (Continued)**

All specifications at  $T_A = 25$ °C,  $V_{BUS}$ , = 5 V,  $f_S = 44.1$  kHz,  $f_{IN} = 1$  kHz, 16-bit data (unless otherwise noted)

|                  | DADAMETED                                          | RAMETER TEST CONDITIONS PCM |                      | B, PCM2               | 906DB                | UNIT |  |

|------------------|----------------------------------------------------|-----------------------------|----------------------|-----------------------|----------------------|------|--|

|                  | PARAMETER                                          | TEST CONDITIONS             | MIN                  | TYP                   | MAX                  | ONII |  |

| ANALO            | G OUTPUT                                           |                             | 1                    |                       | •                    |      |  |

| Vo               | Output voltage                                     |                             | (                    | 0.6 V <sub>CCCI</sub> |                      | Vp-p |  |

|                  | Center voltage                                     |                             | (                    | 0.5 V <sub>CCCI</sub> |                      | V    |  |

|                  | Load impedance                                     | AC coupling                 | 10                   |                       |                      | kΩ   |  |

| ·                | LDE (common and and and and and and and and and an | –3 dB                       |                      | 250                   |                      | kHz  |  |

|                  | LPF frequency response                             | f = 20 kHz                  |                      | -0.03                 |                      | dB   |  |

| DIGITA           | L FILTER PERFORMANCE                               |                             |                      |                       |                      |      |  |

|                  | Pass band                                          |                             |                      |                       | 0.445 f <sub>s</sub> | Hz   |  |

|                  | Stop band                                          |                             | 0.555 f <sub>s</sub> |                       |                      | Hz   |  |

|                  | Pass-band ripple                                   |                             |                      |                       | ±0.1                 | dB   |  |

|                  | Stop-band attenuation                              |                             | -43                  |                       |                      | dB   |  |

| t <sub>d</sub>   | Delay time                                         |                             |                      | 14.3 f <sub>s</sub>   |                      | s    |  |

| POWER            | R SUPPLY REQUIREMENTS                              |                             | ·                    |                       |                      |      |  |

| V <sub>BUS</sub> | Voltage range                                      |                             | 4.36                 | 5                     | 5.25                 | VDC  |  |

|                  | Complex compant                                    | ADC, DAC operation          |                      | 56                    | 67                   | mA   |  |

|                  | Supply current                                     | Suspend mode <sup>(1)</sup> |                      | 210                   |                      | μΑ   |  |

| D                | Device dissination                                 | ADC, DAC operation          |                      | 280                   | 352                  |      |  |

| $P_D$            | Power dissipation                                  | Suspend mode <sup>(1)</sup> |                      | 1.05                  |                      | mW   |  |

|                  | Internal power supply voltage (2)                  |                             | 3.25                 | 3.35                  | 3.5                  | VDC  |  |

| TEMPE            | RATURE RANGE                                       |                             | -                    |                       | ,                    |      |  |

|                  | Operating temperature                              |                             | -25                  |                       | 85                   | °C   |  |

| $\theta_{JA}$    | Thermal resistance                                 | 28-pin SSOP                 |                      | 100                   |                      | °C/W |  |

<sup>(1)</sup> In USB suspend state

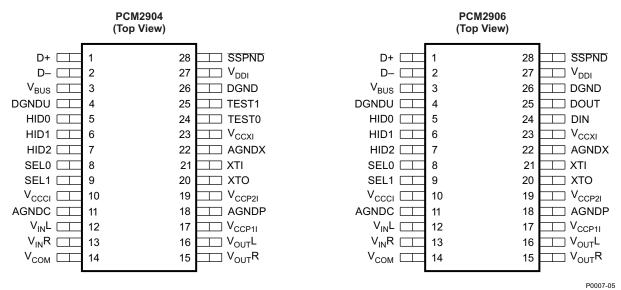

#### **PIN ASSIGNMENTS**

P0007-05

<sup>(2)</sup> Pins 10, 17, 19, 23, 27: V<sub>CCCI</sub>, V<sub>CCP1I</sub>, V<sub>CCP2I</sub>, V<sub>CCXI</sub>, V<sub>DDI</sub>

#### Table 1. PCM2904 TERMINAL FUNCTIONS

| TERM               | TERMINAL |     | DECORPORTION                                                  |

|--------------------|----------|-----|---------------------------------------------------------------|

| NAME               | NO.      | 1/0 | DESCRIPTION                                                   |

| AGNDC              | 11       | _   | Analog ground for codec                                       |

| AGNDP              | 18       | _   | Analog ground for PLL                                         |

| AGNDX              | 22       | -   | Analog ground for oscillator                                  |

| D-                 | 2        | I/O | USB differential input/output minus <sup>(1)</sup>            |

| D+                 | 1        | I/O | USB differential input/output plus <sup>(1)</sup>             |

| DGND               | 26       | _   | Digital ground                                                |

| DGNDU              | 4        | -   | Digital ground for USB transceiver                            |

| HID0               | 5        | I   | HID key state input (mute), active-high (2)                   |

| HID1               | 6        | I   | HID key state input (volume up), active-high <sup>(2)</sup>   |

| HID2               | 7        | I   | HID key state input (volume down), active-high <sup>(2)</sup> |

| SEL0               | 8        | I   | Must be set to high <sup>(3)</sup>                            |

| SEL1               | 9        | I   | Must be set to high <sup>(3)</sup>                            |

| SSPND              | 28       | 0   | Suspend flag, active-low (Low: suspend, High: operational)    |

| TEST0              | 24       | I   | Test pin, must be connected to GND                            |

| TEST1              | 25       | 0   | Test pin, must be left open                                   |

| $V_{BUS}$          | 3        | _   | Connect to USB power (V <sub>BUS</sub> )                      |

| V <sub>CCCI</sub>  | 10       | _   | Internal analog power supply for codec <sup>(4)</sup>         |

| V <sub>CCP1I</sub> | 17       | _   | Internal analog power supply for PLL <sup>(4)</sup>           |

| V <sub>CCP2I</sub> | 19       | _   | Internal analog power supply for PLL <sup>(4)</sup>           |

| V <sub>CCXI</sub>  | 23       | _   | Internal analog power supply for oscillator <sup>(4)</sup>    |

| V <sub>COM</sub>   | 14       | _   | Common for ADC/DAC (V <sub>CCCI</sub> /2) <sup>(4)</sup>      |

| $V_{DDI}$          | 27       | _   | Internal digital power supply <sup>(4)</sup>                  |

| $V_{IN}L$          | 12       | I   | ADC analog input for L-channel                                |

| $V_{IN}R$          | 13       | I   | ADC analog input for R-channel                                |

| V <sub>OUT</sub> L | 16       | 0   | DAC analog output for L-channel                               |

| V <sub>OUT</sub> R | 15       | 0   | DAC analog output for R-channel                               |

| XTI                | 21       | I   | Crystal oscillator input <sup>(5)</sup>                       |

| XTO                | 20       | 0   | Crystal oscillator output                                     |

<sup>(1)</sup> LV-TTL leveL

<sup>3.3-</sup>V CMOS-level input with internal pulldown. This pin informs the PC of serviceable control signals such as mute, volume up, or volume down, which have no direct connection with the internal DAC or ADC. See the *Interface #3* and *End-Points sections*.

TTL Schmitt trigger, 5-V tolerant

Connect a decoupling capacitor to GND. 3.3-V CMOS-level input

#### Table 2. PCM2906 TERMINAL FUNCTIONS

| TERMINAL           |     | 1/0 | DESCRIPTION                                                |

|--------------------|-----|-----|------------------------------------------------------------|

| NAME               | NO. | 1/0 | DESCRIPTION                                                |

| AGNDC              | 11  | _   | Analog ground for codec                                    |

| AGNDP              | 18  | _   | Analog ground for PLL                                      |

| AGNDX              | 22  | _   | Analog ground for oscillator                               |

| D-                 | 2   | I/O | USB differential input/output minus <sup>(1)</sup>         |

| D+                 | 1   | I/O | USB differential input/output plus <sup>(1)</sup>          |

| DGND               | 26  | _   | Digital ground                                             |

| DGNDU              | 4   | _   | Digital ground for USB transceiver                         |

| DIN                | 24  | I   | S/PDIF input <sup>(2)</sup>                                |

| DOUT               | 25  | 0   | S/PDIF output                                              |

| HID0               | 5   | I   | HID key state input (mute), active-high (3)                |

| HID1               | 6   | I   | HID key state input (volume up), active-high (3)           |

| HID2               | 7   | I   | HID key state input (volume down), active-high (3)         |

| SEL0               | 8   | I   | Must be set to high <sup>(4)</sup>                         |

| SEL1               | 9   | I   | Must be set to high <sup>(4)</sup>                         |

| SSPND              | 28  | 0   | Suspend flag, active-low (Low: suspend, High: operational) |

| $V_{BUS}$          | 3   | _   | Connect to USB power (V <sub>BUS</sub> )                   |

| V <sub>CCCI</sub>  | 10  | _   | Internal analog power supply for codec <sup>(5)</sup>      |

| V <sub>CCP1I</sub> | 17  | _   | Internal analog power supply for PLL <sup>(5)</sup>        |

| V <sub>CCP2I</sub> | 19  | _   | Internal analog power supply for PLL <sup>(5)</sup>        |

| $V_{CCXI}$         | 23  | _   | Internal analog power supply for oscillator <sup>(5)</sup> |

| $V_{COM}$          | 14  | _   | Common for ADC/DAC (V <sub>CCCI</sub> /2) <sup>(5)</sup>   |

| $V_{DDI}$          | 27  | _   | Internal digital power supply <sup>(5)</sup>               |

| $V_{IN}L$          | 12  | 1   | ADC analog input for L-channel                             |

| $V_{IN}R$          | 13  | 1   | ADC analog input for R-channel                             |

| $V_{OUT}L$         | 16  | 0   | DAC analog output for L-channel                            |

| $V_{OUT}R$         | 15  | 0   | DAC analog output for R-channel                            |

| XTI                | 21  | I   | Crystal oscillator input <sup>(6)</sup>                    |

| XTO                | 20  | 0   | Crystal oscillator output                                  |

- (1) LV-TTL level

- 3.3-V CMOS-level input with internal pulldown, 5-V tolerant

3.3-V CMOS-level input with internal pulldown. This pin informs the PC of serviceable control signals such as mute, volume up, or volume down, which have no direct connection with the internal DAC or ADC. See the *Interface #3* and *End-Points sections*.

TTL Schmitt trigger, 5-V tolerant

Connect a decoupling capacitor to GND.

3.3-V CMOS-level input

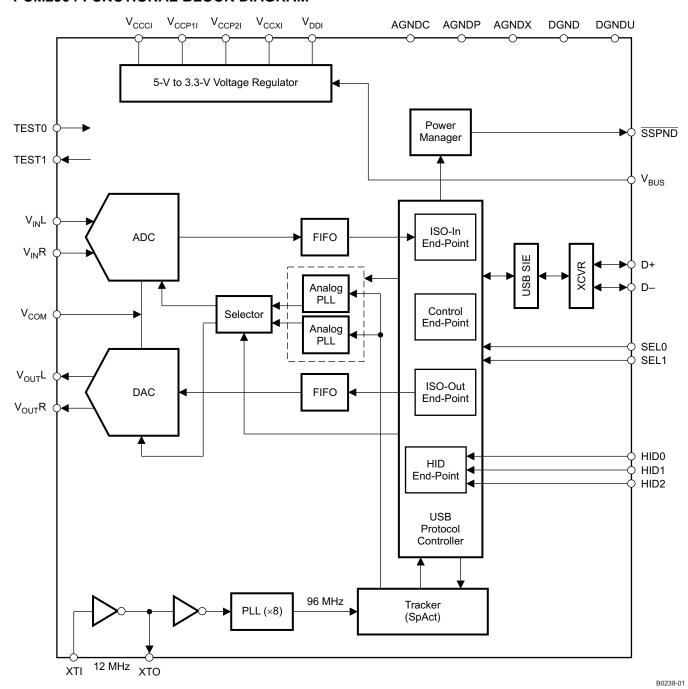

#### PCM2904 FUNCTIONAL BLOCK DIAGRAM

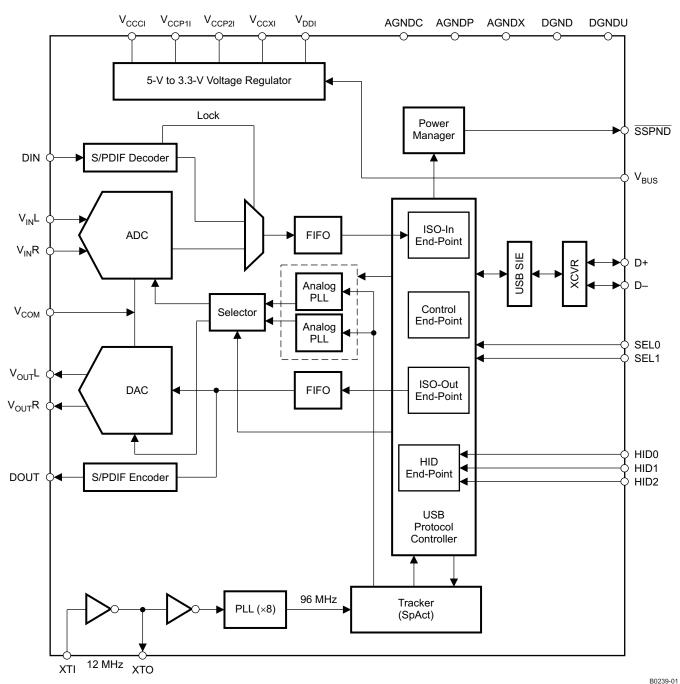

#### PCM2906 FUNCTIONAL BLOCK DIAGRAM

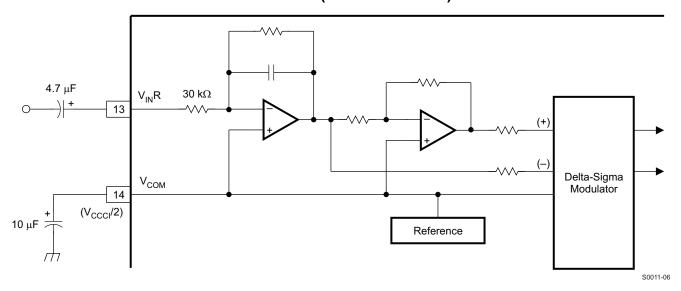

# **BLOCK DIAGRAM OF ANALOG FRONT-END (RIGHT CHANNEL)**

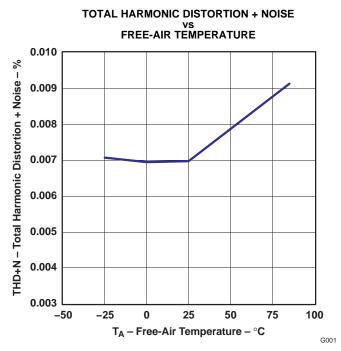

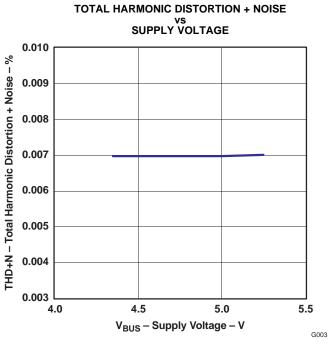

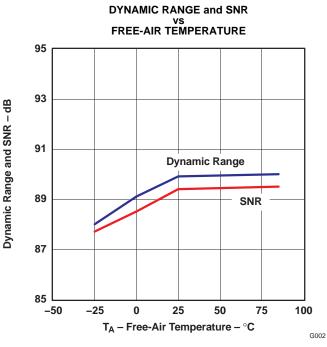

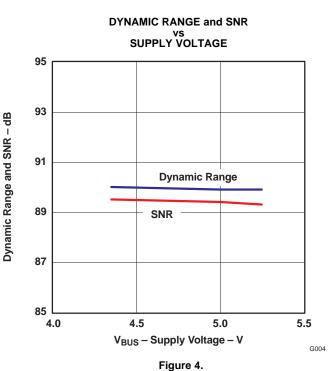

#### **TYPICAL CHARACTERISTICS**

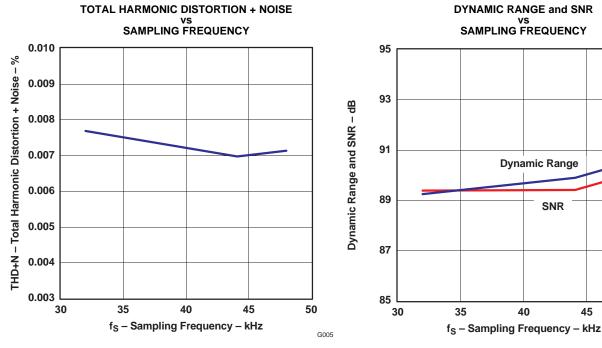

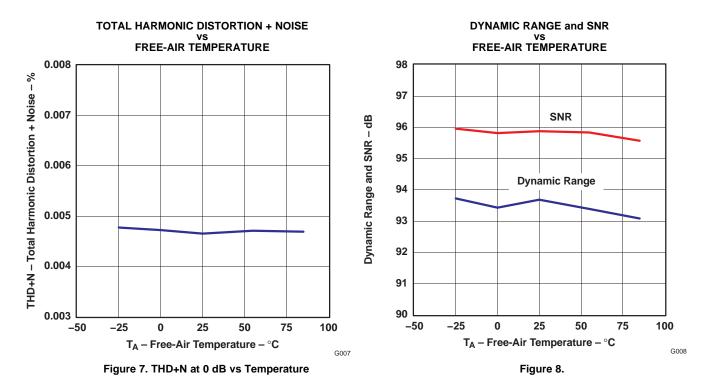

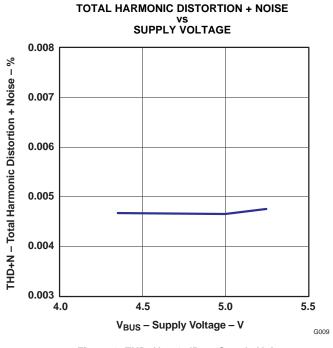

All specifications at  $T_A = 25$ °C,  $V_{BUS} = 5$  V,  $f_s = 44.1$  kHz,  $f_{IN} = 1$  kHz, 16-bit data, using REG103xA-A, unless otherwise noted.

#### **ADC**

Figure 1. THD+N at -0.5 dB vs Temperature

Figure 3. THD+N at -0.5 dB vs Supply Voltage

Figure 2.

Copyright © 2002–2007, Texas Instruments Incorporated

All specifications at  $T_A = 25$ °C,  $V_{BUS} = 5$  V,  $f_s = 44.1$  kHz,  $f_{IN} = 1$  kHz, 16-bit data, using REG103xA-A, unless otherwise noted.

Figure 5. THD+N at -0.5 dB vs Sampling Frequency

#### Figure 6.

45

50

#### DAC

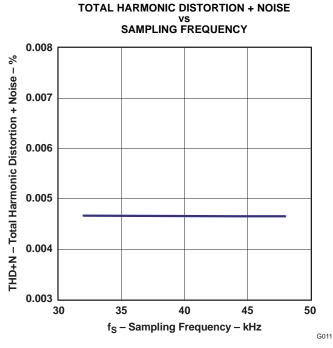

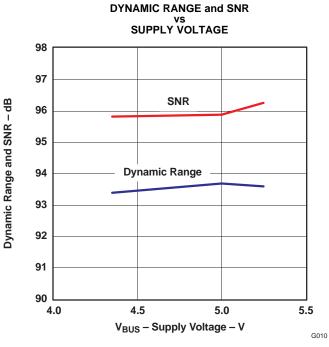

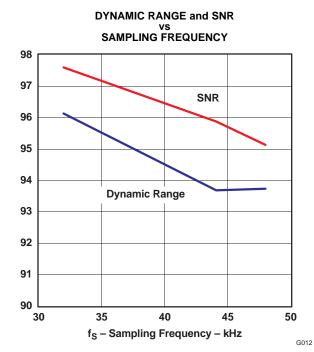

All specifications at  $T_A = 25$ °C,  $V_{BUS} = 5$  V,  $f_s = 44.1$  kHz,  $f_{IN} = 1$  kHz, 16-bit data, using REG103xA-A, unless otherwise noted.

Figure 11. THD+N at 0 dB vs Sampling Frequency

Figure 10.

Figure 12.

Dynamic Range and SNR - dB

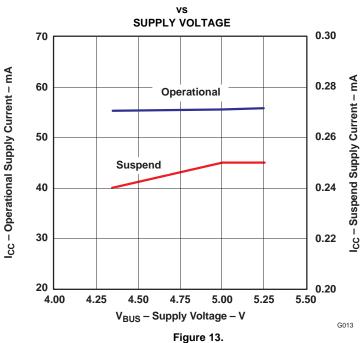

All specifications at  $T_A = 25$ °C,  $V_{BUS} = 5$  V,  $f_s = 44.1$  kHz,  $f_{IN} = 1$  kHz, 16-bit data, using REG103xA-A, unless otherwise noted.

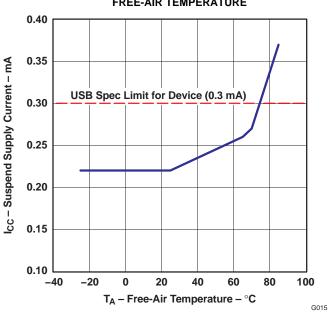

#### **SUPPLY CURRENT**

# OPERATIONAL SUPPLY CURRENT vs

# SAMPLING FREQUENCY 70 70 60 50 40 20 30 35 40 45 50 f<sub>S</sub> - Sampling Frequency - kHz

Figure 14. Supply Current vs Sampling Frequency, ADC and DAC at Same f<sub>S</sub>

# SUSPEND SUPPLY CURRENT vs FREE-AIR TEMPERATURE

Figure 15. Supply Current vs Temperature in Suspend Mode

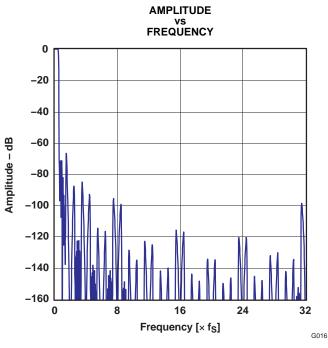

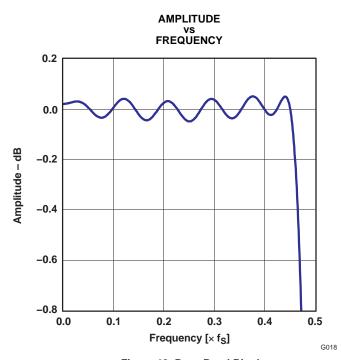

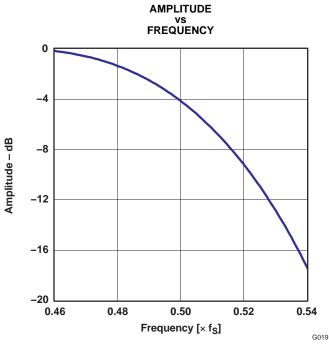

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{BUS} = 5$  V,  $f_s = 44.1$  kHz,  $f_{IN} = 1$  kHz, 16-bit data, unless otherwise noted.

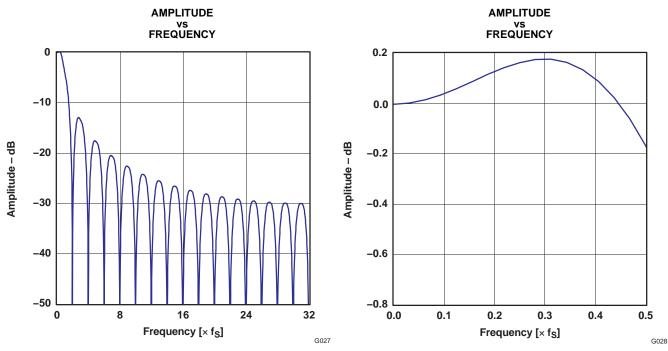

#### ADC DIGITAL DECIMATION FILTER FREQUENCY RESPONSE

**AMPLITUDE** vs FREQUENCY 0 -10 -20 -30 Amplitude – dB -40 -50 -60 -70 -80 -90 -100 0.0 0.2 0.4 0.6 0.8 1.0 Frequency [x fs] G017

Figure 16. Overall Characteristic

Figure 17. Stop-Band Attenuation

Figure 18. Pass-Band Ripple

Figure 19. Transition-Band Response

All specifications at  $T_A = 25$ °C,  $V_{BUS} = 5$  V,  $f_s = 44.1$  kHz,  $f_{IN} = 1$  kHz, 16-bit data, unless otherwise noted.

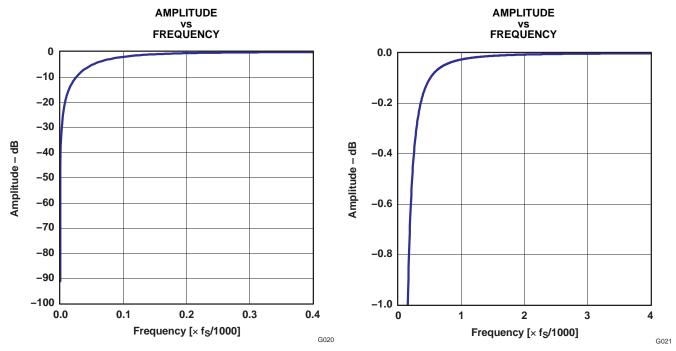

#### ADC DIGITAL HIGH-PASS FILTER FREQUENCY RESPONSE

Figure 20. Stop-Band Characteristic

Figure 21. Pass-Band Characteristic

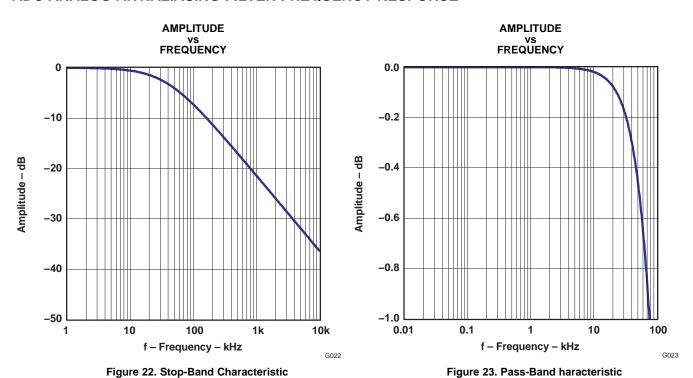

#### ADC ANALOG ANTIALIASING FILTER FREQUENCY RESPONSE

Submit Documentation Feedback

All specifications at  $T_A = 25$ °C,  $V_{BUS} = 5$  V,  $f_s = 44.1$  kHz,  $f_{IN} = 1$  kHz, 16-bit data, unless otherwise noted.

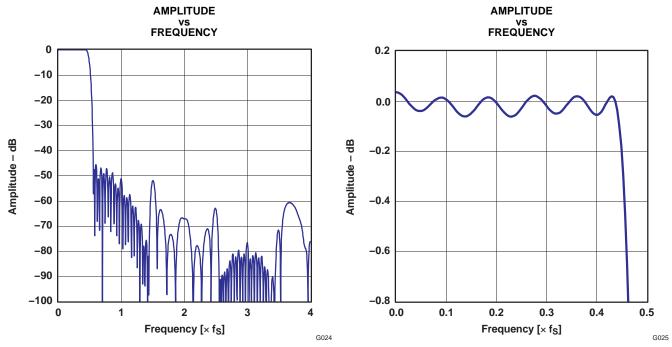

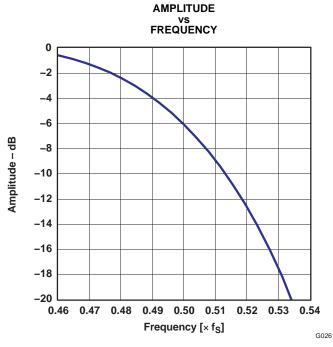

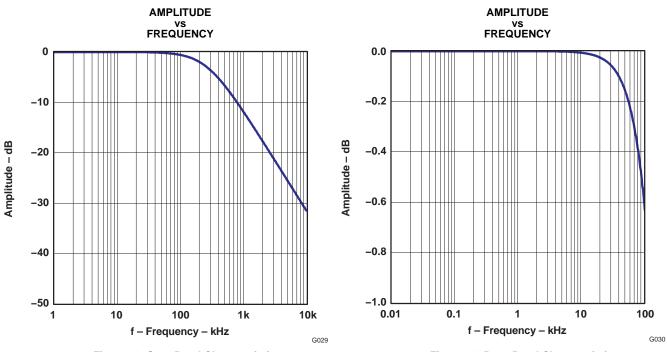

#### DAC DIGITAL INTERPOLATION AND DE-EMPHASIS FILTER FREQUENCY RESPONSE

Figure 24. Stop-Band Attenuation

Figure 25. Pass-Band Ripple

Figure 26. Transition-Band Response

All specifications at  $T_A = 25$ °C,  $V_{BUS} = 5$  V,  $f_s = 44.1$  kHz,  $f_{IN} = 1$  kHz, 16-bit data, unless otherwise noted.

#### DAC ANALOG FIR FILTER FREQUENCY RESPONSE

Figure 27. Stop-Band Characteristic

Figure 28. Pass-Band Characteristic

#### DAC ANALOG LOW-PASS FILTER FREQUENCY RESPONSE

Figure 29. Stop-Band Characteristic

Figure 30. Pass-Band Characteristic

#### **USB INTERFACE**

Control data and audio data are transferred to the PCM2904/2906 via D+ (pin 1) and D- (pin 2). All data to/from the PCM2904/2906 is transferred at full speed. The device descriptor contains the information described in Table 3. The device descriptor can be modified on request; contact a Texas Instruments representative about the details.

**Table 3. Device Descriptor**

| USB revision                    | 1.1 compliant                                  |

|---------------------------------|------------------------------------------------|

| Device class                    | 0x00 (device defined interface level)          |

| Device sub class                | 0x00 (not specified)                           |

| Device protocol                 | 0x00 (not specified)                           |

| Max packet size for end-point 0 | 8 byte                                         |

| Vendor ID                       | 0x08BB (default value, can be modified)        |

| Product ID                      | 0x2904/0x2906 (default value, can be modified) |

| Device release number           | 1.0 (0x0100)                                   |

| Number of configurations        | 1                                              |

| Vendor string                   | String #1 (see Table 5)                        |

| Product string                  | String #2 (see Table 5)                        |

| Serial number                   | Not supported                                  |

The configuration descriptor contains the information described in Table 4. The configuration descriptor can be modified on request; contact a Texas Instruments representative about the details.

**Table 4. Configuration Descriptor**

| Interface       | Four interfaces                               |  |  |

|-----------------|-----------------------------------------------|--|--|

| Power attribute | 0x80 (Bus powered, no remote wakeup)          |  |  |

| Max power       | 0xFA (500 mA. Default value, can be modified) |  |  |

The string descriptor contains the information described in Table 5. The string descriptor can be modified on request; contact a Texas Instruments representative about the details.

**Table 5. String Descriptor**

| #0 | 0x0409                                              |

|----|-----------------------------------------------------|

| #1 | Burr-Brown from TI (default value, can be modified) |

| #2 | USB audio codec (default value, can be modified)    |

#### **DEVICE CONFIGURATION**

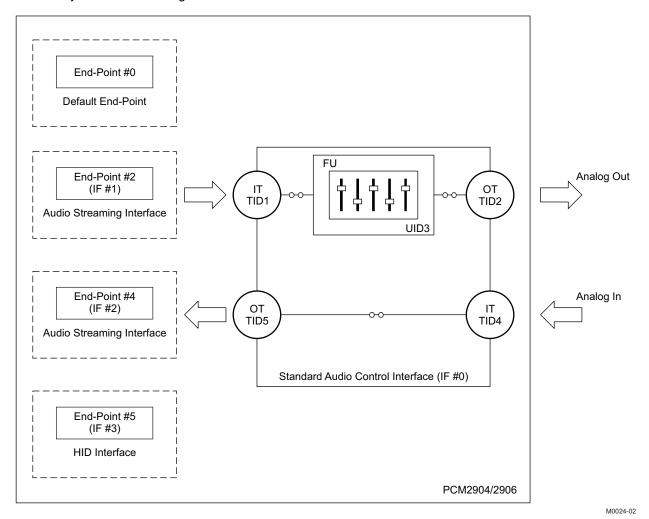

Figure 31 illustrates the USB audio function topology. The PCM2904/2906 has four interfaces. Each interface is constructed by alternative settings.

Figure 31. USB Audio Function Topology

#### Interface #0

Interface #0 is the control interface. Alternative setting #0 is the only possible setting for interface #0. Alternative setting #0 describes the standard audio control interface. The audio control interface is constructed by a terminal. The PCM2904/2906 has the following five terminals.

- Input terminal (IT #1) for isochronous-out stream

- Output terminal (OT #2) for audio analog output

- Feature unit (FU #3) for DAC digital attenuator

- Input terminal (IT #4) for audio analog input

- Output terminal (OT #5) for isochronous-in stream

Input terminal #1 is defined as a *USB stream* (terminal type 0x0101). Input terminal #1 can accept 2-channel audio streams consisting of left and right channels. Output terminal #2 is defined as a *speaker* (terminal type 0x0301). Input terminal #4 is defined as a *microphone* (terminal type 0x0201). Output terminal #5 is defined as a *USB stream* (terminal type 0x0101). Output terminal #5 can generate 2-channel audio streams consisting of left and right channels. Feature unit #3 supports the following sound control features.

- Volume control

- Mute control

The built-in digital volume controller can be manipulated by an audio-class-specific request from 0 dB to -64 dB in steps of 1 dB. Each channel can be set for different values. The master volume control is not supported. A request to the master volume is stalled and ignored. The built-in digital mute controller can be manipulated by audio-class-specific request. A master mute control request is acceptable. A request to an individual channel is stalled and ignored.

#### Interface #1

Interface #1 is the audio streaming data-out interface. Interface #1 has the following seven alternative settings. Alternative setting #0 is the zero-bandwidth setting. All other alternative settings are operational settings.

| ALTERNATIVE<br>SETTING | DATA FORMAT |        |                      | TRANSFER MODE | SAMPLING RATE<br>(kHz) |

|------------------------|-------------|--------|----------------------|---------------|------------------------|

| 00                     |             |        | Zero bandwid         | th            |                        |

| 01                     | 16 bit      | Stereo | 2s complement (PCM)  | Adaptive      | 32, 44.1, 48           |

| 02                     | 16 bit      | Mono   | 2s complement (PCM)  | Adaptive      | 32, 44.1, 48           |

| 03                     | 8 bit       | Stereo | 2s complement (PCM)  | Adaptive      | 32, 44.1, 48           |

| 04                     | 8 bit       | Mono   | 2s complement (PCM)  | Adaptive      | 32, 44.1, 48           |

| 05                     | 8 bit       | Stereo | Offset binary (PCM8) | Adaptive      | 32, 44.1, 48           |

| 06                     | 8 bit       | Mono   | Offset binary (PCM8) | Adaptive      | 32, 44.1, 48           |

#### Interface #2

Interface #2 is the audio streaming data-in interface. Interface #2 has the following 19 alternative settings. Alternative setting #0 is the zero-bandwidth setting. All other alternative settings are operational settings.

| ALTERNATIVE<br>SETTING |        | DA     | TA FORMAT           | TRANSFER MODE | SAMPLING RATE<br>(kHz) |

|------------------------|--------|--------|---------------------|---------------|------------------------|

| 00                     |        |        | ZERO BANDW          | /IDTH         |                        |

| 01                     | 16 bit | Stereo | 2s complement (PCM) | Asynchronous  | 48                     |

| 02                     | 16 bit | Mono   | 2s complement (PCM) | Asynchronous  | 48                     |

| 03                     | 16 bit | Stereo | 2s complement (PCM) | Asynchronous  | 44.1                   |

| 04                     | 16 bit | Mono   | 2s complement (PCM) | Asynchronous  | 44.1                   |

| 05                     | 16 bit | Stereo | 2s complement (PCM) | Asynchronous  | 32                     |

| 06                     | 16 bit | Mono   | 2s complement (PCM) | Asynchronous  | 32                     |

| 07                     | 16 bit | Stereo | 2s complement (PCM) | Asynchronous  | 22.05                  |

| 08                     | 16 bit | Mono   | 2s complement (PCM) | Asynchronous  | 22.05                  |

| 09                     | 16 bit | Stereo | 2s complement (PCM) | Asynchronous  | 16                     |

| 0A                     | 16 bit | Mono   | 2s complement (PCM) | Asynchronous  | 16                     |

| 0B                     | 8 bit  | Stereo | 2s complement (PCM) | Asynchronous  | 16                     |

| 0C                     | 8 bit  | Mono   | 2s complement (PCM) | Asynchronous  | 16                     |

| 0D                     | 8 bit  | Stereo | 2s complement (PCM) | Asynchronous  | 8                      |

| 0E                     | 8 bit  | Mono   | 2s complement (PCM) | Asynchronous  | 8                      |

| 0F                     | 16 bit | Stereo | 2s complement (PCM) | Synchronous   | 11.025                 |

| 10                     | 16 bit | Mono   | 2s complement (PCM) | Synchronous   | 11.025                 |

| 11                     | 8 bit  | Stereo | 2s complement (PCM) | Synchronous   | 11.025                 |

| 12                     | 8 bit  | Mono   | 2s complement (PCM) | Synchronous   | 11.025                 |

#### Interface #3

Interface #3 is the interrupt data-in interface. Alternative setting #0 is the only possible setting for interface #3. Interface #3 constructs the HID consumer control device. Interface #3 reports the following three key statuses.

- Mute (0xE209)

- Volume up (0xE909)

- Volume down (0xEA09)

#### **End-Points**

The PCM2904/2906 has the following four end-points.

- Control end-point (EP #0)

- Isochronous-out audio data stream end-point (EP #2)

- Isochronous-in audio data stream end-point (EP #4)

- HID end-point (EP #5)

The control end-point is a default end-point. The control end-point is used to control all functions of the PCM2904/2906 by the standard USB request and USB audio class specific request from the host. The isochronous-out audio data stream end-point is an audio sink end-point, which receives the PCM audio data. The isochronous-out audio data stream end-point accepts the adaptive transfer mode. The isochronous-in audio data stream end-point is an audio source end-point that transmits the PCM audio data. The isochronous-in audio data stream end-point uses the asynchronous transfer mode. The HID end-point is an interrupt-in end-point. The HID end-point reports HID0, HID1, and HID2 pin status every 32 ms.

The human interface device (HID) pins are defined as consumer control devices. The HID function is designed as an independent end-point from both isochronous-in and -out end-points. This means that the result obtained from the HID operation depends on the host software. Typically, the HID function is used as a primary audio-out device.

#### **Clock and Reset**

The PCM2904/2906 requires a 12-MHz ( $\pm$ 500 ppm) clock for the USB and audio functions. The clock can be generated by a built-in oscillator with a 12-MHz crystal resonator. The 12-MHz crystal resonator must be connected to XTI (pin 21) and XTO (pin 20) with one high-value (1-M $\Omega$ ) resistor and two small capacitors, the capacitance of which depends on the load capacitance of the crystal resonator. An external clock can be supplied to XTI (pin 21). If an external clock is used, XTO (pin 20) must be left open. Because there is no clock disabling signal, use of the external clock supply is not recommended. SSPND (pin 28) is unable to use clock disabling.

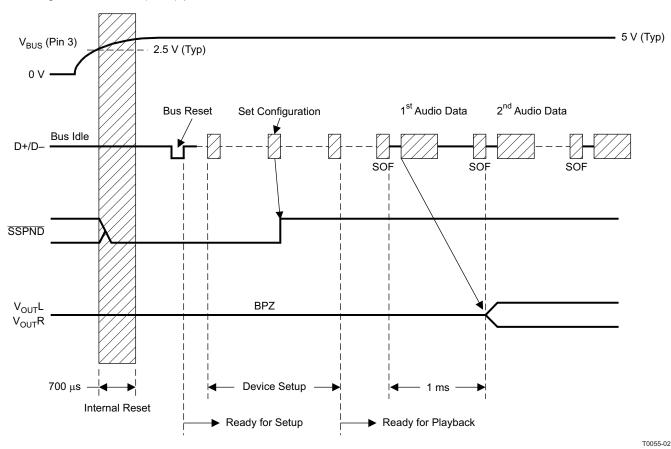

The PCM2904/2906 has an internal power-on reset circuit, which is triggered automatically when  $V_{BUS}$  (pin 3) exceeds 2.5 V typical (2.7 V to 2.2 V). About 700  $\mu$ s is required until internal reset release.

#### **Digital Audio Interface (PCM2906)**

The PCM2906 employs S/PDIF for both input and output. Isochronous-out data from the host is encoded to the S/PDIF output and the DAC analog output. Input data is selected from either the S/PDIF or ADC analog input. When the device detects S/PDIF input and successfully locks the received data, the isochronous-in transfer data source automatically selected is S/PDIF; otherwise, the data source selected is the ADC analog input.

#### Supported Input Data (PCM2906)

The following data formats are accepted by S/PDIF for input and output. All other data formats are unusable as S/PDIF.

- 48-kHz 16-bit stereo

- 44.1-kHz 16-bit stereo

- 32-kHz 16-bit stereo

Mismatch between the input data format and the host command may cause unexpected results, with the following exceptions:

- Recording in monaural format from stereo data input at the same data rate

- Recording in 8-bit format from 16-bit data input at the same data rate

A combination of the two foregoing conditions is not accepted.

For playback, all possible data-rate sources are converted to the 16-bit stereo format at the same source data rate.

#### **Channel Status Information (PCM2906)**

The channel status information is fixed as consumer application, PCM mode, copyright, and digital/digital converter. All other bits are fixed as 0s except for the sample frequency, which is set automatically according to the data received through the USB.

#### **Copyright Management (PCM2906)**

Isochronous-in data is affected by the serial copy management system (SCMS). When the control bit indicates that the received digital audio data is original, the input digital audio data is transferred to the host. If the data is indicated as first generation or higher, the transferred data is routed to the analog input.

Digital audio data output is always encoded as original with SCMS control.

The implementation of this feature is optional. It is the designer's responsibility to determine whether to implement this feature in a product or not.

#### INTERFACE SEQUENCE

#### Power-On, Attach, and Playback Sequence

The PCM2904/2906 is ready for setup when the reset sequence has finished and the USB device is attached. After a connection has been established by setup, the PCM2904/PCM2906 is ready to accept USB audio data. While waiting for the audio data (idle state), the analog output is set to bipolar zero (BPZ).

When receiving the audio data, the PCM2904/2906 stores the first audio packet, which contained 1-ms audio data, into the internal storage buffer. The PCM2904/2906 starts playing the audio data when detecting the following start-of-frame (SOF) packet.

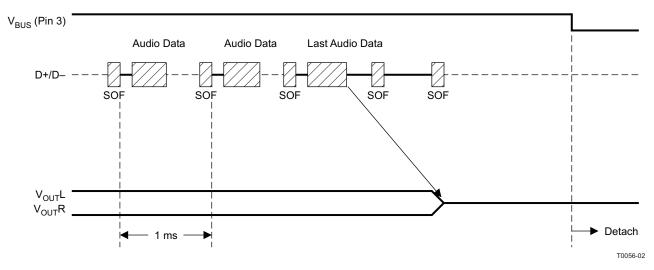

Figure 32. Initial Sequence

#### Play, Stop, and Detach Sequence

When the host finishes or aborts the playback, the PCM2904/2906 stops playing after the last audio data has played.

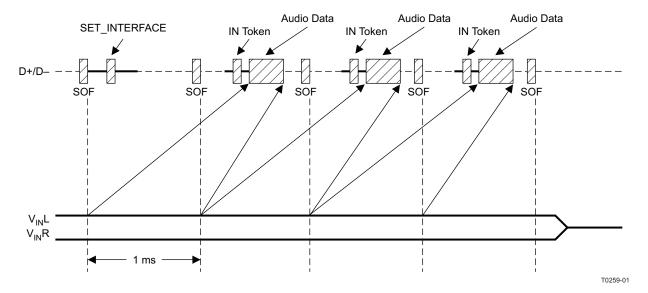

#### **Record Sequence**

The PCM2904/2906 starts audio capture into the internal memory after receiving the SET\_INTERFACE command.

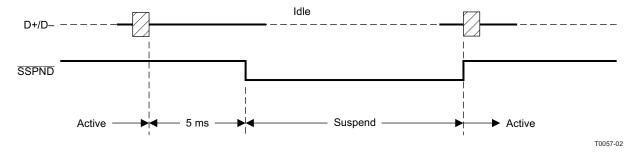

#### Suspend and Resume Sequence

The PCM2904/2906 enters the suspend state after a constant idle state on the USB bus, approximately 5 ms. While the PCM2904/2906 enters the suspend state, the SSPND flag (pin 28) is asserted. The PCM2904/2906 wakes up immediately on detecting a non-idle state on the USB.

Figure 33. Play, Stop, and Detach

Figure 34. Record Sequence

Figure 35. Suspend and Resume

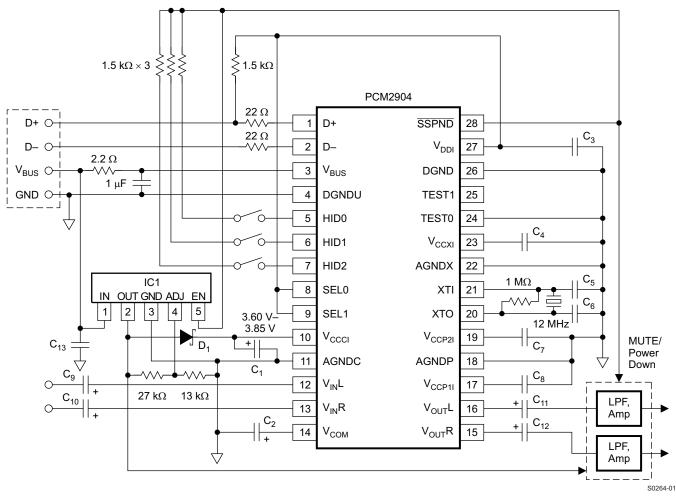

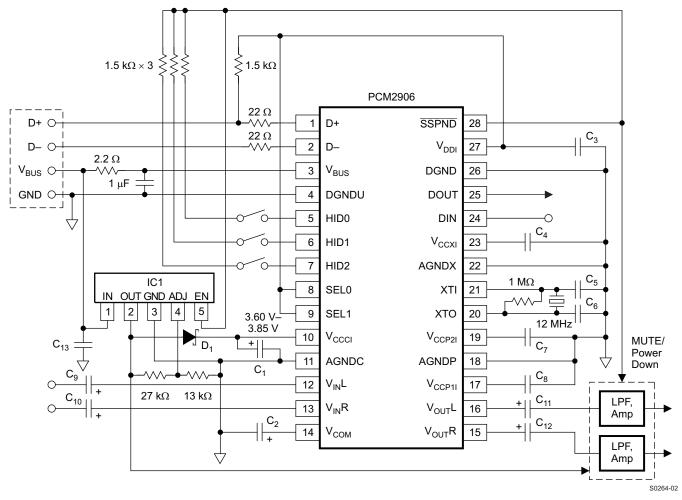

#### PCM2904 TYPICAL CIRCUIT CONNECTION 1

Figure 36 illustrates a typical circuit connection for a simple application. The circuit illustrated is for information only. The whole board design should be considered to meet the USB specification as a USB compliant product.

NOTE: C<sub>1</sub>, C<sub>2</sub>: 10 μF

$C_3,\,C_4,\,C_7,\,C_8,\,C_{13};\,1~\mu F$  (These capacitors must be less than 2  $\mu F.)$

C<sub>5</sub>, C<sub>6</sub>: 10 pF to 33 pF (depending on crystal resonator)

C<sub>9</sub>, C<sub>10</sub>, C<sub>11</sub>, C<sub>12</sub>: The capacitance may vary depending on design.

IC1: REG103xA-A (TI) or equivalent. Analog performance may vary depending on IC1.

D<sub>1</sub>: Schottky barrier diode ( $V_F \le 350 \text{ mV}$  at 10 mA,  $I_R \le 2 \mu A$  at 4 V)

Figure 36. Bus-Powered Configuration for High-Performance PCM2904 Application

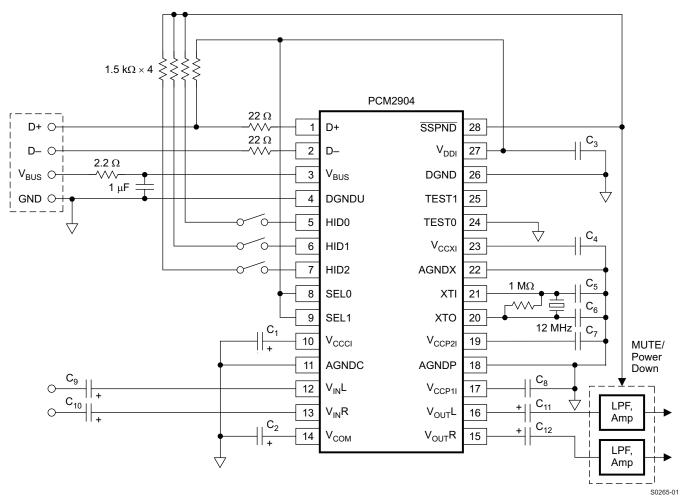

#### PCM2906 TYPICAL CIRCUIT CONNECTION 1

Figure 37 illustrates a typical circuit connection for a simple application. The circuit illustrated is for information only. The whole board design should be considered to meet the USB specification as a USB compliant product.

NOTE:  $C_1$ ,  $C_2$ : 10  $\mu F$

$C_3,\,C_4,\,C_7,\,C_8,\,C_{13};\,1~\mu F$  (These capacitors must be less than 2  $\mu F.)$

C<sub>5</sub>, C<sub>6</sub>: 10 pF to 33 pF (depending on crystal resonator)

C<sub>9</sub>, C<sub>10</sub>, C<sub>11</sub>, C<sub>12</sub>: The capacitance may vary depending on design.

IC1: REG103xA-A (TI) or equivalent. Analog performance may vary depending on IC1.

D<sub>1</sub>: Schottky barrier diode ( $V_F \le 350 \text{ mV}$  at 10 mA,  $I_R \le 2 \mu A$  at 4 V)

Figure 37. Bus-Powered Configuration for High-Performance PCM2906 Application

#### PCM2904 TYPICAL CIRCUIT CONNECTION 2

Figure 38 illustrates a typical circuit connection for a simple application. The circuit illustrated is for information only. The whole board design should be considered to meet the USB specification as a USB compliant product.

NOTE:  $C_1$ ,  $C_2$ : 10  $\mu F$

$C_3,\,C_4,\,C_7,\,C_8{:}$  1  $\mu F$  (These capacitors must be less than 2  $\mu F.)$

C<sub>5</sub>, C<sub>6</sub>: 10 pF to 33 pF (depending on crystal resonator)

C<sub>9</sub>, C<sub>10</sub>, C<sub>11</sub>, C<sub>12</sub>: The capacitance may vary depending on design.

In this case, the analog performance of the A/D converter may be degraded.

Figure 38. PCM2904 Bus-Powered Configuration

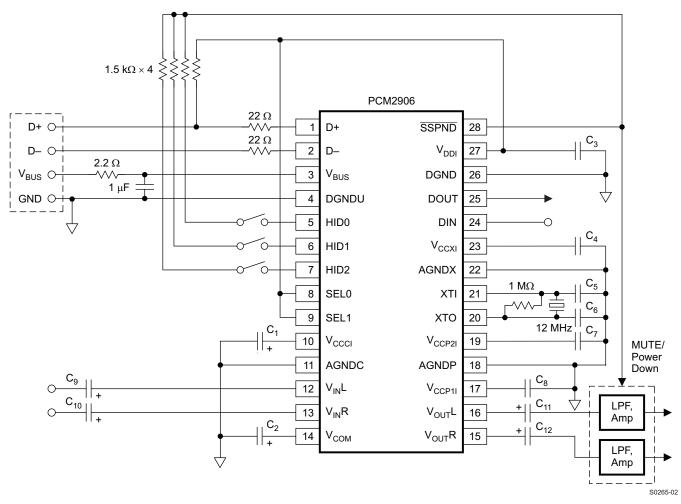

#### PCM2906 TYPICAL CIRCUIT CONNECTION 2

Figure 39 illustrates a typical circuit connection for a simple application. The circuit illustrated is for information only. The whole board design should be considered to meet the USB specification as a USB compliant product.

NOTE:  $C_1$ ,  $C_2$ : 10  $\mu F$

$C_3,\,C_4,\,C_7,\,C_8{:}$  1  $\mu F$  (These capacitors must be less than 2  $\mu F.)$

C<sub>5</sub>, C<sub>6</sub>: 10 pF to 33 pF (depending on crystal resonator)

C<sub>9</sub>, C<sub>10</sub>, C<sub>11</sub>, C<sub>12</sub>: The capacitance may vary depending on design.

In this case, the analog performance of the A/D converter may be degraded.

Figure 39. PCM2906 Bus-Powered Configuration

#### **APPLICATION INFORMATION**

#### **OPERATING ENVIRONMENT**

For current information on the PCM2904/2906 operating environment, see the *Updated Operating Environments* for PCM270X, PCM290X Applications application report, SLAA374.

#### **REVISION HISTORY**

| Cł | Changes from Revision B (March 2007) to Revision C                                                  |    |  |  |  |  |  |  |

|----|-----------------------------------------------------------------------------------------------------|----|--|--|--|--|--|--|

| •  | Deleted operating environment information from data sheet and added reference to application report | 30 |  |  |  |  |  |  |

11-Nov-2025 www.ti.com

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/        | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|----------------|-----------------------|------|---------------|--------------------|--------------|--------------|

|                       | (1)    | (2)           |                |                       | (3)  | Ball material | Peak reflow        |              | (6)          |

|                       |        |               |                |                       |      | (4)           | (5)                |              |              |

| PCM2904DB             | Active | Production    | SSOP (DB)   28 | 47   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | -25 to 85    | PCM2904      |

| PCM2904DB.B           | Active | Production    | SSOP (DB)   28 | 47   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | -25 to 85    | PCM2904      |

| PCM2904DBR            | Active | Production    | SSOP (DB)   28 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -25 to 85    | PCM2904      |

| PCM2904DBR.B          | Active | Production    | SSOP (DB)   28 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -25 to 85    | PCM2904      |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 21-Nov-2025

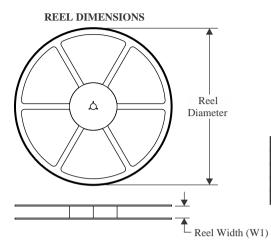

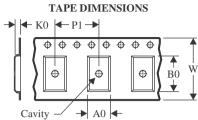

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

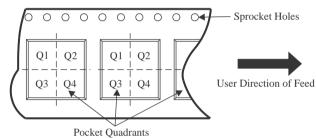

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

|   | Device     | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---|------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| L | PCM2904DBR | SSOP            | DB                 | 28 | 2000 | 330.0                    | 17.4                     | 8.5        | 10.8       | 2.4        | 12.0       | 16.0      | Q1               |

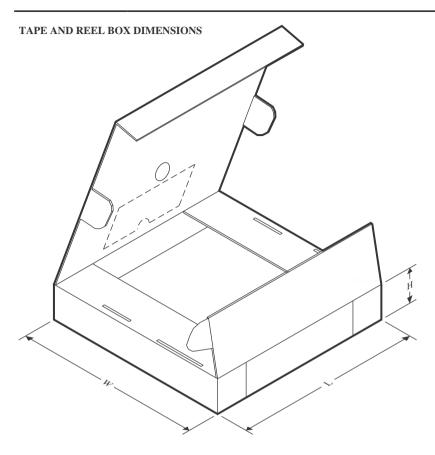

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 21-Nov-2025

#### \*All dimensions are nominal

|   | Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ı | PCM2904DBR | SSOP         | DB              | 28   | 2000 | 336.6       | 336.6      | 28.6        |

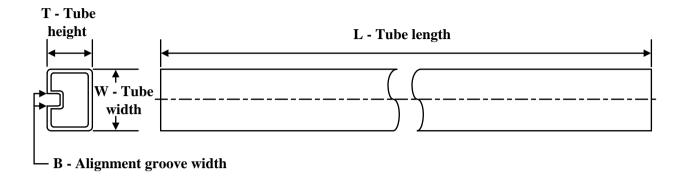

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 21-Nov-2025

#### **TUBE**

#### \*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| PCM2904DB   | DB           | SSOP         | 28   | 47  | 500    | 10.6   | 500    | 9.6    |

| PCM2904DB.B | DB           | SSOP         | 28   | 47  | 500    | 10.6   | 500    | 9.6    |

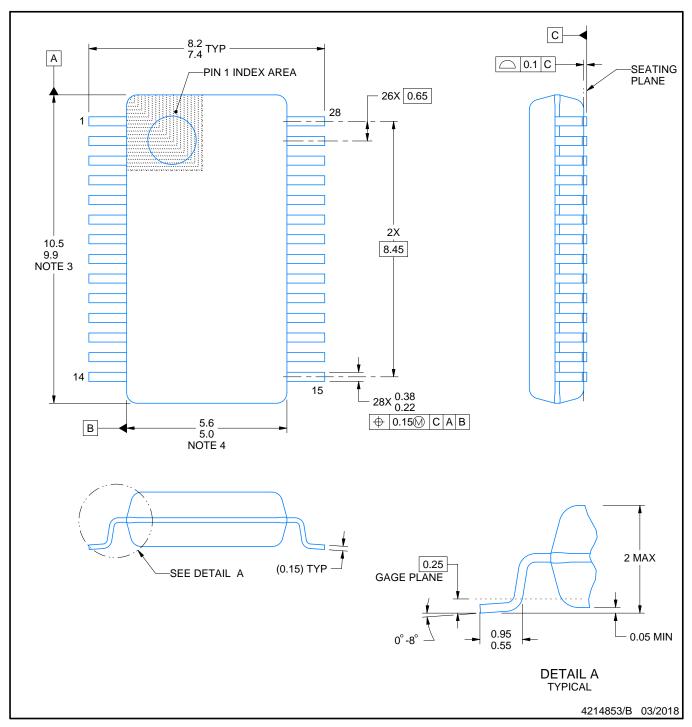

SMALL OUTLINE PACKAGE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-150.

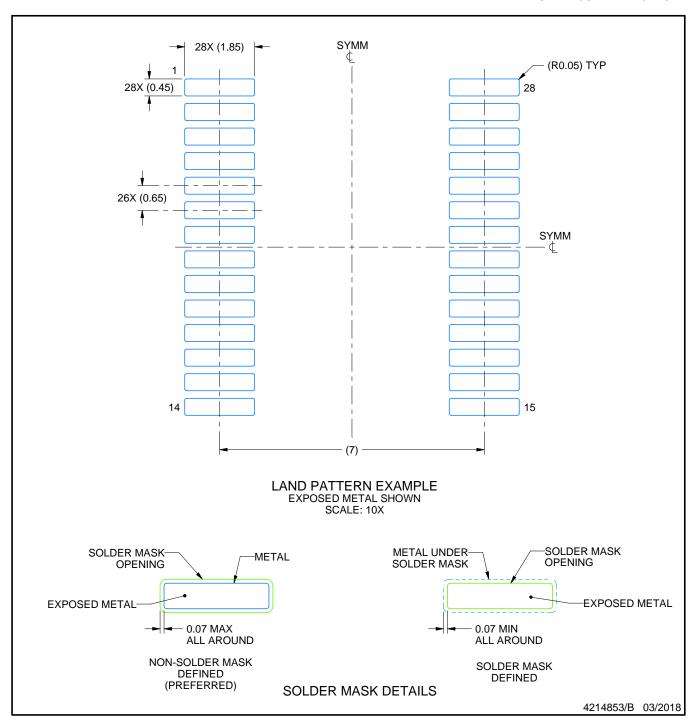

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

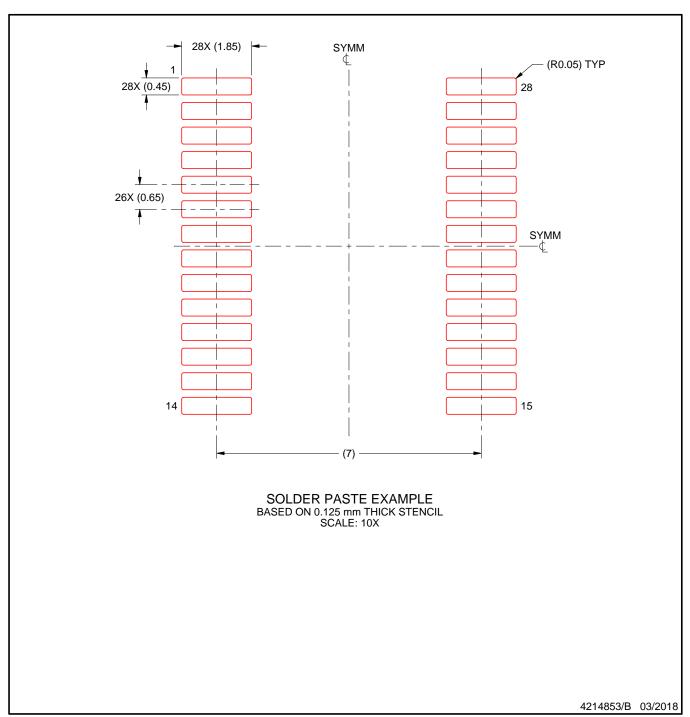

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025