# 双信道 USB3.0 转接驱动器,均衡器

查询样片: SN65LVPE512

# 特性

- 单线路 USB 3.0 均衡器,转接驱动器

- 可选均衡、去加重以及输出摆幅控制

- 集成型端接

- 支持热插拔

- 低有源功耗(**U0** 状态)

- 315mW (典型值) V<sub>CC</sub> = 3.3V

- USB 3.0 低功耗支持

- 未检测到连接时功耗为 7mW (典型值)

- 在 U2, U3 模式下进行链接时功耗为 70mW (典型值)

- 优异的抖动与损耗补偿性能:

- FR4 上大于 40 英寸的总共 4mil 带状线

- 小封装尺寸 3mm x 3mm 和 4mm x 4mm

24 引脚四方扁平无引线 (QFN) 封装

- 针对静电放电 (ESD) 瞬态的高度保护功能

- 人体模型 (HBM): 5000V

- 充电器件模型 (CDM): 1500V

- 机器模型 (MM): 200V

## 应用范围

• 笔记本、台式机、扩展坞、有源线缆、背板与有源线缆

# 说明

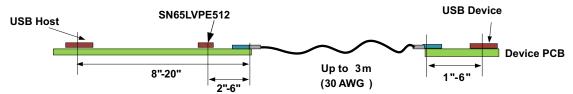

SN65LVPE512 是一款支持 5Gbps 数据速率的双信道、单线路 USB 3.0 转接驱动器与信号调节器。 该器件符合 USB 3.0 技术规范修订版本 1.0,支持针对 USB 3.0 电源管理模式的电气空闲调节与低频率周期信号 (LFPS)。

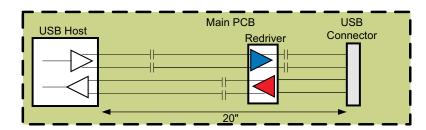

Figure 1. Typical Application

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

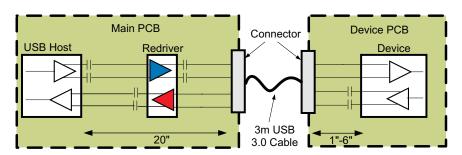

Figure 2. Data Flow Block Diagram

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

# **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range (unless otherwise noted)

|                                     |                                 | VAL         | UE         | UNIT |

|-------------------------------------|---------------------------------|-------------|------------|------|

|                                     |                                 | MIN         | MAX        | UNII |

| Supply voltage range <sup>(2)</sup> | V <sub>CC</sub>                 | -0.5        | 4          | V    |

| Voltage range                       | Differential I/O                | -0.5        | 4          | V    |

|                                     | Control I/O                     | -0.5        | VCC + 0.5  | V    |

|                                     | Human body model <sup>(3)</sup> |             | ±5000      | V    |

| Electrostatic discharge             | Charged-device model (4)        |             | ±1500      | V    |

|                                     | Machine model <sup>(5)</sup>    |             | ±200       | V    |

| Continuous power dissipation        |                                 | See the The | rmal Table |      |

- (1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- All voltage values, except differential voltages, are with respect to network ground terminal.

- Tested in accordance with JEDEC Standard 22, Test Method A114-B Tested in accordance with JEDEC Standard 22, Test Method C101-A

- Tested in accordance with JEDEC Standard 22, Test Method A115-A

## THERMAL INFORMATION

|                         | THERMAL METRIC                               | RGE PACKAGE | RMQ PACKAGE | UNITS |

|-------------------------|----------------------------------------------|-------------|-------------|-------|

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 47.5        | 41.6        |       |

| $\theta_{\text{JCtop}}$ | Junction-to-case (top) thermal resistance    | 51.6        | 37.0        |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 24.6        | 11.5        | 0CAN  |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | 6.4         | 6.4         | °C/W  |

| $\Psi_{\text{JT}}$      | Junction-to-top characterization parameter   | 1.4         | 0.5         |       |

| $\Psi_{JB}$             | Junction-to-board characterization parameter | 24.6        | 11.4        |       |

## THERMAL CHARACTERISTICS

over recommended operating free-air temperature range (unless otherwise noted)

|           | PARAMETER                              | TEST CONDITIONS                                                                                        | MIN | TYP  | MAX | UNIT |

|-----------|----------------------------------------|--------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| $P_D$     | Device power dissipation               | RSVD, EN_RXD, EQ cntrl pins = NC,<br>K28.5 pattern at 5 Gbps, V <sub>ID</sub> = 1000 mV <sub>p-p</sub> |     | 330  | 450 | mW   |

| $P_{Slp}$ | Device power dissipation in sleep mode | EN_RXD = GND                                                                                           |     | 0.03 | 0.4 | mW   |

#### **Device Power**

The SN65LVPE512 is designed to operate from a single 3.3V supply.

# **RECOMMENDED OPERATING CONDITIONS**

|                        | PARAMETER                      | CONDITIONS                                                                | MIN  | TYP  | MAX             | UNITS |

|------------------------|--------------------------------|---------------------------------------------------------------------------|------|------|-----------------|-------|

| V <sub>CC</sub>        | Supply voltage                 |                                                                           | 3    | 3.3  | 3.6             | V     |

| C <sub>COUPLING</sub>  | AC Coupling capacitor          |                                                                           | 75   |      | 200             | nF    |

|                        | Operating free-air temperature |                                                                           | -40  |      | 85              | °C    |

| DEVICE PA              | RAMETERS                       |                                                                           |      |      |                 |       |

| I <sub>CC</sub>        |                                | EN_RXD, RSVD, EQ cntrl = NC,<br>K28.5 pattern at 5 Gbps, VID = 1000mVp-p  |      | 100  | 120             |       |

| $ICC_{Rx.Detect}$      | Supply current                 | In Rx.Detect mode                                                         |      | 2    | 5               | mA    |

| ICC <sub>sleep</sub>   |                                | EN_RXD = GND                                                              |      | 0.01 | 0.1             |       |

| ICC <sub>U2-U3</sub>   |                                | Link in USB low power state                                               |      | 21   |                 | İ     |

|                        | Maximum data rate              |                                                                           |      |      | 5               | Gbps  |

| t <sub>ENB</sub>       | Device enable time             | Sleep mode exit time EN_RXD L $\rightarrow$ H With Rx termination present |      |      | 100             | μs    |

| t <sub>DIS</sub>       | Device disable time            | Sleep mode entry time EN_RXD $H \rightarrow L$                            |      |      | 2               | μs    |

| T <sub>RX.DETECT</sub> | Rx.Detect start event          | Power-up time                                                             |      |      | 100             | μs    |

| CONTROL                | LOGIC                          |                                                                           | ·    |      |                 |       |

| V <sub>IH</sub>        | High level input voltage       |                                                                           | 2.8  |      | V <sub>CC</sub> | V     |

| V <sub>IL</sub>        | Low level input voltage        |                                                                           | -0.3 |      | 0.5             | V     |

| V <sub>HYS</sub>       | Input hysteresis               |                                                                           |      | 150  |                 | mV    |

|                        |                                | OSx, EQx, DEx = $V_{CC}$                                                  |      |      | 30              |       |

| I <sub>IH</sub>        | High level input current       | $EN_RXD = V_{CC}$                                                         |      |      | 1               | μΑ    |

|                        | •                              | $RSVD = V_{CC}$                                                           |      |      | 30              | İ     |

|                        |                                | OSx, EQx, DEx = GND                                                       | -30  |      |                 |       |

| I <sub>IL</sub>        | Low level input current        | EN_RXD = GND                                                              | -30  |      |                 | μA    |

|                        |                                | RSVD = GND                                                                | -1   |      |                 |       |

# **ELECTRICAL CHARACTERISTICS**

over recommended operating conditions (unless otherwise noted)

|                                                | PARAMETER PARAMETER                                                | CONDITIONS                                                                                              | MIN  | TYP      | MAX  | UNITS |

|------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|----------|------|-------|

| RECEIVER AC/D                                  |                                                                    |                                                                                                         |      |          |      |       |

| Vin <sub>diff p-p</sub>                        | RX1, RX2 input voltage swing                                       | AC coupled differential RX peak to peak signal                                                          | 100  |          | 1200 | mVpp  |

| VCM_RX                                         | RX1, RX2 common mode voltage                                       |                                                                                                         |      | 3.3      |      | V     |

| Vin <sub>COM_P</sub>                           | RX1, RX2 AC peak common mode voltage                               | Measured at Rx pins with termination enabled                                                            |      |          | 150  | mVP   |

| Z <sub>CM_RX</sub>                             | DC common mode impedance                                           |                                                                                                         | 18   | 26       | 30   | Ω     |

| $Z_{diff\_RX}$                                 | DC differential input impedance                                    |                                                                                                         | 72   | 80       | 120  | Ω     |

| Z <sub>RX_High_IMP+</sub>                      | DC Input high impedance                                            | Device in sleep mode Rx termination not powered measured with respect to GND over 500mV max             | 50   | 85       |      | kΩ    |

| V <sub>RX-LFPS-DETpp</sub>                     | Low frequency periodic signaling (LFPS) detect threshold           | Measured at receiver pin, below minimum output is squelched, above max input signal is passed to output | 100  |          | 300  | mVpp  |

| RL <sub>RX-DIFF</sub>                          | Differential return loss                                           | 50 MHz – 1.25 GHz                                                                                       | 10   | 11       |      | dB    |

| KX-DIFF                                        |                                                                    | 1.25 GH – 2.5 GHz                                                                                       | 6    | 7        |      |       |

| RL <sub>RX-CM</sub>                            | Common mode return loss                                            | 50 MHz- 2.5 GHz                                                                                         | 11   | 13       |      | dB    |

| TRANSMITTER A                                  | AC/DC                                                              | I                                                                                                       |      |          |      |       |

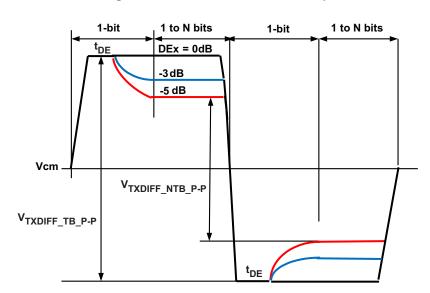

|                                                |                                                                    | $R_L = 100 \Omega \pm 1\%$ , DEx, OSx = NC,<br>Transition Bit                                           | 900  | 1241     | 1500 |       |

| $V_{TXDIFF\_TB\_P-P}$                          |                                                                    | $R_L = 100 \Omega \pm 1\%$ , DEx = NC, OSx = GND<br>Transition Bit                                      |      | 1105     |      | mV    |

|                                                | Differential peak-to-peak output voltage                           | $R_L = 100 \ \Omega \ \pm 1\%$ , DEx = NC, OSx = VCC<br><b>Transition Bit</b>                           | 1324 |          |      |       |

|                                                | (VID = 800, 1200 mVpp, 5 Gbps)                                     | $R_L = 100~\Omega~\pm1\%$ , DEx=NC, OSx = 0,1,NC Non-Transition Bit                                     | 1241 |          |      |       |

| $V_{TXDIFF\_NTB\_P-P}$                         |                                                                    | $R_L = 100~\Omega~\pm1\%,~DEx=0~OSx = 0,1,NC$ Non-Transition Bit                                        |      | 866      |      | mV    |

|                                                |                                                                    | $R_L = 100~\Omega~\pm1\%,~DEx=1~OSx = 0,1,NC$ Non-Transition Bit                                        |      | 691      |      |       |

|                                                |                                                                    | DE1/DE2 = NC                                                                                            |      | 0        |      |       |

| DE                                             | De-emphasis level OS1,2 = NC (for OS1,<br>2 = 1 and 0 see Table 2) | DE1/DE2 = 0 DE1/DE2 = 1                                                                                 |      | -3<br>-5 |      | dB    |

| T <sub>DE</sub>                                | De-emphasis width                                                  |                                                                                                         |      | 0.85     |      | UI    |

| Z <sub>diff TX</sub>                           | DC differential impedance                                          |                                                                                                         | 72   | 90       | 120  | Ω     |

| Z <sub>CM_TX</sub>                             | DC common mode impedance                                           | Measured w.r.t to AC ground over 0-500mV                                                                | 18   | 23       | 30   | Ω     |

|                                                |                                                                    | f = 50 MHz - 1.25 GHz                                                                                   | 9    | 10       |      |       |

| $RL_{diff\_TX}$                                | Differential return loss                                           | f = 1.25 GHz – 2.5 GHz                                                                                  | 6    | 7        |      | dB    |

| RL <sub>CM_TX</sub>                            | Common mode return loss                                            | f = 50 MHz – 2.5 GHz                                                                                    | 11   | 12       |      | dB    |

| I <sub>TX_SC</sub>                             | TX short circuit current                                           | TX± shorted to GND                                                                                      |      |          | 60   | mA    |

| V <sub>TX_CM_DC</sub>                          | Transmitter DC common-mode voltage                                 | OSx = NC                                                                                                | 2.0  | 2.6      | 3.0  | V     |

| V <sub>TX_CM_AC_Active</sub>                   | TX AC common mode voltage active                                   |                                                                                                         |      | 30       | 100  | mVpp  |

| $VT_{X\_idle\_diff-AC-pp}$                     | Electrical idle differential peak to peak output voltage           | HPF to remove DC                                                                                        | 0    |          | 10   | mVpp  |

| V <sub>TX_CM_DeltaU1-U0</sub>                  | Absolute delta of DC CM voltage during active and idle states      |                                                                                                         |      | 35       | 200  | mV    |

| $V_{TX\_idle\_diff\text{-DC}}$                 | DC Electrical idle differential output voltage                     | Voltage must be low pass filtered to remove any AC component                                            | 0    |          | 10   | mV    |

| V <sub>detect</sub>                            | Voltage change to allow receiver detect                            | Positive voltage to sense receiver termination                                                          |      |          | 600  | mV    |

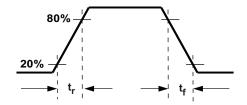

| $t_R$ , $t_F$                                  | Output rise/fall time                                              | 20%–80% of differential voltage measured 1" from the output pin                                         | 30   | 65       |      | ps    |

| t <sub>RF_MM</sub>                             | Output rise/fall time mismatch                                     | 20%–80% of differential voltage measured 1" from the output pin                                         |      | 1.5      | 20   | ps    |

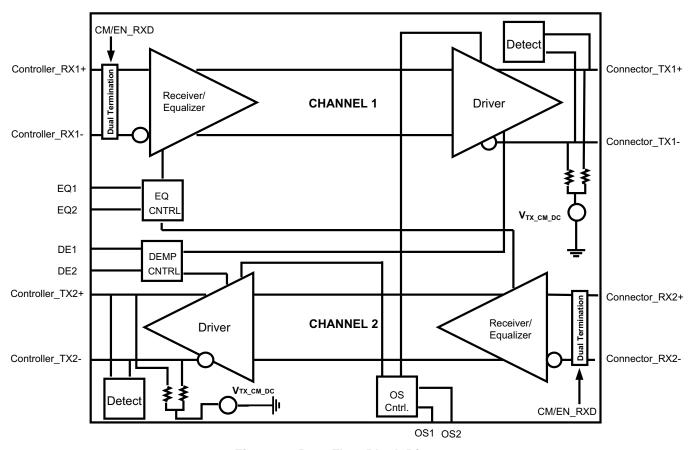

| $T_{diff\_LH},T_{diff\_HL}$                    | Differential propagation delay                                     | De-Emphasis = -3.5 dB (CH 0 and CH 1). Propagation delay between 50% level at input and output          |      | 305      | 370  | ps    |

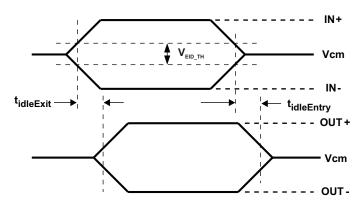

| t <sub>idleEntry</sub> , t <sub>idleExit</sub> | Idle entry and exit times                                          | See Figure 4                                                                                            |      | 4        | 6    | ns    |

| C <sub>TX</sub>                                | Tx input capacitance to GND                                        | At 2.5 GHz                                                                                              |      | 1.25     |      | pF    |

# **ELECTRICAL CHARACTERISTICS (continued)**

over recommended operating conditions (unless otherwise noted)

|                                 | PARAMETER                    | CONDITIONS                                        | MIN TYP | MAX | UNITS                |

|---------------------------------|------------------------------|---------------------------------------------------|---------|-----|----------------------|

| JITTER                          |                              |                                                   |         |     |                      |

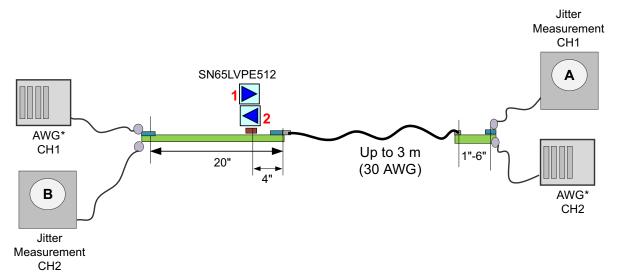

| T <sub>TX-EYE</sub> (1) (2)     | Total jitter (Tj) at point A |                                                   | 0.23    | 0.5 |                      |

| DJ <sub>TX</sub> <sup>(2)</sup> | Deterministic jitter (Dj)    | Device setting: OS1 = L,  DE1 = -6 dB, EQ1 = 7 dB | 0.14    | 0.3 | UI <sup>(3)</sup> pp |

| RJ <sub>TX</sub> (2) (4)        | Random jitter (Rj)           | DET = -0 dB, EQT = 7 dB                           | 0.08    | 0.2 |                      |

| T <sub>TX-EYE</sub> (1) (2)     | Total jitter (Tj) at point B |                                                   | 0.15    | 0.5 |                      |

| DJ <sub>TX</sub> <sup>(2)</sup> | Deterministic jitter (Dj)    | Device setting: OS2 = H,  DE2 = -6 dB, EQ2 = 7dB  | 0.07    | 0.3 | UI <sup>(3)</sup> Pp |

| RJ <sub>TX</sub> (2) (4)        | Random jitter (Rj)           | DEZ = 0 dB, EQZ = 7 dB                            | 0.08    | 0.2 |                      |

- (1) Includes RJ at 10<sup>-12</sup> BER

- (2) Determininstic jitter measured with K28.5 pattern, Random jitter measured with K28.5 pattern at the ends of reference channel in , VID=1000mVpp, 5Gbps, -3.5dB DE from source

- (3) UI = 200ps

- (4) Rj calculated as 14.069 times the RMS random jitter for 10<sup>-12</sup> BER

Figure 3. Propagation Delay

Figure 4. Electrical Idle Mode Exit and Entry Delay

Figure 5. Output Rise and Fall Times

Figure 6. Jitter Measurement Setup

Figure 7. Output De-Emphasis Levels OSx = NC

## **DEVICE INFORMATION**

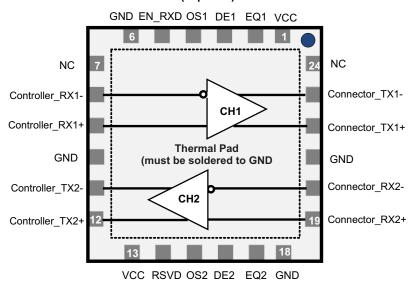

# RGE PACKAGE (Top View)

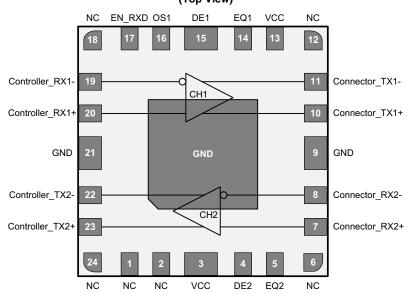

# RMQ PACKAGE (Top View)

## **Table 1. Pin Functions**

|                               | PIN                    | T.              |            |                                                                                              |

|-------------------------------|------------------------|-----------------|------------|----------------------------------------------------------------------------------------------|

| 'LVPE512<br>RGE               | 'LVPE512<br>RMQ        | Name            | I/O Type   | Description                                                                                  |

| HIGH SPEED DI                 | FFERENTIAL I/O         | PINS            |            |                                                                                              |

| 8                             | 19                     | Controller_RX1- | I, CML     | Non-inverting and inverting CML differential input for CH1 and                               |

| 9                             | 20                     | Controller_RX1+ | I, CML     | CH2. These pins are tied to an internal voltage bias by dual termination resistor circuit.   |

| 20                            | 8                      | Connector_RX2-  | I, CML     | Pins labeled "Controller" must connect to the USB 3.0 host or                                |

| 19                            | 7                      | Connector_RX2+  | I, CML     | device controller.  Pins labeled "Connector" must connect to the USB 3.0 connector.          |

| 23                            | 11                     | Connector_TX1-  | O, CML     | Non-inverting and inverting CML differential output for CH1                                  |

| 22                            | 10                     | Connector_TX1+  | O, CML     | and CH2. These pins are tied to an internal voltage bias by termination resistors.           |

| 11                            | 22                     | Controller_TX2- | O, CML     | Pins labeled "Controller" must connect to the USB 3.0 host or                                |

| 12                            | 23                     | Controller_TX2+ | O, CML     | device controller.  Pins labeled "Connector" must connect to the USB 3.0 connector.          |

| DEVICE CONTR                  | OL PIN                 |                 |            |                                                                                              |

| 5                             | 17                     | EN_RXD          | I, LVCMOS  | Sets device operation modes per Table 2. Internally pulled to $V_{CC}$ .                     |

| 14                            | _                      | RSVD            | I, LVCMOS  | RSVD. Can be left as No-Connect.                                                             |

| 7, 24                         | 1, 2, 6, 12, 18,<br>24 | NC              | No-Connect | Pads are not internally connected.                                                           |

| EQ CONTROL F                  | PINS <sup>(1)</sup>    |                 |            |                                                                                              |

| 3, 16                         | 15, 4                  | DE1, DE2        | I, LVCMOS  | Selects de-emphasis settings for CH1 and CH2 per Table 2. Internally tied to $\rm V_{CC}/2$  |

| 2, 17                         | 14, 5                  | EQ1, EQ2        | I, LVCMOS  | Selects equalization settings for CH1 and CH2 per Table 2. Internally tied to $\rm V_{CC}/2$ |

| 4, 15                         | 16, NC <sup>(2)</sup>  | OS1, OS2        | I, LVCMOS  | Selects output amplitude for CH1 and CH2 per Table 2. Internally tied to $V_{\rm CC}/2$      |

| POWER PINS                    |                        |                 |            |                                                                                              |

| 1,13                          | 3                      | VCC             | Power      | Positive supply; should be 3.3V ±10%                                                         |

| 6, 10, 18, 21,<br>Thermal Pad | 9, Thermal Pad         | GND             | Power      | Supply Ground                                                                                |

Internally biased to  $V_{CC}/2$  with >200k $\Omega$  pull-up/pull-down. When pins are left as NC board leakage at this pin pad must be < 1  $\mu$ A otherwise drive to Vcc/2 to assert mid-level state The RMQ has OS2 internally No-Connect, to select the 1042 mVpp level on TX2.

**Table 2. Signal Control Pin Setting**

|                    | OUTPUT SWING AND EQ CO               | NTROL (at 2.5 GHz)     |                        |  |  |  |  |  |  |  |  |

|--------------------|--------------------------------------|------------------------|------------------------|--|--|--|--|--|--|--|--|

| OSx                | TRANSISTION BIT AMPLITUDE (TYP mVpp) | EQx                    | EQUALIZATION<br>(dB)   |  |  |  |  |  |  |  |  |

| NC (default)       | 1241                                 | NC (default)           | 0                      |  |  |  |  |  |  |  |  |

| 0                  | 1105                                 | 0                      | 7                      |  |  |  |  |  |  |  |  |

| 1                  | 1324                                 | 1                      | 15                     |  |  |  |  |  |  |  |  |

|                    | OUTPUT DE CONTROL (at 2.5 GHz)       |                        |                        |  |  |  |  |  |  |  |  |

| DEx <sup>(1)</sup> | OSx <sup>(1)</sup> = NC              | OSx <sup>(1)</sup> = 0 | OSx <sup>(1)</sup> = 1 |  |  |  |  |  |  |  |  |

| NC (default)       | 0 dB                                 | 0 dB                   | 0 dB                   |  |  |  |  |  |  |  |  |

| 0                  | −3 dB                                | −2 dB                  | -4 dB                  |  |  |  |  |  |  |  |  |

| 1                  | –5 dB                                | –4 dB                  | −5.6 dB                |  |  |  |  |  |  |  |  |

|                    | CONTROL PINS S                       | ETTINGS                |                        |  |  |  |  |  |  |  |  |

| EN_RXD             | DEV                                  | ICE FUNCTION           |                        |  |  |  |  |  |  |  |  |

| 1 (default)        | No                                   | rmal Operation         |                        |  |  |  |  |  |  |  |  |

| 0                  |                                      | Sleep Mode             |                        |  |  |  |  |  |  |  |  |

(1) Where x = Channel 1 or Channel 2

NOTE: For more detailed placement example of redriver see typical eye diagrams and jitter plots at end of data sheet.

Figure 8. Redriver Placement Example

#### DETAILED DESCRIPTION

### **Controller- and Connector-side Pins**

The SN65LVPE512 features a link state machine that makes the device transparent on the USB 3.0 bus while minimizing power. The state machine relies on the system host or device controller to be connected to the pins named "Controller". The pins labeled connector should be connected to the USB 3.0 receptacle or captive cable. Multiple SN65LVPE512 devices may be used in series.

## Programmable EQ, De-Emphasis and Amplitude Swing

The SN65LVPE512 is designed to minimize signal degradation effects such as crosstalk and inter-symbol interference (ISI) that limits the interconnect distance between two devices. The input stage of each channel offers selectable equalization settings that can be programmed to match loss in the channel. The differential outputs provide selectable de-emphasis to compensate for the anticipated distortion USB 3.0 signal will experience. Level of de-emphasis will depend on the length of interconnect and its characteristics. The SN65LVPE512 provides a unique way to tailor output de-emphasis on a per channel basis with use of DE and OS pins. All Rx and Tx equalization settings supported by the device are programmed by six 3-state pins as shown in Table 2.

#### **Low Power Modes**

Device supports three low power modes as described below

1. Sleep Mode

Initiated anytime EN\_RXD undergoes a high to low transition and stays low or when device powers up with EN\_RXD set low. In sleep mode both input and output terminations are held at HiZ and device ceases operation to conserve power. Sleep mode max power consumption is 1mW, entry time is 2µs, device exits sleep mode to Rx.Detect mode after EN\_RXD is driven to Vcc, exit time is 100µs max.

RX Detect Mode--When no remote device is connected

Anytime 'LVPE512 detects a break in link (that is, when upstream device is disconnected) or after power-up fails to find a remote device, 'LVPE512 goes to Rx Detect mode and conserves power by shutting down majority of its internal circuitry. In this mode, input termination for both channels are driven to Hi-Z. In Rx Detect mode device power is < 10mW (TYP) or less than 5% of its normal operating power. This feature is very useful in saving system power in mobile applications like notebook PC where battery life is critical.

Anytime an upstream device gets reconnected the redriver automatically senses the connection and goes to normal operating mode. This operation requires no setting to the device.

3. U2/U3 Mode

With the help of internal timers the device tracks when link enters USB 3.0 low power modes U2 and U3; in these modes link is in electrical idle state. 'LVPE512 will selectively turn-off internal circuitry to save on power. Typical power saving is about 75% lower than normal operating mode. The device will automatically revert to active mode when signal activity (LFPS) is detected.

### **Receiver Detection**

### At Power Up or Reset

After power-up or anytime EN\_RXD is toggled, RX.Detect cycle is performed by first setting Rx termination for each channel to Hi-Z, device then starts sensing for receiver termination that may be attached at the other end of each TX.

If receiver is detected on both channel

The TX and RX terminations are switched to Z<sub>DIFF\_TX</sub>, Z<sub>DIFF\_RX</sub> respectively.

If no receiver is detected on one or both channels

- The transmitter is pulled to Hi-Z

- The channel is put in low power mode

- Device attempts to detect Rx termination in 12 ms (TYP) interval until termination is found or device is put in sleep mode

## **During U2, U3 Link State**

Rx detection is also performed periodically when link is in U2/U3 states. However in these states during Rx detection, input termination is not automatically disabled before performing Rx.Detect. If termination is found device goes back to its low power state if termination is not found then device disables its input termination and then jumps to power-up RX.Detect state.

## **Electrical Idle Support**

Electrical idle support is needed for low frequency periodic signaling (LFPS) used in USB 3.0 side band communication. A link is in an electrical idle state when the TX± voltage is held at a steady constant value like the common mode voltage. 'LVPE512 detects an electrical idle state when RX± voltage at the device pin falls below VRX\_LFPS\_DIFFp-p min. After detection of an idle state in a given channel the device asserts electrical idle state in its corresponding TX. When RX± voltage exceeds VRX\_LFPS\_DIFFp-p max normal operation is restored and output start passing input signal. Electrical idle exit and entry time is specified at < 6ns.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| SN65LVPE512RGER  | NRND       | VQFN         | RGE                | 24   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | LVPE<br>512             |         |

| SN65LVPE512RMQR  | NRND       | WQFN         | RMQ                | 24   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | SN512                   |         |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL. Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 25-Feb-2023

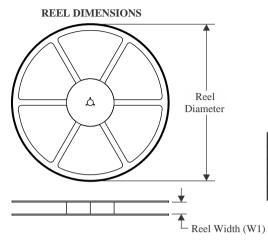

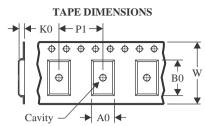

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing | l . | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|-----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN65LVPE512RGER | VQFN            | RGE                | 24  | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

| SN65LVPE512RMQR | WQFN            | RMQ                | 24  | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

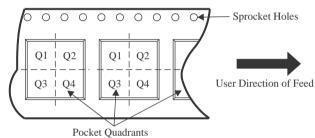

www.ti.com 25-Feb-2023

# \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN65LVPE512RGER | VQFN         | RGE             | 24   | 3000 | 356.0       | 356.0      | 35.0        |

| SN65LVPE512RMQR | WQFN         | RMQ             | 24   | 3000 | 367.0       | 367.0      | 35.0        |

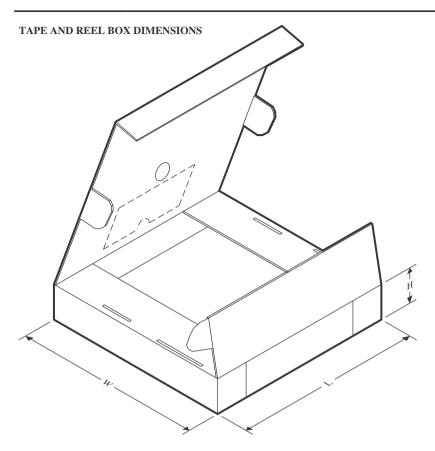

## NOTES:

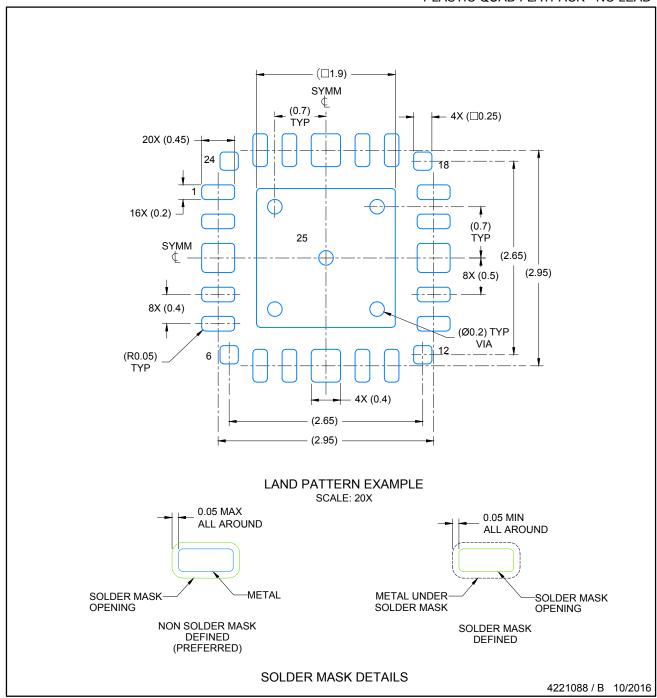

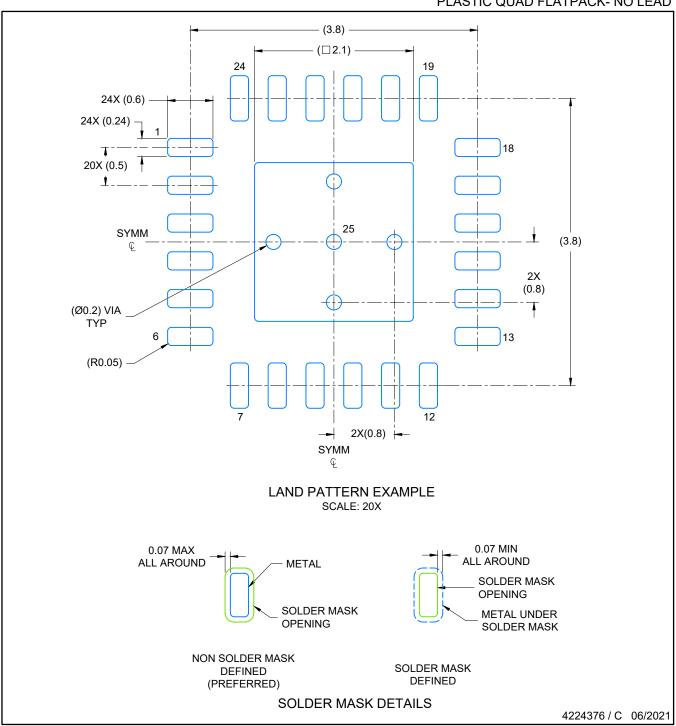

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

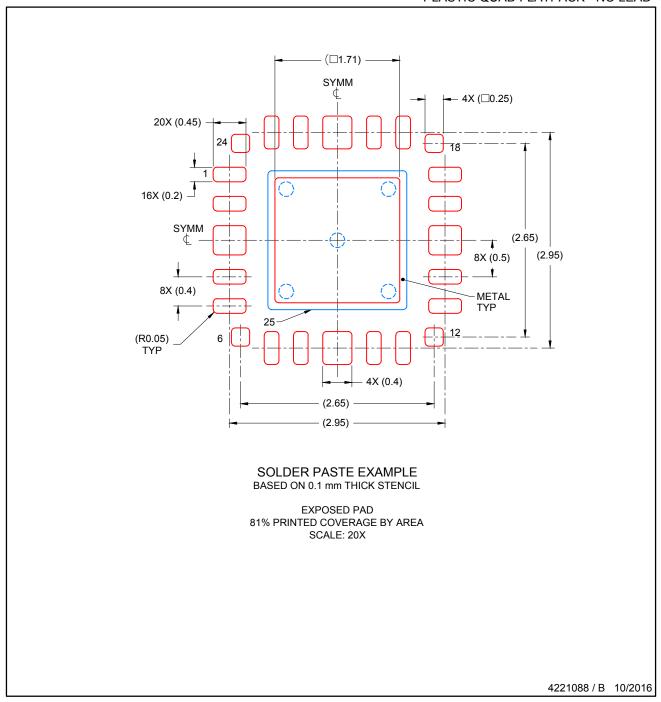

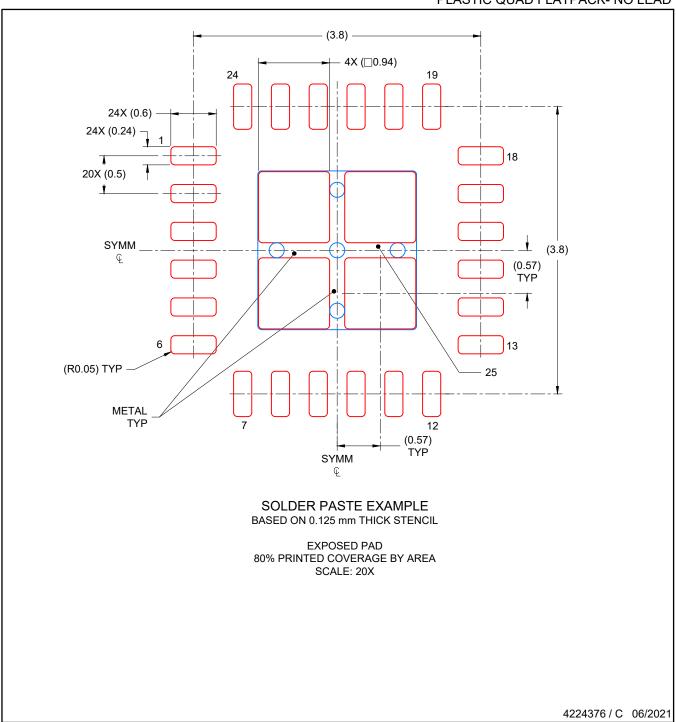

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations..

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4204104/H

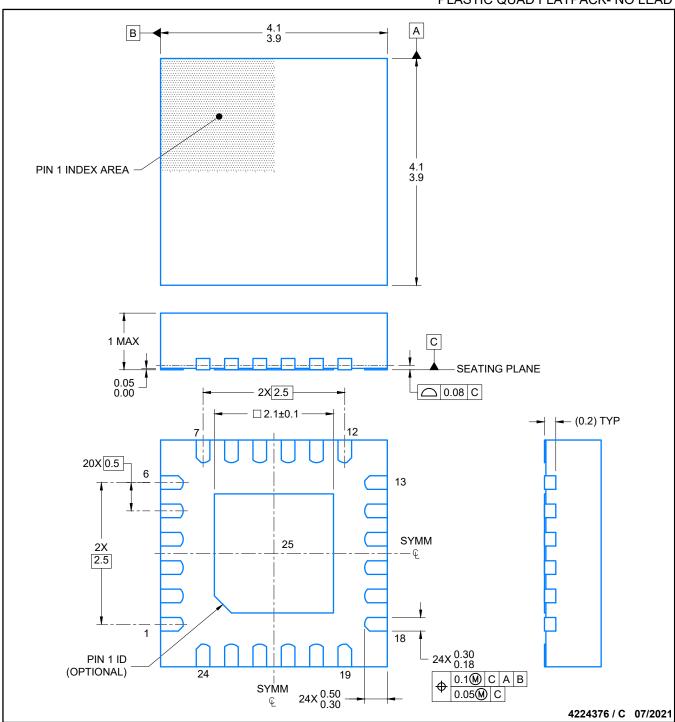

## NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

NOTES: (continued)

- This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations..

# 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023,德州仪器 (TI) 公司