# 25-BIT CONFIGURABLE REGISTERED BUFFER WITH ADDRESS-PARITY TEST

#### **FEATURES**

- Member of the Texas Instruments Widebus+™ Family

- **Pinout Optimizes DDR2 DIMM PCB Layout**

- Configurable as 25-Bit 1:1 or 14-Bit 1:2 Registered Buffer

- **Chip-Select Inputs Gate the Data Outputs from Changing State and Minimizes System Power** Consumption

- **Output Edge-Control Circuitry Minimizes** Switching Noise in an Unterminated Line

- Supports SSTL 18 Data Inputs

- Differential Clock (CLK and CLK) Inputs

- Supports LVCMOS Switching Levels on the **Control and RESET Inputs**

- **Checks Parity on DIMM-Independent Data** Inputs

- Able to Cascade with a Second **SN74SSTUB32866**

- **Supports Industrial Temperature Range** (-40°C to 85°C)

#### DESCRIPTION

This 25-bit 1:1 or 14-bit 1:2 configurable registered buffer is designed for 1.7-V to 1.9-V VCC operation. In the 1:1 pinout configuration, only one device per DIMM is required to drive nine SDRAM loads. In the 1:2 pinout configuration, two devices per DIMM are required to drive 18 SDRAM loads.

All inputs are SSTL\_18, except the reset (RESET) and control (Cn) inputs, which are LVCMOS. All outputs are edge-controlled circuits optimized for unterminated DIMM loads and meet SSTL 18 specifications, except the open-drain error (QERR) output.

The SN74SSTUB32866 operates from a differential clock (CLK and CLK). Data are registered at the crossing of CLK going high and CLK going low.

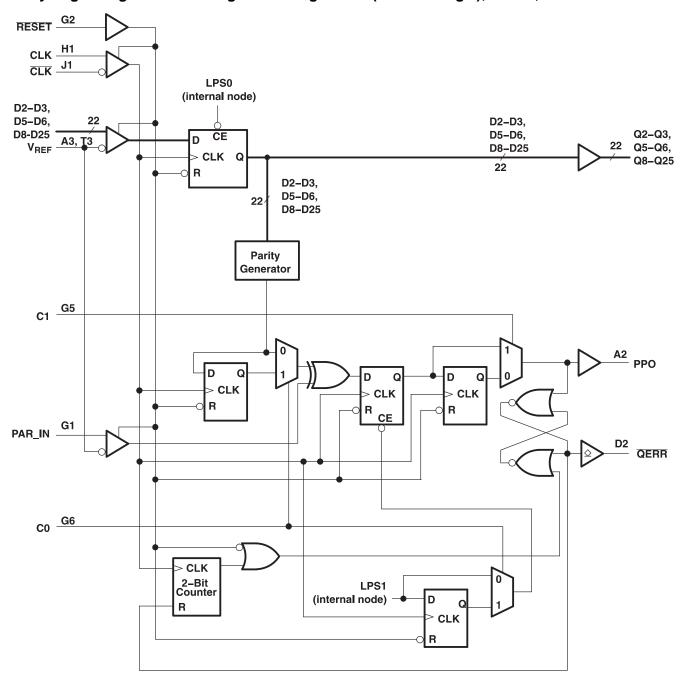

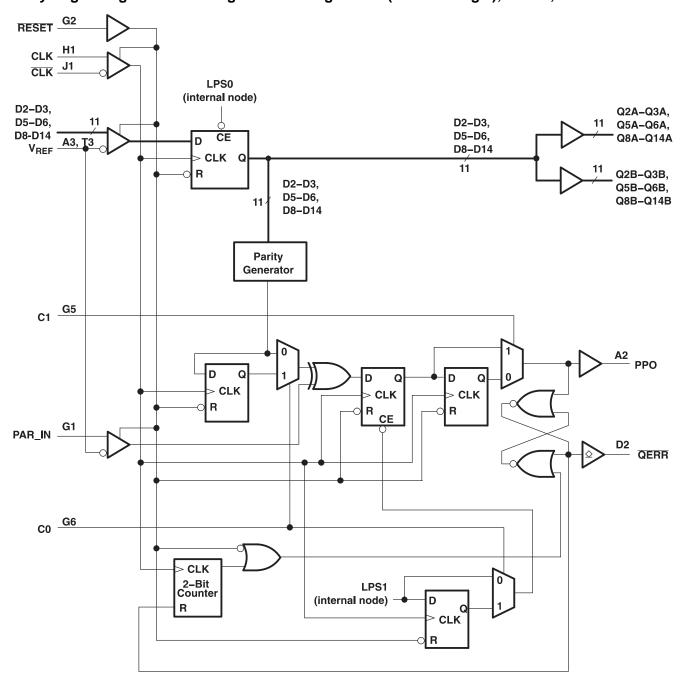

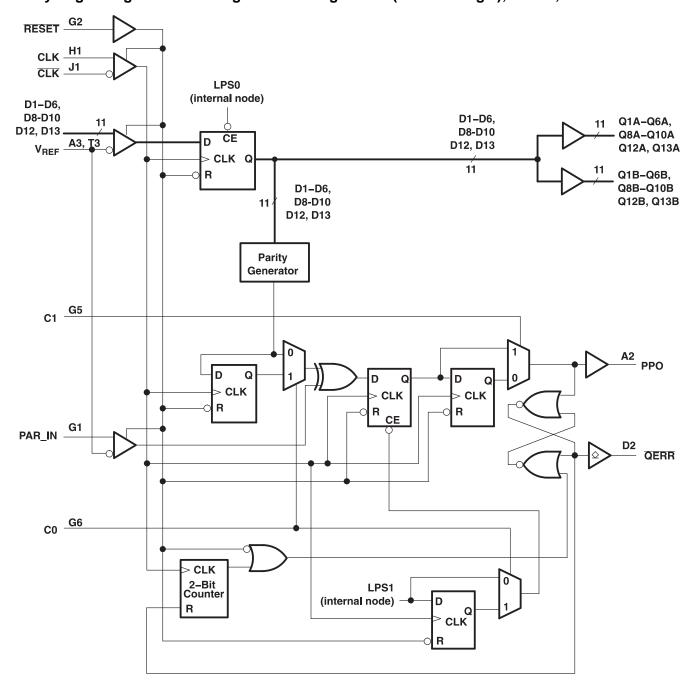

The SN74SSTUB32866 accepts a parity bit from the memory controller on the parity bit (PAR IN) input, compares it with the data received on the DIMM-independent D-inputs (D2-D3, D5-D6, D8-D25 when C0 = 0 and C1 = 0; D2-D3, D5-D6, D8-D14 when C0 = 0 and C1 = 1; or D1-D6, D8-D13 when C0 = 1 and C1 = 1) and indicates whether a parity error has occurred on the open-drain QERR pin (active low). The convention is even parity; i.e., valid parity is defined as an even number of ones across the DIMM-independent data inputs, combined with the parity input bit. To calculate parity, all DIMM-independent data inputs must be tied to a known logic state.

When used as a single device, the C0 and C1 inputs are tied low. In this configuration, parity is checked on the PAR IN input signal, which arrives one cycle after the input data to which it applies. Two clock cycles after the data are registered, the corresponding partial-parity-out (PPO) and QERR signals are generated.

When used in pairs, the C0 input of the first register is tied low, and the C0 input of the second register is tied high. The C1 input of both registers are tied high. Parity, which arrives one cycle after the data input to which it applies, is checked on the PAR\_IN input signal of the first device. Two clock cycles after the data are registered, the corresponding PPO and QERR signals are generated on the second device. The PPO output of the first register is cascaded to the PAR IN of the second SN74SSTUB32866. The QERR output of the first SN74SSTUB32866 is left floating, and the valid error information is latched on the QERR output of the second SN74SSTUB32866.

#### ORDERING INFORMATION

| T <sub>A</sub> | PACKAGE <sup>(1)</sup> |               | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|------------------------|---------------|-----------------------|------------------|

| 40°C to 95°C   | LFBGA-ZKE              | Tape and reel | SN74SSTUB32866ZKER    | SB866            |

| -40°C to 85°C  | LFBGA-ZWL              | Tape and reel | SN74SSTUB32866ZWLR    | SB866            |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. Widebus+ is a trademark of Texas Instruments.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **DESCRIPTION (CONTINUED)**

If an error occurs and the QERR output is driven low, it stays latched low for a minimum of two clock cycles or until RESET is driven low. If two or more consecutive parity errors occur, the QERR output is driven low and latched low for a clock duration equal to the parity-error duration or until RESET is driven low. The DIMM-dependent signals (DCKE, DCS, DODT, and CSR) are not included in the parity-check computation.

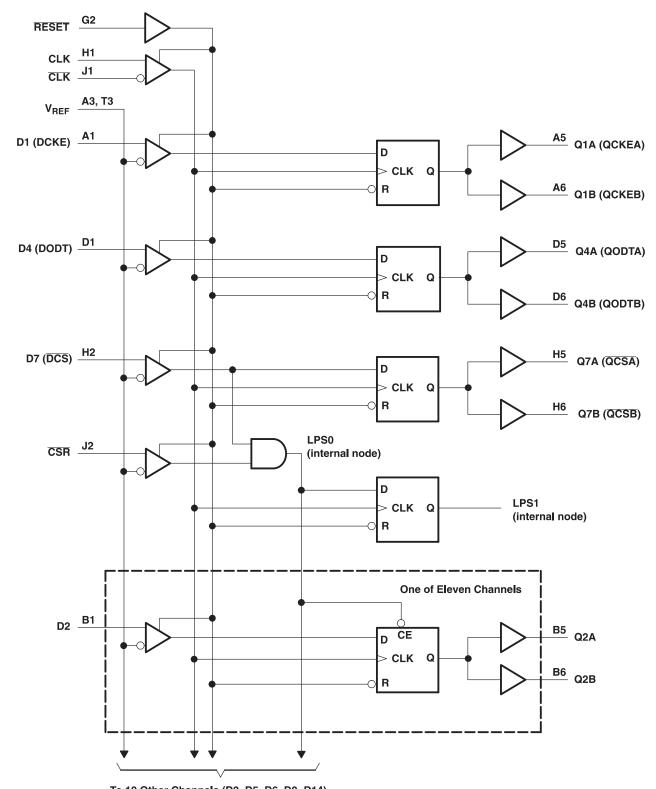

The C0 input controls the pinout configuration of the 1:2 pinout from register-A configuration (when low) to register-B configuration (when high). The C1 input controls the pinout configuration from 25-bit 1:1 (when low) to 14-bit 1:2 (when high). C0 and C1 should not be switched during normal operation. They should be hard-wired to a valid low or high level to configure the register in the desired mode. In the 25-bit 1:1 pinout configuration, the A6, D6, and H6 terminals are driven low and are do-not-use (DNU) pins.

In the DDR2 RDIMM application, RESET is specified to be completely asynchronous with respect to CLK and CLK. Therefore, no timing relationship can be ensured between the two. When entering reset, the register is cleared, and the data outputs are driven low quickly, relative to the time required to disable the differential input receivers. However, when coming out of reset, the register becomes active quickly, relative to the time required to enable the differential input receivers. As long as the data inputs are low, and the clock is stable during the time from the low-to-high transition of RESET until the input receivers are fully enabled, the design of the SN74SSTUB32866 ensures that the outputs remain low, thus ensuring there will be no glitches on the output.

To ensure defined outputs from the register before a stable clock has been supplied, RESET must be held in the low state during power up.

The device supports low-power standby operation. When  $\overline{\text{RESET}}$  is low, the differential input receivers are disabled, and undriven (floating) data, clock, and reference voltage (V<sub>REF</sub>) inputs are allowed. In addition, when  $\overline{\text{RESET}}$  is low, all registers are reset and all outputs are forced low, except  $\overline{\text{QERR}}$ . The LVCMOS  $\overline{\text{RESET}}$  and Cn inputs always must be held at a valid logic high or low level.

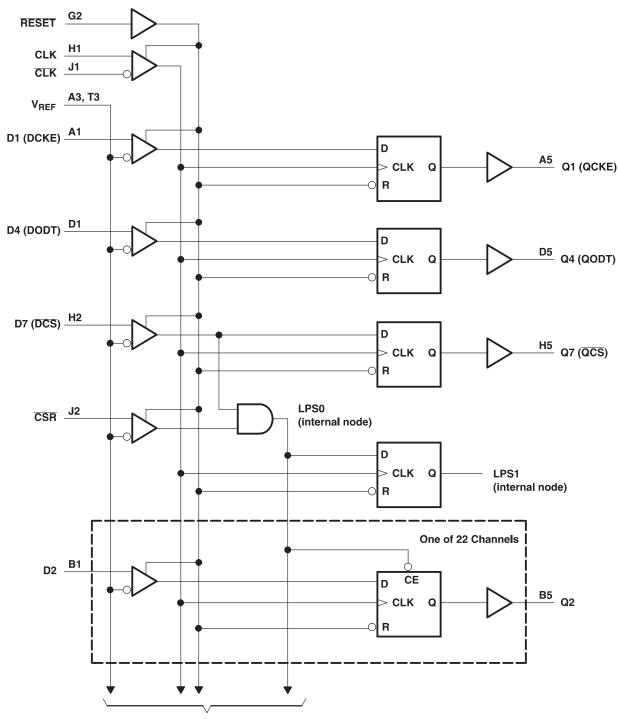

The device also supports low-power active operation by monitoring both system chip select ( $\overline{DCS}$  and  $\overline{CSR}$ ) inputs and gates the Qn and PPO outputs from changing states when both  $\overline{DCS}$  and  $\overline{CSR}$  inputs are high. If either DCS or CSR input is low, the Qn and PPO outputs function normally. Also, if the internal low-power signal (LPS1) is high (one cycle after  $\overline{DCS}$  and  $\overline{CSR}$  go high), the device gates the  $\overline{QERR}$  output from changing states. If  $\overline{LPS1}$  is low, the  $\overline{QERR}$  output functions normally. The  $\overline{RESET}$  input has priority over the  $\overline{DCS}$  and  $\overline{CSR}$  control and, when driven low, forces the Qn and PPO outputs low and forces the  $\overline{QERR}$  output high. If the  $\overline{DCS}$  control functionality is not desired, the  $\overline{CSR}$  input can be hard-wired to ground, in which case the setup-time requirement for  $\overline{DCS}$  is the same as for the other D data inputs. To control the low-power mode with  $\overline{DCS}$  only, the  $\overline{CSR}$  input should be pulled up to  $V_{CC}$  through a pullup resistor.

The two  $V_{REF}$  pins (A3 and T3) are connected together internally by approximately 150 $\Omega$ . However, it is necessary to connect only one of the two  $V_{REF}$  pins to the external  $V_{REF}$  power supply. An unused  $V_{REF}$  pin should be terminated with a  $V_{REF}$  coupling capacitor.

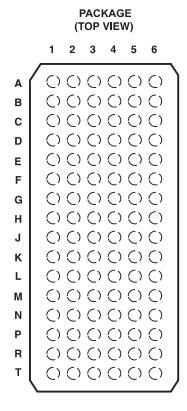

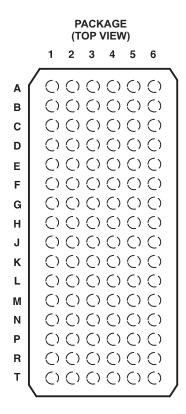

## Terminal Assignments for 1:1 Register-A (C0 = 0, C1 = 0)

| - | 1         | 2        | 3         | 4               | 5         | 6   |

|---|-----------|----------|-----------|-----------------|-----------|-----|

| Α | D1 (DCKE) | PPO      | $V_{REF}$ | V <sub>CC</sub> | Q1 (QCKE) | DNU |

| В | D2        | D15      | GND       | GND             | Q2        | Q15 |

| С | D3        | D16      | $V_{CC}$  | V <sub>CC</sub> | Q3        | Q16 |

| D | D4 (DODT) | QERR     | GND       | GND             | Q4 (QODT) | DNU |

| Ε | D5        | D17      | $V_{CC}$  | V <sub>CC</sub> | Q5        | Q17 |

| F | D6        | D18      | GND       | GND             | Q6        | Q18 |

| G | PAR_IN    | RESET    | $V_{CC}$  | V <sub>CC</sub> | C1        | C0  |

| Н | CLK       | D7 (DCS) | GND       | GND             | Q7 (QCS)  | DNU |

| J | CLK       | CSR      | $V_{CC}$  | V <sub>CC</sub> | NC        | NC  |

| K | D8        | D19      | GND       | GND             | Q8        | Q19 |

| L | D9        | D20      | $V_{CC}$  | V <sub>CC</sub> | Q9        | Q20 |

| М | D10       | D21      | GND       | GND             | Q10       | Q21 |

| N | D11       | D22      | $V_{CC}$  | $V_{CC}$        | Q11       | Q22 |

| Р | D12       | D23      | GND       | GND             | Q12       | Q23 |

| R | D13       | D24      | $V_{CC}$  | V <sub>CC</sub> | Q13       | Q24 |

| Т | D14       | D25      | $V_{REF}$ | V <sub>CC</sub> | Q14       | Q25 |

Each pin name in parentheses indicates the DDR2 DIMM signal name.

DNU - Do not use

NC - No internal connection

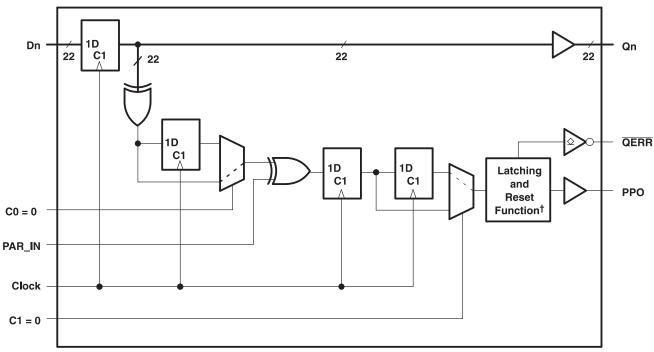

## Logic Diagram for 1:1 Register Configuration (Positive Logic); C0 = 0, C1 = 0

To 21 Other Channels (D3, D5, D6, D8-D25)

## Parity Logic Diagram for 1:1 Register Configuration (Positive Logic); C0 = 0, C1 = 0

|   | PACKAGE<br>(TOP VIEW) |    |    |    |            |    |            |   |

|---|-----------------------|----|----|----|------------|----|------------|---|

|   | _                     | 1  | 2  | 3  | 4          | 5  | 6          |   |

| Α |                       | () | () | () | $\bigcirc$ | () | $\bigcirc$ | \ |

| В |                       | () | () | () | ()         | () | ()         |   |

| С |                       | () | () | () | ()         | () | ()         |   |

| D |                       | () | () | () | ()         | () | ()         |   |

| Е |                       | () | () | () | ()         | () | ()         |   |

| F |                       | () | () | () | ()         | () | ()         |   |

| G |                       | () | () | () | ()         | () | ()         |   |

| Н |                       | () | () | () | ()         | () | ()         |   |

| J |                       | () | () | () | ()         | () | ()         |   |

| Κ |                       | () | () | () | ()         | () | ()         |   |

| L |                       | () | () | () | ()         | () | $\bigcirc$ |   |

| М |                       | () | () | () | ()         | () | ()         |   |

| N |                       | () | () | () | ()         | () | ()         |   |

| Р |                       | () | () | () | ()         | () | ()         |   |

| R |                       | () | () | () | ()         | () | ()         |   |

| Т |                       | () | () | () | ()         | () | $\bigcirc$ | / |

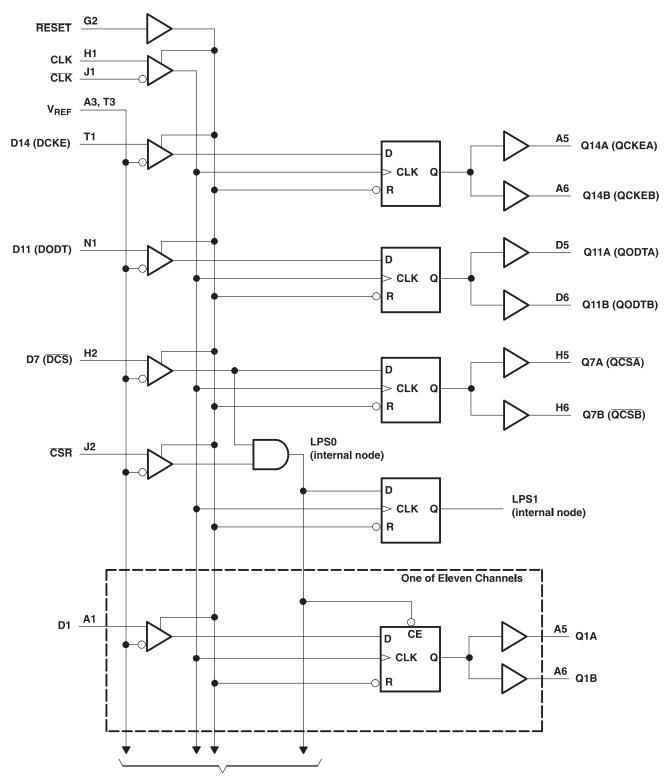

|   | 1         | 2        | 3         | 4               | 5           | 6           |

|---|-----------|----------|-----------|-----------------|-------------|-------------|

| Α | D1 (DCKE) | PPO      | $V_{REF}$ | V <sub>cc</sub> | Q1A (QCKEA) | Q1B (QCKEB) |

| В | D2        | DNU      | GND       | GND             | Q2A         | Q2B         |

| С | D3        | DNU      | $V_{CC}$  | V <sub>CC</sub> | Q3A         | Q3B         |

| D | D4 (DODT) | QERR     | GND       | GND             | Q4A (QODTA) | Q4B(QODTB)  |

| Ε | D5        | DNU      | $V_{CC}$  | V <sub>CC</sub> | Q5A         | Q5B         |

| F | D6        | DNU      | GND       | GND             | Q6A         | Q6B         |

| G | PAR_IN    | RESET    | $V_{CC}$  | V <sub>CC</sub> | C1          | C0          |

| Н | CLK       | D7 (DCS) | GND       | GND             | Q7A (QCSA)  | Q7B (QCSB)  |

| J | CLK       | CSR      | $V_{CC}$  | V <sub>CC</sub> | NC          | NC          |

| K | D8        | DNU      | GND       | GND             | Q8A         | Q8B         |

| L | D9        | DNU      | $V_{CC}$  | V <sub>CC</sub> | Q9A         | Q9B         |

| M | D10       | DNU      | GND       | GND             | Q10A        | Q10B        |

| N | D11       | DNU      | $V_{CC}$  | V <sub>CC</sub> | Q11A        | Q11B        |

| Р | D12       | DNU      | GND       | GND             | Q12A        | Q12B        |

| R | D13       | DNU      | $V_{CC}$  | V <sub>CC</sub> | Q13A        | Q13B        |

| T | D14       | DNU      | $V_{REF}$ | $V_{CC}$        | Q14A        | Q14B        |

Each pin name in parentheses indicates the DDR2 DIMM signal name.

DNU - Do not use

NC - No internal connection

## Logic Diagram for 1:2 Register-A Configuration (Positive Logic); C0 = 0, C1 = 1

To 10 Other Channels (D3, D5, D6, D8-D14)

## Parity Logic Diagram for 1:2 Register-A Configuration (Positive Logic); C0 = 0, C1 = 1

## Terminal Assignments for 1:2 Register-B (C0 = 1, C1 = 1)

|   | 1          | 2        | 3         | 4               | 5            | 6            |

|---|------------|----------|-----------|-----------------|--------------|--------------|

| Α | D1         | PPO      | $V_{REF}$ | V <sub>CC</sub> | Q1A          | Q1B          |

| В | D2         | DNU      | GND       | GND             | Q2A          | Q2B          |

| С | D3         | DNU      | $V_{CC}$  | V <sub>CC</sub> | Q3A          | Q3B          |

| D | D4         | QERR     | GND       | GND             | Q4A          | Q4B          |

| E | D5         | DNU      | $V_{CC}$  | V <sub>CC</sub> | Q5A          | Q5B          |

| F | D6         | DNU      | GND       | GND             | Q6A          | Q6B          |

| G | PAR_IN     | RESET    | $V_{CC}$  | V <sub>CC</sub> | C1           | C0           |

| Н | CLK        | D7 (DCS) | GND       | GND             | Q7A (QCSA)   | Q7B (QCSB)   |

| J | CLK        | CSR      | $V_{CC}$  | V <sub>CC</sub> | NC           | NC           |

| K | D8         | DNU      | GND       | GND             | Q8A          | Q8B          |

| L | D9         | DNU      | $V_{CC}$  | V <sub>CC</sub> | Q9A          | Q9B          |

| М | D10        | DNU      | GND       | GND             | Q10A         | Q10B         |

| N | D11 (DODT) | DNU      | $V_{CC}$  | V <sub>CC</sub> | Q11A (QODTA) | Q11B (QODTB) |

| Р | D12        | DNU      | GND       | GND             | Q12A         | Q12B         |

| R | D13        | DNU      | $V_{CC}$  | V <sub>CC</sub> | Q13A         | Q13B         |

| T | D14 (DCKE) | DNU      | $V_{REF}$ | V <sub>CC</sub> | Q14A (QCKEA) | Q14B (QCKEB) |

Each pin name in parentheses indicates the DDR2 DIMM signal name.

DNU - Do not use

NC - No internal connection

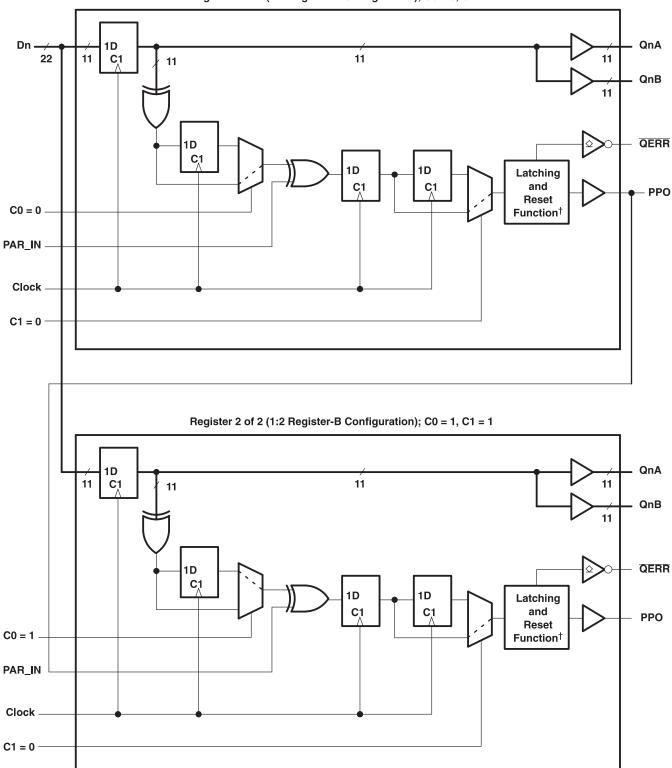

## Logic Diagram for 1:2 Register-B Configuration C0 = 1, C1 = 1

To 10 Other Channels (D2-D6, D8-D10, D12-D13)

## Parity Logic Diagram for 1:2 Register-B Configuration (Positive Logic); C0 = 1, C1 = 1

#### **TERMINAL FUNCTIONS**

| TERMINAL NAME         | DESCRIPTION                                                                                                                                                                                                  | ELECTRICAL CHARACTERISTICS |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| GND                   | Ground                                                                                                                                                                                                       | Ground input               |

| V <sub>CC</sub>       | Power-supply voltage                                                                                                                                                                                         | 1.8 V nominal              |

| $V_{REF}$             | Input reference voltage                                                                                                                                                                                      | 0.9 V nominal              |

| CLK                   | Positive master clock input                                                                                                                                                                                  | Differential input         |

| CLK                   | Negative master clock input                                                                                                                                                                                  | Differential input         |

| C0, C1                | Configuration control input. Register A or Register B and 1:1 mode or 1:2 mode select.                                                                                                                       | LVCMOS inputs              |

| RESET                 | Asynchronous reset input. Resets registers and disables V <sub>REF</sub> , data, and clock differential-input receivers. When RESET is low, all Q outputs are forced low and the QERR output is forced high. | LVCMOS input               |

| D1-D25                | Data input. Clocked in on the crossing of the rising edge of CLK and the falling edge of CLK.                                                                                                                | SSTL_18 inputs             |

| CSR, DCS              | Chip select inputs. Disables D1–D25 <sup>(1)</sup> outputs switching when both inputs are high                                                                                                               | SSTL_18 inputs             |

| DODT                  | The outputs of this register bit will not be suspended by the DCS and CSR control.                                                                                                                           | SSTL_18 input              |

| DCKE                  | The outputs of this register bit will not be suspended by the $\overline{\text{DCS}}$ and $\overline{\text{CSR}}$ control.                                                                                   | SSTL_18 input              |

| PAR_IN                | Parity input. Arrives one clock cycle after the corresponding data input. Pulldown resistor of typical $150k\Omega$ to GND.                                                                                  | SSTL_18 input pulldown     |

| Q1-Q25 <sup>(2)</sup> | Data outputs that are suspended by the DCS and CSR control.                                                                                                                                                  | 1.8 V CMOS outputs         |

| PPO                   | Partial parity out. Indicates odd parity of inputs D1–D25. (1)                                                                                                                                               | 1.8 V CMOS output          |

| QCS                   | Data output that will not be suspended by the DCS and CSR control                                                                                                                                            | 1.8 V CMOS output          |

| QODT                  | Data output that will not be suspended by the DCS and CSR control                                                                                                                                            | 1.8 V CMOS output          |

| QCKE                  | Data output that will not be suspended by the DCS and CSR control                                                                                                                                            | 1.8 V CMOS output          |

| QERR                  | Output error bit. Timing is determined by the device mode.                                                                                                                                                   | Open-drain output          |

| NC                    | No internal connection                                                                                                                                                                                       |                            |

| DNU                   | Do not use. Inputs are in standby-equivalent mode, and outputs are driven low.                                                                                                                               |                            |

- (1) Data inputs = D2, D3, D5, D6, D8-D25 when C0 = 0 and C1 = 0

Data inputs = D2, D3, D5, D6, D8-D14 when C0 = 0 and C1 = 1

Data inputs = D1-D6, D8-D10, D12, D13 when C0 = 1 and C1 = 1.D

- (2) Data outputs = Q2, Q3, Q5, Q6, Q8-Q25 when C0 = 0 and C1 = 0 Data outputs = Q2, Q3, Q5, Q6, Q8-Q14 when C0 = 0 and C1 = 1 Data outputs = Q1-Q6, Q8-Q10, Q12, Q13 when C0 = 1 and C1 = 1.

#### **FUNCTION TABLE**

|       | INPUTS        |               |               |               |               |       |  |  |

|-------|---------------|---------------|---------------|---------------|---------------|-------|--|--|

| RESET | DCS           | CSR           | CLK           | CLK           | Dn            | Qn    |  |  |

| Н     | L             | Х             | 1             | <b></b>       | L             | L     |  |  |

| Н     | L             | X             | 1             | $\downarrow$  | Н             | Н     |  |  |

| Н     | X             | L             | 1             | $\downarrow$  | L             | L     |  |  |

| Н     | X             | L             | 1             | $\downarrow$  | Н             | Н     |  |  |

| Н     | Н             | Н             | 1             | $\downarrow$  | X             | $Q_0$ |  |  |

| Н     | X             | Χ             | L or H        | L or H        | X             | $Q_0$ |  |  |

| L     | X or Floating | L     |  |  |

## **FUNCTION TABLE**

|       | INPUTS        |               |                 |                 |  |  |

|-------|---------------|---------------|-----------------|-----------------|--|--|

| RESET | CLK           | CLK           | DCKE, DCS, DODT | QCKE, QCS, QODT |  |  |

| Н     | <b>↑</b>      | <b>↓</b>      | Н               | Н               |  |  |

| Н     | <b>↑</b>      | $\downarrow$  | L               | L               |  |  |

| Н     | L orH         | L orH         | X               | $Q_0$           |  |  |

| L     | X or Floating | X or Floating | X or Floating   | L               |  |  |

Submit Documentation Feedback

#### PARITY AND STANDBY FUNCTION

|       |               |                  | INP           | UTS           |                                          |                       | OL               | OUTPUTS           |  |

|-------|---------------|------------------|---------------|---------------|------------------------------------------|-----------------------|------------------|-------------------|--|

| RESET | CLK           | CLK              | DCS           | CSR           | Σ OF INPUTS = H<br>D1-D25 <sup>(1)</sup> | PAR_IN <sup>(2)</sup> | PPO              | QERR (3)          |  |

| Н     | 1             | $\downarrow$     | L             | Х             | Even                                     | L                     | L                | Н                 |  |

| Н     | <b>↑</b>      | $\downarrow$     | L             | X             | Odd                                      | L                     | Н                | L                 |  |

| Н     | 1             | $\downarrow$     | L             | Х             | Even                                     | Н                     | Н                | L                 |  |

| Н     | 1             | $\downarrow$     | L             | Х             | Odd                                      | Н                     | L                | Н                 |  |

| Н     | 1             | $\downarrow$     | Н             | L             | Even                                     | L                     | L                | Н                 |  |

| Н     | 1             | $\downarrow$     | Н             | L             | Odd                                      | L                     | Н                | L                 |  |

| Н     | <b>↑</b>      | $\downarrow$     | Н             | L             | Even                                     | Н                     | Н                | L                 |  |

| Н     | 1             | $\downarrow$     | Н             | L             | Odd                                      | Н                     | L                | Н                 |  |

| Н     | 1             | $\downarrow$     | Н             | Н             | X                                        | Χ                     | $PPO_0$          | QERR <sub>0</sub> |  |

| Н     | L or H        | L or H           | Х             | Х             | X                                        | Χ                     | PPO <sub>0</sub> | QERR 0            |  |

| L     | X or Floating | X or<br>Floating | X or Floating | X or Floating | Х                                        | X or Floating         | L                | Н                 |  |

- (1) Data inputs = D2-D3, D5-D6, D8-D25 when C0 = 0 and C1 = 0 Data inputs = D2-D3, D5-D6, D8-D14 when C0 = 0 and C1 = 1 Data inputs = D1-D6, D8-D10, D12, D13 when C0 = 1 and C1 = 1

- PAR\_IN arrives one clock cycle (C0 = 0) or two clock cycles (C0 = 1) after the data to which it applies. This transition assumes that  $\overline{\text{QERR}}$  is high at the crossing of CLK going high and  $\overline{\text{CLK}}$  going low. If QERR goes low, it stays latched low for a minimum of two clock cycles or until RESET is driven low. If two or more consecutive parity errors occur, the QERR output is driven low and latched low for a clock duration equal to the parity duration or until RESET is driven low.

### PARITY ERROR DETECT IN LOW-POWER MODE(1)

| INPUT-DATA<br>ERROR<br>OCCURRENCE <sup>(2)</sup> | 1:1 MODE<br>(C0 = 0, C1 = 0)   |                                 | 1:2 REGISTER-A MODE<br>(C0 = 0, C1 = 1) |                                 | 1:2 REGISTER-B MODE<br>(C0 = 1, C1 = 1) |                                 | CASCADED MODE<br>(Registers A and B) |                                 |

|--------------------------------------------------|--------------------------------|---------------------------------|-----------------------------------------|---------------------------------|-----------------------------------------|---------------------------------|--------------------------------------|---------------------------------|

|                                                  | PPO<br>DURATION <sup>(3)</sup> | QERR<br>DURATION <sup>(3)</sup> | PPO<br>DURATION <sup>(3)</sup>          | QERR<br>DURATION <sup>(3)</sup> | PPO<br>DURATION <sup>(3)</sup>          | QERR<br>DURATION <sup>(3)</sup> | PPO<br>DURATION <sup>(3)</sup>       | QERR<br>DURATION <sup>(3)</sup> |

| n – 4                                            | 1 Cycle                        | 2 Cycles                        | 1 Cycle                                 | 2 Cycles                        | 1 Cycle                                 | 2 Cycles                        | 1 Cycle                              | 2 Cycles                        |

| n – 3                                            | 1 Cycle                        | 2 Cycles                        | 1 Cycle                                 | 2 Cycles                        | 1 Cycle                                 | 2 Cycles                        | 1 Cycle                              | 2 Cycles                        |

| n – 2                                            | 1 Cycle                        | 2 Cycles                        | 1 Cycle                                 | 2 Cycles                        | 1 Cycle                                 | 2 Cycles                        | 1 Cycle                              | 2 Cycles                        |

| n – 1                                            | LPM + 2<br>Cycles              | LPM + 2<br>Cycles               | LPM + 1<br>Cycle                        | LPM + 1<br>Cycle                | LPM + 2<br>Cycles                       | LPM + 2<br>Cycles               | LPM + 2<br>Cycles                    | LPM + 2<br>Cycles               |

| n                                                | Not detected                   | Not detected                    | Not detected                            | Not detected                    | Not detected                            | Not detected                    | Not detected                         | Not detected                    |

- If a parity error occurs before the device enters the low-power mode (LPM), the behavior of PPO and QERR is dependent on the mode of the device and the position of the parity error occurrence. This table illustrates the low-power-mode effect on parity detect. The low-power mode is activated on the n clock cycle when DCS and CSR go high.

- The clock-edge position of a one cycle data-input error relative to the clock-edge (n) which initiates LPM at the DCS and CSR inputs.

- If an error occurs, then QERR output may be driven low and the PPO output driven high. These columns show the clock duration for which the PPO signal will be high.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                                                                              |                                                                               | VALUE                         | UNIT |  |

|------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------|------|--|

| V <sub>CC</sub>  | Supply voltage range                                                         |                                                                               | -0.5 to 2.5                   | V    |  |

| $V_{I}$          | Input voltage range <sup>(2)</sup> (3)                                       | Input voltage range <sup>(2) (3)</sup>                                        |                               |      |  |

| Vo               | Output voltage range (2) (3)                                                 |                                                                               | -0.5 to V <sub>CC</sub> + 0.5 | V    |  |

| I <sub>IK</sub>  | Input clamp current, $(V_I < 0 \text{ or } V_I > V_{CC})$                    | nput clamp current, (V <sub>I</sub> < 0 or V <sub>I</sub> > V <sub>CC</sub> ) |                               |      |  |

| I <sub>OK</sub>  | Output clamp current, (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>O</sub> | ±50                                                                           | mA                            |      |  |

| Io               | Continuous output current (V <sub>O</sub> = 0 to V <sub>CO</sub>             | Continuous output current (V <sub>O</sub> = 0 to V <sub>CC</sub> )            |                               |      |  |

| I <sub>CC</sub>  | Continuous current through each V <sub>CC</sub> or                           | GND                                                                           | ±100                          | mA   |  |

|                  |                                                                              | No airflow                                                                    | 39.8                          |      |  |

| D                | Thermal impedance,                                                           | Airflow 150 ft/min                                                            | 34.1                          |      |  |

| $R_{\theta JA}$  | Thermal impedance, junction-to-ambient <sup>(4)</sup>                        | Airflow 250 ft/min                                                            | 33.6                          | K/W  |  |

|                  |                                                                              | Airflow 500 ft/min                                                            | 32.5                          |      |  |

| $R_{\theta JC}$  | Thermal resistance, junction-to-case <sup>(4)</sup>                          | No airflow                                                                    | 14.5                          |      |  |

| T <sub>stg</sub> | Storage temperature range                                                    |                                                                               | -65 to 150                    | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS<sup>(1)</sup>**

|                 |                                 |                          | MIN                       | NOM                      | MAX                      | UNIT |

|-----------------|---------------------------------|--------------------------|---------------------------|--------------------------|--------------------------|------|

| V <sub>CC</sub> | Supply voltage                  |                          | 1.7                       |                          | 1.9                      | V    |

| $V_{REF}$       | Reference voltage               | Reference voltage        |                           |                          | $0.51 \times V_{CC}$     | V    |

| $V_{TT}$        | Termination voltage             | V <sub>REF</sub> -40 mV  | $V_{REF}$                 | V <sub>REF</sub> + 40 mV | V                        |      |

| VI              | Input voltage                   | 0                        |                           | VCC                      | V                        |      |

| V <sub>IH</sub> | AC high-level input voltage     | Data inputs, CSR, PAR_IN | V <sub>REF</sub> + 250 mV |                          |                          | V    |

| $V_{IL}$        | AC low-level input voltage      | Data inputs, CSR, PAR_IN |                           |                          | V <sub>REF</sub> -250 mV | V    |

| V <sub>IH</sub> | DC high-level input voltage     | Data inputs, CSR, PAR_IN | V <sub>REF</sub> + 125 mV |                          |                          | V    |

| $V_{IL}$        | DC low-level input voltage      | Data inputs, CSR, PAR_IN |                           |                          | V <sub>REF</sub> -125 mV | V    |

| $V_{IH}$        | High-level input voltage        | RESET, C <sub>n</sub>    | 0.65 × V <sub>CC</sub>    |                          |                          | V    |

| $V_{IL}$        | Low-level input voltage         | RESET, C <sub>n</sub>    |                           |                          | $0.35 \times V_{CC}$     | V    |

| $V_{ICR}$       | Common-mode input voltage range | CLK, CLK                 | 0.675                     |                          | 1.125                    | V    |

| $V_{I(PP)}$     | Peak-to-peak input voltage      | CLK, CLK                 | 600                       |                          |                          | mV   |

| I <sub>OH</sub> | High-level output current       | Q outputs, PPO           |                           |                          | -8                       | mA   |

|                 | Low lovel output oursent        | Q outputs, PPO           |                           |                          | 8                        | A    |

| I <sub>OL</sub> | Low-level output current        | QERR output              | 30                        |                          |                          | mA   |

| T <sub>A</sub>  | Operating free-air temperature  |                          | -40                       |                          | 85                       | °C   |

<sup>(1)</sup> The RESET and Cn inputs of the device must be held at valid logic voltage levels (not floating) to ensure proper device operation. The differential inputs must not be floating unless RESET is low. See the TI application report, *Implications of Slow or Floating CMOS Inputs* (SCBA004).

Submit Documentation Feedback

<sup>(2)</sup> The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

<sup>(3)</sup> This value is limited to 2.5 V maximum.

<sup>(4)</sup> The package thermal impedance is calculated in accordance with JESD 51-7.

### **ELECTRICAL CHARACTERISTICS**

over recommended operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                                                                                                                                          | TEST CONDITIONS                                                                                               | V <sub>CC</sub>         | MIN          | TYP <sup>(1)</sup>   | MAX | UNIT |                  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------|--------------|----------------------|-----|------|------------------|

| \ /                | O sutanta DDO                                                                                                                                      | $I_{OH} = -100 \mu A$                                                                                         |                         | 1.7V to 1.9V | V <sub>CC</sub> -0.2 |     |      | V                |

| V <sub>OH</sub>    | Q outputs, PPO                                                                                                                                     | I <sub>OH</sub> = -6 mA                                                                                       | 1.7V                    | 1.3          |                      |     | V    |                  |

|                    | O sutanta DDO                                                                                                                                      | I <sub>OL</sub> = 100 μA                                                                                      | 1.7V to 1.9V            |              |                      | 0.2 |      |                  |

| $V_{OL}$           | Q outputs, PPO                                                                                                                                     | I <sub>OL</sub> = 6 mA                                                                                        | 1.7V                    |              |                      | 0.4 | V    |                  |

|                    | QERR output                                                                                                                                        | I <sub>OL</sub> = 25 mA                                                                                       | l <sub>OL</sub> = 25 mA |              |                      |     | 0.5  |                  |

|                    | DAD IN                                                                                                                                             | V <sub>I</sub> = GND                                                                                          |                         |              |                      |     | -5   |                  |

| I                  | PAR_IN                                                                                                                                             | $V_I = V_{CC}$                                                                                                |                         | 1.9V         |                      |     | 25   | μΑ               |

|                    | All other inputs <sup>(2)</sup>                                                                                                                    | V <sub>I</sub> = V <sub>CC</sub> or GND                                                                       |                         |              |                      |     | ±5   | ·                |

| l <sub>OZ</sub>    | QERR output                                                                                                                                        | VO = V <sub>CC</sub> or GND                                                                                   |                         | 1.9V         |                      |     | ±10  | μΑ               |

|                    | Static standby                                                                                                                                     | RESET = GND                                                                                                   |                         |              |                      |     | 200  | μΑ               |

| I <sub>CC</sub>    | Static operating                                                                                                                                   | $\overline{\text{RESET}} = V_{CC}, V_{I} = V_{IH(AC)} \text{ or } V_{IL(AC)}$                                 | I <sub>O</sub> = 0      | 1.9V         |                      |     | 40   | mA               |

|                    | only V <sub>IL(AC)</sub> , CL                                                                                                                      |                                                                                                               |                         |              |                      | 45  |      | μΑ/MHz           |

| I <sub>CCD</sub>   | Dynamic operating – per each data input, 1:1 configuration                                                                                         |                                                                                                               | I <sub>O</sub> = 0      | 1.8V         |                      | 43  |      | μΑ clock<br>MHz/ |

|                    | Dynamic operating – per each data input, 1:2 configuration                                                                                         | switching at one-half clock<br>frequency, 50% duty cycle                                                      |                         |              |                      | 60  |      | D input          |

|                    | Chip-select-enabled<br>low-power active mode –<br>clock only                                                                                       |                                                                                                               |                         |              |                      | 45  |      | μΑ/MHz           |

| I <sub>CCDLP</sub> | Chip-select-enabled low-power active mode - 1:1 configuration                                                                                      | RESET = V <sub>CC</sub> , V <sub>I</sub> = V <sub>IH(AC)</sub> or V <sub>IL(AC)</sub> , CLK and CLK switching | , CLK and CLK switching | 1.8V         |                      | 2   |      | μΑ clock<br>MHz/ |

|                    | Chip-select-enabled low-power active mode – 1:2 configuration 50% duty cycle, one data input switching at one-half clock frequency, 50% duty cycle |                                                                                                               |                         |              |                      | 3   |      | D input          |

|                    | Data inputs, CSR, PAR_IN                                                                                                                           | V <sub>I</sub> = V <sub>REF</sub> ± 250 mV                                                                    |                         |              | 2.5                  | 3   | 3.5  |                  |

| CI                 | CLK, CLK                                                                                                                                           | $V_{ICR} = 0.9 \text{ V}, V_{I(PP)} = 600 \text{ mV}$                                                         |                         | 1.8V         | 2                    |     | pF   |                  |

|                    | RESET                                                                                                                                              | V <sub>I</sub> = V <sub>CC</sub> or GND                                                                       |                         |              |                      | 4   |      |                  |

<sup>(1)</sup> All typical values are at  $V_{CC}$  = 1.8 V,  $T_A$  = 25°C. (2) Each  $V_{REF}$  pin (A3 or T3) should be tested independently, with the other (untested) pin open.

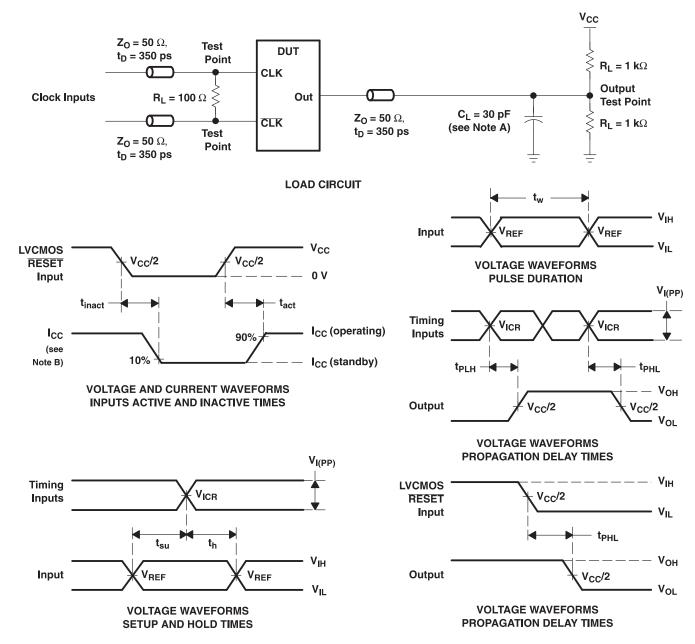

#### TIMING REQUIREMENTS

over recommended operating free-air temperature range (unless otherwise noted) (see Figure 2 and (1)

|                 |                |                                                                                                                                                                                                                | V <sub>CC</sub> = 1.8 V | ± 0.1 V | UNIT |

|-----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------|------|

|                 |                |                                                                                                                                                                                                                | MIN                     | MAX     | UNII |

| fclock          | Clock freque   | ency                                                                                                                                                                                                           |                         | 410     | MHz  |

| tw              | Pulse durati   | on, CLK, CLK high or low                                                                                                                                                                                       | 1                       |         | ns   |

| tact            | Differential i |                                                                                                                                                                                                                | 10                      | ns      |      |

| tinact          | Differential i | nputs inactive time <sup>(3)</sup>                                                                                                                                                                             |                         | 15      | ns   |

|                 |                | $\overline{\text{DCS}}$ before CLK $\uparrow$ , $\overline{\text{CLK}}$ , $\overline{\text{CSR}}$ high; $\overline{\text{CSR}}$ before CLK $\uparrow$ , $\overline{\text{CLK}}$ , $\overline{\text{DCS}}$ high | 600                     |         |      |

|                 | Catum time     | DCS before CLK↑, CLK↓, CSR low                                                                                                                                                                                 | 500                     |         |      |

| t <sub>su</sub> | Setup time     | DODT, DCKE, and Data before CLK↑, CLK↓                                                                                                                                                                         | 500                     |         | ps   |

|                 |                | PAR_IN before CLK↑, CLK↓                                                                                                                                                                                       | 500                     |         |      |

|                 | Hold time      | DCS, DODT, DCKE, and Data after CLK↑, CLK↓                                                                                                                                                                     | 400                     |         | 20   |

| ι <sub>h</sub>  | Hold time      | PAR_IN after CLK↑, CLK↓                                                                                                                                                                                        | 400                     |         | ps   |

All inputs slew rate is 1 V/ns ± 20%.

#### **SWITCHING CHARACTERISTICS**

over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER                        |                               | FROM          | то       | $V_{CC} = 1.8 V \pm$ | 0.1 V | LINUT |

|----------------------------------|-------------------------------|---------------|----------|----------------------|-------|-------|

|                                  |                               | (INPUT)       | (OUTPUT) | MIN                  | MAX   | UNIT  |

| f <sub>max</sub>                 | See Figure 2                  |               |          | 410                  |       | MHz   |

| t <sub>pdm</sub>                 | Production test, See Figure 1 | CLK and CLK   | Q        | 0.4                  | 0.8   | ns    |

| t <sub>pd</sub>                  | See Figure 5                  | CLK and CLK   | PPO      | 0.6                  | 1.6   | ns    |

| t <sub>PLH</sub>                 | Con Figure 4                  | CLIV and CLIV | OFF      | 1.2                  | 2.4   |       |

| t <sub>PHL</sub>                 | See Figure 4                  | CLK and CLK   | QERR     | 1                    | 2.0   | ns    |

| t <sub>RPHL</sub> <sup>(1)</sup> | See Figure 2                  | RESET         | Q        |                      | 3     |       |

| t <sub>RPHL</sub>                | See Figure 5                  | RESEI         | PPO      |                      | 3     | ns    |

| t <sub>RPLH</sub>                | See Figure 5                  | RESET         | QERR     |                      | 3     | ns    |

<sup>(1)</sup> Includes 350-ps test-load transmission-line delay.

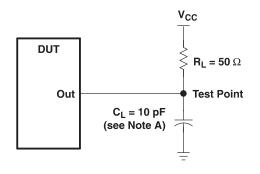

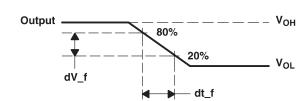

#### **OUTPUT SLEW RATES**

over recommended operating free-air temperature range (unless otherwise noted) (see Figure 2)

| PARAMETER             | FROM       | то         | V <sub>CC</sub> = 1.8 V : | UNIT |      |

|-----------------------|------------|------------|---------------------------|------|------|

| FARAMETER             | FROW       | 10         | MIN                       | MAX  | ONIT |

| dV/dt_r               | 20%        | 80%        | 1                         | 4    | V/ns |

| dV/dt_f               | 80%        | 20%        | 1                         | 4    | V/ns |

| $dV/dt\_\Delta^{(1)}$ | 20% or 80% | 80% or 20% |                           | 1    | V/ns |

(1) Difference between dV/dt\_r (rising edge rate) and dV/dt\_f (falling edge rate).

Submit Documentation Feedback

$V_{REF}$  must be held at a valid input level, and data inputs must be held low for a minimum time of  $t_{act}$  max, after  $\overline{RESET}$  is taken high.  $V_{REF}$ , data, and clock inputs must be held at valid voltage levels (not floating) for a minimum time of  $t_{inact}$  max, after  $\overline{RESET}$  is taken low.

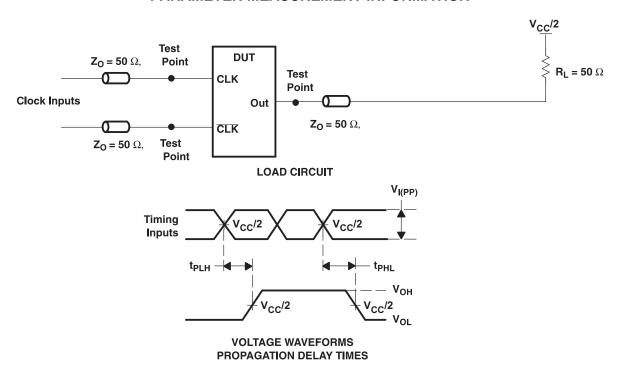

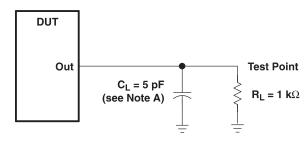

### PARAMETER MEASUREMENT INFORMATION

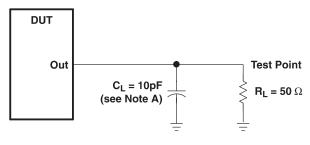

Figure 1. Output Load For Production Test

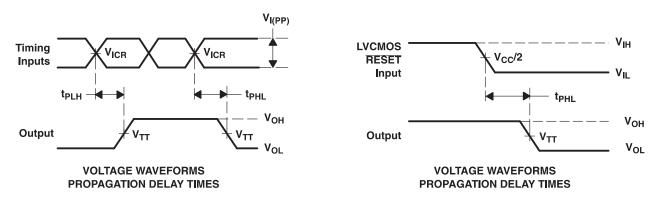

## PROPAGATION DELAY (Design Goal as per JEDEC Specification)

| DADAMETED                         | FROM        | ТО       | V <sub>CC</sub> = 1.8 V | UNIT |      |

|-----------------------------------|-------------|----------|-------------------------|------|------|

| PARAMETER                         | (INPUT)     | (OUTPUT) | MIN                     | MAX  | UNII |

| t <sub>pdm</sub> <sup>(1)</sup>   | CLK and CLK | Q        | 1.1                     | 1.5  | ns   |

| t <sub>pdmss</sub> <sup>(1)</sup> | CLK and CLK | Q        |                         | 1.6  | ns   |

(1) Includes 350 psi test-load transmission delay line

NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

- B.  $I_{CC}$  tested with clock and data inputs held at  $V_{CC}$  or GND, and  $I_{O} = 0$  mA.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O = 50~\Omega$ , input slew rate = 1 V/ns  $\pm$ 20% (unless otherwise noted).

- D. The outputs are measured one at a time, with one transition per measurement.

- E.  $V_{REF} = V_{TT} = V_{CC}/2$

- F.  $V_{IH} = V_{REF} + 250$  mV (ac voltage levels) for differential inputs.  $V_{IH} = V_{CC}$  for LVCMOS input.

- G.  $V_{IL} = V_{REF} 250$  mV (ac voltage levels) for differential inputs.  $V_{IL} = GND$  for LVCMOS input.

- H.  $V_{I(PP)} = 600 \text{ mV}$

- I. t<sub>PLH</sub> and t<sub>PHL</sub> are the same as t<sub>pd</sub>.

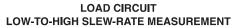

Figure 2. Data Output Load Circuit and Voltage Waveforms

LOAD CIRCUIT

HIGH-TO-LOW SLEW-RATE MEASUREMENT

VOLTAGE WAVEFORMS

HIGH-TO-LOW SLEW-RATE MEASUREMENT

VOLTAGE WAVEFORMS

LOW-TO-HIGH SLEW-RATE MEASUREMENT

NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

B. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O = 50~\Omega$ , input slew rate = 1 V/ns  $\pm$  20% (unless otherwise specified).

Figure 3. Data Output Slew-Rate Measurement Information

NOTES: A.  $C_L$  includes probe and jig capacitance.

- B. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O = 50~\Omega$ , input slew rate = 1 V/ns  $\pm$ 20% (unless otherwise noted).

- C.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{pd}$ .

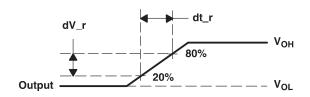

Figure 4. Error Output Load Circuit and Voltage Waveforms

#### **LOAD CIRCUIT**

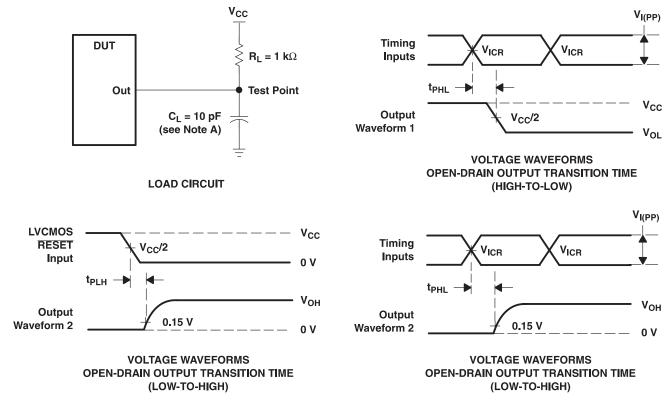

- NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

- B. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O = 50~\Omega$ , input slew rate = 1 V/ns  $\pm$ 20% (unless otherwise noted).

- C.  $V_{REF} = V_{TT} = V_{CC}/2$

- D.  $V_{IH} = V_{REF} + 250$  mV (ac voltage levels) for differential inputs.  $V_{IH} = V_{CC}$  for LVCMOS input.

- E.  $V_{IL} = V_{REF} 250$  mV (ac voltage levels) for differential inputs.  $V_{IL} = GND$  for LVCMOS input.

- F.  $V_{I(PP)} = 600 \text{ mV}$

- G.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{pd}$ .

Figure 5. Partial-Parity-Out Load Circuit and Voltage Waveforms

#### **APPLICATION INFORMATION**

The typical values below are for standard raw cards. Test equipment used was the JEDEC register validation board using pattern 0x43, 0x4F, and 0x5A.

Table 1. Raw Card Values (1) (2)

| RAW CARD | t <sub>pd</sub> | OVERSHOOT |        |

|----------|-----------------|-----------|--------|

|          | MIN             | MAX       |        |

| A/F      | 1.2 ns          | 1.6 ns    | 140 mV |

| B/G      | 1.3 ns          | 2.0 ns    | 430 mV |

| C/H      | 1.3 ns          | 2.0 ns    | 430 mV |

- All values are valid under nominal conditions and minimum/maximum of typical signals on one typical DIMM.

- (2) Measurements include all jitter and ISI effects.

## SN74SSTUB32866 Used as a Single Device in the 1:1 Register Configuration; C0 = 0, C1 = 0

Register 1 of 1

<sup>&</sup>lt;sup>†</sup> This function holds the error for two cycles. For details, see the parity logic diagram.

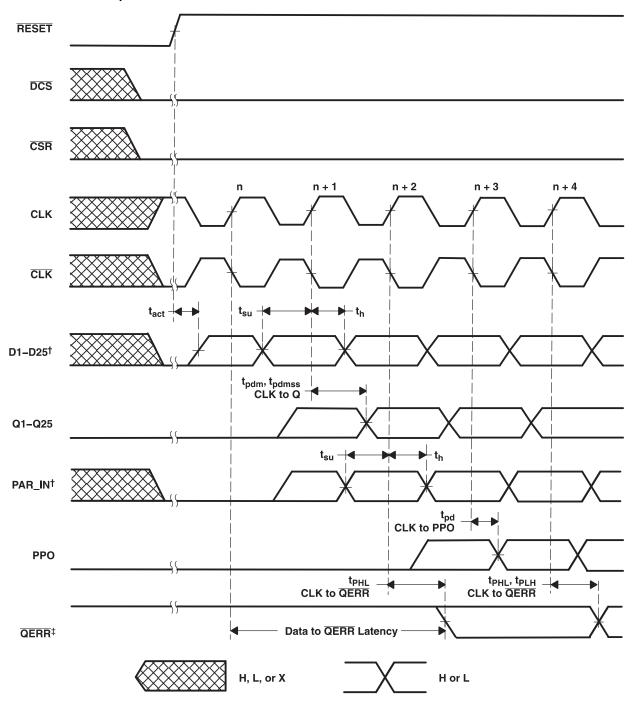

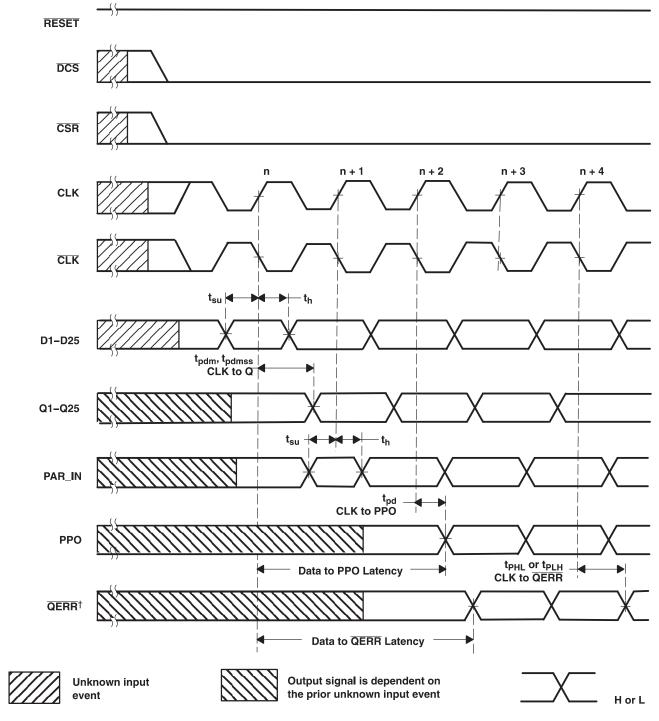

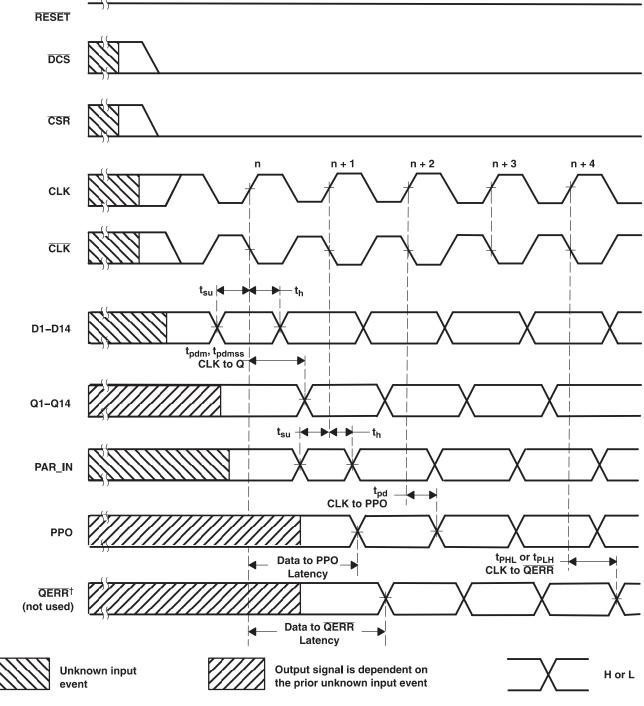

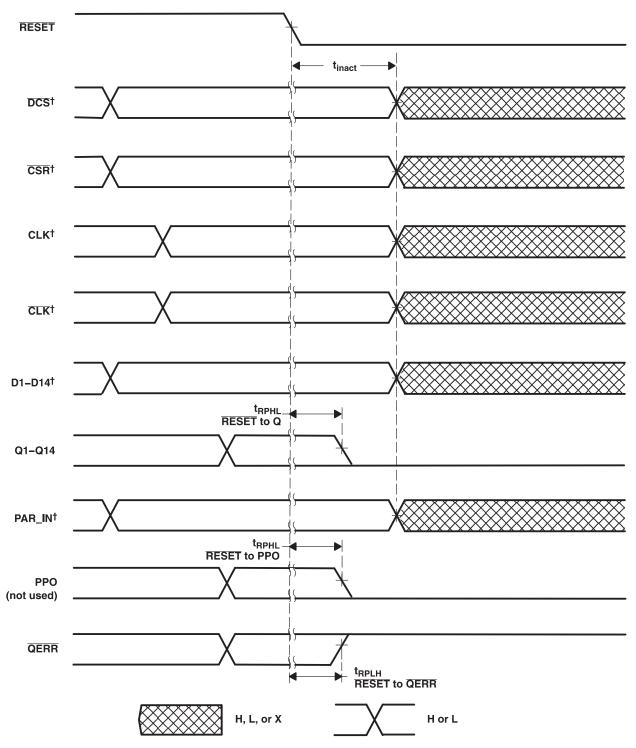

# Timing Diagram for SN74SSTUB32866 Used as a Single Device; C0 = 0, C1 = 0 (RESET Switches From L to H)

<sup>†</sup> After RESET is switched from low to high, all data and PAR\_IN input signals must be set and held low for a minimum time of t<sub>act</sub> max, to avoid false error.

<sup>‡</sup>If the data is clocked in on the n clock pulse, the QERR output signal will be generated on the n + 2 clock pulse, and it will be valid on the n + 3 clock pulse.

## Timing Diagram for SN74SSTUB32866 Used as a Single Device; C0 = 0, C1 = 0 (RESET = H)

<sup>†</sup> If the data is clocked in on the n clock pulse, the QERR output signal will be generated on the n + 2 clock pulse, and it will be valid on n + 3 clock pulse. If an error occurs and the QERR output is driven low, it stays latched low for a minimum of two clock cycles or until RESET is driven low.

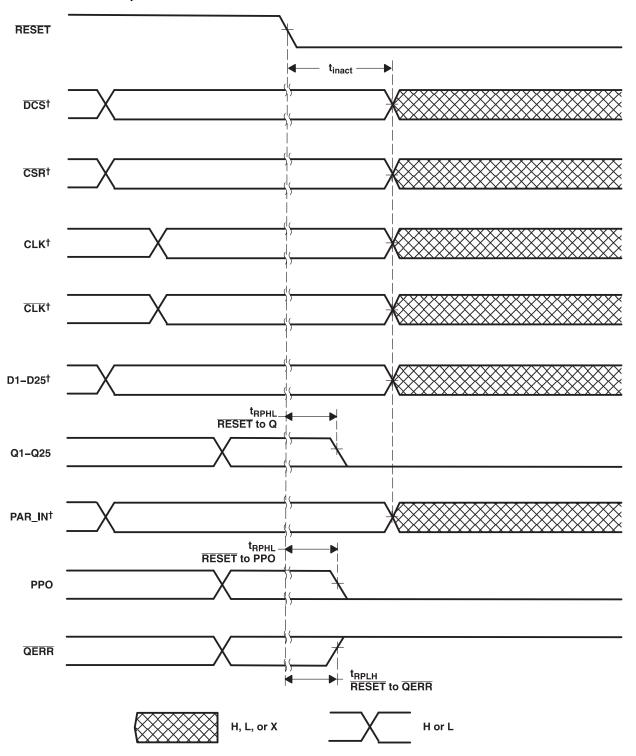

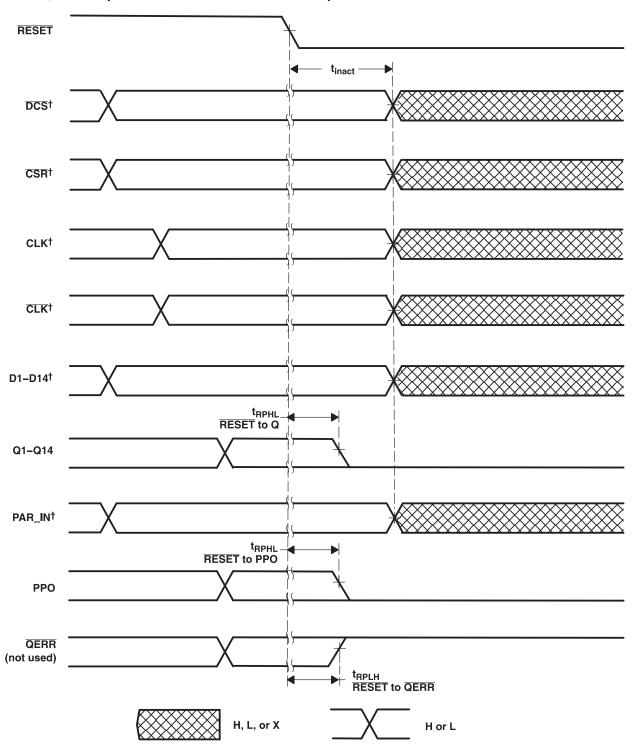

# Timing Diagram for SN74SSTUB32866 Used as a Single Device; C0 = 0, C1 = 0 (RESET Switches From = H to L)

<sup>†</sup> After RESET is switched from high to low, all data and clock input signals must be held at valid logic levels (not floating) for a minimum time of t<sub>inact</sub> max.

## SN74SSTUB32866 Used in Pair in the 1:2 Register Configuration

Register 1 of 2 (1:2 Register-A Configuration); C0 = 0, C1 = 1

<sup>&</sup>lt;sup>†</sup> This function holds the error for two cycles. For details, see the parity logic diagram.

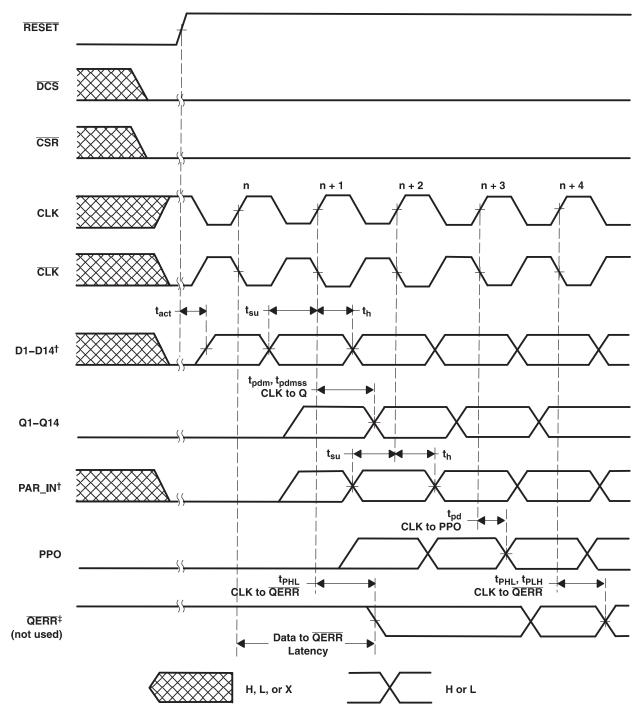

# Timing Diagram for the First SN74SSTUB32866 (1:2 Register-A Configuration) Device Used in Pair; C0 = 0, C1 = 1 (RESET Switches From L to H)

<sup>†</sup> After RESET is switched from low to high, all data and PAR\_IN input signals must be set and held low for a minimum time of t<sub>act</sub> max, to avoid false error.

$<sup>^{\</sup>ddagger}$ If the data is clocked in on the n clock pulse, the  $\overline{\text{QERR}}$  output signal will be generated on the n + 1 clock pulse, and it will be valid on the n + 2 clock pulse.

# Timing Diagram for the First SN74SSTUB32866 (1:2 Register-A Configuration) Device Used in Pair; C0 = 0, C1 = 1 (RESET = H)

<sup>†</sup> If the data is clocked in on the n clock pulse, the QERR output signal will be generated on the n + 1 clock pulse, and it will be valid on n + 2 clock pulse. If an error occurs and the QERR output is driven low, it stays latched low for a minimum of two clock cycles or until RESET is driven low.

# Timing Diagram for the First SN74SSTUB32866 (1:2 Register-A Configuration) Device Used in Pair; C0 = 0, C1 = 1 (RESET = Switches From H to L)

<sup>†</sup> After RESET is switched from high to low, all data and clock input signals must be held at valid logic levels (not floating) for a minimum time of t<sub>inact</sub> max.

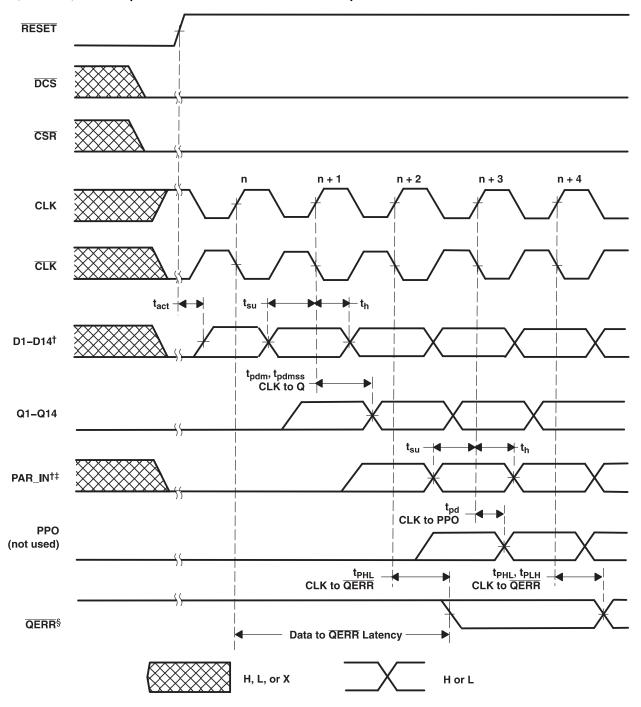

# Timing Diagram for the Second SN74SSTUB32866 (1:2 Register-B Configuration) Device Used in Pair; C0 = 1, C1 = 1 (RESET = Switches From L to H)

<sup>&</sup>lt;sup>†</sup> After RESET is switched from low to high, all data and PAR\_IN input signals must be set and held low for a minimum time of t<sub>act</sub> max, to avoid false error.

<sup>&</sup>lt;sup>‡</sup>PAR\_IN is driven from PPO of the first SN74SSTUB32866 device.

<sup>§</sup> If the data is clocked in on the n clock pulse, the QERR output signal will be generated on the n + 2 clock pulse, and it will be valid on the n + 3 clock pulse.

# Timing Diagram for the Second SN74SSTUB32866 (1:2 Register-B Configuration) Device Used in Pair; C0 = 1, C1 = 1 (RESET = H)

<sup>&</sup>lt;sup>†</sup> PAR\_IN is driven from PPO of the first SN74SSTUB32866 device.

<sup>‡</sup>If the data is clocked in on the n clock pulse, the QERR output signal will be generated on the n + 2 clock pulse, and it will be valid on n + 3 clock pulse. If an error occurs and the QERR output is driven low, it stays latched low for a minimum of two clock cycles or until RESET is driven low.

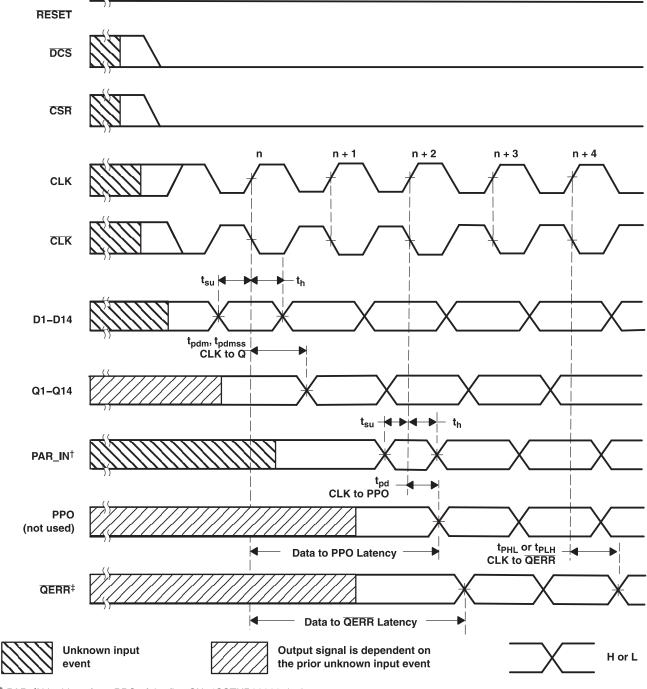

# Timing Diagram for the Second SN74SSTUB32866 (1:2 Register-B Configuration) Device Used in Pair; C0 = 1, C1 = 1 (RESET = Switches From H to L)

<sup>&</sup>lt;sup>†</sup> After RESET is switched from high to low, all data and clock input signals must be held at valid logic levels (not floating) for a minimum time of t<sub>inact</sub> max.

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|------------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                  |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                  |                       |      | (4)           | (5)                 |              |              |

| SN74SSTUB32866NMJR    | Active | Production    | NFBGA (NMJ)   96 | 1000   LARGE T&R      | Yes  | SNAGCU        | Level-3-260C-168 HR | -40 to 85    | SB866        |

| SN74SSTUB32866NMJR.B  | Active | Production    | NFBGA (NMJ)   96 | 1000   LARGE T&R      | Yes  | SNAGCU        | Level-3-260C-168 HR | -40 to 85    | SB866        |

| SN74SSTUB32866ZWLR    | Active | Production    | BGA (ZWL)   96   | 1000   LARGE T&R      | Yes  | SNAGCU        | Level-3-260C-168 HR | -40 to 85    | SB866        |

| SN74SSTUB32866ZWLR.B  | Active | Production    | BGA (ZWL)   96   | 1000   LARGE T&R      | Yes  | SNAGCU        | Level-3-260C-168 HR | -40 to 85    | SB866        |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Dec-2023

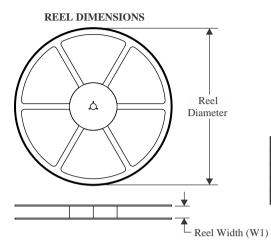

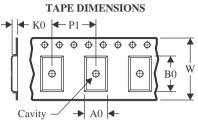

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

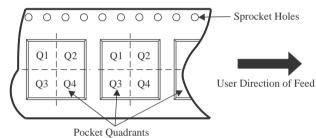

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device             | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN74SSTUB32866NMJR | NFBGA           | NMJ                | 96 | 1000 | 330.0                    | 24.4                     | 5.7        | 13.7       | 2.0        | 8.0        | 24.0      | Q1               |

| SN74SSTUB32866ZWLR | BGA             | ZWL                | 96 | 1000 | 330.0                    | 24.4                     | 5.7        | 13.7       | 2.0        | 8.0        | 24.0      | Q1               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Dec-2023

## \*All dimensions are nominal

| Device             | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN74SSTUB32866NMJR | NFBGA        | NMJ             | 96   | 1000 | 350.0       | 350.0      | 43.0        |

| SN74SSTUB32866ZWLR | BGA          | ZWL             | 96   | 1000 | 350.0       | 350.0      | 43.0        |

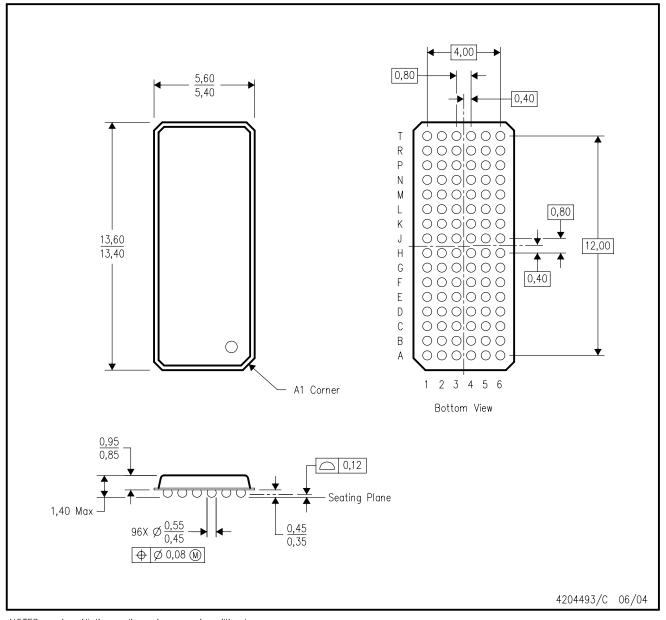

# ZKE (R-PBGA-N96)

## PLASTIC BALL GRID ARRAY

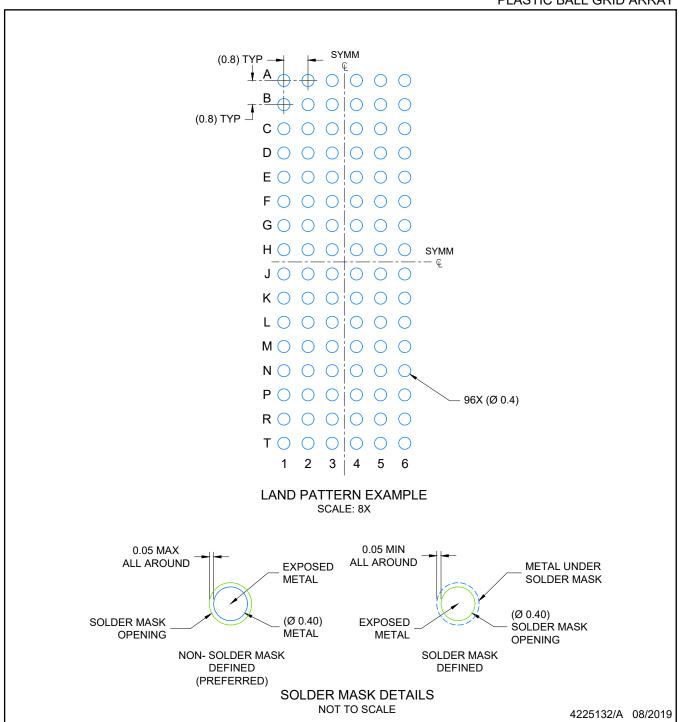

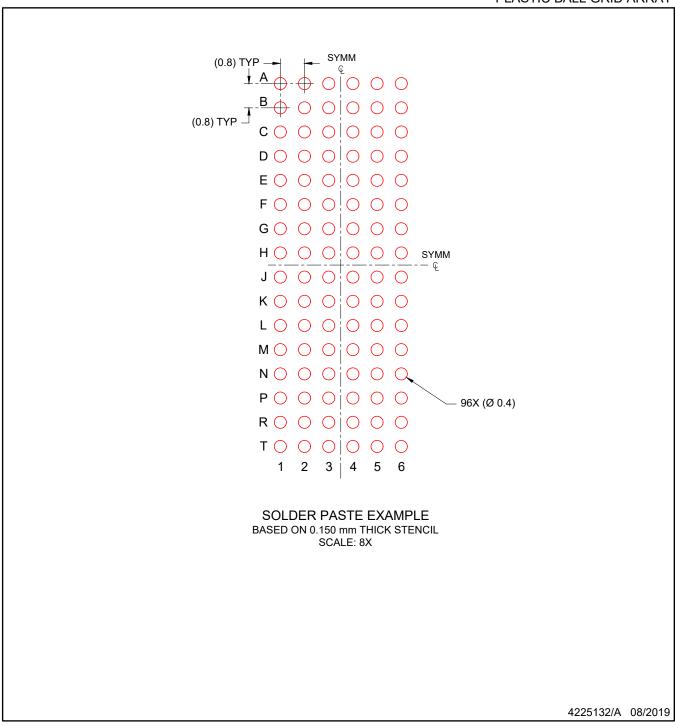

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MO-205 variation CC.

- D. This package is lead-free. Refer to the 96 GKE package (drawing 4188953) for tin-lead (SnPb).

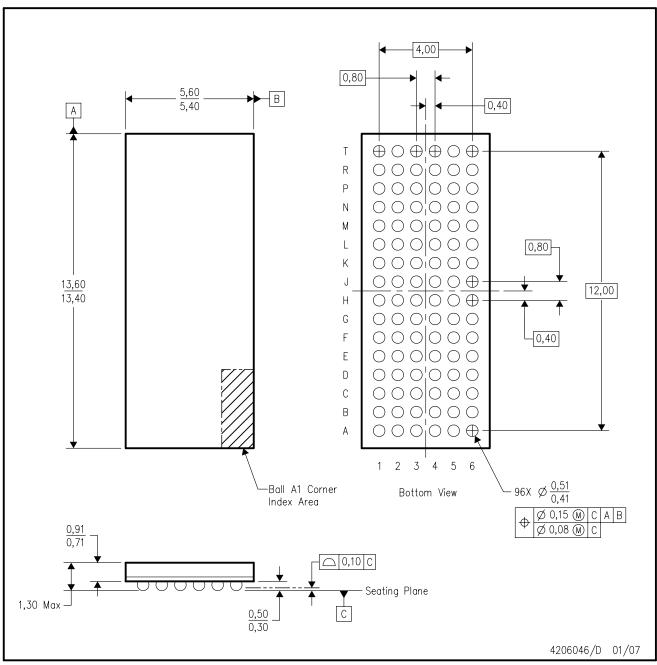

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MO-205 variation CC.

- D. This package is lead-free. Refer to the 96 GWL package (drawing 4206045) for tin-lead (SnPb).

PLASTIC BALL GRID ARRAY

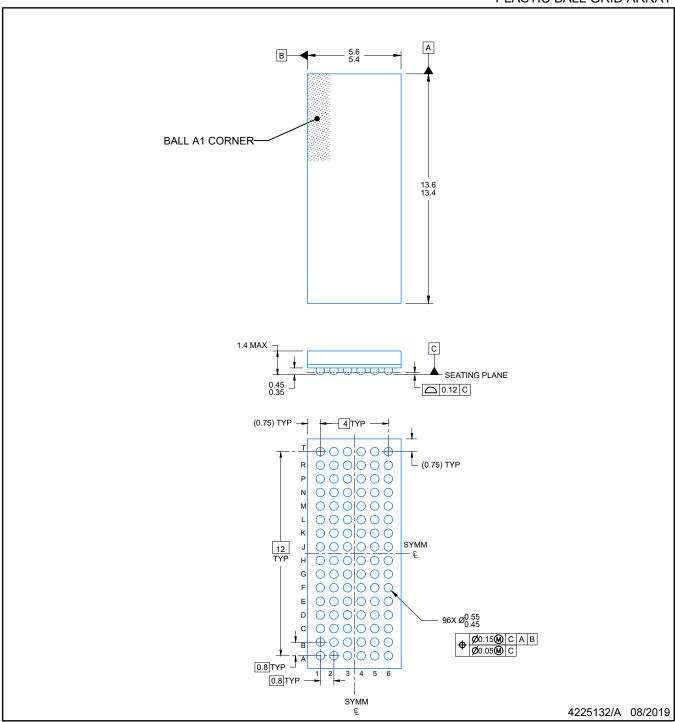

NOTES:

NanoFree is a trademark of Texas Instruments.

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

PLASTIC BALL GRID ARRAY

NOTES: (continued)

3. Final dimensions may vary due to manufacturing tolerance considerations and also routing constraints. Refer to Texas Instruments Literature number SNVA009 (www.ti.com/lit/snva009).

PLASTIC BALL GRID ARRAY

NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025