**TLC5973**

ZHCSAX3B-MARCH 2013-REVISED MAY 2014

## TLC5973 3 通道, 12位, 脉宽调制 (PWM) 恒定电流发光二极管 (LED) 驱 动器

# 具有单线制接口 (EasySet™)

## 特性

- 3个恒定灌电流通道

- 电流处理能力:

- 每通道 2mA 至 35mA (VCC ≤ 4.0V)

- 每通道 2mA 至 50mA (VCC > 4.0V)

- 支持 PWM 的灰度 (GS) 控制:

- 12位(4096 步长)

- 单线制接口 (EasySet)

- 电源 (VCC) 电压范围:

- 3V 至 6V

- OUT 引脚最大电压: 最高 21V

- 集成型并联稳压器

- 数据传输最大速率:

- 每秒位数 (bps): 3Mbps

- 内部 GS 时钟振荡器: 12MHz(典型值)

- 显示重复率: 2.9kHz (典型值)

- 输出延迟开关以防止涌入电流

- 不受限器件级联

- 运行温度: -40°C 至 85°C

## 2 应用范围

这款器件针对一类应用。这款器件的主要应用是 RGB LED 灯簇显示屏。

## 3 说明

TLC5973 是一款易于使用, 3 通道, 50mA 恒定灌电 流 LED 驱动器。 这个单线制,

3Mbps 串行接口 (EasySet) 提供了一个最大限度减少 配线成本的解决方案。 LED 驱动器提供 12 位脉宽调 制 (PWM) 分辨率。显示重复率使用一个集成型

12MHz 灰度 (GS) 时钟振荡器在 2.9kHz (典型值) 上 实现。此驱动器还提供不受限级联功能。

所有输出恒定灌电流可由一个外部电阻器设定。 TLC5973 有一个可用于更高 VCC 电源电压应用的内

部并联稳压器。

#### 器件信息(1)

| 88 11 IA G |                         |                |  |  |  |  |

|------------|-------------------------|----------------|--|--|--|--|

| 器件名称       | 封装                      | 封装尺寸           |  |  |  |  |

| TLC5973    | 小外形尺寸集成电路<br>(SOIC) (8) | 4.9mm x 3.91mm |  |  |  |  |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

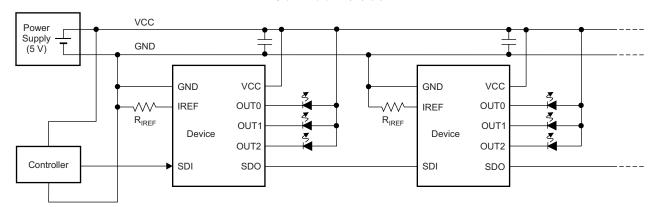

#### 典型应用电路示例

| 1 | 特性 1                                          |      | 8.1 Overview                         |    |

|---|-----------------------------------------------|------|--------------------------------------|----|

| 2 | 应用范围 1                                        |      | 8.2 Functional Block Diagram         | 11 |

| 3 | 说明 1                                          |      | 8.3 Feature Description              | 11 |

| 4 | 修订历史记录 2                                      |      | 8.4 Device Functional Modes          | 13 |

| 5 | Pin Configuration and Functions               |      | 8.5 Programming                      | 19 |

| 6 |                                               |      | 8.6 Register Maps                    | 21 |

| О | Specifications                                | 9    | Applications and Implementation      | 22 |

|   | 6.1 Absolute Maximum Ratings                  |      | 9.1 Application Information          |    |

|   | 6.2 Handling Ratings                          |      | 9.2 Typical Applications             |    |

|   | 6.3 Recommended Operating Conditions          | 10   | Power Supply Recommendations         |    |

|   | 6.4 Thermal Information                       | 11   | Layout                               |    |

|   | 6.5 Electrical Characteristics5               | - '' |                                      |    |

|   | 6.6 Switching Characteristics 6               |      | 11.1 Layout Guidelines               |    |

|   | 6.7 Typical Characteristics 6                 |      | 11.2 Layout Example                  | 28 |

| 7 | Parameter Measurement Information 7           | 12   | 器件和文档支持                              | 29 |

| - | 7.1 Pin-Equivalent Input and Output Schematic |      | 12.1 Trademarks                      | 29 |

|   | Diagrams                                      |      | 12.2 Electrostatic Discharge Caution | 29 |

|   | 7.2 Test Circuits 7                           |      | 12.3 Glossary                        |    |

|   | 7.3 Timing Diagrams 8                         | 13   | 机械封装和可订购信息                           | 29 |

| 8 | Detailed Description 10                       |      |                                      |    |

|   |                                               |      |                                      |    |

## 4 修订历史记录

| Cr | nanges from Revision A (May 2013) to Revision B                                                                                                                                                                                                         | Page           |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| •  | 已将格式更改为符合最新的数据表标准;已添加应用范围和执行,电源建议,和布局布线章节,已移动现有章节                                                                                                                                                                                                       | 1              |

| •  | 已将说明部分中的 8 位脉宽调制 更改为 12 位脉宽调制                                                                                                                                                                                                                           | 1              |

| •  | Changed t <sub>H0</sub> and t <sub>H1</sub> parameter units from µs to ns in Recommended Operating Conditions table                                                                                                                                     | 4              |

| •  | Changed Figure 8: deleted top SDO, changed bottom SDO to OUTn                                                                                                                                                                                           | <mark>7</mark> |

| •  | Changed Figure 11: deleted extraneous breaks in traces, extraneous data call-outs, and t <sub>H1</sub> on GSLAT trace, changed data transfer trace note to <i>Internal to 1st Device</i> and 1st Data to 47th Data in 48-Bit Shift Register LSB traces. | e 9            |

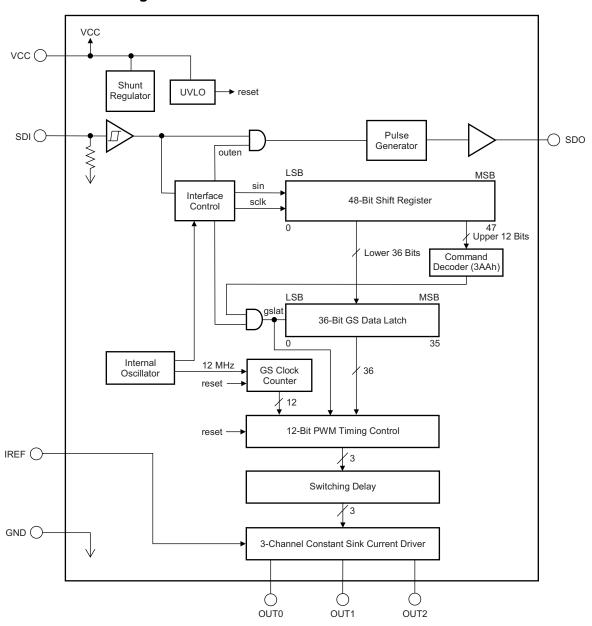

| •  | Changed functional block diagram: changed Upper 8 Bits to Upper 12 Bits on 48-Bit Shift Register block                                                                                                                                                  | 11             |

| •  | Added Grayscale (GS) Control, EasySet and Shunt Regulator, and No Limit Cascading sections                                                                                                                                                              | 11             |

| •  | Changed Connector Design title                                                                                                                                                                                                                          | 13             |

| •  | Changed Figure 13: changed OUTn traces GSDATA = 4093 and GSDATA = 4094                                                                                                                                                                                  | 15             |

| •  | Changed description of the Data '0' and Data '1' Write Sequence (Data Write Sequence) section                                                                                                                                                           | 16             |

| •  | Changed title of Controlling Devices Connected in Series section                                                                                                                                                                                        | 19             |

| •  | Changed Data 101 to Data 1010 in Figure 18                                                                                                                                                                                                              | 19             |

| •  | Changed eight MSBs to 12 MSBs in third sentence of the Register and Data Latch Configuration section                                                                                                                                                    | 21             |

| •  | Changed Figure 21: corrected 3AAh bit set sequence                                                                                                                                                                                                      | 21             |

| •  | Changed Figure 26: changed number of LEDs in optional dashed box                                                                                                                                                                                        | 26             |

| •  | Changed Table 7: changed all values in R <sub>VCC</sub> column and first and last values in Resistor Wattage column                                                                                                                                     | 27             |

| Cł | nanges from Original (March 2013) to Revision A                                                                                                                                                                                                         | Page           |

| •  | Changed second paragraph of Grayscale (GS) Function (PWM Control) section                                                                                                                                                                               | 13             |

| •  | Changed t <sub>CYCLE</sub> setting range in <i>Data Transfer Rate</i> (t <sub>CYCLE</sub> ) <i>Measurement Sequence</i> section                                                                                                                         | 16             |

| •  | Updated Figure 18                                                                                                                                                                                                                                       | 19             |

| •  | Updated Figure 21 and Table 3                                                                                                                                                                                                                           | 21             |

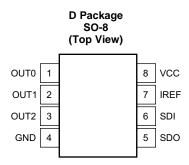

## 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN  |     |     |                                                                                                                                                                               |  |

|------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME | NO. | 1/0 | DESCRIPTION                                                                                                                                                                   |  |

| OUT0 | 1   | 0   | Constant sink current driver outputs.                                                                                                                                         |  |

| OUT1 | 2   | 0   | Multiple outputs can be configured in parallel to increase the sink drive current capability.                                                                                 |  |

| OUT2 | 3   | 0   | Different voltages can be applied to each output.                                                                                                                             |  |

| GND  | 4   | _   | Power ground                                                                                                                                                                  |  |

| SDO  | 5   | 0   | Serial data output                                                                                                                                                            |  |

| SDI  | 6   | I   | Serial data input. This pin is internally pulled down to GND with a 1-M $\Omega$ (typ) resistor.                                                                              |  |

| IREF | 7   | I/O | Output current programming pin. A resistor connected between IREF and GND sets the current for each constant-current output. Place the external resistor close to the device. |  |

| VCC  | 8   | _   | Power-supply voltage                                                                                                                                                          |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                                |                                |              | MIN  | MAX                   | UNIT |

|------------------------------------------------|--------------------------------|--------------|------|-----------------------|------|

|                                                | Supply, V <sub>CC</sub>        | VCC          | -0.3 | 7.0                   | V    |

| Voltage <sup>(2)</sup>                         | Input range, V <sub>IN</sub>   | SDI          | -0.3 | V <sub>CC</sub> + 1.2 | V    |

| Voltage (=)                                    | Output range \/                | OUT0 to OUT2 | -0.3 | 21                    | V    |

|                                                | Output range, V <sub>OUT</sub> | SDO          | -0.3 | 7.0                   | V    |

| Current                                        | Output (dc), I <sub>OUT</sub>  | OUT0 to OUT2 | 0    | 60                    | mA   |

| Operating junction temperature, T <sub>J</sub> |                                |              | -40  | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods my affect device reliability.

(2) All voltages are with respect to network ground pin.

## 6.2 Handling Ratings

|                    |                                                                                                                                                                          |       | MIN             | MAX   | UNIT |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|-------|------|

| T <sub>stg</sub>   | T <sub>stg</sub> Storage temperature range                                                                                                                               |       | <del>-</del> 55 | 150   | °C   |

| V                  | Electrostatic discharge  Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)  Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) |       | -8000           | 8000  | V    |

| V <sub>(ESD)</sub> |                                                                                                                                                                          | -2000 | 2000            | v<br> |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

|                        | PARAMETER                            | TEST CONDITIONS                  | MIN                    | NOM                   | MAX                    | UNIT |

|------------------------|--------------------------------------|----------------------------------|------------------------|-----------------------|------------------------|------|

| DC CHARA               | CTERISTICS                           |                                  | 1                      |                       |                        |      |

| V                      | Cupply voltage                       | No internal shunt regulator mode | 3.0                    | 5.0                   | 5.5                    | V    |

| V <sub>CC</sub>        | Supply voltage                       | Internal shunt regulator mode    |                        |                       | 6.0                    | V    |

| Vo                     | Voltage applied to output            | OUT0 to OUT2                     |                        |                       | 21                     | V    |

| V <sub>IH</sub>        | High-level input voltage             | SDI                              | $0.7 \times V_{CC}$    |                       | $V_{CC}$               | V    |

| V <sub>IL</sub>        | Low-level input voltage              | SDI                              | GND                    |                       | 0.3 × V <sub>CC</sub>  | V    |

| V <sub>IHYST</sub>     | Input voltage hysteresis             | SDI                              |                        | 0.2 × V <sub>CC</sub> |                        | V    |

| I <sub>OH</sub>        | High-level output current            | SDO                              |                        |                       | -2                     | mA   |

|                        |                                      | SDO                              |                        |                       | 2                      | mA   |

| I <sub>OL</sub>        | Low-level output current             | OUT0 to OUT2 (VCC ≤ 4.0 V)       | 2                      |                       | 35                     | mA   |

|                        |                                      | OUT0 to OUT2 (VCC > 4.0 V)       | 2                      |                       | 50                     | mA   |

| I <sub>REG</sub>       | Shunt regulator sink current         | VCC                              |                        |                       | 20                     | mA   |

| T <sub>A</sub>         | Operating free-air temperature range |                                  | -40                    |                       | 85                     | °C   |

| T <sub>J</sub>         | Operating junction temperature range |                                  | -40                    |                       | 125                    | °C   |

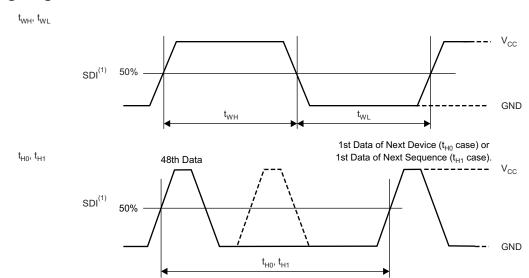

| AC CHARA               | CTERISTICS                           |                                  | •                      |                       |                        |      |

| f <sub>CLK (SDI)</sub> | Data transfer rate                   | SDI                              | 100                    |                       | 3000                   | kHz  |

| t <sub>SDI</sub>       | SDI input pulse duration             | SDI                              | 60                     |                       | 0.5 / f <sub>CLK</sub> | ns   |

| t <sub>WH</sub>        | Pulse duration, high                 | SDI                              | 14                     |                       |                        | ns   |

| t <sub>WL</sub>        | Pulse duration, low                  | SDI                              | 14                     |                       |                        | ns   |

| t <sub>H0</sub>        | Hold time: end of sequence (EOS)     | SDI↑ to SDI↑                     | 3.5 / f <sub>CLK</sub> |                       | 5.5 / f <sub>CLK</sub> | ns   |

| t <sub>H1</sub>        | Hold time: data latch (GSLAT)        | SDI↑ to SDI↑                     | 8 / f <sub>CLK</sub>   |                       |                        | ns   |

## 6.4 Thermal Information

|                        |                                              | TLC5973 |       |

|------------------------|----------------------------------------------|---------|-------|

|                        | THERMAL METRIC <sup>(1)</sup>                | D (SO)  | UNIT  |

|                        |                                              | 8 PINS  |       |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 134.6   |       |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 88.6    |       |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 75.3    | 20044 |

| Ψлт                    | Junction-to-top characterization parameter   | 37.7    | °C/W  |

| $\Psi_{JB}$            | Junction-to-board characterization parameter | 74.8    |       |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | N/A     |       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 6.5 Electrical Characteristics

At  $T_A = -40^{\circ}\text{C}$  to 85°C,  $V_{CC} = 3$  V to 6.0 V, and  $C_{VCC} = 0.1~\mu\text{F}$ . Typical values at  $T_A = 25^{\circ}\text{C}$  and  $V_{CC} = 5.0$  V, unless otherwise

|                    | PARAMETER                                                  | TEST CON                                                                                                                                                                      | IDITIONS                                                                                                                                                    | MIN                   | TYP   | MAX             | UNIT |

|--------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-----------------|------|

| V <sub>OH</sub>    | High-level output voltage (SDO)                            | I <sub>OH</sub> = −2 mA                                                                                                                                                       |                                                                                                                                                             | V <sub>CC</sub> - 0.4 |       | V <sub>CC</sub> | V    |

| V <sub>OL</sub>    | Low-level output voltage (SDO)                             | I <sub>OL</sub> = 2 mA                                                                                                                                                        |                                                                                                                                                             | 0                     |       | 0.4             | V    |

| V <sub>IREF</sub>  | Reference voltage output                                   | $R_{IREF} = 1.5 \text{ k}\Omega$                                                                                                                                              |                                                                                                                                                             | 1.18                  | 1.20  | 1.23            | V    |

| $V_R$              | Shunt regulator output voltage (V <sub>CC</sub> )          | I <sub>CC</sub> = 1 mA, SDI = low                                                                                                                                             |                                                                                                                                                             |                       | 5.9   |                 | V    |

| I <sub>CC0</sub>   |                                                            | $V_{CC} = 3.0 \text{ V to } 5.5 \text{ V , SDI} = \text{low} \\ \text{FFFh, } V_{OUTn} = 1 \text{ V, SDO} = 15 \text{ p} \\ (I_{OUTn} = 2\text{-mA target})$                  |                                                                                                                                                             |                       | 3     | 6               | mA   |

| I <sub>CC1</sub>   | County county (V.)                                         | $V_{CC} = 3.0 \text{ V to } 5.5 \text{ V, SDI} = \text{low} \\ V_{OUTn} = 1 \text{ V, SDO} = 15 \text{ pF, R}_{IRI} \\ (I_{OUTn} = 17\text{-mA target})$                      |                                                                                                                                                             |                       | 4     | 7               | mA   |

| I <sub>CC2</sub>   | Supply current (V <sub>CC</sub> )                          | $V_{CC} = 3.0 \text{ V to } 5.5 \text{ V, SDI} = 5 \text{ M}$ FFFh, $V_{OUTn} = 1 \text{ V, SDO} = 15 \text{ p}$ $R_{IREF} = 3 \text{ k}\Omega (I_{OUTn} = 17\text{-mA tar})$ | oF,                                                                                                                                                         |                       | 5     | 8               | mA   |

| I <sub>CC3</sub>   |                                                            | FFFh, V <sub>OUTn</sub> = 1 V, SDO = 15 p                                                                                                                                     | $V_{CC}$ = 3.0 V to 5.5 V, SDI = 5 MHz, all grayscale (GSn) = FFFh, $V_{OUTn}$ = 1 V, SDO = 15 pF, $R_{IREF}$ = 1.5 k $\Omega$ ( $I_{OUTn}$ = 34-mA target) |                       | 5.5   | 10              | mA   |

| I <sub>OLC</sub>   | Constant output current (OUT0 to OUT2)                     | All OUT $n$ = on, $V_{OUTn}$ = 1 V, $V_{O}$ $R_{IREF}$ = 1.5 k $\Omega$                                                                                                       | $p_{\text{UTfix}} = 1 \text{ V},$                                                                                                                           | 31                    | 34    | 37              | mA   |

| laura              | Output leakage current                                     | GS <i>n</i> = 000h, V <sub>OUTp</sub> = 21 V                                                                                                                                  | $T_J = -40$ °C to 85°C                                                                                                                                      |                       |       | 0.1             | μΑ   |

| I <sub>OLKG</sub>  | (OUT0 to OUT2)                                             | 0011 = 00011, V <sub>001n</sub> = 21 V                                                                                                                                        | $T_J = 85^{\circ}C$ to $125^{\circ}C$                                                                                                                       |                       |       | 0.2             | μΑ   |

| ΔI <sub>OLC0</sub> | Constant-current error (channel-to-channel) <sup>(1)</sup> | All OUT $n = \text{on}$ , $V_{\text{OUT}n} = V_{\text{OUTfix}}$                                                                                                               | = 1 V, $R_{IREF}$ = 1.5 k $\Omega$                                                                                                                          |                       | ±0.5% | ±3%             |      |

| ΔI <sub>OLC1</sub> | Constant-current error (device-to-device) (2)              | All OUT $n$ = on, $V_{OUTn} = V_{OUTfix} = 1 \text{ V}$ , $R_{IREF} = 1.5 \text{ k}\Omega$                                                                                    |                                                                                                                                                             |                       | ±0.5% | ±6%             |      |

| ΔI <sub>OLC2</sub> | Line regulation of constant-current output (3)             | All OUT $n$ = on, $V_{OUT_n} = V_{OUTfix} = 1 \text{ V}$ , $R_{IREF} = 1.5 \text{ k}\Omega$                                                                                   |                                                                                                                                                             |                       | ±0.5  | ±1              | %/V  |

| ΔI <sub>OLC3</sub> | Load regulation of constant-current output (4)             | All OUT $n$ = on, $V_{OUTn} = V_{OUTfix} = 1 \text{ V}$ , $R_{IREF} = 1.5 \text{ k}\Omega$                                                                                    |                                                                                                                                                             |                       | ±0.5  | ±1              | %/V  |

| R <sub>PD</sub>    | Internal pull-down resistance (SDI)                        | At SDI                                                                                                                                                                        |                                                                                                                                                             |                       | 1     |                 | ΜΩ   |

(1) The deviation of each output (OUT0 to OUT2) from the constant-current average. Deviation is calculated by the formula:

$$\Delta \text{ (\%)} = \left[ \frac{\frac{I_{\text{OUT}n}}{I_{\text{OUT}1} + I_{\text{OUT}2}} - 1}{3} \right] \times 100$$

Deviation of the constant-current average in each color group from the ideal constant-current value. Deviation is calculated by the

$$\Delta \text{ (\%)} = \left[ \frac{I_{\text{OUT0}} + I_{\text{OUT1}} + I_{\text{OUT2}}}{3} - \text{Ideal Output Current}}{||\mathbf{I}||} \right] \times 100$$

Ideal current is calculated by the formula:

$$I_{OUTn(IDEAL)}$$

(mA) = 43.4 ×  $\left[\frac{1.20}{R_{IREF}(\Omega)}\right]$

where n = 0 to 2.

(3) Line regulation is calculated by the formula:

$$\Delta (\%/V) = \left(\frac{(I_{OUT_n} \text{ at V}_{CC} = 5.5 \text{ V}) - (I_{OUT_n} \text{ at V}_{CC} = 3.0 \text{ V})}{I_{OUT_n} \text{ at V}_{CC} = 3.0 \text{ V}}\right) \times \frac{100}{5.5 \text{ V} - 3.0 \text{ V}}$$

where n = 0 to 2.

Load regulation is calculated by the equation:

$$\Delta (\%/V) = \left\{ \frac{(I_{OUT_n} \text{ at } V_{OUT_n} = 3.0 \text{ V}) - (I_{OUT_n} \text{ at } V_{OUT_n} = 1.0 \text{ V})}{I_{OUT_n} \text{ at } V_{OUT_n} = 1.0 \text{ V}} \right\} \times \frac{100}{3.0 \text{ V} - 1.0 \text{ V}}$$

, where n = 0 to 2.

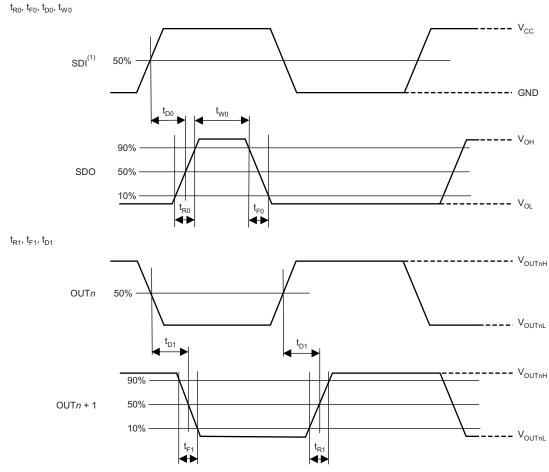

## 6.6 Switching Characteristics

At  $T_A = -40$ °C to 85°C,  $V_{CC} = 3.0$  V to 5.5 V,  $C_L = 15$  pF,  $R_L = 110$   $\Omega$ , and  $V_{LED} = 5.0$  V, unless otherwise noted. Typical values are at  $T_A = 25$ °C and  $V_{CC} = 5.0$  V.

|                 | PARAMETER                            | TEST CONDITIONS                                                 | MIN | TYP | MAX | UNIT |

|-----------------|--------------------------------------|-----------------------------------------------------------------|-----|-----|-----|------|

| t <sub>R0</sub> | Rise time                            | SDO                                                             | 2   | 6   | 12  | ns   |

| t <sub>R1</sub> | Rise time                            | $OUTn$ (on $\rightarrow$ off)                                   |     | 200 | 400 | ns   |

| t <sub>F0</sub> | Fall time                            | SDO                                                             | 2   | 6   | 12  | ns   |

| t <sub>F1</sub> | - Fall time                          | $OUTn$ (off $\to$ on)                                           |     | 200 | 400 | ns   |

| t <sub>D0</sub> |                                      | SDI↑ to SDO↑                                                    |     | 30  | 50  | ns   |

| t <sub>D1</sub> | Propagation delay                    | OUT0↓ to OUT1↓, OUT1↓to OUT2↓,<br>OUT0↑ to OUT1↑, OUT1↑to OUT2↑ |     | 25  |     | ns   |

| $t_{WO}$        | Shift data output one pulse duration | SDO↑ to SDO↓                                                    | 15  | 25  | 45  | ns   |

| fosc            | Internal GS oscillator frequency     |                                                                 | 8   | 12  | 16  | MHz  |

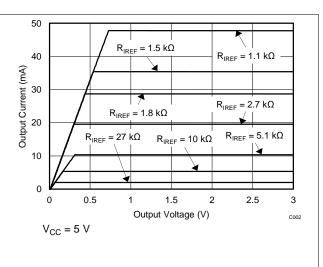

## 6.7 Typical Characteristics

At  $T_A = 25$ °C and  $V_{CC} = 12$  V, unless otherwise noted.

Figure 2. Output Current vs Output Voltage (OUTn)

## 7 Parameter Measurement Information

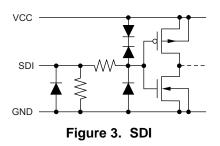

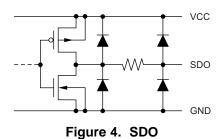

## 7.1 Pin-Equivalent Input and Output Schematic Diagrams

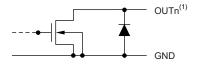

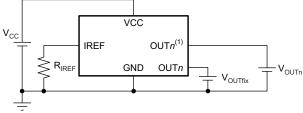

(1) n = 0 to 2.

Figure 5. OUT0 Through OUT2

## 7.2 Test Circuits

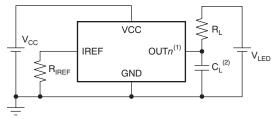

- (1) n = 0 to 2.

- (2) C<sub>L</sub> includes measurement probe and jig capacitance.

V<sub>CC</sub> VCC IREF SDO C<sub>L</sub><sup>(1)</sup>

Figure 7. Rise and Fall Time Test Circuit for SDO

(1)  $C_L$  includes measurement probe and jig capacitance.

Figure 6. Rise and Fall Time Test Circuit for OUTn

(1) n = 0 to 2.

Figure 8. Constant-Current Test Circuit for OUTn

## 7.3 Timing Diagrams

(1) Input pulse rise and fall time is 1 ns to 3 ns.

Figure 9. Input Timing

(1) Input pulse rise and fall time is 1 ns to 3 ns.

Figure 10. Output Timing

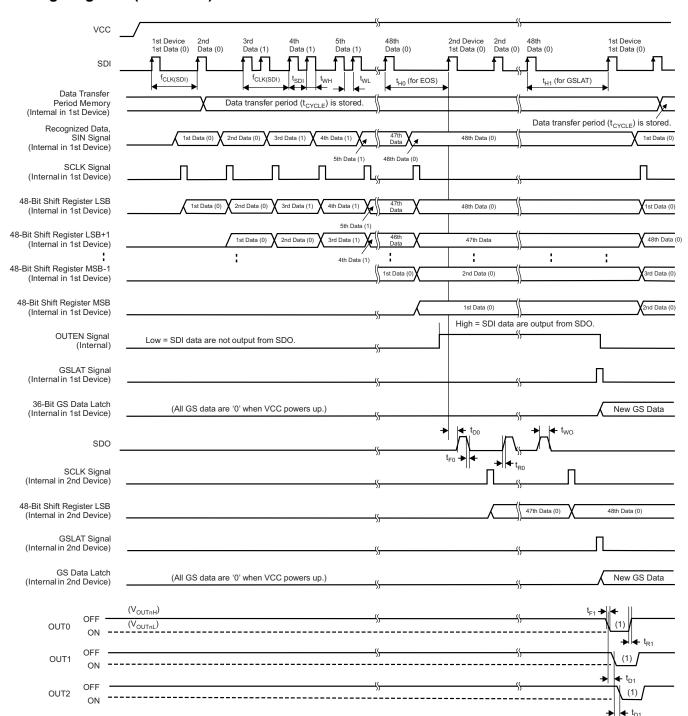

## **Timing Diagrams (continued)**

(1) OUTn on-time changes, depending on the data in the 36-bit GS data latch.

Figure 11. Data Write and OUTn Switching Timing

#### 8 Detailed Description

#### 8.1 Overview

The TLC5973 is 3-channel, 50-mA, constant-current LED driver that can control LED on-time with pulse width modulation (PWM) in 4096 steps for grayscale (GS) control. A maximum of 68 billion colors can be generated with red, green, and blue LEDs connected to each constant-current output. Furthermore, a reference clock generator is implemented in the device, which means that the reference clock for PWM timing control is not required to be supplied from an external clock generator or controller.

The device adopts a single-wire input or output system. Therefore, communication wire cost and communication wire failure are reduced. Further wire cost reduction can be attained when supplying power to the device. One wire can be eliminated because the device power can be generated from the LED power line with the internal shunt regulator.

The device can reduce the amount of incorrect data writes because the one-write command is required to write GS data to the device. The maximum data transfer rate for the device is 3 Mbps. Therefore, GS data can be updated with a high refresh rate even if many devices are connected in series. The number of TLC5973 devices connected in series is not limited because the TLC5973 has an internal buffer that drives the output signal.

#### 8.2 Functional Block Diagram

## 8.3 Feature Description

## 8.3.1 Grayscale (GS) Control

This control feature is a 12-bit (4096-step) grayscale (GS) control that provides a wide range of color generation. 68 billion colors can be generated with the red, green, and blue LEDs. Connect the LEDs to the device OUT*n* pins, as described in the *Applications and Implementation* section.

#### 8.3.2 EasySet and Shunt Regulator

This device includes a single-wire serial interface (EasySet) and a shunt regulator. The total number of wires for power supply and data write operations can be reduced with the EasySet and shunt regulator included in the design.

#### **Feature Description (continued)**

## 8.3.3 No Limit Cascading

This feature results in no limitation on the number of total cascaded devices used in series in an application. This advantage is attained because a timing-adjusted pulse generator is implemented in the device.

#### 8.3.4 Constant Sink Current Value

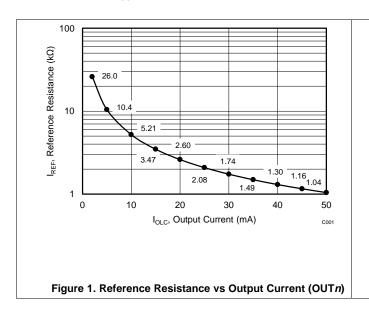

The output current value of each channel ( $I_{OLC}$ ) is programmed by a single resistor ( $R_{IREF}$ ) that is placed between the IREF and GND pins. The current value can be calculated by Equation 1:

$$R_{IREF} (k\Omega) = \frac{V_{IREF} (V)}{I_{OLC} (mA)} \times 43.4$$

where:

• V<sub>IREF</sub> = the internal reference voltage on IREF (typically 1.20 V), and

•

$$I_{OLC} = 2 \text{ mA to } 50 \text{ mA}$$

(1)

$I_{OLC}$  is the current for each output. Each output sinks  $I_{OLC}$  current when it is turned on.  $R_{IREF}$  must be between 1 k $\Omega$  and 27 k $\Omega$  in order to hold  $I_{OLC}$  between 50 mA (typ) and 1.93 mA (typ). Otherwise, the output may be unstable. Refer to Figure 1 and Table 1 for the constant-current sink values for specific external resistor values.

Table 1. Constant-Current Output versus External Resistor Value

| I <sub>OLC</sub> (mA) | R <sub>IREF</sub> (kΩ, typ) |

|-----------------------|-----------------------------|

| 50                    | 1.04                        |

| 45                    | 1.16                        |

| 40                    | 1.30                        |

| 35                    | 1.49                        |

| 30                    | 1.74                        |

| 25                    | 2.08                        |

| 20                    | 2.60                        |

| 15                    | 3.47                        |

| 10                    | 5.21                        |

| 5                     | 10.4                        |

| 2                     | 26.0                        |

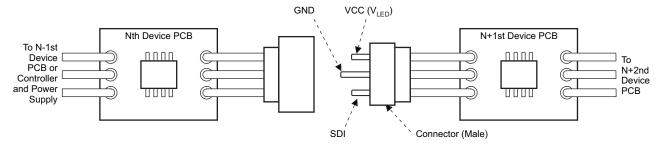

#### 8.3.5 Connector Design

When the connector pin of the device application printed circuit board (PCB) is connected or disconnected to other PCBs, the power must be turned off to avoid device malfunction or failure. Furthermore, designing the connector GND pin to be longer than other pins (as shown in Figure 12) is preferable. This arrangement allows the GND line to either be connected first or disconnected last, which is imperative for proper device function.

Figure 12. Connector Pin Design Application

#### 8.4 Device Functional Modes

#### 8.4.1 Grayscale (GS) Function (PWM Control)

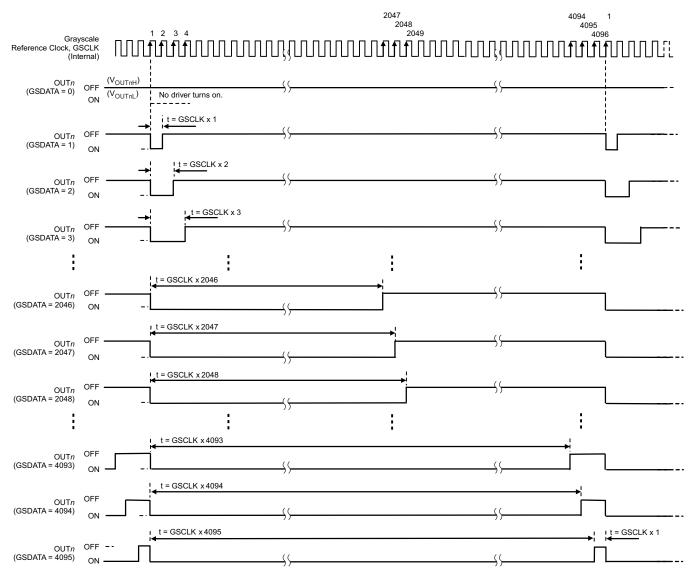

The TLC5973 can adjust the brightness of each output channel using a pulse width modulation (PWM) control scheme. The PWM data bit length for each output is 12 bits. The architecture of 12 bits per channel results in 4096 brightness steps, from 0% to 99.98% on-time duty cycle.

The PWM operation for OUT*n* is controlled by an 12-bit grayscale (GS) counter. The GS counter increments on each internal GS clock (GSCLK) rising edge. All OUT*n* are turned on when the GS counter is '1', except when OUT*n* are programed to GS data '0' in the 36-bit GS data latch. After turning on, each output is turns off when the GS counter value exceeds the programmed GS data for the output. The GS counter resets to 000h and all outputs are forced off when the GS data are written to the 36-bit GS data latch. Afterwards, the GS counter begins incrementing and PWM control is started from the next internal GS clock.

## **Device Functional Modes (continued)**

Table 2 summarizes the GS data values versus the output ideal on-time duty cycle. Furthermore, actual on-time differs from the ideal on-time because the output drivers and control circuit have some timing delay. When the device is powered on, all outputs are forced off and remain off until the non-zero GS data are written to the 36-bit GS data latch.

Table 2. Output Duty Cycle and Total On-Time versus GS Data

| GS DATA |     | NO. OF GSCLKs | NO. OF GSCLKs | TOTAL IDEAL TIME |                  |  |

|---------|-----|---------------|---------------|------------------|------------------|--|

| DECIMAL | HEX | OUT TURNS ON  | OUT TURNS OFF | (µs)             | ON-TIME DUTY (%) |  |

| 0       | 0   | Off           | Off           | 0                | 0                |  |

| 1       | 1   | 1             | 2             | 0.08             | 0.02             |  |

| 2       | 2   | 1             | 3             | 0.17             | 0.05             |  |

| _       | _   | _             | _             | _                | _                |  |

| 255     | 0FE | 1             | 256           | 21.25            | 6.23             |  |

| 256     | 0FF | 1             | 257           | 21.33            | 6.25             |  |

| 257     | 100 | 1             | 258           | 21.42            | 6.27             |  |

| _       | _   | _             | _             | _                | _                |  |

| 511     | 1FF | 1             | 512           | 42.58            | 12.48            |  |

| 512     | 200 | 1             | 513           | 42.67            | 12.50            |  |

| 513     | 201 | 1             | 514           | 42.75            | 12.52            |  |

| _       | _   | _             | _             | _                | _                |  |

| 1023    | 3FF | 1             | 1024          | 85.25            | 24.98            |  |

| 1024    | 400 | 1             | 1025          | 85.33            | 25.00            |  |

| 1025    | 401 | 1             | 1026          | 85.42            | 25.00            |  |

| _       | _   | _             | _             | _                | _                |  |

| 2047    | 7FF | 1             | 2048          | 170.6            | 49.98            |  |

| 2048    | 800 | 1             | 2049          | 170.7            | 50.00            |  |

| 2049    | 801 | 1             | 2050          | 170.8            | 50.02            |  |

| _       | _   | _             | _             | _                | _                |  |

| 4093    | FFD | 1             | 4094          | 341.1            | 99.93            |  |

| 4094    | FFE | 1             | 4095          | 341.2            | 99.95            |  |

| 4095    | FFF | 1             | 4096          | 341.3            | 99.98            |  |

#### 8.4.1.1 PWM Control

The GS counter keeps track of the number of grayscale reference clocks (GSCLKs) from the internal oscillator. Each output stays on while the counter is less than or equal to the programmed GS value. Each output turns off when the GS counter is greater than the GS value in the 36-bit GS data latch. Figure 13 illustrates the PWM operation timing.

(1) Actual on-time differs from the ideal on-time.

Figure 13. PWM Operation

#### 8.4.2 One-Wire Interface (EasySet) Data Writing Method

There are four sequences to write GS data into the TLC5973 via a single-wire interface. This section discusses each sequence in detail.

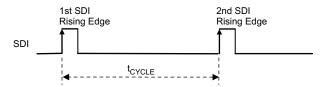

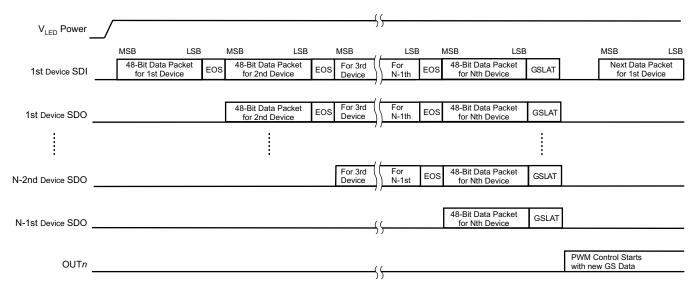

#### 8.4.2.1 Data Transfer Rate ( $t_{CYCLF}$ ) Measurement Sequence

The TLC5973 measures the time between the first and second SDI rising edges either after the device is powered up or when the GS data latch sequence is executed (as described in the GS Data Latch Sequence (GSLAT) section) and the time is internally stored as  $t_{CYCLE}$ .  $t_{CYCLE}$  serves as a base time used to recognize one complete data write operation, a 48-bit data write operation, and a GS data write operation to the GS data latch.  $t_{CYCLE}$  can be set between 0.33  $\mu$ s and 10  $\mu$ s ( $t_{CLK(SDI)}$ ) = 100 kHz to 3000 kHz). In this sequence, two instances of data '0' are written to the LSB side of the 48-bit shift register. Figure 14 shows the  $t_{CYCLE}$  measurement timing.

Figure 14. Data Transfer Rate (t<sub>CYCLE</sub>) Measurement

#### 8.4.2.2 Data '0' and Data '1' Write Sequence (Data Write Sequence)

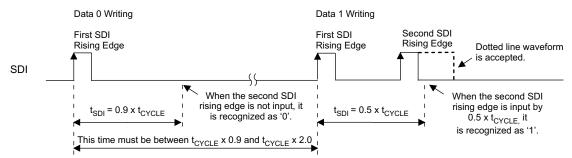

When the second SDI rising edge is not input before  $0.9 \times t_{CYCLE}$  elapses from the first SDI rising edge input, the data are recognized as '0'. When the second SDI rising edge is input before 50% of  $t_{CYCLE}$  elapses from the first SDI rising edge input, the data are recognized as '1'. This write sequence must be repeated 46 times after the  $t_{CYCLE}$  measurement sequence in order to send the write command to the higher 10-bit (3AAh) and 36-bit GS data. Figure 15 shows the data '0' and '1' write timing.

Figure 15. Data '0' and '1' Write Operation

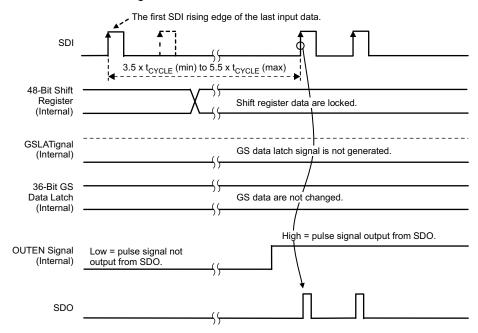

## 8.4.2.3 One Communication Cycle End of Sequence (EOS)

One communication cycle end of sequence (EOS) must be input after the 48-bit data are written because the TLC5973 does not count the number of input data. When SDI is held low for the EOS hold time (t<sub>H0</sub>), the 48-bit shift register values are locked and a buffered SDI signal is output from SDO to transfer GS data to the next device. Figure 16 shows the EOS timing.

Figure 16. End of Sequence (EOS)

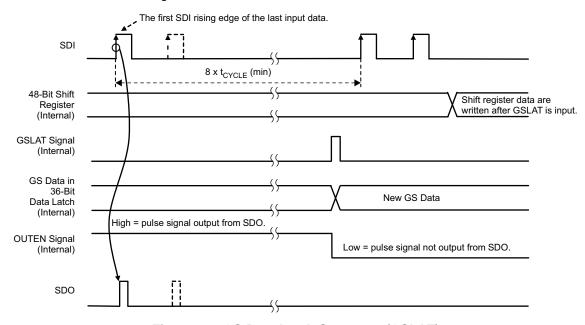

#### 8.4.2.4 GS Data Latch (GSLAT) Sequence

A GS data latch (GSLAT) sequence must be input after the 48-bit data for all cascaded devices are written. When SDI is held low for the data latch hold time ( $t_{H1}$ ), the 48-bit shift register data in all devices are copied to the GS data latch in each device. Furthermore, PWM control starts with the new GS data at the same time. Figure 17 shows the GSLAT timing.

Figure 17. GS Data Latch Sequence (GSLAT)

## 8.5 Programming

### 8.5.1 Controlling Devices Connected in Series

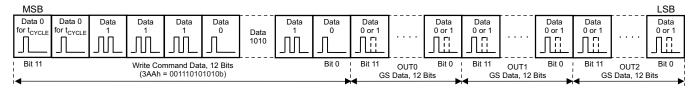

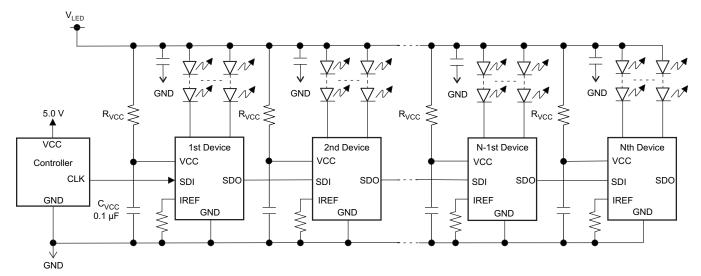

The 12-bit write command and 36-bit grayscale (GS) data for OUT0 to OUT2 (for a total of 48 bits of data) must be written to the device. Figure 18 shows the 48-bit data packet configuration. When multiple devices are cascaded (as shown in Figure 19), *N* times the packet must be written into each TLC5973 in order to control all devices. There is no limit on how many devices can be cascaded, as long as proper VCC voltage is supplied. The packet for all devices must be written again whenever any GS data changes.

Figure 18. 48-Bit Data Packet Configuration for One TLC5973

Figure 19. Cascade Connection of NTLC5973 Units (Internal Shunt Regulator Mode)

#### **Programming (continued)**

The function setting write procedure and display control is:

- 1. Power-up VCC (V<sub>LED</sub>); all OUT*n* are off because GS data are not written yet.

- 2. Write the 48-bit data packet (MSB-first) for the first device using t<sub>CYCLE</sub> and the data write sequences illustrated in Figure 14 and Figure 15. The first 12 bits of the 48-bit data packet are used as the write command. The write command must be 3AAh (001110101010b); otherwise, the 36-bit GS data in the 48-bit shift register are not copied to the 36-bit GS data latch.

- 3. Execute one communication cycle EOS (refer to Figure 16) for the first device.

- 4. Write the 48-bit data packet for the second TLC5973 as described step 2. However, t<sub>CYCLE</sub> should be set to the same timing as the first device.

- 5. Execute one communication cycle EOS for the second device.

- 6. Repeat steps 4 and 5 until all devices have GS data.

- 7. The number of total bits is 48 × N. After all data are written, execute a GSLAT sequence as described in Figure 17 in order to copy the 36-bit LSBs in the 48-bit shift resister to the 36-bit GS data latch in each device; PWM control starts with the written GS data at the same time.

Figure 20. Data Packet Input Order for NTLC5973 Units

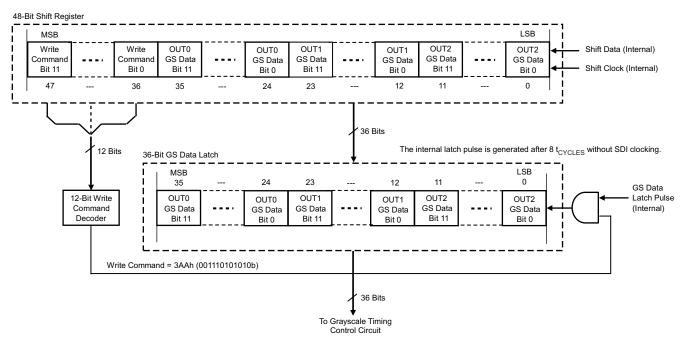

#### 8.6 Register Maps

## 8.6.1 Register and Data Latch Configuration

The TLC5973 has a 48-bit shift register and a 36-bit data latch that stores GS data. When the internal GS data latch pulse is generated and the data of the 12 MSBs in the shift register are 3AAh, the lower 36-bit data in the 48-bit shift register are copied into the 36-bit GS data latch. If the data of the 12 MSBs is not 3AAh, the 36-bit data are not copied into the 36-bit GS data latch. Figure 21 shows the shift register and GS data latch configurations. Table 3 shows the 48-bit shift register bit assignment.

Figure 21. Common Shift Register and Control Data Latches Configuration

Table 3. 48-Bit Shift Register Data Bit Assignment

| BITS     | BIT NAME | CONTROLLED CHANNEL/FUNCTIONS                                                                                                                                                                                         |

|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 to 11  | GSOUT2   | GS data bits 0 to 11 for OUT2                                                                                                                                                                                        |

| 12 to 23 | GSOUT1   | GS data bits 0 to 11 for OUT1                                                                                                                                                                                        |

| 24 to 35 | GSOUT0   | GS data bits 0 to 11 for OUT0                                                                                                                                                                                        |

| 36 to 47 | WRTCMD   | Data write command (3AAh) for GS data. The lower 36-bit GS data in the 48-bit shift register are copied to the GS data latch when the internal GS latch is generated (when these data bits are 3AAh, 001110101010b). |

## 9 Applications and Implementation

## 9.1 Application Information

The device is a constant sink current LED driver. This device is typically used to minimize wiring cost in applications and also provides no restrictions of cascading multiple devices in series. Furthermore, the device maximum data transfer rate is 3 Mbps and can contribute high-frequency display data change rates. The following design procedures can be used to maximize application design with minimal wiring cost. The device is also a good choice for higher VCC power-supply voltage applications because of the internal shunt regulator included in the device.

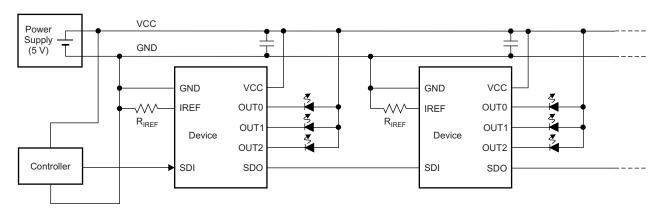

## 9.2 Typical Applications

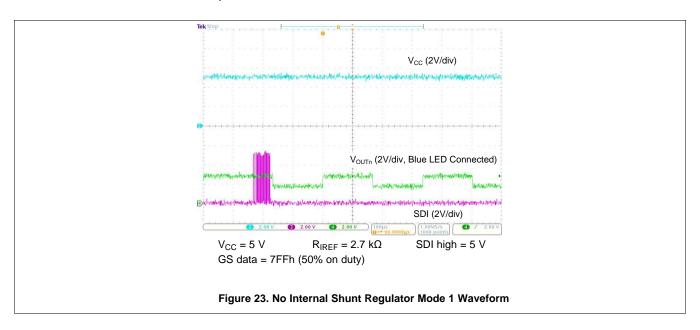

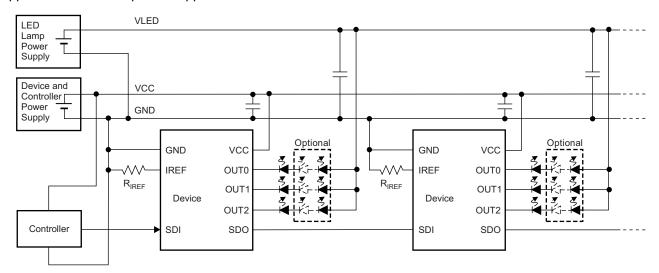

## 9.2.1 No Internal Shunt Regulator Mode 1

This application does not use the shunt regulator. However, the device VCC and LED lamp anode voltage can be supplied from the same power supply because only one LED lamp is connected in series.

Figure 22. No Internal Shunt Regulator Mode 1 Typical Application Circuit

#### 9.2.1.1 Design Requirements

**Table 4. Design Parameters**

| DESIGN PARAMETER            | EXAMPLE VALUE                                       |

|-----------------------------|-----------------------------------------------------|

| Input voltage range for VCC | 3.0 V or LED forward voltage $(V_F)$ + 1 V to 5.5 V |

| SDI voltage range           | Low level = GND, high level = VCC                   |

| SDI data transfer rate      | 100 kbps to 3 Mbps                                  |

#### 9.2.1.2 Detailed Design Procedure

The OUTn (n = 0 to 2) constant output current is set by an external resistor connected between the device IREF and GND pins. Use Equation 1 to calculate the requirements for  $R_{IREF}$ .

## 9.2.1.3 Application Curve

One LED is connected to each output.

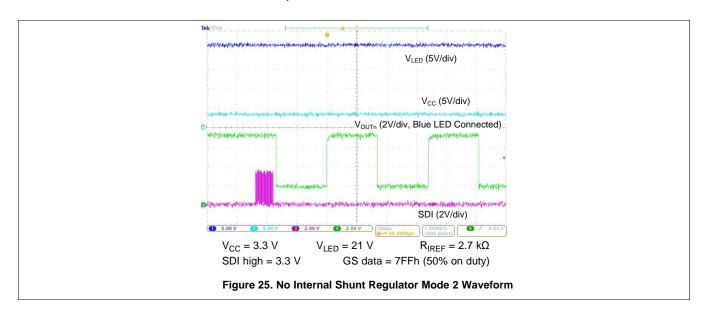

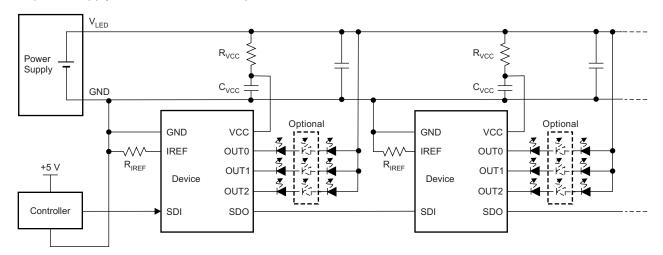

#### 9.2.2 No Internal Shunt Regulator Mode 2

This application does not use the shunt regulator. However, the device VCC and LED lamp anode voltage are supplied from different power supplies.

Figure 24. No Internal Shunt Regulator Mode 2 Typical Application Circuit

#### 9.2.2.1 Design Requirements

**Table 5. Design Parameters**

| DESIGN PARAMETER                 | EXAMPLE VALUE                                                                                  |

|----------------------------------|------------------------------------------------------------------------------------------------|

| Input voltage range for VCC      | 3.0 V to 5.5 V                                                                                 |

| Input voltage range for LED lamp | LED forward voltage (V <sub>F</sub> ) × the number of LED lamps + 1 V; maximum voltage is 24 V |

| SDI voltage range                | Low level = GND, high level = VCC                                                              |

| SDI data frequency               | 100 kbps to 3 Mbps                                                                             |

## 9.2.2.2 Detailed Design Procedure

The OUTn (n = 0 to 2) constant output current is set by an external resistor connected between the device IREF and GND pins. Use Equation 1 to calculate the requirements for R<sub>IREF</sub>.

## 9.2.2.3 Application Curve

Six LEDs are connected in series to each output.

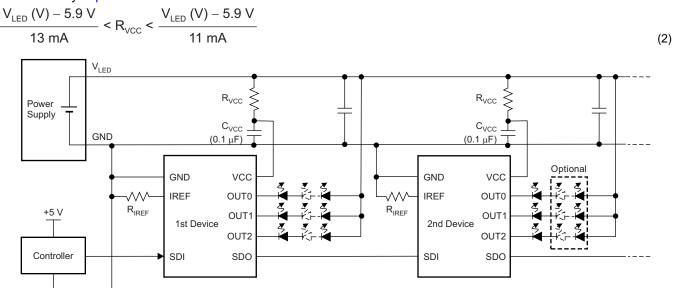

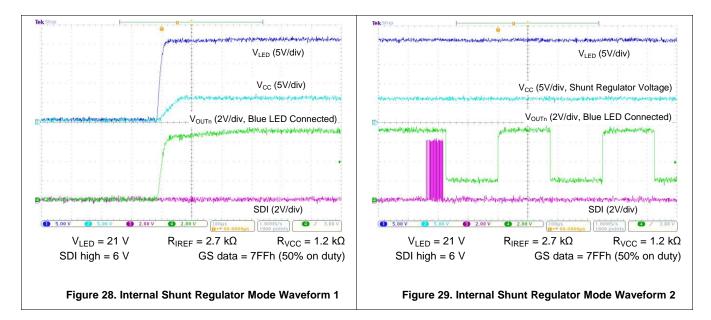

#### 9.2.3 Internal Shunt Regulator Mode

This application uses the shunt regulator. The device VCC and LED lamp anode voltage are supplied from the same power supply. At least two LED lamps are connected in series.

Figure 26. Internal Shunt Regulator Mode Typical Application Circuit

#### 9.2.3.1 Design Requirements

**Table 6. Design Parameters**

| DESIGN PARAMETER                         | EXAMPLE VALUE                                |

|------------------------------------------|----------------------------------------------|

| Input voltage range for V <sub>LED</sub> | 6 V to 24 V                                  |

| SDI voltage range                        | Low level = GND, high level = 5.0 V to 6.0 V |

| SDI data transfer rate                   | 100 kbps to 3 Mbps                           |

#### 9.2.3.2 Detailed Design Procedure

The TLC5973 internally integrates a shunt regulator to regulate  $V_{CC}$  voltage. Refer to Figure 27 for an application circuit that uses the internal shunt regulator through a resistor,  $R_{VCC}$ . The recommended  $R_{VCC}$  value can be calculated by Equation 2.

Figure 27. Internal Shunt Regulator Mode Application Circuit

Table 7 shows the typical resistor value for several  $V_{LED}$  voltages. Note that the  $C_{VCC}$  value should be 0.1  $\mu$ F.

Table 7. Resistor Example for Shunt Resistor versus LED Voltage<sup>(1)</sup>

| V <sub>LED</sub> (V) | R <sub>VCC</sub> (Ω) | RESISTOR WATTAGE (W) |

|----------------------|----------------------|----------------------|

| 9                    | 270                  | 0.04                 |

| 12                   | 510                  | 0.07                 |

| 18                   | 1000                 | 0.15                 |

| 24                   | 1500                 | 0.22                 |

<sup>(1)</sup>  $R_{IREF}$  is at 1.5 k $\Omega$ .

## 9.2.3.3 Application Curves

Six LEDs are connected in series to each output.

## 10 Power Supply Recommendations

The power supply voltage should be well regulated. An electrolytic capacitor must be used to reduce the voltage ripple to less than 5% of the input voltage.

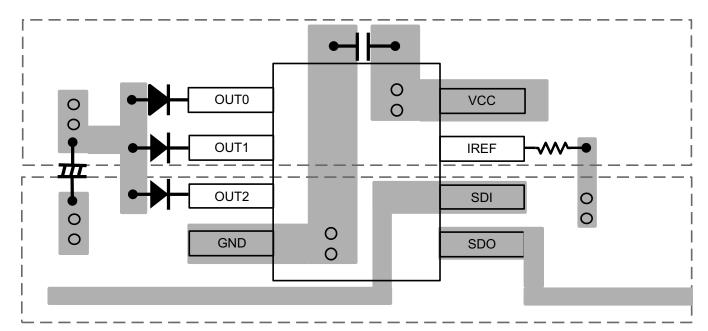

## 11 Layout

## 11.1 Layout Guidelines

- The resistor used for the output current setting should be placed near the IREF and GND pins of the device.

- The decoupling capacitor and the shunt regulator resistor should be placed near the VCC pin of the device.

## 11.2 Layout Example

Figure 30. Layout Example

## 12 器件和文档支持

## 12.1 Trademarks

EasySet is a trademark of Texas Instruments, Inc.

All other trademarks are the property of their respective owners.

## 12.2 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 12.3 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms and definitions.

## 13 机械封装和可订购信息

以下页中包括机械封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 这些数据会在无通知且不对本文档进行修订的情况下发生改变。 欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

www.ti.com 10-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                |                       |      | (4)                           | (5)                        |              |                  |

| TLC5973D              | Active | Production    | SOIC (D)   8   | 75   TUBE             | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 5973             |

| TLC5973D.B            | Active | Production    | SOIC (D)   8   | 75   TUBE             | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 5973             |

| TLC5973DR             | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 5973             |

| TLC5973DR.B           | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 5973             |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

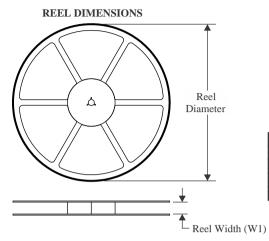

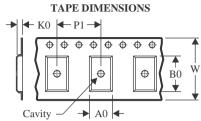

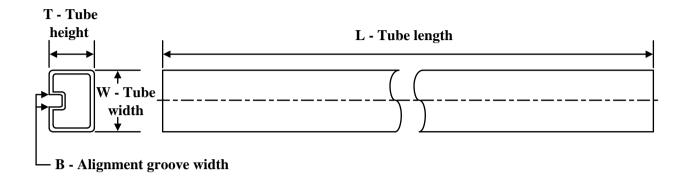

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

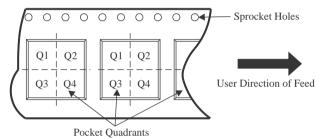

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device    | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TLC5973DR | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.5                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

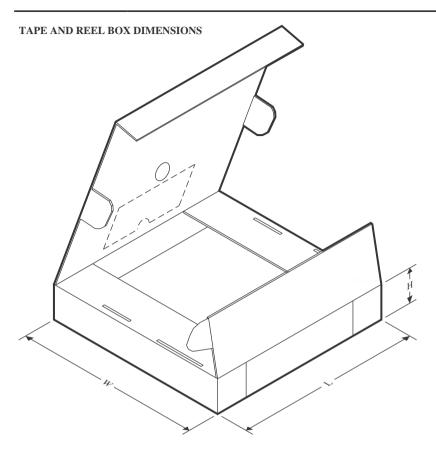

#### \*All dimensions are nominal

| Ì | Device    | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---|-----------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| ı | TLC5973DR | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |  |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

## **TUBE**

#### \*All dimensions are nominal

| Device     | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TLC5973D   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| TLC5973D.B | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

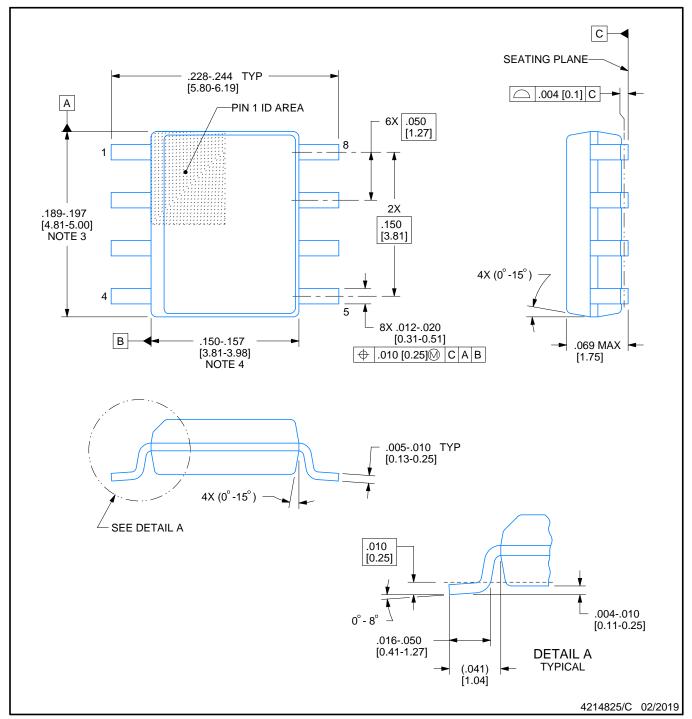

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

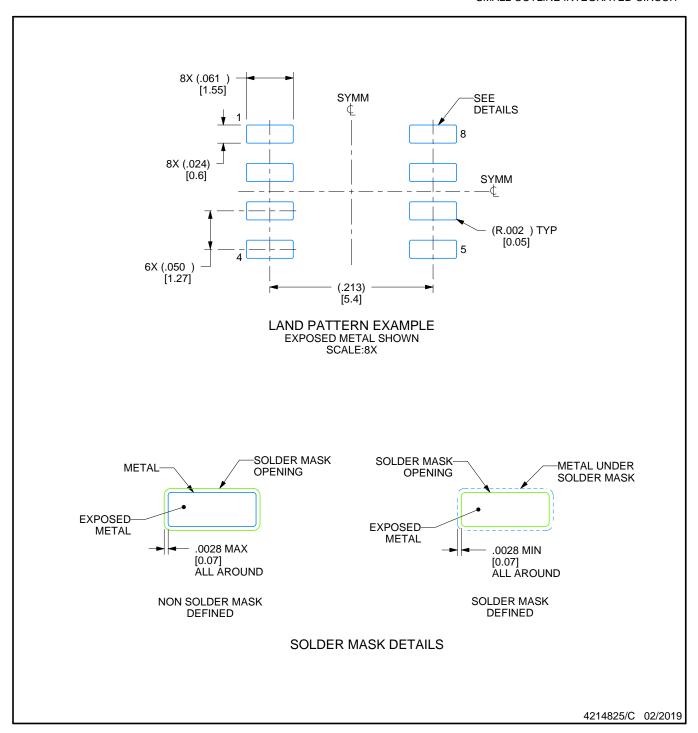

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

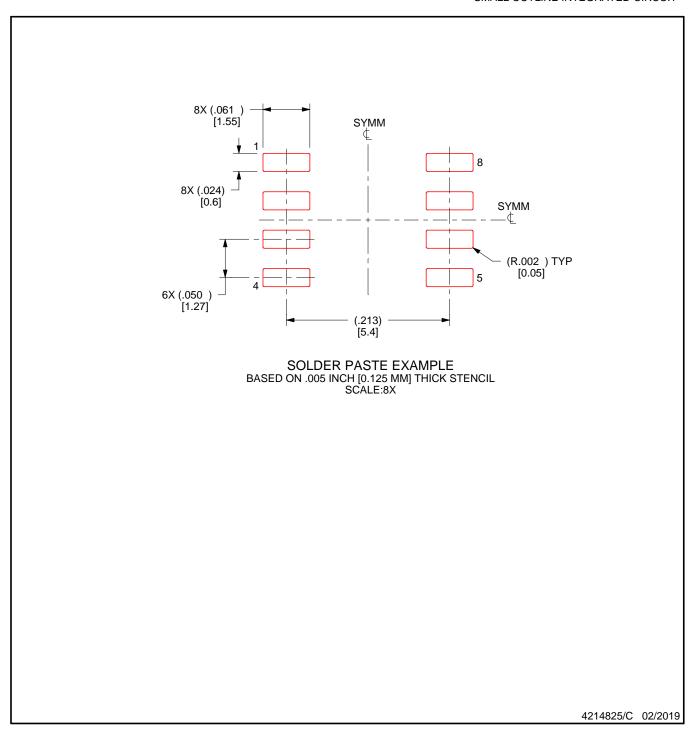

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

## 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月