# LEGACY/IEEE802.3af COMPATIBLE POWER INTERFACE SWITCH FOR POWER OVER ETHERNET (PoE) POWERED DEVICES

#### **FEATURES**

- Integrated Power Interface Switch for IEEE 802.3af Powered Devices (PDs)

- Precision UVLO Thresholds

- 20-ms UVLO Off-Time Delay

- Provides PD Detection Signature

- Provides PD Classification Signature (Class 0-4)

- Programmable Inrush Current Limit

- Internal 0.3-Ω Low-Side FET

- Interfaces to DC/DC Soft-Start for DC/DC Enable

- Internal Thermal Protection Disconnects PD Load

- 8-Pin SOIC, 8-Pin TSSOP Packages

#### **APPLICATIONS**

- VolP Phones

- Internet Appliances

- Wireless LAN Access Points

- Bluetooth™ Access Points

#### DESCRIPTION

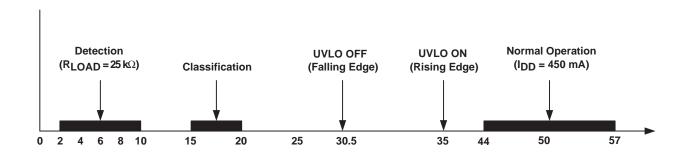

Acting as an interface between the Power Source Equipment (PSE) and the Powered Device (PD), the TPS2371 performs all detection, classification, inrush current limiting, and switch FET control that is necessary for compatibility with Legacy/IEEE 802.3af Standard. The TPS2371 incorporates precision UVLO thresholds and hysteresis as well as a UVLO off-time delay to enable Legacy IEEE802.3af PoE compatibilty. An internal  $0.3\text{-}\Omega$  FET provides maximum power delivery. As an additional feature, the TPS2371 interfaces with the enable/soft-start signal of a dc-to-dc converter, eliminating the need to have an accurate UVLO in the dc-to-dc converter.

At low input voltages (1.8 V to 10 V), the TPS2371 draws less than 12  $\mu\text{A}$ , allowing accurate sensing of the external 24.9-k $\Omega$  discovery resistor. At input voltages between 15 V and 20 V, an external resistor sets the level of current to be drawn during classification mode. TPS2371 is compatible with current as well as voltage measurement schemes for classification. Above 20-V input, the classification current is shut off, reducing internal power dissipation.

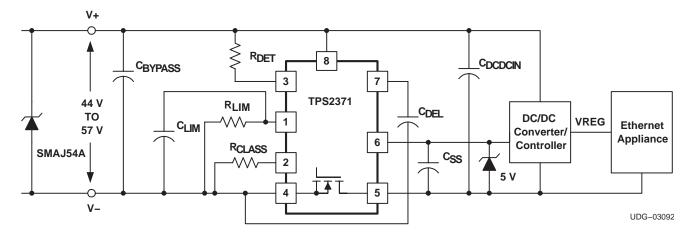

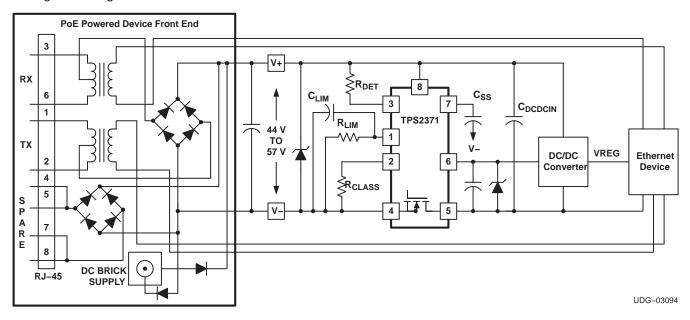

# SIMPLIFIED APPLICATION DIAGRAM

Bluetooth is a trademark of the Bluetooth SIG, Inc.

# **DESCRIPTION** (continued)

The TPS2371 drives an internal low-side FET for control of the return side of the power path. The internal FET is turned on when the input voltage reaches 36 V and above. When the input voltage decreases, the FET remains on until the input voltage drops to below 30 V.

During initial turn-on of the switch (inrush mode), an external resistor is used to program the inrush current, allowing a wide range of capacitor values to be used at the load. According to IEEE 802.3af specification, inrush current of 400 mA is allowed only for 50 ms, limiting the load capacitor to approximately 180  $\mu$ F. A programmable inrush current limit removes this limitation, allowing a larger capacitor to be used with a lower inrush current limit.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range unless otherwise noted (2)

|                                                      |                                                              |    | TPS2371    | UNIT |

|------------------------------------------------------|--------------------------------------------------------------|----|------------|------|

|                                                      | ILIM, DELAY                                                  |    | 4          |      |

| Input voltage range, wrt VEE                         | CLASS                                                        |    | 12         | V    |

|                                                      | DET, RTN, EN_DC, VDD                                         |    | 68         |      |

| Operating junction temperature range, T <sub>J</sub> |                                                              |    | -55 to 150 | °C   |

| Storage temperature, T <sub>Stg</sub>                | -65 to 150                                                   | °C |            |      |

| Lead temperature 1,6 mm (1/16 inch) from case        | Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds |    |            |      |

<sup>(2)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

|                                                | MIN | NOM | MAX | UNIT |

|------------------------------------------------|-----|-----|-----|------|

| Input voltage, V <sub>I</sub>                  |     | 48  | 57  | V    |

| Operating junction temperature, T <sub>J</sub> | 0   |     | 70  | °C   |

# **DISSIPATION RATINGS**(3)(4)

| PACKAGE                  | THERMAL IMPEDANCE JUNCTION-TO-AMBIENT | T <sub>A</sub> < 25°C<br>POWER RATING | T <sub>A</sub> = 25°C<br>DERATING<br>FACTOR | T <sub>A</sub> = 70°C<br>POWER RATING |

|--------------------------|---------------------------------------|---------------------------------------|---------------------------------------------|---------------------------------------|

| 8-Pin Plastic TSSOP (PW) | 258.5°C/W                             | 464 mW                                | 3.9 mW/°C                                   | 290 mW                                |

| 8-Pin Plastic SOIC (D)   | 176.0°C/W                             | 682 mW                                | 5.7 mW/°C                                   | 426 mW                                |

<sup>(3)</sup> Test board conditions:

- 1. 3" x 3", 4 layers, thickness: 0.062"

- 2. 1.5 oz. copper traces located on the top of the PCB

- 3. 1.5 oz. copper ground plane on the bottom of the PCB

- 4. 0.5 oz. copper ground planes on the 2 internal layers

- 5. 12 thermal vias (see "Recommended Land Pattern" in applications section of this data sheet)

- (4) Maximum power dissipation may be limited by over current protection.

# **ELECTRICAL CHARACTERISTICS**

$V_{DD} = 48 \text{ V}$ ;  $T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ ; all voltages and currents are with respect to VEE; (unless otherwise noted)

|                 | PARAMETER                           | TEST CONDITIONS                                                                                             | MIN  | TYP  | MAX  | UNIT |

|-----------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------|------|------|------|------|

| SUPPL           | Υ                                   |                                                                                                             |      |      |      |      |

|                 | Offset current                      | VDD = 1.8 V, DET = OPEN                                                                                     |      |      | 3    |      |

| I <sub>DD</sub> | Sleep current                       | 1.8 V ≤ VDD < 10 V, DET = OPEN                                                                              |      | 5    | 12   |      |

|                 |                                     | $R_{DET} = 24.9 \text{ k}\Omega, \text{ VDD} = 1.8 \text{ V}$                                               | 70   | 73   | 76   | μА   |

| DET             | Detection load current              | $R_{DET} = 24.9 \text{ k}\Omega, VDD = 9.5 \text{ V}$                                                       | 380  | 390  | 400  |      |

|                 | Olassa Wasting assessed three shall | Turn on                                                                                                     | 10.0 | 12.5 | 14.0 | V    |

|                 | Classification current threshold    | Turn off                                                                                                    | 21.5 | 22.5 | 23.5 | V    |

|                 | VDD current class 0                 | 0.44 W $\leq$ P <sub>POE</sub> $\leq$ 12.95 W,<br>15 V $\leq$ VDD $\leq$ 20 V, R <sub>CLASS</sub> = 4.42 kΩ | 2.2  | 2.5  | 2.8  |      |

|                 | VDD current class 1                 | 0.44 W $\leq$ P <sub>POE</sub> $\leq$ 3.84 W,<br>15 V $\leq$ VDD $\leq$ 20 V, R <sub>CLASS</sub> = 953 Ω    | 10.4 | 10.8 | 11.5 |      |

|                 | VDD current class 2                 | 3.84 W $\leq$ PP <sub>OE</sub> $\leq$ 6.49 W,<br>15 V $\leq$ VDD $\leq$ 20 V, R <sub>CLASS</sub> = 549 Ω    | 18.1 | 18.6 | 19.5 | mA   |

|                 | VDD current class 3                 | 6.49 W ≤ P <sub>PoE</sub> ≤ 12.95 W,<br>15 V ≤ VDD ≤ 20 V, R <sub>CLASS</sub> = 357 Ω                       | 27.7 | 28.4 | 29.9 |      |

|                 | VDD current class 4                 | Reserved for future use,<br>15 V $\leq$ VDD $\leq$ 20 V, RCLASS = 255 $\Omega$                              | 38.5 | 39.6 | 42.0 |      |

|                 | VDD quiescent current               | $30 \text{ V} \le \text{VDD} \le 57 \text{ V},  \text{R}_{\text{CLASS}} = 255 \Omega$                       |      | 500  | 800  | μΑ   |

|                 |                                     | Turn on                                                                                                     | 33.9 | 35.0 | 36.1 |      |

|                 | Input UVLO threshold                | Turn off                                                                                                    | 29.5 | 30.5 | 31.5 | V    |

|                 | UVLO hysteresis                     |                                                                                                             | 4.3  | 4.5  |      |      |

|                 | UVLO off-time delay                 | C <sub>DELAY</sub> = 180 nF                                                                                 |      | 18   |      | ms   |

|                 | EN_DC sink current                  |                                                                                                             | 40   | 80   | 200  | μΑ   |

|                 | RTN threshold for EN_DC             |                                                                                                             | 1.2  | 1.5  | 1.8  | V    |

|                 | DMOS R <sub>DS(on)</sub>            | I <sub>RTN</sub> = 200 mA                                                                                   | 0.15 | 0.30 | 0.60 | Ω    |

|                 | Full load current limit             | V <sub>RTN</sub> < 1.5 V                                                                                    | 405  | 455  | 505  |      |

|                 | ILIM current limit programming      | $R_{LIM}$ = 125 kΩ, $V_{RTN}$ > 1.5 V during startup                                                        | 180  | 250  | 300  | mA   |

|                 | Thermal shutdown temperature        |                                                                                                             |      | 144  |      | 00   |

|                 | Thermal shutdown hysteresis         |                                                                                                             |      | 20   |      | °C   |

####

# **ORDERING INFORMATION**

| TA          | PACKAGE <sup>(1)</sup> | PART NUMBER |

|-------------|------------------------|-------------|

| 2024 7002   | Plastic TSSOP (PW)     | TPS2371PW   |

| 0°C to 70°C | Plastic SOIC (D)       | TPS2371D    |

<sup>(1)</sup> The PW and D packages are also available taped and reeled. Add an R suffix to the device type (i.e., TPS2371PWR).

#### TERMINAL FUNCTIONS

| TERMIN                   | NAL |     |                                                                                                                                                                                                            |

|--------------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                     | NO. | I/O | DESCRIPTION                                                                                                                                                                                                |

| CLASS 2 O                |     | 0   | Sets classification level with a single resistor to VEE. A precision voltage of 10.0 V is applied to this pin during classification. R <sub>CLASS</sub> values listed in Table 1.                          |

| DELAY <sup>(2)</sup> 7 I |     | I   | UVLO turn-off delay programming. Connect a capacitor between VCC and this pin to program the UVLO turn-off delay.                                                                                          |

| DET                      | 3   | 0   | Connect the 24.9k $\Omega$ detection resistor (RDET) between this pin and VDD.                                                                                                                             |

| EN_DC                    | 6   | 0   | Ties to dc-to-dc converter's shutdown or soft-start pin. Sinks 80μA until the load capacitor is fully charged.                                                                                             |

| ILIM(1)                  | 1   | 0   | Sets startup current limit level with a resistor to VEE. If using $C_{DC2DCIN} > 180 \mu$ F, IRUSH must be less than 400 mA. Extra capacitance on ILIM pin can cause oscillations in the current waveform. |

| RTN 5 O                  |     | 0   | Return pin. Connect this pin to input return side of the dc-to-dc converter.                                                                                                                               |

| VDD                      | 8   | I   | Connection to PD input port positive voltage.                                                                                                                                                              |

| VEE 4 I                  |     | I   | Input side power return for the controller.                                                                                                                                                                |

NOTE 1:

$$I_{INRUSH} = 450 \text{ mA} - \left(\frac{25 \text{ k}\Omega}{R_{LIM}}\right) \times (1 \text{ A})$$

NOTE 2:  $T_{DELAY} = \left(\frac{100 \text{ ms}}{\mu F}\right) \times C_{DELAY}$

# **DETAILED PIN DESCRIPTIONS**

#### ILIM (Pin 1)

Inrush current limiting pin. This pin is used to program the inrush current of the device. Due to the low UVLO hysteresis of this device, a 1.0- $\mu$ F capacitor from this pin to VEE is necessary to allow startup with 20  $\Omega$  in series with V<sub>DD</sub> as required by the IEEE standards. By placing a resistor to VEE from this pin, the inrush current into the load will be limited via the following equation:

$$I_{INRUSH} = 450 \text{ mA} - \left(\frac{25 \text{ k}\Omega}{\text{R}_{LIM}}\right) \times (1 \text{ A})$$

(1)

# CLASS (Pin 2)

Classification pin. The PD can be optionally classified by adding a resistor from this pin to ground. The resistor specific to each class is given in *Table 1: PoE Classification Resistance Values*.

#### DET (Pin3)

Detection pin. This pin is used to set up the detection resistance during PD detection. By tying a resistor,  $R_{DET}$ , from this pin to VDD, the user sets the detection resistance. It should be noted that the device itself looks like approximately 1 M $\Omega$  of resistance in parallel with  $R_{DET}$ .

#### VEE (Pin 4)

Negative supply to the device.

#### RET (Pin 5)

Negative supply to the load. This pin is the drain side of a FET between the RET pin and the VEE pin, providing hot swap capabilities to the load. When the FET is switched on, there is approximately  $300m\Omega$  between this pin and VEE.

# **DETAILED PIN DESCRIPTIONS (continued)**

# EN\_DC (Pin 6)

Enable pin for the load. This pin is intended to be used with a dc-to-dc coverter with a soft start capacitor. When power is not available to the dc-to-dc converter, this pin sinks 80-µA and hold off the softstart cap on the dc-to-dc converter. Once the voltage across the load is within 1.5 V of its final value, the EN\_DC pin stops drawing current and become high impedance, allowing the dc-to-dc to soft start normally.

# DELAY (Pin 7)

This pin controls the amount of time that the device ignores an undervoltage condition on VDD. That time is set by the following equation:

$$T_{DELAY} = \left(\frac{100 \text{ ms}}{\mu F}\right) \times C_{DELAY}$$

(2)

# VDD (Pin 8)

Positive supply to the device.

**Table 1. PoE Classification Resistance Values**

| CLASS | RESISTANCE (R <sub>CLASS</sub> ) VALUE ( $\Omega$ ) | POWERED DEVICES<br>(PDs) Power (W) | CLASSIFICATION<br>CURRENT (mA) |

|-------|-----------------------------------------------------|------------------------------------|--------------------------------|

| 0     | 4420                                                | 0.44 – 12.95                       | 2.5                            |

| 1     | 953                                                 | 0.44 – 3.84                        | 10.8                           |

| 2     | 549                                                 | 3.84 - 6.49                        | 18.6                           |

| 3     | 357                                                 | 6.49 – 12.95                       | 28.4                           |

| 4     | 255                                                 | reserved for future use            | 39.6                           |

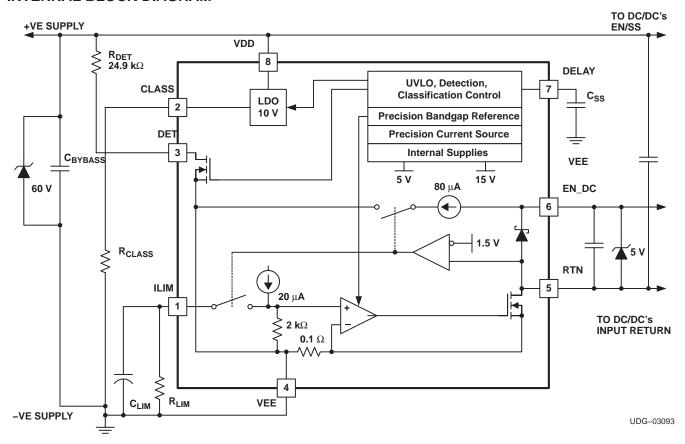

# **INTERNAL BLOCK DIAGRAM**

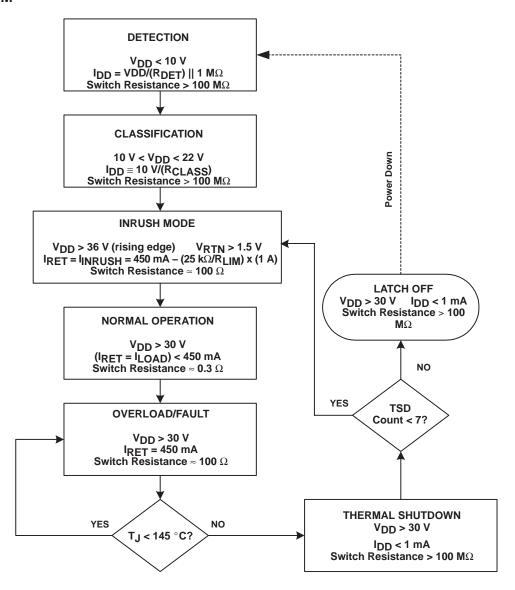

#### STATE DIAGRAM

# **MACHINE STATE**

#### **OVERVIEW**

With the addition of power via media dependent interface (MDI) to the IEEE 802.3af Standard, all data terminal equipment (DTE) now has the option to receive power over existing cabling that is used for data transmission. The IEEE 802.3af Standard defines the requirements associated with providing and receiving power over the existing cabling. The power sourcing equipment (PSE) provides the power on the cable and the powered device (PD) receives the power. As part of the IEEE 802.3af Standard, the interface between the PSE and PD is defined as it relates to the detection and classification protocol.

#### POWER SOURCING EQUIPMENT DETECTION OF A POWERED DEVICE

A powered device (PD) draws power or requests power by participating in a PD detection algorithm. This algorithm requires the power sourcing equipment (PSE) to probe the link looking for a valid PD. The PSE probes the link by sending out a voltage between 2.8 V and 10 V across the power lines. A valid PD detects this voltage and places a resistance of between 23.75 k $\Omega$  and 26.25k $\Omega$  across the power lines. Naturally, the current varies depending on the input voltage. Upon detecting this current, the PSE concludes that a valid PD is connected at the end of the ethernet cable and is requesting power.

If the powered device (PD) is in a state in which it does not accept power, the PD is required to place a resistance above or below the values listed for a valid PD. On the lower end, a range between 12 k $\Omega$  and 23.75 k $\Omega$  signifies that the PD does not require power. On the higher end, the range is defined to be between 26.25 k $\Omega$  and 45 k $\Omega$ . Any resistance value less than 12 k $\Omega$  and greater than 45 k $\Omega$ , is interpreted by the PSE as a non-valid PD detection signature.

The TPS2371 participates in the detection algorithm by activating an internal FET, which connects the DET pin of the device to VEE. As a result, any resistance connected between VDD and the DET pin of the TPS2371 is, in effect, across the power lines. This internal FET is active only when input power to the PD is between 2.8 V and 10 V.

#### POWER SOURCING EQUIPMENT CLASSIFICATION OF A POWERED DEVICE

After the detection phase, the PSE can optionally initiate a classification of the PD. The classification of a PD is used by the PSE to determine the maximum power required by the PD during normal operation. Five different levels of classification are defined by the IEEE 802.3af Standard. These levels are shown in Table 2.

Table 2. Powered Device Classification Levels

| CLASS | USAGE       | POWER<br>POV<br>(V | VER          | CLASSIF<br>CURF<br>(m |     |

|-------|-------------|--------------------|--------------|-----------------------|-----|

|       |             | MIN                | MAX          | MIN                   | MAX |

| 0     | Default     | 0.44               | 12.95        | 0                     | 4   |

| 1     | Optional    | 0.44               | 3.84         | 9                     | 12  |

| 2     | Optional    | 3.84               | 6.49         | 17                    | 20  |

| 3     | Optional    | 6.49               | 12.95        | 26                    | 30  |

| 4     | Not allowed | reserved fo        | r future use | 36                    | 44  |

Classification of the PD is optionally performed by the PSE only after a valid PD has been detected. To determine PD classification, the PSE increases the voltage across the power lines to between 15.5 V and 20.5 V. The amount of current drawn by the PD determines the classification (see Table 2).

When the input voltage to the TPS2371 is between 14.0 V and 20.5 V, the TPS2371 uses an internal regulator to generate a fixed voltage on the CLASS pin. A resistor connected between the CLASS pin and VEE draws a fixed amount of current and thereby defines the classification level of the PD.

#### POWER SOURCING EQUIPMENT POWER TO THE POWERED DEVICE

Upon completion of the detection and optional classification phases, the PSE ramps its output voltage above 36 V . Once the UVLO threshold has been reached, the internal FET is turned on. At this point, the PD begins to operate normally and it continues to operate normally as long as the input voltage remains above 30 V. For most PDs, this input voltage is down-converted using an on board dc-to-dc converter to generate the required voltages.

The TPS2371 is designed to apply the PSE output voltage of 36 V to 57 V across the input of the on board dc-to-dc converter. This is accomplished on the TPS2371 by turning on an internal pass FET located across the power return.

#### **Programming the Inrush Current**

During the initial turn-on of the pass FET, an inrush current is created from the charging of the capacitance at the input of the dc-to-dc converter. According to the IEEE 802.3af specification, if the input capacitance is less than 180- $\mu$ F, the PSE limits the inrush current. If the input capacitance is greater than 180- $\mu$ F, the IEEE 802.3af specification requires the PD to limit the inrush current to less than 400 mA.

In order to satisfy the IEEE 802.3af requirements, the TPS2371 has been designed for a typical current limit of 450 mA. This current limit setting satisfies the normal operation requirements as well as the inrush requirements for a capacitive load of 180- $\mu$ F or less. If a larger load capacitor is desired, the TPS2371 has been designed with a programmable inrush current limit feature. This feature allows the designer the option of using a capacitor larger than 180- $\mu$ F. Note that the inrush current feature may also be used to lower voltage drops in the cabling between the PSE and the PD during startup.

The programmable inrush current limit has a range of 50 mA to 449 mA. The limit is set by connecting an external resistor from ILIM (pin 1) to VEE (pin 4) of the TPS2371. Equation (3) shows the calculation for the programmable inrush current limit.

$$I_{INRUSH} = 450 \text{ mA} - \left(\frac{25 \text{ k}\Omega}{R_{LIM}}\right) \times (1 \text{ A})$$

(3)

where R<sub>LIM</sub> is a value between 63.5 k $\Omega$  and 25 M $\Omega$ .

# Using EN\_DC as a SoftStart or a PowerGood Function

The EN\_DC pin is an output intended for use as a soft-start for a dc-to-dc converter. During the initial turn-on of the pass FET, an internal 80- $\mu$ A current sink is enabled on the EN\_DC pin. This internal current sink is removed only after the load capacitance has been charged to within 1.5-V of the supply voltage. By connecting the EN\_DC output to the soft start capacitor of a dc-to-dc converter, the internal current sink keeps the dc-to-dc converter off during startup. Once the voltage across the converter has reached within 1.5 V of full voltage, the dc-to-dc converter is allowed to soft start. A 5-V zener diode connected between EN\_DC and RTN is required for operation in this architecture.

For operation as a powergood output, the EN\_DC requires an external pull-up. A 1-M $\Omega$  resistor is recommended. The EN\_DC output also requires a clamp to limit the output voltage to within recommended operating levels. A 5-V zener diode connected between EN\_DC and RTN (pin 5 of the TPS2371) is recommended. This configuration allows the EN\_DC pin to act as an open drain output with which many designers are more familiar.

#### SURGE SUPPRESSION

As specified in the *Absolute Maximum Ratings* table, the absolute maximum input voltage of the TPS2371 is 68 V. The IEEE 802.3af Power-Over-Ethernet Standard specifies the voltage range of PSE output is between 44 V asd 57 V. This PSE output voltage range would be reduced by cable, connector and other IR drops between the PSE and the TPS2371 in the PD. However, the use of extended cable lengths and transformers in some applications may induce transients in excess of 68 V during a hot plug event. To manage these transient events and keep them from significantly exceeding the application's maximum voltage, a transorb such as the SMAJ54A should be placed between the positive input supply, VDD (pin 8), and the negative input supply, VEE (pin 4). This, combined with a 0.1- $\mu$ F bypass capacitor in parallel with the transorb helps to protect the TPS2371 from damage caused by transients during hot plug events. The transorb or zener diode should be selected such that it does not zener below the maximum required application voltage of 57 V, but before reaching the 68-V absolute maximum rating. For layout purposes, the 0.1- $\mu$ F capacitor should be placed as close as possible to the device; the transorb or zener diode should be placed as close to the supply connector as possible. Based on the nature of the PD application, these measures should be considered an implementation requirement.

#### **USE OF BARREL RECTIFIERS**

Many applications use barrel rectifiers after the RJ-45 connector in order to be polarity insensitive. Barrel rectifiers in front of the TPS2371 cause the voltages at the device to be lower than the voltages at the RJ-45. The TPS2371 allows for this and is IEEE802.3af compliant during the detection and classification phases. For the detection phase, the device begins detection for voltages as low as 1.3 V across the supply pins. For the optional classification phase, the device is guaranteed to start classification below 14 V across the supply pins. Once classification has been engaged, it becomes latched-in and further voltage drops due to cable resistance and class current does not cause it to switch out of classification. However, in cases where the PSE is operating at minimum class voltage (15.5 V) and there is a 20- $\Omega$ , 100-m cable between the PSE and the PD, Class 3 devices may not classify correctly when using barrel rectifiers. Class 3 device designs should include schottky diodes to handle all corner cases or switch to Class 0 devices when using barrel rectifiers.

#### Thermal Shutdown

In the event of a short circuit or overload condition, the TPS2371 begins to heat up until thermal shutdown is reached. Once thermal shutdown is reached, the internal FET is switched off, removing the load from the supply. After the device has cooled sufficiently, it retries by restarting the internal FET. If the overload or short is not removed, the device cycles thermal shutdown seven times before latching the internal FET off. Once the internal FET is latched off, power needs to be cycled to reset the latch.

Figure 1 shows an application where 40 V < V<sub>IN</sub> < 57 V. In this case, the brick supply is greater then 40 V and goes through TPS2371.

Figure 1. For Applications 40 V < V<sub>IN</sub> < 57 V.

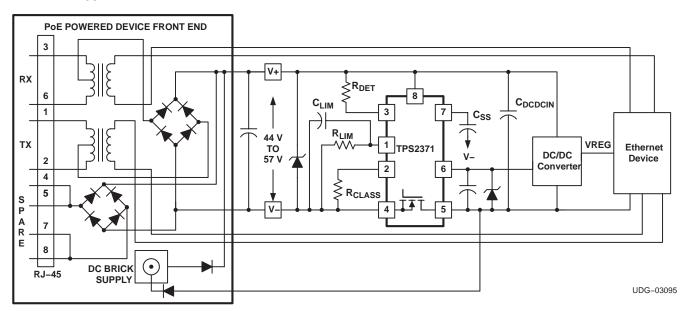

Figure 2 shows an application where  $V_{IN}$  < 36 V. In this application, the brick supply is bypassing the hot swap switch. Consequently, the dc-to-dc converter can operate from any voltage. However, for  $V_{BRICK}$  < 23 V, a Class 0 resistor ( $R_{CLASS}$  = 4.42 k $\Omega$ ) is recommended. This minimizes the power dissipation in TPS2371 if  $V_{BRICK}$  falls in the classification voltage range (15 V to 20 V). The 80- $\mu$ A current sink on EN\_DC pin is enabled only if VDD > 36 V.

Figure 2. For Applications  $V_{IN}$  < 40 V.

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| TPS2371DR             | NRND   | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | 2371             |

| TPS2371DR.A           | NRND   | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | 2371             |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 31-Oct-2023

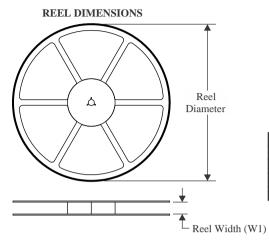

# TAPE AND REEL INFORMATION

# TAPE DIMENSIONS + K0 - P1 - B0 W Cavity - A0 -

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

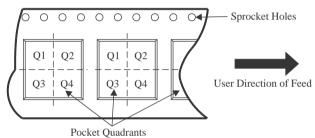

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

|   | Device    | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---|-----------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ĺ | TPS2371DR | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

# PACKAGE MATERIALS INFORMATION

www.ti.com 31-Oct-2023

# \*All dimensions are nominal

| Ì | Device    | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|-----------|--------------|-----------------|------|------|-------------|------------|-------------|

| ı | TPS2371DR | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

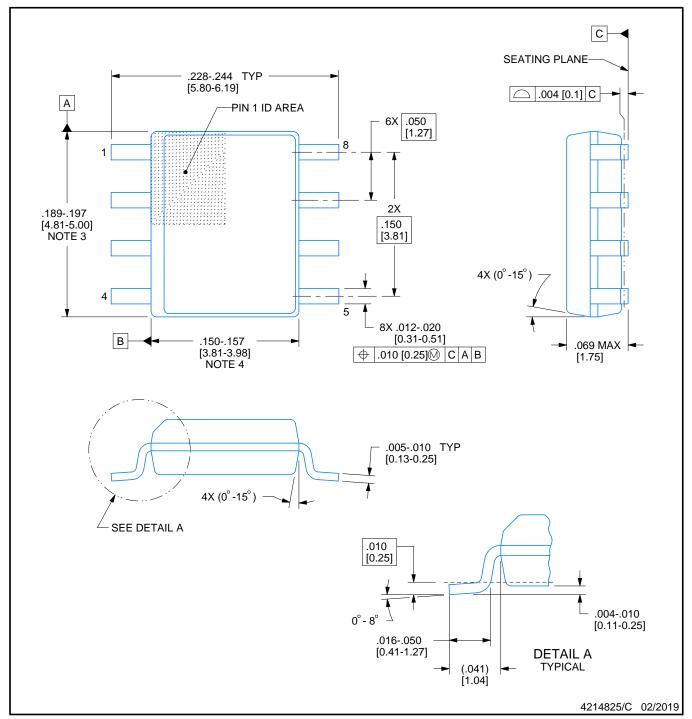

SMALL OUTLINE INTEGRATED CIRCUIT

# NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

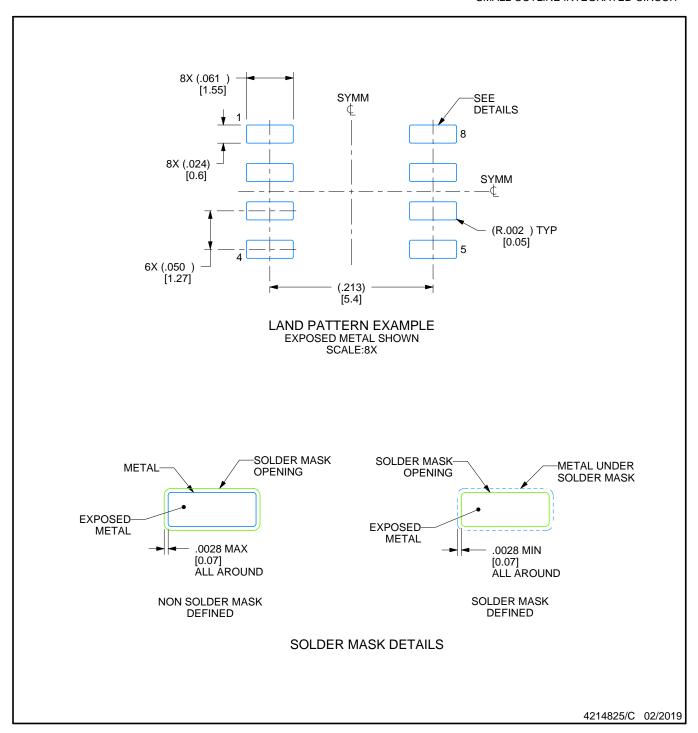

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

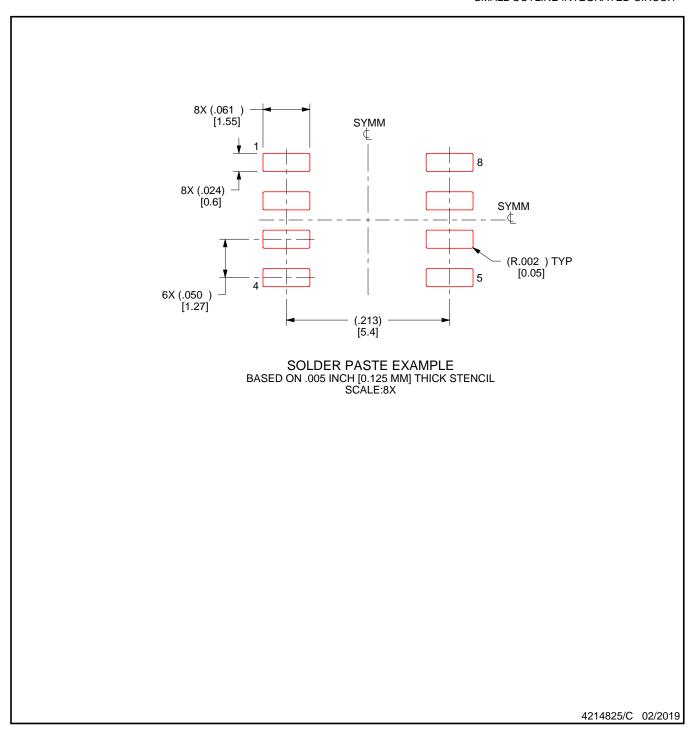

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025