TPS40428

ZHCSCO3A-MAY 2014-REVISED JULY 2014

# TPS40428 支持自适性电压调节 (AVS) 总线的双路输出、双相、 PMBus™ 同步降压无驱动器控制器

# 特性

- 出厂默认为智能功率模式(与德州仪器(TI)的 CSD95378B 智能功率级兼容并且与出厂默认为非 智能功率模式的 TPS40425 引脚对引脚等效)

- 单电源运行: 4.5V 至 20V

- V<sub>OUT</sub> 为 0.6V

- 双路或多相同步降压控制器

- 独立的高速 AVS 接口

- 快速瞬态响应

- 最多可堆叠四相位

- 2相、3相或4相交错式相移

- 精准电流均流

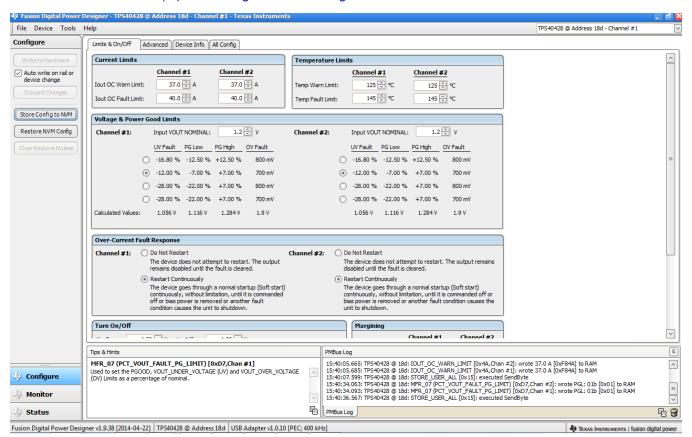

- PMBus 接口功能

- 2mV步长的边界上升/下降

- 可编程故障限制和响应

- ±0.8% V<sub>OUT</sub>

- 精准电流监视

- 智能功率模式下的 ±3°C 外部温度监视

- 可编程欠压闭锁 (UVLO) 开/关阈值

- 可编程软启动时间、接通延迟和关断延迟

- 用于存储定制配置的片载非易失性存储器 (NVM)

- -40°C 到 125°C 温度范围内的基准电压为 0.6V, 精度为 0.5%

- 可编程  $f_{SW}$ ,范围从 200kHz 到 1.5MHz

- 支持预偏置输出

- 差分远程感应

- 与外部时钟同步

- 过流/过压/欠压/过热(OC/OV/UV/OT)故障保护

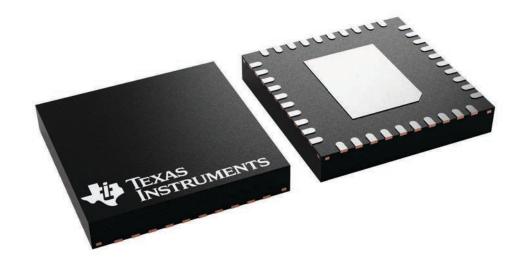

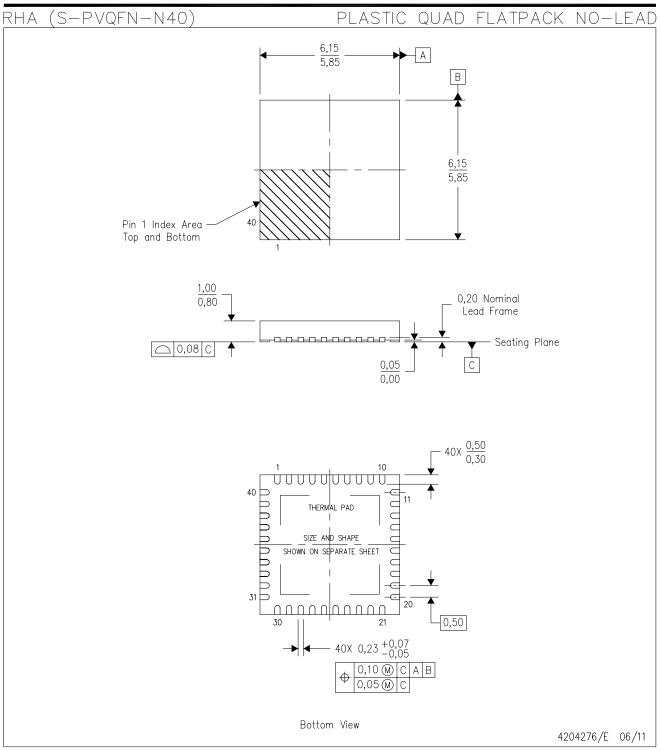

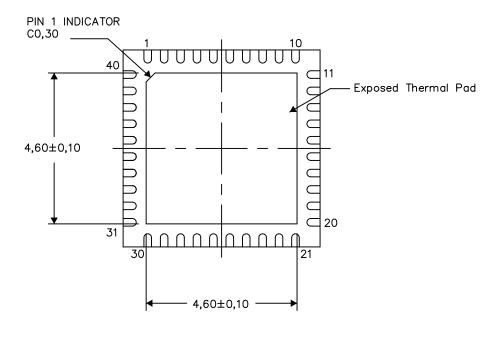

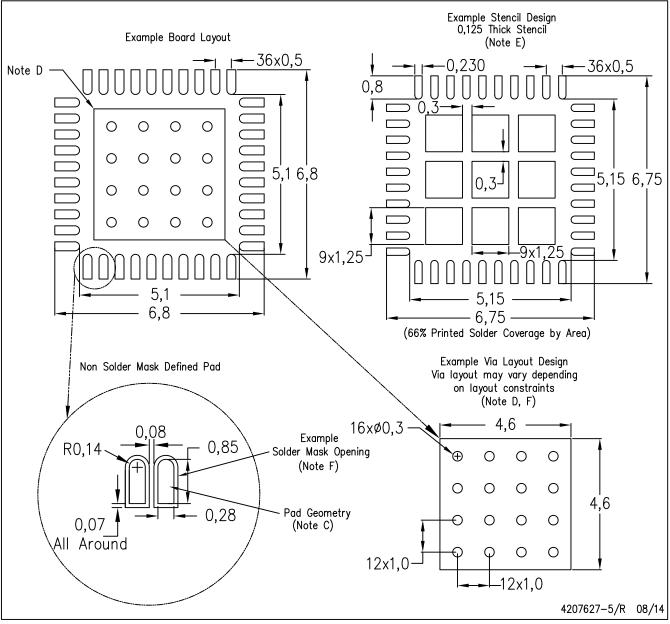

- 40引脚, 6mm x 6mm, QFN封装

# 2 应用

- 无线基础设施

- 交换机/路由器联网/服务器/存储

# 3 说明

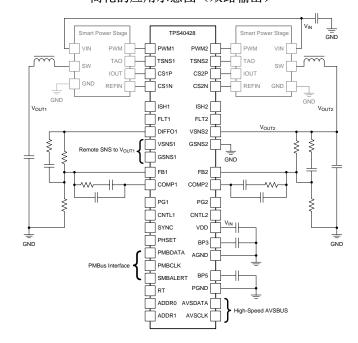

TPS40428 器件是一款 PMBus 同步降压无驱动器控制 器。 其出厂默认设置的工作模式为智能功率模式, 在 进行 PMBus 编程并重启电源之后即可在非智能功率模 式下工作。 该器件可配置为双路输出或双相操作。 而 且该器件最多可堆叠 4 个相位, 支持高达 120A 的负 载电流。2相、3相或4相交错式相移可减少输入和输 出波纹, 从而减小输入和输出电容。

它的宽输入电压范围可支持 5V 和 12V 中间电源总 线。 基准电压精度达 0.5%, 可满足现代专用集成电路 (ASIC) 对于精准电压的需求。

根据 PMBus 标准, TPS40428 器件可对基准电压、故 障限制、UVLO 阈值、软启动时间以及接通和关断延 迟进行编程。

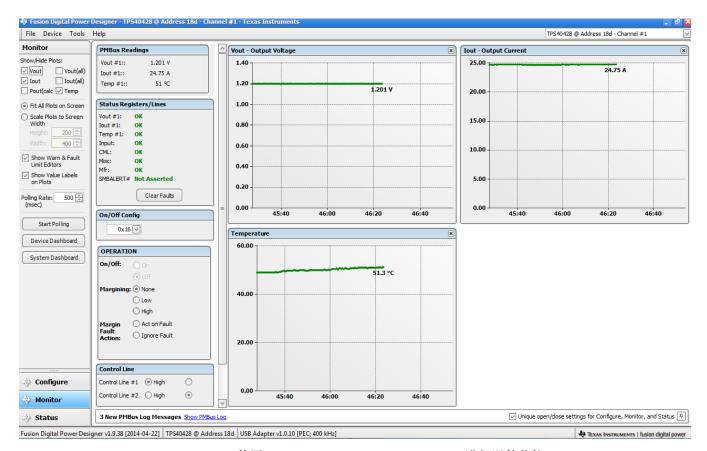

此外,该器件还实现了精准的测量系统,用于监视各通 道的输出电压、电流和温度。

# 器件信息(1)

| 部件号      | 封装       | 封装尺寸 (标称值)      |

|----------|----------|-----------------|

| TPS40428 | RHA (40) | 6.00mm x 6.00mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

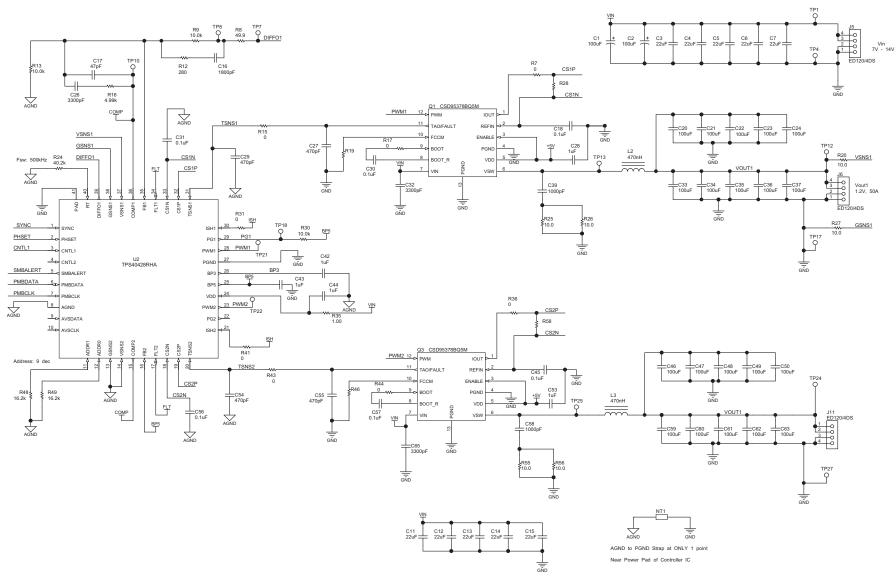

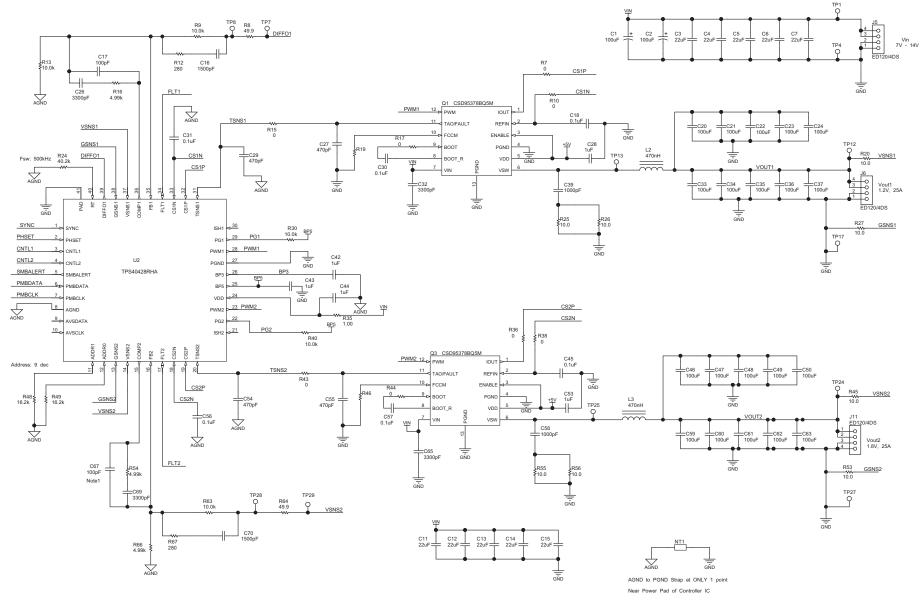

# 简化的应用示意图(双路输出)

12 机械封装和可订购信息 .......84

|   | 目录                                   | <u>.</u><br>C |                                                      |                 |

|---|--------------------------------------|---------------|------------------------------------------------------|-----------------|

| 1 | 特性 1                                 |               | 7.4 Device Functional Modes                          | 23              |

| 2 | 应用 1                                 |               | 7.5 Programming                                      | <mark>24</mark> |

| 3 | 说明 1                                 |               | 7.6 Register Maps                                    | 29              |

| 4 | 修订历史记录 2                             | 8             | Applications and Implementation                      | 71              |

| 5 | Pin Configuration and Functions3     |               | 8.1 Application Information                          | 71              |

| 6 | Specifications4                      |               | 8.2 Typical Application                              | 71              |

| • | 6.1 Absolute Maximum Ratings 4       | 9             | Power Supply Recommendations                         | 80              |

|   | 6.2 Handling Ratings5                | 10            | Layout                                               | 80              |

|   | 6.3 Recommended Operating Conditions |               | 10.1 Layout Guidelines                               | 80              |

|   | 6.4 Thermal Information              |               | 10.2 Layout Example                                  | 81              |

|   | 6.5 Electrical Characteristics 5     | 11            | 器件和文档支持                                              | 82              |

|   | 6.6 Typical Characteristics          |               | 11.1 开发支持                                            | 82              |

| 7 | Detailed Description 12              |               | 11.2 Trademarks                                      | 83              |

| - | 7.1 Overview 12                      |               | 11.3 Electrostatic Discharge Caution                 | 83              |

|   | 7.2 Functional Block Diagram         |               | 11.4 术语表                                             | 83              |

|   |                                      |               | 1 1 to 1 1 11 1 at 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                 |

# 4 修订历史记录

| Changes from Original (MAY 2014) to Revision A                        | Pag                          |

|-----------------------------------------------------------------------|------------------------------|

| Updated Pin Functions table                                           |                              |

| • Updated notes and conditions in Electrical Characteristics table. N | lo updates to specifications |

| Added clarity to Table 4                                              | 20                           |

| Added clarity to Table 5                                              | 2                            |

| Added clarity to Table 6                                              | 29                           |

| • Updated (E0h) MFR_SPECIFIC_16 (COMM_EEPROM_SPARE)                   | section6                     |

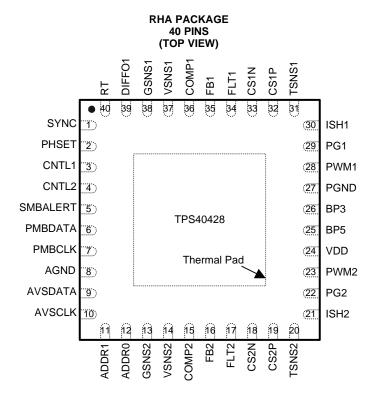

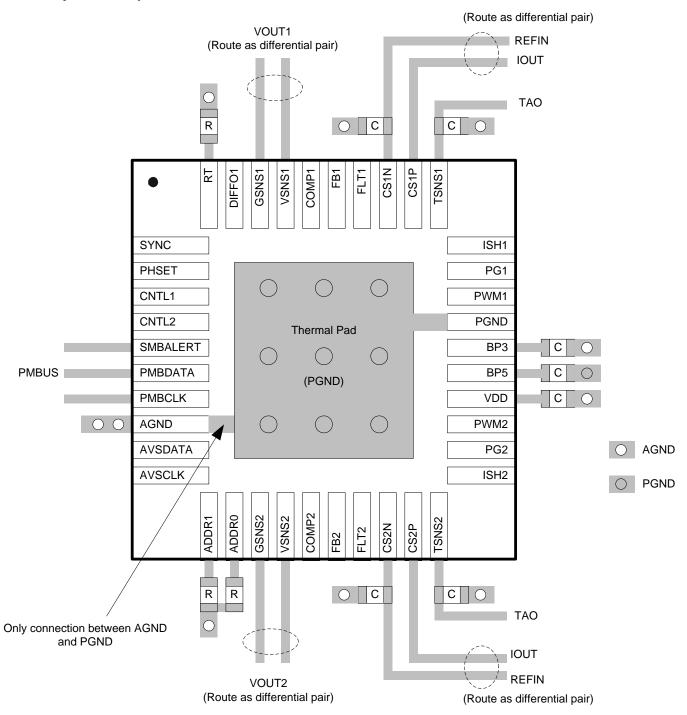

# 5 Pin Configuration and Functions

**Pin Functions**

| PIN     |     | 1/0 | DECORPORTION                                                                                                                                                                                               |  |  |  |  |

|---------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME    | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                |  |  |  |  |

| ADDR1   | 11  | - 1 | High order address pin for PMBus device. Connect a resistor to AGND (see Table 3).                                                                                                                         |  |  |  |  |

| ADDR0   | 12  | - 1 | Low order address pin for PMBus device. Connect a resistor to AGND (see Table 3).                                                                                                                          |  |  |  |  |

| AGND    | 8   | _   | Analog ground pin, used for analog signal. Connect to thermal pad directly.                                                                                                                                |  |  |  |  |

| AVSCLK  | 10  | - 1 | AVS clock                                                                                                                                                                                                  |  |  |  |  |

| AVSDATA | 9   | - 1 | AVS data                                                                                                                                                                                                   |  |  |  |  |

| BP3     | 26  | 0   | 3.3-V bias power for logic. A low-ESR ceramic capacitor with a value of 0.33 $\mu$ F or greater should be connected closely from this pin or to AGND. The maximum suggested capacitor value is 10 $\mu$ F. |  |  |  |  |

| BP5     | 25  | 0   | Output bypass for the internal regulator. A low-ESR ceramic capacitor of 1 $\mu$ F or greater should be connected closely from this pin to PGND pin. The maximum suggested capacitor value is 10 $\mu$ F.  |  |  |  |  |

| CNTL1   | 3   | I   | pgic level input which starts or stops channel 1. An internal 6- $\mu$ A current source pulls $V_{CNTL1}$ up to $V_{BP}$ hen the pin is floating.                                                          |  |  |  |  |

| CNTL2   | 4   | ı   | Logic level input which starts or stops channel 2. An internal 6- $\mu$ A current source pulls $V_{CNTL2}$ up to $V_{BP5}$ when the pin is floating.                                                       |  |  |  |  |

| COMP1   | 36  | 0   | Output of the error amplifier 1 and connection node for loop feedback components                                                                                                                           |  |  |  |  |

| COMP2   | 15  | 0   | Output of the error amplifier 2 and connection node for loop feedback components                                                                                                                           |  |  |  |  |

| CS1N    | 33  | I   | Negative pin of current sense amplifier for channel 1. An internal, $4-k\Omega$ resistor pulls CS1N to 1.24 V during smart power mode operation to provide a bias voltage required by smart power stage.   |  |  |  |  |

| CS1P    | 32  | ı   | Positive pin of current sense amplifier for channel 1                                                                                                                                                      |  |  |  |  |

| CS2N    | 18  | I   | Negative pin of current sense amplifier for channel 2. An internal, 4-k $\Omega$ resistor pulls CS2N to 1.24 V during smart power mode operation to provide a bias voltage required by smart power stage.  |  |  |  |  |

| CS2P    | 19  | - 1 | Positive pin of current sense amplifier for channel 2                                                                                                                                                      |  |  |  |  |

| DIFFO1  | 39  | 0   | Remote Sense Amplifier Output for channel 1                                                                                                                                                                |  |  |  |  |

| FB1     | 35  | I   | Inverting input to the error amplifier 1. In normal operation, the voltage on this pin is equal to the internal reference voltage. Connect the FB1 pin to the BP5 pin to set the channel as slave channel. |  |  |  |  |

# Pin Functions (continued)

| PIN      |     |     | DESCRIPTION                                                                                                                                                                                                                                                          |

|----------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                          |

| FB2      | 16  | I   | Inverting input to the error amplifier 2. In normal operation, the voltage on this pin is equal to the internal reference voltage. Connect the FB2 pin to the BP5 pin to set the channel as slave channel.                                                           |

| FLT1     | 34  | I/O | Fault signal of channel 1. An internal 100-kΩ resistor pulls FLT1 to BP3.                                                                                                                                                                                            |

| FLT2     | 17  | I/O | Fault signal of channel 2. An internal 100-kΩ resistor pulls FLT2 to BP3.                                                                                                                                                                                            |

| GSNS1    | 38  | - 1 | Negative pin of Voltage Sense Signal for channel 1                                                                                                                                                                                                                   |

| GSNS2    | 13  | I   | Negative pin of Voltage Sense Signal for channel 2                                                                                                                                                                                                                   |

| ISH1     | 30  | I   | Current sharing signal of channel 1 for multi-phase mode                                                                                                                                                                                                             |

| ISH2     | 21  | I   | Current sharing signal of channel 2 for multi-phase mode                                                                                                                                                                                                             |

| PG1      | 29  | 0   | Open drain power good indicator for channel 1 output voltage. This pin is pulled to ground internally in slave channel.                                                                                                                                              |

| PG2      | 22  | 0   | Open drain power good indicator for channel 2 output voltage. This pin is pulled to ground internally in slave channel.                                                                                                                                              |

| PGND     | 27  | _   | Power GND, used for BP5 bypass capacitor. Connect to thermal pad directly.                                                                                                                                                                                           |

| PHSET    | 2   | I/O | Phase set for multiphase mode                                                                                                                                                                                                                                        |

| PMBCLK   | 7   | I   | PMBus clock pin                                                                                                                                                                                                                                                      |

| PMBDATA  | 6   | I/O | PMBus data pin                                                                                                                                                                                                                                                       |

| PWM1     | 28  | 0   | PWM signal for channel 1                                                                                                                                                                                                                                             |

| PWM2     | 23  | 0   | PWM signal for channel 2                                                                                                                                                                                                                                             |

| RT       | 40  | I   | Connecting a resistor from this pin to AGND sets the oscillator frequency                                                                                                                                                                                            |

| SMBALERT | 5   | 0   | PMBus alert pin.                                                                                                                                                                                                                                                     |

| SYNC     | 1   | I/O | This is the synchronization pin for use with the external clock. The frequency of external SYNC signal must be 4 times of desired switching frequency during 1-, 2-, or 4- phases, and must be 3 times the desired switching frequency during 3-phase configuration. |

| TSNS1    | 31  | ı   | External temperature sense signal input for channel 1                                                                                                                                                                                                                |

| TSNS2    | 20  | I   | External temperature sense signal input for channel 2                                                                                                                                                                                                                |

| VDD      | 24  | I   | Power input to the controller. A low-ESR ceramic capacitor with a value of 1-µF or greater should be connected closely from this pin to AGND.                                                                                                                        |

| VSNS1    | 37  | I   | Positive pin of voltage sense signal for channel 1                                                                                                                                                                                                                   |

| VSNS2    | 14  | ı   | Positive pin of voltage sense signal for channel 2                                                                                                                                                                                                                   |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                        |                                                                                                        | MIN  | MAX | UNIT |

|------------------------|--------------------------------------------------------------------------------------------------------|------|-----|------|

|                        | VDD                                                                                                    | -0.3 | 22  |      |

| Input voltage range    | CS1N, CS1P, CS2N, CS2P, GSNS1, GSNS2, ISH1, ISH2, PHSET, PMBDATA, PMBCLK, SMBALERT, SYNC, VSNS1, VSNS2 | -0.3 | 5.5 | V    |

|                        | AVSDATA, AVSCLK, TSNS1, TSNS2                                                                          | -0.3 | 3.6 |      |

|                        | CNTL1, CNTL2, FB1, FB2                                                                                 | -0.3 | 7   |      |

| Output valtage range   | ADDR0, ADDR1, RT, BP3                                                                                  | -0.3 | 3.6 | V    |

| Output voltage range   | BP5, COMP1, COMP2, DIFFO1, FLT1, FLT2, PG1, PG2, PWM1, PWM2                                            | -0.3 | 7   | V    |

| Operating junction tem | perature, T <sub>J</sub>                                                                               | -40  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 Handling Ratings

|                    |                           |                                                                                          | MIN  | MAX | UNIT |

|--------------------|---------------------------|------------------------------------------------------------------------------------------|------|-----|------|

| T <sub>stg</sub>   | Storage temperature range |                                                                                          | -55  | 155 | °C   |

| .,                 |                           | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | -2   | 2   | 1.27 |

| V <sub>(ESD)</sub> | Electrostatic discharge   | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | -1.5 | 1.5 | kV   |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|          |                                | MIN | MAX | UNIT |

|----------|--------------------------------|-----|-----|------|

| $V_{DD}$ | Input operating voltage        | 4.5 | 20  | V    |

| TJ       | Operating junction temperature | -40 | 125 | °C   |

#### 6.4 Thermal Information

|                    | THERMAL METRIC <sup>(1)</sup>                | TPS40428      | LIMIT |

|--------------------|----------------------------------------------|---------------|-------|

|                    | I HERMAL METRIC                              | QFN (40 PINS) | UNIT  |

| $R_{\theta JA}$    | Junction-to-ambient thermal resistance       | 27.8          |       |

| $R_{\theta JCtop}$ | Junction-to-case (top) thermal resistance    | 17.2          |       |

| $\theta_{JB}$      | Junction-to-board thermal resistance         | 4.8           | °C/W  |

| $R_{\psi JT}$      | Junction-to-top characterization parameter   | 0.2           | C/VV  |

| $R_{\psi JB}$      | Junction-to-board characterization parameter | 4.8           |       |

| $R_{\theta JCbot}$ | Junction-to-case (bottom) thermal resistance | 1.2           |       |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 6.5 Electrical Characteristics

|                         | PARAMETER                               | TEST CONDITIONS                             | MIN  | TYP  | MAX   | UNIT |

|-------------------------|-----------------------------------------|---------------------------------------------|------|------|-------|------|

| INPUT SUPF              | PLY                                     |                                             |      |      |       |      |

| $V_{VDD}$               | Input supply voltage range              |                                             | 4.5  |      | 20    | V    |

| I <sub>VDD</sub>        | Input operating current                 | Switching, no driver load, smart-power mode |      | 17.3 |       | mA   |

| 100                     |                                         | Not switching, smart-power mode             |      | 15.9 |       |      |

| UVLO                    |                                         |                                             |      |      |       |      |

| V <sub>IN(on)</sub>     | Input turn-on voltage <sup>(1)</sup>    | Default settings                            | 4    | 4.25 | 4.5   | V    |

| V <sub>IN(off)</sub>    | Input turn-off voltage <sup>(1)</sup>   | Default settings                            | 3.8  | 4    | 4.2   | V    |

| V <sub>INON(rng)</sub>  | Programmable range for turn on voltage  |                                             | 4.25 |      | 16    | V    |

| V <sub>INOFF(rng)</sub> | Programmable range for turn off voltage |                                             | 4    |      | 15.75 | V    |

| ERROR AME               | PLIFIER                                 |                                             |      |      |       |      |

| $V_{FB}$                | Feedback pin voltage                    | -40°C ≤ T <sub>J</sub> ≤ 125°C              | 597  | 600  | 603   | mV   |

| A <sub>OL</sub>         | Open-loop gain <sup>(2)</sup>           |                                             | 80   |      |       | dB   |

| G <sub>BWP</sub>        | Gain bandwidth product <sup>(2)</sup>   |                                             | 50   |      |       | MHz  |

| I <sub>FB</sub>         | FB pin bias current (out of pin)        | V <sub>FB</sub> = 0.6 V                     |      |      | 100   | nA   |

|                         | Sourcing                                | V <sub>FB</sub> = 0 V                       | 1    |      |       | A    |

| ICOMP                   | Sinking                                 | V <sub>FB</sub> = 1 V                       | 1    |      |       | mA   |

<sup>(1)</sup> Hysteresis of at least 150 mV is specified by design.

<sup>(2)</sup> Specified by design. Not production tested.

|                                        | PARAMETER                                                                        | TEST CONDITIONS                                                            | MIN       | TYP                  | MAX  | UNIT |

|----------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------|----------------------|------|------|

| BP5 REGUL                              | ATOR                                                                             |                                                                            |           |                      |      |      |

|                                        | Output voltage                                                                   | I <sub>BP5</sub> = 10 mA                                                   | 4.5       | 5                    | 5.5  | V    |

| $V_{BP5}$                              | Dropout voltage                                                                  | $V_{VIN} - V_{BP5}, V_{VDD} = 4.5 \text{ V},$<br>$I_{BP5} = 25 \text{ mA}$ |           |                      | 400  | mV   |

| I <sub>BP5</sub>                       | Output current                                                                   | V <sub>VDD</sub> = 12 V                                                    | 40        |                      |      | mA   |

| V <sub>BP5UV</sub>                     | Regulator UVLO voltage (3)                                                       |                                                                            | 3.3       | 3.55                 | 3.8  | V    |

| V <sub>BP5UV(hyst)</sub>               | Regulator UVLO voltage hysteresis (3)                                            |                                                                            |           | 300                  |      | mV   |

| BP3 REGUL                              | ATOR                                                                             |                                                                            |           |                      | '    |      |

| V <sub>BP3</sub>                       | Output voltage                                                                   | $V_{VDD} = 4.5 \text{ V}, I_{BP3} \le 5 \text{ mA}$                        | 3.1       | 3.3                  | 3.5  | V    |

| OSCILLATO                              | R AND RAMP GENERATOR                                                             |                                                                            | <u> </u>  |                      |      |      |

|                                        | Adjustment range <sup>(3)</sup>                                                  |                                                                            | 200       |                      | 1500 | kHz  |

|                                        | Switching frequency <sup>(4)</sup>                                               | $R_{RT} = 100 \text{ k}\Omega$                                             | 180       | 200                  | 220  |      |

| Fsw V <sub>RAMP</sub> V <sub>VAL</sub> | Switching frequency <sup>(4)</sup>                                               | $R_{RT} = 40 \text{ k}\Omega$                                              | 450       | 500                  | 550  | kHz  |

|                                        | Switching frequency <sup>(4)</sup>                                               | $R_{RT} = 13 \text{ k}\Omega$                                              | 1230      | 1370                 | 1500 |      |

| V <sub>RAMP</sub>                      | Ramp amplitude (peak-to-peak)                                                    | - N                                                                        |           | V <sub>VDD</sub> /10 |      | V    |

|                                        | Valley voltage                                                                   |                                                                            |           | 1.22                 |      | V    |

| SYNCHRON                               |                                                                                  |                                                                            |           |                      |      |      |

| V <sub>SYNCH</sub>                     | SYNC high-level threshold (5)                                                    |                                                                            | 2         |                      |      | V    |

| V <sub>SYNCL</sub>                     | SYNC low-level threshold <sup>(5)</sup>                                          |                                                                            |           |                      | 0.8  | V    |

| t <sub>SYNC</sub>                      | Minimum SYNC pulse width (3)                                                     |                                                                            |           |                      | 100  | ns   |

| -31NC                                  | Maximum PWM frequency for SYNC <sup>(3)</sup>                                    |                                                                            | 1500      |                      |      |      |

| ferno                                  | Minimum PWM frequency for SYNC <sup>(3)</sup>                                    |                                                                            |           |                      | 200  | kHz  |

| $f_{	extsf{SYNC}}$                     | SYNC frequency range (increase from nominal oscillator frequency) <sup>(3)</sup> |                                                                            | -20%      |                      | 20%  |      |

| PWM                                    |                                                                                  |                                                                            |           |                      |      |      |

| V <sub>OH(pwm)</sub>                   | PWM high-level output voltage                                                    | I <sub>LOAD</sub> = 500 μA                                                 | 4.5       |                      |      | V    |

| V <sub>OL(pwm)</sub>                   | PWM low-level output voltage                                                     | I <sub>LOAD</sub> = 500 μA                                                 |           |                      | 0.5  | V    |

| t <sub>OFF(min)</sub>                  | Minimum off-time                                                                 | LOAD CCC P                                                                 |           | 100                  |      | ns   |

| t <sub>ON(min)</sub>                   | Minimum pulse                                                                    |                                                                            |           | 90                   |      | ns   |

| SOFT-STAR                              |                                                                                  |                                                                            |           |                      |      |      |

|                                        | Soft-start time (6)                                                              | Factory default settings                                                   |           | 2.7                  |      | ms   |

| t <sub>SS</sub>                        | Programmable range <sup>(3)</sup>                                                | r detery decidant commige                                                  | 0.6       |                      | 9    | ms   |

| *55                                    | Accuracy over range <sup>(3)</sup>                                               |                                                                            | -15%      |                      | 15%  | 1110 |

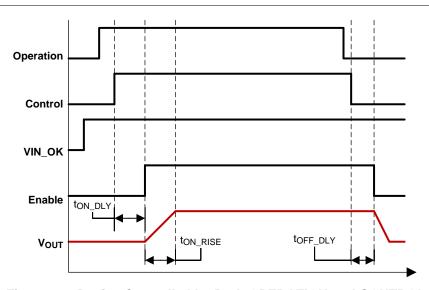

| town                                   | Turn-on delay time <sup>(3)</sup>                                                | Factory default settings                                                   | 1070      | 0                    | 1070 | ms   |

| t <sub>ON(dly)</sub>                   | Turn-off delay time (3)                                                          | Factory default settings                                                   |           | 0                    |      | ms   |

| TOFF(dly)                              | INSE AMPLIFIER                                                                   | . actory doladit dottings                                                  |           | •                    |      | 1110 |

| BW                                     | Closed-loop bandwidth <sup>(3)</sup>                                             |                                                                            | 2         |                      |      | MHz  |

|                                        | Maximum DIFFO output voltage                                                     |                                                                            | 2         |                      | 4.7  | V    |

| $V_{\text{DIFFO(max)}}$                | <u>-</u>                                                                         | ()/ G ) = 10 \/                                                            | 6         |                      | 4.7  |      |

| V <sub>DIFFO(err)</sub>                | Error voltage from DIFFO1 to (V <sub>SNS1</sub> – G <sub>SNS1</sub> )            | $(V_{SNS1} - G_{SNS1}) = 1.0 \text{ V}$                                    | <u>-6</u> |                      |      | mV   |

|                                        |                                                                                  | $(V_{SNS1} - G_{SNS1}) = 3.6 \text{ V}$                                    | -19       |                      | 19   |      |

| I <sub>DIFFO</sub>                     | Sourcing                                                                         |                                                                            | 1         |                      |      | mA   |

|                                        | Sinking                                                                          |                                                                            | 1         |                      |      |      |

Specified by design. Not production tested.

Apply to 1-,2- or 4-phase operation. For 3-phase operation, the switching frequency is 33% higher than the value in the table. The external SYNC pin signal must be a square waveform with 50% duty cycle.

The soft-start time is the time that the internal reference voltage rises from 0 V to 600 mV.

|                          | PARAMETER                                              | TEST CONDITIONS                                                | MIN  | TYP                 | MAX | UNIT |

|--------------------------|--------------------------------------------------------|----------------------------------------------------------------|------|---------------------|-----|------|

| CURRENT SE               | ENSING AMPLIFIER                                       |                                                                |      |                     |     |      |

| V                        | Differential insultant linear linear and               | (V <sub>CSxP</sub> – V <sub>CSxN</sub> ), non-smart power mode | 0    |                     | 60  |      |

| V <sub>CS(mg)</sub>      | Differential input voltage linear range                | (V <sub>CSxP</sub> – V <sub>CSxN</sub> ), smart power mode     | 0    |                     | 600 | mV   |

| V <sub>CS(cmr)</sub>     | Input common-mode range                                | Non-smart power mode                                           | 0    |                     | 3.6 | V    |

| V <sub>CS(cm)</sub>      | Input common-mode voltage                              | Smart power mode                                               |      | 1.24                |     | V    |

|                          |                                                        | CHx_CSGAIN_SEL= 20 V/V <sup>(7)</sup> , non-smart power mode   |      | 10                  |     |      |

| A <sub>CS</sub>          | Current sensing gain                                   | CHx_CSGAIN_SEL= 20 V/V <sup>(7)</sup> , smart power mode       |      | 1                   |     | V/V  |

| f <sub>co</sub>          | Closed loop bandwidth (8)                              |                                                                |      | 0.66                |     | MHz  |

| V <sub>CS(chch)</sub>    | Amplifier output difference between two channels (9)   | $I_{PHASE}$ = 20 A, IOUT_CAL_GAIN = 0.503 $mΩ$                 | -6%  |                     | 6%  |      |

| CURRENT LI               | MIT                                                    |                                                                |      |                     |     |      |

| t <sub>OFF(oc)</sub>     | Off-time between restart attempts                      | Hiccup mode                                                    |      | 7 × t <sub>SS</sub> |     | ms   |

|                          | Output peak current overcurrent fault                  | Factory default settings                                       |      | 40                  |     |      |

| I <sub>OC(flt)</sub>     | threshold                                              | Programmable range                                             | 3    |                     | 50  | Α    |

|                          | Output peak current overcurrent warning                | Factory default settings                                       |      | 37                  |     |      |

| I <sub>OC(warn)</sub>    | threshold                                              | Programmable range                                             | 2    |                     | 49  | Α    |

|                          | Output peak current overcurrent fault accuracy         | $I_{OUT}$ = 40 A, IOUT_CAL_GAIN = 0.503 m $\Omega$             | -10% |                     | 10% | -    |

| I <sub>OC(acc)</sub>     | Output peak current overcurrent warning accuracy       | $I_{OUT}$ = 37 A, IOUT_CAL_GAIN = 0.503 m $\Omega$             | -10% |                     | 10% |      |

| PGOOD                    |                                                        |                                                                |      |                     |     |      |

| V <sub>FBPGH</sub>       | FB PGOOD high threshold                                | Factory default settings                                       |      | 642                 |     | mV   |

| V <sub>FBPGL</sub>       | FB PGOOD low threshold                                 | Factory default settings                                       |      | 558                 |     | mV   |

| V <sub>PG(acc)</sub>     | PGOOD accuracy over range                              |                                                                | -4%  |                     | 4%  |      |

| V <sub>pg(hyst)</sub>    | FB PGOOD hysteresis voltage                            |                                                                | 15   | 28                  | 45  | mV   |

| R <sub>PGOOD</sub>       | PGOOD pull-down resistance                             | V <sub>FB</sub> = 0 V, I <sub>PGOOD</sub> = 5 mA               |      | 50                  |     | Ω    |

| I <sub>PGOOD(lk)</sub>   | PGOOD pin leakage current                              | V <sub>FB</sub> = 600 mV, V <sub>PGOOD</sub> = 5 V             |      |                     | 20  | μA   |

| t <sub>PGDELAY</sub>     | PGOOD delay time after soft-start sequence is complete | Factory default settings                                       |      | 2                   |     | ms   |

| OUTPUT OVE               | RVOLTAGE/UNDERVOLTAGE                                  |                                                                |      |                     | ,   |      |

| V <sub>FBOV</sub>        | FB pin over voltage threshold                          | Factory default settings                                       |      | 700                 |     | mV   |

| V <sub>FBUV</sub>        | FB pin under voltage threshold                         | Factory default settings                                       |      | 528                 |     | mV   |

| V <sub>UVOV(acc)</sub>   | FB UV/OV accuracy over range                           |                                                                | -4%  |                     | 4%  |      |

|                          | TAGE TRIMMING AND MARGINING                            |                                                                |      |                     |     |      |

| V <sub>FBTM(step)</sub>  | Resolution of FB steps with trim and margin            |                                                                |      | 2                   |     | mV   |

| t <sub>FBTM(step)</sub>  | Transition time per trim or margin step                | After soft-start time                                          |      | 30                  |     | μs   |

| V <sub>FBTM(max)</sub>   | Maximum FB voltage with trim or margin only            |                                                                |      | 660                 |     | mV   |

| V <sub>FBTM(min)</sub>   | Minimum FB voltage with trim or margin only            |                                                                |      | 480                 |     | mV   |

| V <sub>FBTM(rng)</sub>   | FB voltage range with trim and margin combined         |                                                                | 420  |                     | 660 | mV   |

| $V_{FBMH}$               | Margin high FB pin voltage                             | Factory default settings                                       |      | 660                 |     | mV   |

| V <sub>FBML</sub>        | Margin low FB pin voltage                              | Factory default settings                                       |      | 540                 |     | mV   |

|                          | TAGE AT AVS MODE                                       |                                                                |      |                     | ,   |      |

| V <sub>FBAVS(step)</sub> | Resolution of FB steps at AVS mode                     |                                                                |      | 2                   |     | mV   |

| V <sub>FBAVS(max)</sub>  | Maximum FB voltage at AVS mode                         |                                                                |      | 1.5                 |     | V    |

| V <sub>FBAVS(min)</sub>  | Minimum FB voltage at AVS mode                         |                                                                |      | 500                 |     | mV   |

- (7) Refer to PMBus command MFR\_SPECIFIC\_21 (OPTIONS) (E5h) section.

- 8) Specified by design. Not production tested.

- (9) Performance verified under application conditions.

|                        | PARAMETER                                                   | TEST CONDITIONS                                                                                                                          | MIN    | TYP MAX   | UNIT  |

|------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|-------|

| AVS INTERF             |                                                             | 1201 00110110110                                                                                                                         | 141114 | TTT IN/AA | 01111 |

| V <sub>VIO</sub>       | ASIC I/O voltage <sup>(10)</sup>                            |                                                                                                                                          | 1.8    | 2.5       | V     |

| VIO                    | ·                                                           | V <sub>VIO</sub> = 2.5 V                                                                                                                 | 1.75   | 2.3       | V     |

| V <sub>IH(avs)</sub>   | High-level input voltage, AVSCLK, AVSDATA                   | V <sub>VIO</sub> = 2.5 V<br>V <sub>VIO</sub> = 1.8 V                                                                                     | 1.75   |           | V     |

|                        |                                                             | 110                                                                                                                                      | 1.20   | 0.75      |       |

| V <sub>IL(avs)</sub>   | Low-level input voltage, AVSCLK, AVSDATA                    | V <sub>VIO</sub> = 2.5 V                                                                                                                 |        | 0.75      | V     |

|                        |                                                             | V <sub>VIO</sub> = 1.8 V                                                                                                                 |        | 0.54      |       |

| I <sub>IH(avs)</sub>   | High-level input current, AVSCLK, AVSDATA <sup>(10)</sup>   |                                                                                                                                          | -50    | 50        | μA    |

| $I_{IL(avs)}$          | Low-level input current, AVSCLK, AVSDATA (10)               |                                                                                                                                          | -50    | 50        | μA    |

| f <sub>AVS</sub>       | AVS clock frequency range                                   |                                                                                                                                          | 10     | 30        | MHz   |

| MEASUREME              | NT SYSTEM                                                   |                                                                                                                                          |        |           |       |

| M <sub>VOUT(rng)</sub> | V <sub>OUT</sub> measurement range                          |                                                                                                                                          | 0.5    | 3.6       | V     |

| M <sub>VOUT(acc)</sub> | V <sub>OUT</sub> measurement accuracy <sup>(11)</sup>       | $V_{OUT} = 1 \text{ V}, 0^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$                                                             | -0.8%  | 0.8%      |       |

| M <sub>IOUT(rng)</sub> | I <sub>OUT</sub> measurement range <sup>(12)</sup>          |                                                                                                                                          | 0      | 50        | Α     |

| M <sub>IOUT(acc)</sub> | I <sub>OUT</sub> measurement accuracy <sup>(11)</sup>       | $I_{OUT} \ge 20 \text{ A, } IOUT\_CAL\_GAIN = 0.503 \text{ m}\Omega, \\ 0^{\circ}C \le T_{J} \le 125^{\circ}C, \text{ smart power mode}$ | -640   | 640       | mA    |

| PMBus INTER            | RFACE <sup>(13)</sup>                                       |                                                                                                                                          |        |           |       |

| V <sub>IH</sub>        | High-level input voltage, CLK, DATA, CNTL                   |                                                                                                                                          | 2.1    |           |       |

| V <sub>IL</sub>        | Low-level input voltage, CLK, DATA, CNTL                    |                                                                                                                                          |        | 0.8       | V     |

| I <sub>IH</sub>        | High-level input current, CLK, DATA, CNTL                   | Pin voltage = 3.3 V                                                                                                                      | -10    | 10        |       |

|                        | Low-level input current, CLK, DATA, CNTL                    | Pin voltage = 0 V                                                                                                                        | -10    | 10        | μA    |

| V <sub>OL</sub>        | Low-level output voltage, DATA, SMBALRT                     | I <sub>OUT</sub> = 4 mA                                                                                                                  |        | 0.4       | V     |

| I <sub>OH</sub>        | High-level output open drain leakage current, DATA, SMBALRT | $V_{OUT} = V_{BP5}$                                                                                                                      | 0      | 10        | μA    |

| I <sub>OL</sub>        | Low-level output open drain current, DATA, SMBALRT          |                                                                                                                                          | 4      |           | mA    |

| C <sub>OUT</sub>       | Pin capacitance, CLK, DATA <sup>(10)</sup>                  |                                                                                                                                          |        | 1         | pF    |

|                        | PMBus operating frequency range                             | Slave mode                                                                                                                               | 10     | 400       | kHz   |

| f <sub>PMB</sub>       | Bus free time between START and STOP <sup>(10)</sup>        | Slave mode                                                                                                                               | 1.3    | 400       | KIIZ  |

|                        |                                                             |                                                                                                                                          |        |           |       |

| t <sub>HD:STA</sub>    | Hold time after repeated START <sup>(10)</sup>              |                                                                                                                                          | 0.6    |           | μs    |

| t <sub>SU:STA</sub>    | Repeated START set-up time <sup>(10)</sup>                  |                                                                                                                                          | 0.6    |           | _     |

| t <sub>SU:STO</sub>    | STOP setup time (10)                                        |                                                                                                                                          | 0.6    |           |       |

| t <sub>HD:DAT</sub>    | Data hold time (10)                                         | Receive mode                                                                                                                             | 0      |           |       |

| 110.0711               |                                                             | Transmit mode                                                                                                                            | 300    |           | ns    |

| t <sub>SU:DAT</sub>    | Data setup time <sup>(10)</sup>                             |                                                                                                                                          | 100    |           |       |

| t <sub>TIMEOUT</sub>   | Error signal/detect <sup>(10)</sup>                         |                                                                                                                                          | 25     | 35        | ms    |

| t <sub>LOW:MEXT</sub>  | Cumulative clock low master extend time <sup>(10)</sup>     |                                                                                                                                          |        | 10        | ms    |

| t <sub>LOW:SEXT</sub>  | Cumulative clock low slave extend time <sup>(10)</sup>      |                                                                                                                                          |        | 25        | ms    |

| t <sub>LOW</sub>       | Clock low time <sup>(10)</sup>                              |                                                                                                                                          | 1.3    |           | μs    |

| t <sub>HIGH</sub>      | Clock high time (10)                                        |                                                                                                                                          | 0.6    |           | μs    |

| t <sub>FALL</sub>      | CLK/DATA fall time <sup>(10)</sup>                          |                                                                                                                                          |        | 300       |       |

| t <sub>RISE</sub>      | CLK/DATA rise time <sup>(10)</sup>                          |                                                                                                                                          |        | 300       | ns    |

| t <sub>RETENTION</sub> | Retention of configuration parameters (10)                  | T <sub>J</sub> = 25°C                                                                                                                    | 100    |           | Year  |

|                        |                                                             |                                                                                                                                          |        |           |       |

- (10) Specified by design. Not production tested.

- (11) Performance verified under application conditions.

(12) The actual measurement range is limited by IOUT\_CAL\_GAIN command. See the IOUT\_CAL\_GAIN (38h) section.

(13) The device supports both 100-kHz and 400-kHz bus speeds. The PMBus timing parameters in this table is for operation at 400 kHz. If the PMBus operating frequency is 100 kHz, refer to SMBus specification for timing parameters.

|                          | PARAMETER                                                         | TEST CONDITIONS                                        | MIN   | TYP  | MAX    | UNIT |

|--------------------------|-------------------------------------------------------------------|--------------------------------------------------------|-------|------|--------|------|

| PMBus ADD                | RESSING                                                           |                                                        |       |      | '      |      |

| I <sub>ADD</sub>         | Address pin bias current                                          |                                                        | 8.775 | 9.75 | 10.725 | μA   |

| INITIALIZATI             | ION TIME                                                          |                                                        |       |      |        |      |

| t <sub>INI</sub>         | Initialization time after BP3 voltage is ready <sup>(14)</sup>    |                                                        |       | 1    |        | ms   |

| TEMPERATU                | JRE SENSE AND THERMAL SHUTDOWN                                    |                                                        |       |      |        |      |

| T <sub>SD</sub>          | Junction shutdown temperature (14)                                |                                                        |       | 160  |        |      |

| T <sub>HYST</sub>        | Thermal shutdown hysteresis (14)                                  |                                                        |       | 20   |        | °C   |

| I <sub>TSNS(ratio)</sub> | Ratio of bias current flowing out of TSNS pin, state 2 to state 1 | Non-smart power mode                                   | 9.7   | 10   | 10.3   |      |

| I <sub>TSNS(1)</sub>     | State 1 current out of TSNS pin                                   | Non-smart power mode                                   |       | 10   |        | μΑ   |

| I <sub>TSNS(2)</sub>     | State 2 current out of TSNS pin                                   | Non-smart power mode                                   |       | 100  |        | μA   |

| T <sub>SNS(acc)</sub>    | External temperature sense accuracy <sup>(15)</sup>               | -40°C ≤ T <sub>SNS</sub> ≤ 125°C, Non-smart power mode | -4.5  |      | 4.5    | °C   |

| 0.10(000)                |                                                                   | -40°C ≤ T <sub>SNS</sub> ≤ 125°C, Smart power mode     | -3    |      | 3      |      |

| <b>-</b>                 | Overtemperature fault limit <sup>(14)</sup>                       | Factory default settings                               |       | 145  |        | °C   |

| $T_{OT(flt)}$            | OT fault limit range <sup>(14)</sup>                              |                                                        | 120   |      | 165    | 30   |

| <b>-</b>                 | Overtemperature warning limit <sup>(14)</sup>                     | Factory default settings                               |       | 125  |        | ۰.0  |

| T <sub>OT(warn)</sub>    | OT warning limit range <sup>(14)</sup>                            |                                                        | 100   |      | 140    | °C   |

| T <sub>OT(step)</sub>    | OT fault/warning step                                             |                                                        |       | 1    |        | °C   |

| T <sub>OT(hys)</sub>     | OT fault/warning hysteresis (14)                                  |                                                        |       | 20   |        | °C   |

<sup>(14)</sup> Specified by design. Not production tested.

<sup>(15)</sup> Performance verified under application conditions.

# TEXAS INSTRUMENTS

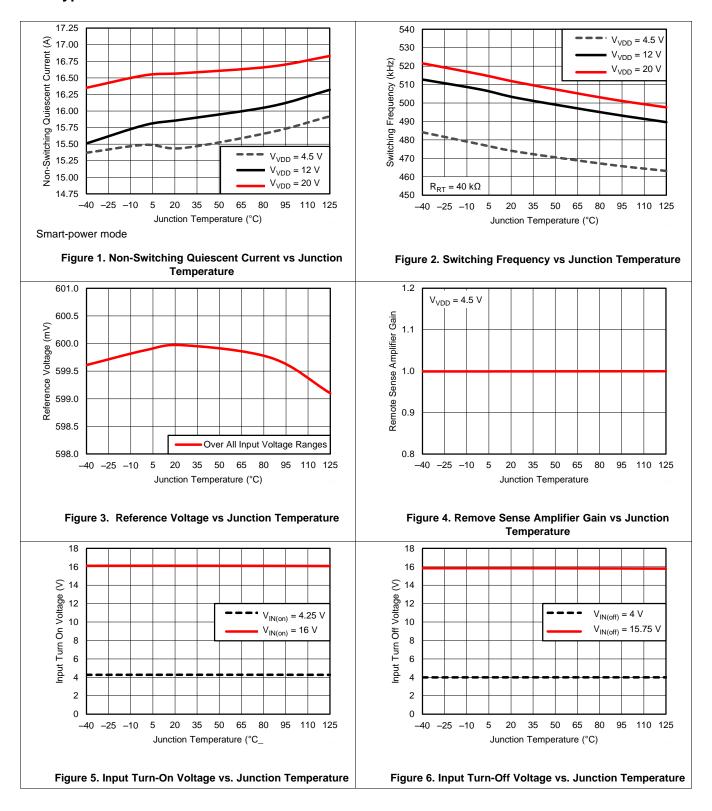

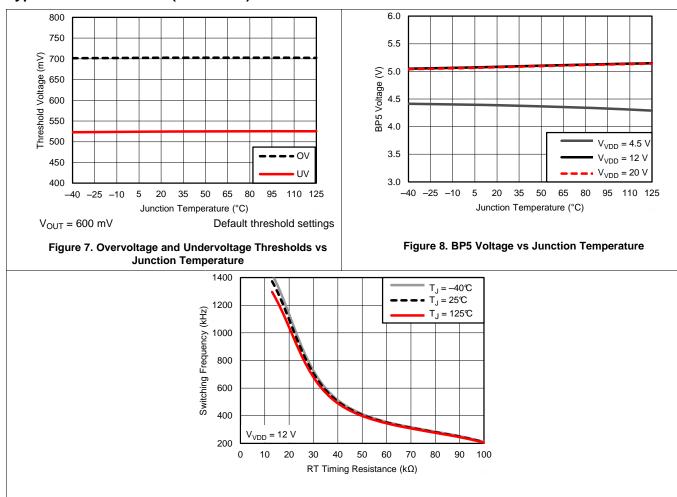

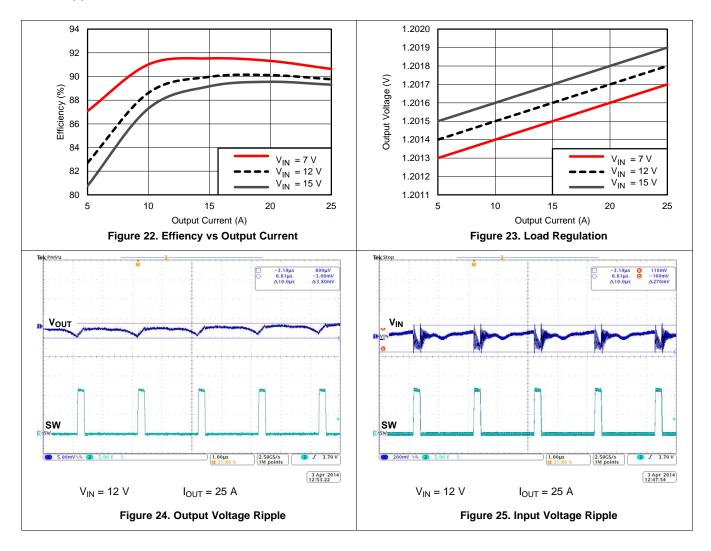

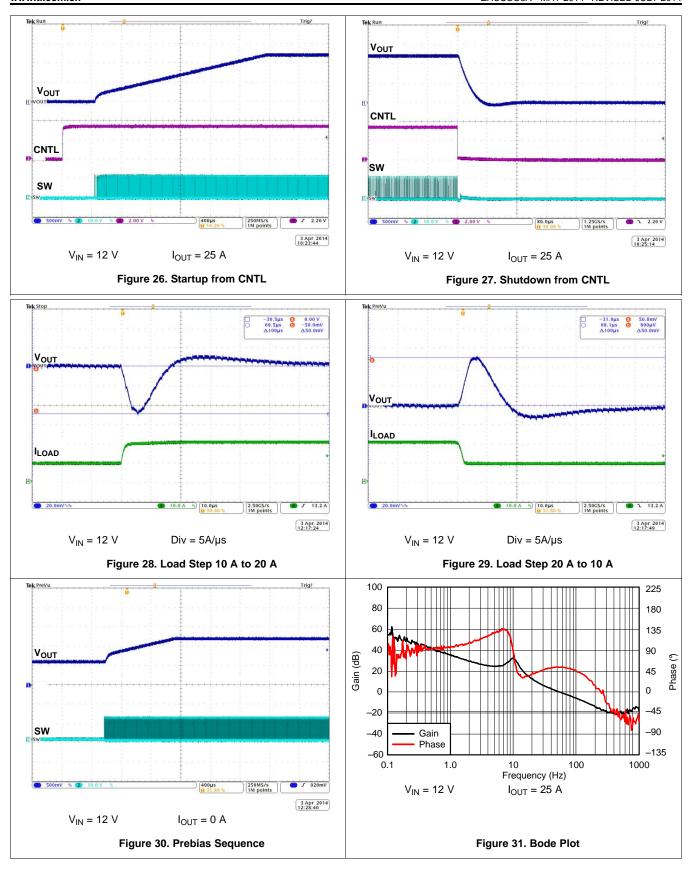

# 6.6 Typical Characteristics

# **Typical Characteristics (continued)**

Figure 9. Timing Resistance vs Switching Frequency

# 7 Detailed Description

#### 7.1 Overview

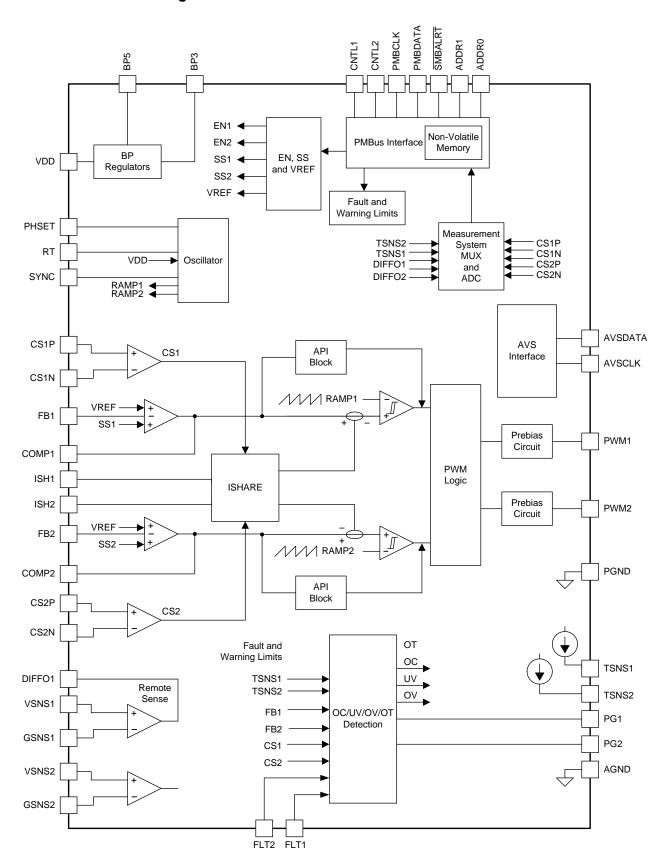

The TPS40428 device is a PMBus synchronous buck driverless controller. It can be configured as a dual-output or single output two phase. It is also stackable up to 4 phases to support load current as high as 120 A. Interleaved phase shift for 2-, 3-, or 4-phase operation reduces the input and output ripples therefore reducing input and output capacitance.

When operating in dual-output mode, the device implements voltage mode control with input feed-forward architecture. With this architecture, the benefits are less noise sensitivity, no control instability issues for small DCR applications, and a smaller minimum controllable on-time, often desired for high conversion ratio applications. In multi-phase mode, the device implements a current-sharing loop to ensure a balance of current between phases.

The wide input voltage range supports 5-V and 12-V intermediate buses. The 0.5% reference voltage satisfies the need for precision voltage required by modern ASICs. PMBus functionality allows the TPS40428 device to program margining function, reference voltage, fault limit, UVLO threshold, soft-start time and turn-on delay time and turn-off delay time. In addition, an accurate measurement system monitors the output voltages, currents and temperatures for individual channels.

# 7.2 Functional Block Diagram

#### 7.3 Feature Description

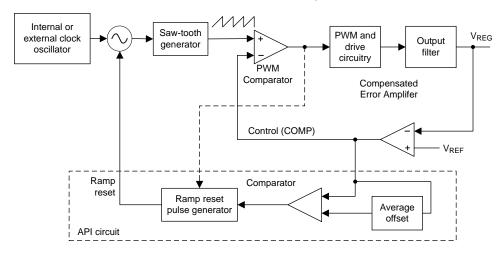

# 7.3.1 Asynchronous Pulse Injection (API)

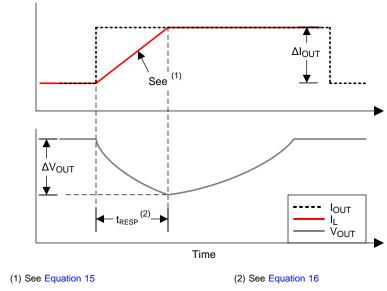

The TPS40428 device implements a TI proprietary control scheme to achieve fast transient response. This scheme has the following key features:

- Voltage mode with API (asynchronous pulse injection) technology

- Fast transient response to reduce output capacitance

Figure 10 shows the control loop with API technology. The control scheme continuously senses the voltage on the COMP pin to determine a transient event that could require a sudden increase in duty-cycle. Upon detecting such an event, additional pulses are asynchronously injected in the PWM stream to quickly respond to the transient and arrest any undershoot in the output voltage.

During load step-up, the deviation of the COMP pin voltage must be above the API comparator threshold to trigger API. Refer to the MFR SPECIFIC 32 (API OPTIONS) (F0h) section for more information.

The API response can be delayed by compensation, parasitic impedance between the output inductor and the voltage sense point. If the delay is large, the asynchronous PWM might inject too much energy and result in overshoot during load step-up. In this case, it is imperative to optimize the compensation and reduce the parasitic impedance. If these efforts cannot reduce the overshoot to an acceptable level, disable the API function.

Figure 10. Asynchronous Pulse Injection (API) Block Diagram

#### 7.3.2 Adaptive Voltage Scaling (AVS)

AVS provides output voltage scaling. AVSBus is a 2-wire communication link that enables bi-directional communication between one ASIC and one or more slave devices for controlling voltage scaling. The two wires required for communication are AVS\_Clock and AVS\_Data. The AVSBus interface could be used exclusively once PMBus has configured the device properly. The AVS commands can select channel 1 or channel 2 of slave device.

AVSBus is scalable for use with multiple slave devices, and allows for independent control of multiple rails within each slave. This scalability is achieved without sacrificing response time for simpler designs with a single slave, by means of configuration settings.

## **NOTE**

PMBus commands are required to:

- configure the device to AVS mode

- set AVS address for the device

- set transition slew rate of output voltage

(1)

# **Feature Description (continued)**

#### 7.3.3 Switching Frequency and Synchronization

A resistor from the RT pin to AGNG sets the switching frequency ( $f_{SW}$ ). The  $R_{RT}$  resistor value is calculated in Equation 1 for switching frequencies below 800 kHz. For switching frequencies above 800 kHz, refer to Table 1 for  $R_{RT}$  resistor values.

$$R_{RT} = \frac{20 \times 10^9}{f_{SW}}$$

where

- $R_{RT}$  is the resistor from the RT pin to AGND, in  $\Omega$

- f<sub>SW</sub> is the desired switching frequency, in Hz

The switching frequency during 3-phase operation is 1.33 times of that at 1-, 2-, or 4-phase operation with the same RT resistor value. Use Equation 2 to calculate the RT resistor value for 3-phase operation.

$$R_{RT} = \frac{26.67 \times 10^9}{f_{SW}}$$

where

- $R_{RT}$  is the resistor from the RT pin to AGND, in  $\Omega$

- $f_{SW}$  is the desired switching frequency, in Hz

frequency, in Hz (2)

| Table 1. Setting | the | Switch | ıng l | Frequ | uency |

|------------------|-----|--------|-------|-------|-------|

|                  |     |        |       |       |       |

| TIMING RESISTANCE<br>R <sub>RT</sub> (kΩ) | SWITCHING FREQUENCY $f_{\rm SW}$ (kHz) |

|-------------------------------------------|----------------------------------------|

| 11                                        | 1520                                   |

| 11.8                                      | 1450                                   |

| 12.4                                      | 1400                                   |

| 13                                        | 1370                                   |

| 15                                        | 1208                                   |

| 20                                        | 948                                    |

| 24.9                                      | 776                                    |

The accuracy of the frequency setting is ±10%. For 3-phase and 4-phase applications, the RT resistors should be identical for both the controllers. In 3-phase and 4-phase applications, the device achieves clock and phase synchronization between the two controllers by connecting the SYNC pins and PHSET pins of the master controller to the corresponding pins on the slave controller. Phase configuration indicating number of phases is set according to the PMBus manufacturer specific command MFR\_SPECIFIC\_22 (E6h).

The switching frequency can be synchronized by an external clock on the SYNC pin. The frequency of the SYNC signal must be 4 times the switching frequency during 1-, 2-, or 4-phase operation, and must be 3 times the switching frequency during 3-phase operation. The SYNC signal must be a square waveform with 50% duty cycle. The high-level threshold must be above 2 V, and the low-level threshold must be below 0.8 V. The change on SYNC and PHSET setting occurs only after a power re-cycle.

### 7.3.4 Voltage Reference

The 600-mV bandgap cell is internally connected to the non-inverting input of the error amplifier. The reference voltage is 600 mV with ±0.5% between -40°C and 125°C.

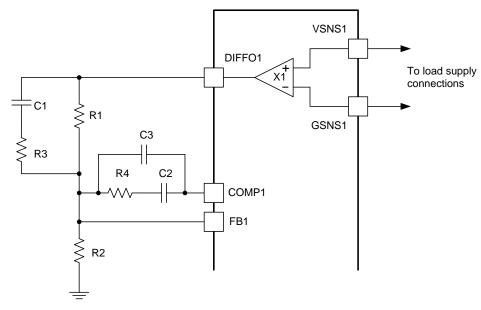

#### 7.3.5 Output Voltage and Remote Sensing Amplifier

Setting the output voltage is very similar to that of a traditional analog controller using a voltage divider from the output to the feedback (FB) pin. The output voltage must be divided to the nominal reference voltage of 600 mV. Figure 11 shows the typical connections for the controller. The voltage at the load is sensed using the unity gain differential voltage sense amplifier. This type of sensing provides better load regulation (see electrical specifications for the maximum output voltage of the differential sense amplifier).

(3)

To prevent output voltage out of regulation, ensure the maximum allowed DIFFO1 voltage ( $V_{BP5}-0.2~V$ ) is larger than actual output voltage at any time including when BP5 ramps down. For output voltages above the DIFFO1 pin specification, connect the output voltage directly to the junction of R1 and C1, leave DIFFO1 open and do not connect the VSNS1 pin to the output voltage. If the design includes a resistor divider before the remote sensing amplifier, the output voltage readout on PMBus is equal to the voltage between VSNS1 and GSNS1.

Figure 11. Setting the Output Voltage

$$R2 = V_{FB} \frac{R1}{(V_{OUT} - V_{FB})}$$

#### where

- V<sub>FB</sub> is the feedback voltage

- V<sub>OUT</sub> is the desired output voltage

- R1 and R2 are in the same units

#### **DESIGN NOTE**

There is no DIFFO2 pin. In dual-output mode, VSNS2 and GSNS2 are connected to the load for channel 2 and the DIFFO2 signal is used internally for voltage monitoring. Connect the output directly to the junction of R1 and C1 for channel 2 to set the output voltage and for feedback.

The feedback voltage can be changed –30% to 10% from the nominal 600 mV using PMBus commands. The output voltage can vary by the same percentage.

## 7.3.6 Current Sensing and Temperature Sensing Modes

The TPS40428 device can operate in two operating modes as far as the current and temperature sensing methods are concerned. The device operates at smart power mode in factory default setting, and it can also operate at non-smart power mode after PMBus programing and power reboot. Refer to the *MFR\_SPECIFIC\_21* (*OPTIONS*) (*E5h*) section for more information.

Consider using the TPS40425 device if non smart-power mode in factory default is preferred in an application. Refer to the TPS40425 datasheet (SLUSBO6) for more information.

During smart power operation, an internal 4-k $\Omega$  resistor pulls the CSxN pin of the TPS40428 device to 1.24 V once VDD voltage is applied. When a board is configured to operate using non smart-power mode, but the TPS40428 device configured for smart power mode is used, the CSxN voltage charges the output capacitor to 1.24 V because the CSxN pin is connected to output for DCR sensing. This problem can avoid in two ways, either:

- the TPS40428 must be reprogrammed to non smart-power mode before it is assembled on the board, or

- the application must include a small-value (on the order of 100 Ω) resistor between output and ground such

that a very small portion of the CSxN pin voltage is applied on output

#### 7.3.6.1 Non Smart-Power Operation

Current sensing is based on inductor DCR (direct current resistance) sensing or a separate current sense resistor. Temperature sensing is based on the  $\Delta$ Vbe measurement of an external diode (x3904). This mode can be used with standard power-stages, such as the CSD95372A.

If inductor DCR is used for current sensing, the TPS40428 device compensates for the temperature variation of DCR value by using the temperature sensed at the external sensor for that channel. The temperature-compensated DCR value is used both for reporting inductor current over PMBus and for overcurrent fault and warning functions.

If a sense resistor is used for current sensing and the temperature variation of resistor value is very small, the temperature compensation in the TPS40428 device can be disabled.

# 7.3.6.2 Smart-Power Operation.

The current sensing function in the TPS40428 device is based on sensed voltage reported by the smart power-stage (at 5 mV/A). No temperature compensation is needed on the controller side. Temperature sensing is based on the voltage reported by the smart power-stage (at 8 mV/°C + 400 mV offset). This mode can be used with the smart power-stage (CSD95378B). During smart-power mode operation, an internal 10-x factor is applied to the current readout, therefore the IOUT\_CAL\_GAIN command must be set to 0.5 m $\Omega$  instead of 5 m $\Omega$ .

#### **NOTE**

Both channels of the TPS40428 device need to operate in the same operating mode (either non smart-power or smart-power) at all times. The factory default setting is smart-power mode. An operation mode change occurs only after a power re-cycle.

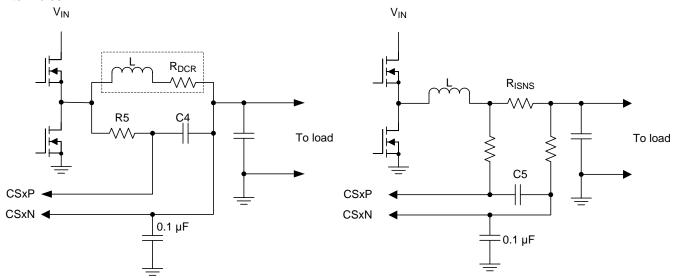

#### 7.3.7 Current Sensing

During non smart-power operation and while the controller uses inductor DCR for current sensing as shown in Figure 12, a filter must be used to remove the large AC component of voltage across the inductor and leave only the component of the voltage that appears across the resistance of the inductor. The values of R5 and C4 for the ideal case can be found using Equation 4. The time constant of the R-C filter should be equal to or greater than the time constant of the inductor. If the time constants are equal, the voltage appearing across C4 is the current in the inductor multiplied the inductor resistance. The voltage across C4 perfectly reflects the inductor ripple current in this case and there is no reason to have a shorter R-C time constant.

Extending the R-C filter time constant beyond the inductor time constant lowers the AC ripple component of voltage present at the current sense pins of the TPS40428 device but allows the correct DC current information to remain intact. This extension also delays slightly the response to an overcurrent event, but reduces noise in the system leading to cleaner overcurrent performance and current reporting data over the PMBus. The extension of R-C filter time slightly affects control loop during multi-phase operation, because the current information is applied to the loop to achieve current balance between the phases.

In all cases, C4 should be placed as close to current sense pins as possible to help avoid problems with noise and a decoupling capacitor connected to the CSNx pin is suggested.

$$R_5 \times C_4 \geq (\frac{L}{R_{DCR}})$$

where

• R5 and  $R_{DCR}$  are in  $\Omega$

- C4 is in F (C4 is suggested to be larger than 220 nF)

- Lis in H (4)

When a sensing resistor performs the current sensing, an R-C-R filter as shown in Figure 13 is recommended to filter noise.

Figure 12. Current Sensing Using DCR

Figure 13. Current Sensing Using Sense Resistor

#### **NOTE**

The programming range of current sense element resistance is between 0.244 m $\Omega$  and 7.747 m $\Omega$ . The IOUT\_CAL\_GAIN command sets the value of the current sense element resistance. The maximum difference between CSP and CSN is limited to 60 mV by the current-sharing and current-limit circuit. However, under some conditions, the current-monitoring circuit has tighter limits, as follows:

- For sense element resistance between 0.244 m $\Omega$  and 0.5795 m $\Omega$ , the maximum differential voltage is 24 mV

- For sense element resistance between 0.5795 m $\Omega$  and 1.1285 m $\Omega$ , the maximum differential voltage is 40 mV

- For sense element resistance higher than 1.1285 m $\Omega$ , the maximum differential voltage is 60 mV

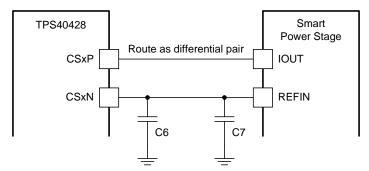

During smart-power operation current sense as Figure 14 shows, the design requires local bypass capacitors for the CSxN pin of the TPS40428 device and the REFIN pin of the smart power stage to avoid noise problems. The recommended value of C6 is 100 nF. Refer to the datasheet of the smart power stage for a C7 value. The two current signal traces must be routed as a differential pair on quiet area.

Figure 14. Current Sensing using Smart-Power Stage

NOTE

During smart-power mode operation, the IOUT\_CAL\_GAIN must be set to 0.5 mΩ.

## 7.3.8 Temperature Sensing

As shown in Figure 15, the non smart-power operation is selected and  $\Delta V$ be measurement of external diode (x3904) is used for temperature sensing. The external diode must be placed close to the inductor if the inductor DCR is used for current sensing, so that the current readout can be more accurate with temperature compensation. It is recommended to place a 1-nF capacitor between the TSNS pin and AGND, and another 1-nF bypass capacitor for the transistor. A separate AGND trace is recommended for the TSNS signal. Route the TSNS trace and the AGND trace as a differential pair.

For temperature sensing using a smart-power stage as shown in Figure 16, the smart-power operation is selected for temperature sensing. Local bypass capacitors are recommended for the TSNS pin of the TPS40428 device and the TAO pin of the smart power stage. The total capacitance of the two bypass capacitors should not exceed 1 nF. The recommended value for both C10 and C11 is 470 pF.

In all cases, the temperature sense trace must be placed in a guiet area and be as short as possible.

Figure 15. Temperature Sensing Using External Diode

Figure 16. Temperature Sensing Using Smart-Power Stage

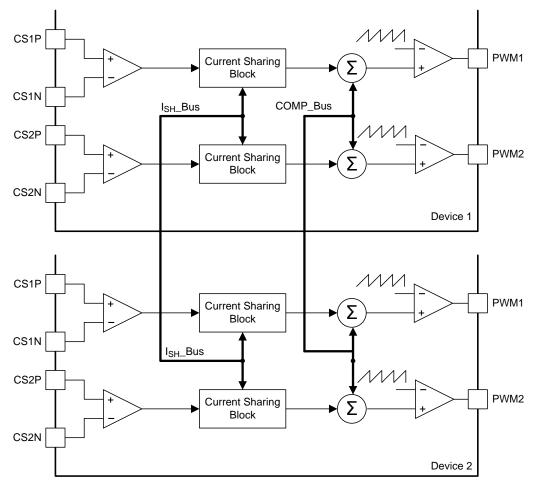

#### 7.3.9 Current Sharing

When the device operates in multi-phase mode, a current sharing loop as shown in Figure 17 maintains the current balance between phases. All phases share the same comparator voltage (V<sub>COMP</sub>). The sensed current in each phase is compared first in a current share block, then to an error current and fed into COMP. The resulting error voltage is compared with the voltage ramp to generate the PWM pulse.

NOTE: All the current sharing components are integrated in the device.

Figure 17. Current Sharing

## 7.3.10 Linear Regulators

The TPS40428 device has two on-board linear regulators that provide suitable power for the internal circuitry of the device. These pins, BP3 and BP5 must be properly bypassed to function properly. The BP3 pin requires a minimum capacitance of 0.33  $\mu$ F connected to AGND and the BP5 pin should have approximately 1  $\mu$ F of capacitance connected to PGND. The bypass capacitors for VDD, BP5 and BP3 pins need to be placed as close to the device as possible.

#### 7.3.11 Power Sequence Between TPS40428 Device and Power Stage

Before soft-start operation begins to generate a PWM signal, the VDD voltage for power stage must be prepared. Refer to the power stage datasheet for VDD value. Without preparation, the TPS40428 device outputs the PWM signal at maximum duty cycle, because the power stage is not working and output voltage is not regulated.

The VDD voltage for power stage must remain above its threshold until the TPS40428 device is turned off.

#### 7.3.12 PWM Signal

The PWM signal has three voltage levels:

- High level to turn on only the high-side MOSFET

- Level level to turn on only the low-side MOSFET

- Tri-state level to turn off both high-side and low-side MOSFETs.