# 低 lo, 双同步降压稳压器

查询样品: TPS43350-Q1, TPS43351-Q1

#### 特性

- 符合汽车应用要求

- 具有下列结果的 AEC-Q100 测试指南:

- 器件温度 1 级: -40°C 至 125°C 的环境运行温度范围

- 器件人体模型 (HBM) 静电放电 (ESD) 分类等级 H2

- 器件 HBM 充电器件模型 (CDM) 分类等级 C2

- 两个同步降压控制器

- 输入电压范围最高 40V, (瞬态电压高达 60V)

- 低功耗模式 I<sub>Q</sub>: 30μA(一个降压稳压器打 开),35μA(两个降压稳压器打开)

- 低关断电流 I<sub>sh</sub><4µA</li>

- 降压输出范围 0.9V 至 11V

- 可编程频率和外部同步范围为 150kHz 至 600kHz

- 独立的使能输入 (ENA, ENB)

- 频率展频 (TPS43351-Q1)

- 轻负载时的,可选强制连续模式或自动低功耗模式

- 感应电阻器或者电感器 DCR 感测

- 降压通道之间的异相切换

- 峰值栅极驱动电流 1.5A

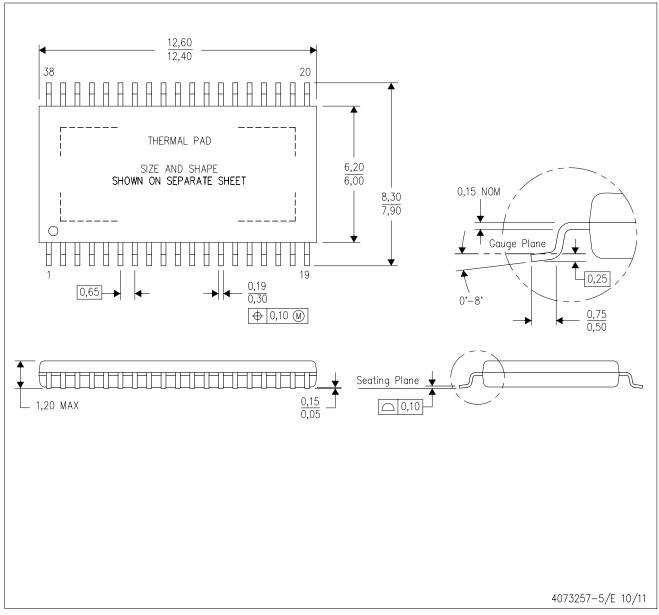

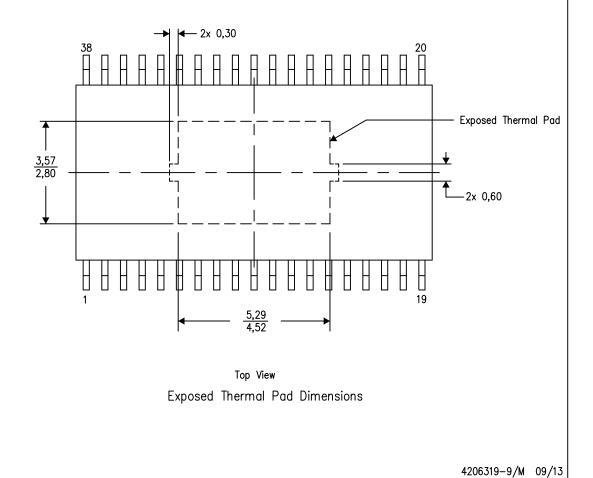

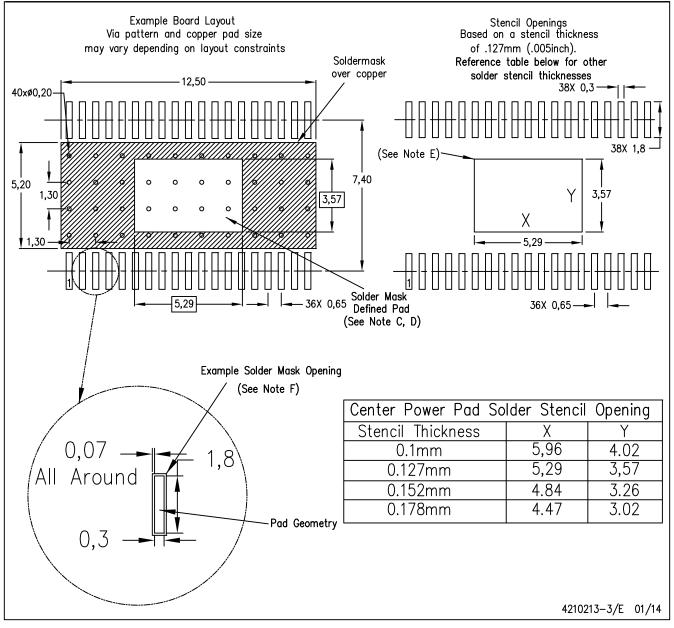

- 耐热增强型,38 引脚散热薄型小外形尺寸封装 (DAP) PowerPAD™ 封装

#### 应用范围

- 车载信息娱乐、导航、和仪表板系统

- 工业或汽车用多轨 DC 配电系统和电子控制单元

#### 说明

TPS43350-Q1 和 TPS43351-Q1 包含两个设计用于恶劣环境中车载应用的电流模式同步降压控制器。 此器件非常适合于要求低静态电流的多轨系统中,这是因为它们在轻负载时运行在低功耗模式中(流耗只有 30μA)。 此器件提供诸如过热保护、软启动、和过流保护等保护特性。 在稳压器输出的短路情况下,电流折返特性被激活,这样可限制流经金属氧化物半导体场效应晶体管 (MOSFET) (用于控制功率耗散)的电流。 两个独立软启动输入可在启动期间独立实现输出电压缓升。

开关频率的可编程范围介于 150kHz 至 600kHz 之间,即器件可同步至的外部时钟的频率。 此外,TPS43351-Q1 提供跳频展频操作。

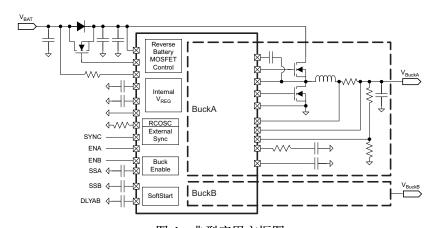

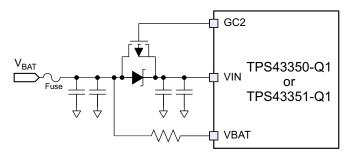

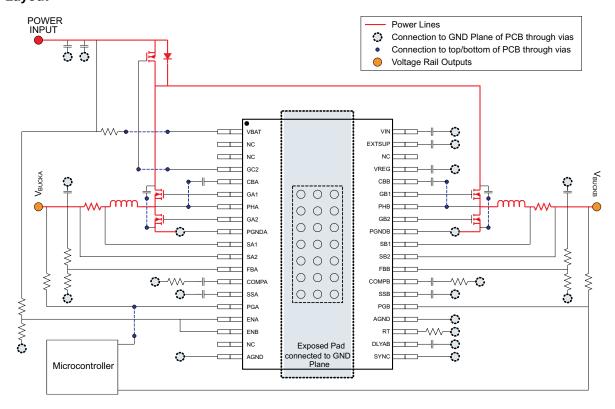

图 1. 典型应用方框图

A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### PACKAGE AND ORDERING INFORMATION

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

#### ABSOLUTE MAXIMUM RATINGS(1)

|                                 |                                                             |                                               | MIN  | MAX | UNIT |  |

|---------------------------------|-------------------------------------------------------------|-----------------------------------------------|------|-----|------|--|

| Voltage                         | Input voltage: VBAT                                         |                                               | -0.3 | 60  | V    |  |

|                                 | Ground: PGNDA-AGND, PGNDB-                                  | AGND                                          | -0.3 | 0.3 | V    |  |

|                                 | Enable inputs: ENA, ENB                                     |                                               | -0.3 | 60  | V    |  |

|                                 | Bootstrap inputs: CBA, CBB                                  |                                               | -0.3 | 68  | V    |  |

|                                 | Bootstrap inputs: CBA-PHA, CBB-                             | PHB                                           | -0.3 | 8.8 | V    |  |

|                                 | Phase inputs: PHA, PHB                                      |                                               | -0.7 | 60  | V    |  |

|                                 | Phase inputs: PHA, PHB (for 150 n                           | s)                                            | -1   |     | V    |  |

|                                 | Feedback inputs: FBA, FBB                                   |                                               | -0.3 | 13  | V    |  |

| Voltage<br>(Buck function:      | Error amplifier outputs: COMPA, CO                          | OMPB                                          | -0.3 | 13  | V    |  |

| BuckA and BuckB)                | High-side MOSFET driver: GA1-PH                             | IA, GB1–PHB                                   | -0.3 | 8.8 | V    |  |

| •                               | Low-side MOSFET drivers: GA2-P                              | Low-side MOSFET drivers: GA2-PGNDA, GB2-PGNDB |      |     | V    |  |

|                                 | Current-sense voltage: SA1, SA2, SB1, SB2                   |                                               |      | 13  | V    |  |

|                                 | Soft start: SSA, SSB                                        |                                               |      | 13  | V    |  |

|                                 | Power-good output: PGA, PGB                                 |                                               | -0.3 | 13  | V    |  |

|                                 | Power-good delay: DLYAB                                     | Power-good delay: DLYAB                       |      |     | V    |  |

|                                 | Switching-frequency timing resistor                         | -0.3                                          | 13   | V   |      |  |

|                                 | SYNC, EXTSUP                                                | -0.3                                          | 13   | V   |      |  |

| Voltage                         | P-channel MOSFET driver: GC2                                |                                               |      | 60  | V    |  |

| (PMOS driver)                   | P-channel MOSFET driver: -GC2                               |                                               |      | 8.8 | V    |  |

|                                 | Gate-driver supply: VREG                                    |                                               |      | 8.8 | V    |  |

|                                 | Junction temperature: T <sub>J</sub>                        |                                               | -40  | 150 | °C   |  |

| Temperature                     | Operating temperature: T <sub>A</sub>                       |                                               | -40  | 125 | °C   |  |

|                                 | Storage temperature: T <sub>stg</sub>                       |                                               |      | 165 | °C   |  |

|                                 | Human-body model (HBM) AEC-<br>Q100 Classification Level H2 |                                               | ±2   |     | kV   |  |

|                                 |                                                             | FBA, FBB, RT, DLYAB                           | ±400 |     |      |  |

| Electrostatic discharge ratings | Charged-device model (CDM) AEC-Q100 Classification Level C2 | VBAT, SYNC,                                   | ±750 |     |      |  |

| uistriarge ratiligs             | 2 100 Glacomodulon Edvoi 62                                 | All other pins                                | ±500 |     | V    |  |

|                                 | Machina madel (MM)                                          | PGA, PGB                                      | ±150 |     |      |  |

|                                 | Machine model (MM)                                          | All other pins                                | ±200 |     |      |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to AGND, unless otherwise stated.

#### THERMAL INFORMATION

|                  |                                                             | TPS4335x-Q1 |       |

|------------------|-------------------------------------------------------------|-------------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                               | DAP         | UNIT  |

|                  |                                                             | 38 PINS     |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance (2)                  | 27.3        |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 19.6        |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance (4)                    | 15.9        | 90.00 |

| ΨЈТ              | Junction-to-top characterization parameter (5)              | 0.24        | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter <sup>(6)</sup> | 6.6         |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance (7)            | 1.2         |       |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

#### RECOMMENDED OPERATING CONDITIONS

|                 |                                           | MIN  | MAX | UNIT |

|-----------------|-------------------------------------------|------|-----|------|

|                 | Input voltage: , VBAT                     | 4    | 40  | V    |

|                 | Enable inputs: ENA, ENB                   | 0    | 40  | V    |

| Buck function:  | Boot inputs: CBA, CBB                     | 4    | 48  | V    |

| BuckA and BuckB | Phase inputs: PHA, PHB                    | -0.6 | 40  | V    |

| voltage         | Current-sense voltage: SA1, SA2, SB1, SB2 | 0    | 11  | V    |

|                 | Power-good output: PGA, PGB               | 0    | 11  | V    |

|                 | SYNC, EXTSUP                              | 0    | 9   | V    |

|                 | Operating temperature: T <sub>A</sub>     | -40  | 125 | °C   |

#### DC ELECTRICAL CHARACTERISTICS

$V_{IN} = 8 \text{ V to } 18 \text{ V}, T_{I} = -40 ^{\circ}\text{C} \text{ to } 150 ^{\circ}\text{C} \text{ (unless otherwise noted)}$

| NO. |                         | PARAMETER                                                   | TEST CONDITIONS                                                                               | MIN          | TYP    | MAX         | UNIT |

|-----|-------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------|--------|-------------|------|

| 1.0 | Input Supply            | /                                                           | 1                                                                                             |              |        |             |      |

| 1.1 | V <sub>Bat</sub>        | Supply voltage                                              | After initial start-up, condition is satisfied.                                               | 4            |        | 40          | V    |

|     |                         | Input voltage required for device on initial start-up       |                                                                                               | 6.5          |        | 40          | ٧    |

| 1.2 | V <sub>IN</sub>         | Buck regulator operating range after initial start-up       |                                                                                               | 4            |        | 40          | V    |

| 1.3 | V                       | Buck undervoltage lockout                                   | $V_{\rm IN}$ falling. After a reset, initial start-up conditions may apply. (1)               | 3.5          | 3.6    | 3.8         | V    |

| 1.3 | V <sub>IN UV</sub>      | Buck undervoltage lockout                                   | $V_{\text{IN}}$ rising. After a reset, initial start-up conditions may apply. $^{(1)}$        |              | 3.8    | 4           | V    |

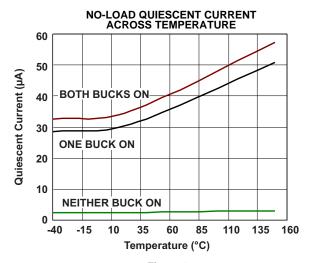

| 1.5 | I <sub>q_LPM</sub> _    | LPM quiescent current:                                      | V <sub>IN</sub> = 13 V, BuckA: LPM, BuckB: off V <sub>IN</sub> = 13 V, BuckB: LPM, BuckA: off |              | 30     | 40          | μΑ   |

|     | 4_2                     | $T_A = 25^{\circ}C^{(2)}$                                   | V <sub>IN</sub> = 13 V, BuckA, B: LPM                                                         |              | 35     | 45          | μA   |

|     |                         |                                                             | V <sub>IN</sub> = 13 V, BuckA: LPM, BuckB: off                                                |              |        |             |      |

| 1.6 | I <sub>q_LPM</sub>      | LPM quiescent current:                                      | V <sub>IN</sub> = 13 V, BuckB: LPM, BuckA: off                                                |              | 40     | 50          | μΑ   |

|     | q_LFIVI                 | $T_A = 125^{\circ}C^{(2)}$                                  | V <sub>IN</sub> = 13 V, BuckA, B: LPM                                                         |              | 45     | 55          | μA   |

|     |                         |                                                             | Normal operation, SYNC = High                                                                 |              | 70     | 33          | μ, τ |

|     |                         | Ouise sent surrect:                                         | V <sub>IN</sub> = 13 V, BuckA: CCM, BuckB: off                                                |              | 4.85   | 5.3         | mA   |

| 1.7 | $I_{q\_NRM}$            | Quiescent current:<br>$T_A = 25^{\circ}C^{(2)}$             | V <sub>IN</sub> = 13 V, BuckA: CCM, BuckA: off                                                |              | 4.00   | 5.5         | IIIA |

|     |                         |                                                             | V <sub>IN</sub> = 13 V, BuckA, B: CCM                                                         |              | 7      | 7.6         | mA   |

|     |                         |                                                             | Normal operation, SYNC = High                                                                 |              | '      | 7.0         | ША   |

|     |                         |                                                             | 1 ,                                                                                           |              | F      |             | A    |

| 1.8 | I <sub>q_NRM</sub>      | Quiescent current:<br>T <sub>A</sub> = 125°C <sup>(2)</sup> | V <sub>IN</sub> = 13 V, BuckA: CCM, BuckB: off                                                |              | 5      | 5.5         | mA   |

|     |                         | 1 <sub>A</sub> = 125 0                                      | V <sub>IN</sub> = 13 V, BuckB: CCM, BuckA: off                                                |              | 7.5    | 0           |      |

| 4.0 |                         |                                                             | V <sub>IN</sub> = 13 V, BuckA, B: CCM                                                         |              | 7.5    | 8           | mA   |

| 1.9 | I <sub>BAT_sh</sub>     | Shutdown current                                            | BuckA, B: off, V <sub>BAT</sub> = 13 V                                                        |              | 2.5    | 4           | μA   |

| 2.0 | input voitag            | e - Overvoltage Lockout                                     | \(\lambda_{}\)                                                                                | 45           | 40     | 47          |      |

| 2.1 | V <sub>OVLO</sub>       | Overvoltage shutdown                                        | V <sub>IN</sub> rising                                                                        | 45           | 46     | 47          | V    |

|     |                         |                                                             | V <sub>IN</sub> falling                                                                       | 43           | 44     | 45          | V    |

| 2.2 | OVLO <sub>Hys</sub>     | Hysteresis                                                  |                                                                                               | 1            | 2      | 3           | V    |

| 2.3 | OVLO <sub>filter</sub>  | Filter time                                                 |                                                                                               |              | 5      |             | μs   |

|     | Gate Driver             |                                                             |                                                                                               |              |        |             |      |

| 3.1 | r <sub>DS(on)</sub>     | PMOS OFF                                                    |                                                                                               |              | 10     | 20          | Ω    |

| 3.2 | I <sub>PMOS_ON</sub>    | Gate current                                                | V <sub>IN</sub> = 13.5 V, V <sub>GS</sub> = -5 V                                              | 10           |        |             | mA   |

| 3.3 | t <sub>delay_ON</sub>   | Turnon delay                                                | C = 10 nF                                                                                     |              | 5      | 10          | μs   |

| 4.0 | Buck Contro             | ollers                                                      |                                                                                               |              |        | г           |      |

| 4.1 | V <sub>BuckA/B</sub>    | Adjustable output voltage range                             |                                                                                               | 0.9          |        | 11          | V    |

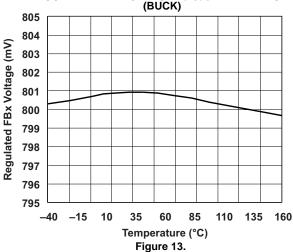

| 4.2 | V <sub>REF, NRM</sub>   | Internal reference voltage and tolerance in normal mode     | Measure FBX pin                                                                               | 0.792<br>-1% | 0.8    | 0.808       | V    |

| 4.3 | V <sub>REF, LPM</sub>   | Internal reference voltage and tolerance in low-power mode  | Measure FBX pin                                                                               | 0.784<br>-2% | 0.8    | 0.816<br>2% | V    |

| 4.4 |                         | V sense for forward current limit in CCM                    | FBx = 0.75 V (low duty cycles)                                                                | 60           | 75     | 90          | mV   |

| 4.5 | V <sub>SENSE</sub>      | V sense for reverse current limit in CCM                    | FBx = 1 V                                                                                     | -65          | -37.5  | -23         | mV   |

| 4.6 | V <sub>I-Foldback</sub> | V sense for output short                                    | FBx = 0 V                                                                                     | 17           | 32.5   | 48          | mV   |

| 4.7 | t <sub>dead</sub>       | Shoot-through delay, blanking time                          |                                                                                               |              | 100    |             | ns   |

|     |                         | High-side minimum on-time                                   |                                                                                               |              | 100    |             | ns   |

| 4.8 | DC <sub>NRM</sub>       | Maximum duty cycle (digitally controlled)                   |                                                                                               |              | 98.75% |             |      |

| 4.9 | DC <sub>LPM</sub>       | Duty cycle LPM                                              |                                                                                               |              |        | 80%         |      |

<sup>(1)</sup> If V<sub>BAT</sub> and V<sub>REG</sub> remain adequate, the buck can continue to operate if V<sub>IN</sub> is > 3.8 V.

(2) Quiescent current specification is non-switching current consumption without including the current in the external feedback resistor divider.

## **DC ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN} = 8 \text{ V}$  to 18 V,  $T_{J} = -40^{\circ}\text{C}$  to 150°C (unless otherwise noted)

| NO.  |                                | PARAMETER                                                                | TEST CONDITIONS                                                             | MIN  | TYP        | MAX  | UNIT |

|------|--------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------|------|------------|------|------|

| 4.40 | I <sub>LPM_Entry</sub>         | LPM entry threshold load current as fraction of maximum set load current | The exit threshold is specified to be always higher                         |      | 1%         | (3)  |      |

| 4.10 | I <sub>LPM_Exit</sub>          | LPM exit threshold load current as fraction of maximum set load current  | than entry threshold                                                        | (3)  | 10%        |      |      |

|      | High-Side Ext                  | ernal NMOS Gate Drivers for Buck                                         | Controller                                                                  |      |            |      |      |

| 4.11 | I <sub>GX1_peak</sub>          | Gate driver peak current                                                 |                                                                             |      | 1.5        |      | Α    |

| 4.12 | r <sub>DS(on)</sub>            | Source and sink driver                                                   | V <sub>REG</sub> = 5.8 V, I <sub>GX1</sub> current = 200 mA                 |      |            | 2    | Ω    |

|      | Low-Side NM                    | OS Gate Drivers for Buck Controlle                                       | er                                                                          |      |            |      |      |

| 4.13 | I <sub>GX2_peak</sub>          | Gate-driver peak current                                                 |                                                                             |      | 1.5        |      | Α    |

| 4.14 | r <sub>DS(on)</sub>            | Source and sink driver                                                   | V <sub>REG</sub> = 5.8 V, I <sub>GX2</sub> current = 200 mA                 |      |            | 2    | Ω    |

|      | Error Amplifie                 | er (OTA) for Buck Converters                                             |                                                                             |      |            |      |      |

| 4.15 | Gm <sub>BUCK</sub>             | Transconductance                                                         | COMPA, COMPB = 0.8 V,<br>source/sink = 5 μA, test in feedback loop          | 0.72 | 1          | 1.35 | mS   |

| 4.16 | I <sub>PULLUP_FBx</sub>        | Pullup current at FBx pins                                               | FBx = 0 V                                                                   | 50   | 100        | 200  | nA   |

| 5.0  | Digital Inputs                 | ENA, ENB, SYNC                                                           |                                                                             |      |            |      |      |

| 5.1  | V <sub>IH</sub>                | Higher threshold                                                         | V <sub>IN</sub> = 13 V                                                      | 1.7  |            |      | V    |

| 5.2  | V <sub>IL</sub>                | Lower threshold                                                          | V <sub>IN</sub> = 13 V                                                      |      |            | 0.7  | V    |

| 5.3  | R <sub>IH_SYNC</sub>           | Resistance                                                               | V <sub>SYNC</sub> = 5 V                                                     |      | 500        |      | kΩ   |

| 5.5  | I <sub>IL_ENx</sub>            | Pullup current source on ENA,<br>ENB                                     | V <sub>ENx</sub> = 0 V                                                      |      | 0.5        | 2    | μΑ   |

| 6.0  | Switching Par                  | rameters – Buck DC-DC Controllers                                        | 5                                                                           |      |            |      |      |

| 6.1  | f <sub>SW_Buck</sub>           | Buck switching frequency                                                 | RT pin: GND                                                                 | 360  | 400        | 440  | kHz  |

| 6.2  | f <sub>SW_Buck</sub>           | Buck switching frequency                                                 | RT pin: 60-kΩ external resistor                                             | 360  | 400        | 440  | kHz  |

| 6.3  | f <sub>SW_adj</sub>            | Buck adjustable range with external resistor                             | RT pin: external resistor                                                   | 150  |            | 600  | kHz  |

| 6.4  | f <sub>SYNC</sub>              | Buck synchronization range                                               | External clock input                                                        | 150  |            | 600  | kHz  |

| 6.5  | f <sub>SS</sub>                | Spread-spectrum spreading                                                | TPS43351-Q1 only                                                            |      | 5%         |      |      |

| 7.0  | Internal Gate-                 | Driver Supply                                                            | ,                                                                           |      |            |      |      |

|      |                                | Internal regulated supply                                                | V <sub>IN</sub> = 8 V to 18 V, EXTSUP = 0 V, SYNC = High                    | 5.5  | 5.8        | 6.1  | V    |

| 7.1  | V <sub>REG</sub>               | Load regulation                                                          | I <sub>VREG</sub> = 0 mA to 100 mA, EXTSUP = 0 V,<br>SYNC = High            |      | 0.2%       | 1%   |      |

|      |                                | Internal regulated supply                                                | EXTSUP = 8.5 V                                                              | 7.2  | 7.5        | 7.8  | V    |

| 7.2  | V <sub>REG(EXTSUP)</sub>       | Load regulation                                                          | I <sub>EXTSUP</sub> = 0 mA to 125 mA, SYNC = High<br>EXTSUP = 8.5 V to 13 V |      | 0.2%       | 1%   |      |

| 7.3  | V <sub>EXTSUP_th</sub>         | EXTSUP switch-over voltage threshold                                     | I <sub>VREG</sub> = 0 mA to 100 mA ,<br>EXTSUP ramping positive             | 4.4  | 4.6        | 4.8  | V    |

| 7.4  | V <sub>EXTSUP-Hys</sub>        | EXTSUP switch-over hysteresis                                            |                                                                             | 150  |            | 250  | mV   |

| 7.5  | I <sub>REG-Limit</sub>         | Current limit on VREG                                                    | EXTSUP = 0 V, normal mode as well as LPM                                    | 100  |            | 400  | mA   |

| 7.6  | I <sub>REG_EXTSUP</sub> -Limit | Current limit on VREG when using EXTSUP                                  | I <sub>VREG</sub> = 0 mA to 100 mA,<br>EXTSUP = 8.5 V, SYNC = High          | 125  |            | 400  | mA   |

| 8.0  | Soft Start                     |                                                                          |                                                                             |      |            |      |      |

| 8.1  | I <sub>SSx</sub>               | Soft-start source current                                                | SSA and SSB = 0 V                                                           | 0.75 | 1          | 1.25 | μA   |

| 9.0  | Oscillator (RT                 | )                                                                        |                                                                             |      |            |      |      |

| 9.1  | $V_{RT}$                       | Oscillator reference voltage                                             |                                                                             |      | 1.2        |      | V    |

| 10.0 | Power-Good /                   | Delay                                                                    |                                                                             |      |            |      |      |

| 10.1 | PG <sub>pullup</sub>           | Pullup for A and B to Sx2                                                |                                                                             |      | 50         |      | kΩ   |

| 10.2 | PG <sub>th1</sub>              | Power-good threshold                                                     | FBx falling                                                                 | -5%  | -7%        | -9%  |      |

| 10.3 | PG <sub>hys</sub>              | Hysteresis                                                               |                                                                             |      | 2%         |      |      |

| 10.4 | PG <sub>drop</sub>             | Voltage drop                                                             | I <sub>PGA</sub> = 5 mA                                                     |      |            | 450  | mV   |

| 10.5 |                                |                                                                          | I <sub>PGA</sub> = 1 mA                                                     |      |            | 100  | mV   |

| 10.6 | PG <sub>leak</sub>             | Leakage                                                                  | VSx2 = VPGx = 13 V                                                          |      | · <u> </u> | 1    | μΑ   |

<sup>(3)</sup> The exit threshold specification is to be always higher than the entry threshold.

## DC ELECTRICAL CHARACTERISTICS (continued)

$V_{IN} = 8 \text{ V to } 18 \text{ V}, T_J = -40 ^{\circ}\text{C to } 150 ^{\circ}\text{C} \text{ (unless otherwise noted)}$

| NO.   | PARAMETER              |                                                                 | TEST CONDITIONS                                                     | MIN | TYP | MAX | UNIT |

|-------|------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| 10.7  | t <sub>deglitch</sub>  | Power-good deglitch time                                        |                                                                     | 2   |     | 16  | μs   |

| 10.8  | t <sub>delay</sub>     | Reset delay                                                     | External capacitor = 1 nF<br>V <sub>BuckX</sub> < PG <sub>th1</sub> |     | 1   |     | ms   |

| 10.9  | t <sub>delay_fix</sub> | Fixed reset delay                                               | No external capacitor, pin open                                     |     | 20  | 50  | μs   |

| 10.10 | I <sub>OH</sub>        | Activate current source (current to charge external capacitor)  |                                                                     | 30  | 40  | 50  | μΑ   |

| 10.11 | I <sub>IL</sub>        | Activate current sink (current to discharge external capacitor) |                                                                     | 30  | 40  | 50  | μΑ   |

| 11.0  | Overtempera            | ture Protection                                                 |                                                                     |     |     |     |      |

| 11.1  | T <sub>shutdown</sub>  | Junction temperature shutdown threshold                         |                                                                     | 150 | 165 |     | °C   |

| 11.2  | T <sub>hys</sub>       | Junction temperature hysteresis                                 |                                                                     |     | 15  |     | °C   |

#### **DEVICE INFORMATION**

#### **PIN FUNCTIONS**

| NAME   | NO.       | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                          |

|--------|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND   | 19,<br>23 | 0   | Analog ground reference                                                                                                                                                                                                                                                                                                              |

| СВА    | 5         | I   | A capacitor on this pin acts as the voltage supply for the high-side N-channel MOSFET gate-drive circuitry in buck controller BuckA. When the buck is in a dropout condition, the device automatically reduces the duty cycle of the high-side MOSFET to approximately 95% on every fourth cycle to allow the capacitor to recharge. |

| СВВ    | 34        | 1   | A capacitor on this pin acts as the voltage supply for the high-side N-channel MOSFET gate-drive circuitry in buck controller BuckB. When the buck is in a dropout condition, the device automatically reduces the duty cycle of the high-side MOSFET to approximately 95% on every fourth cycle to allow the capacitor to recharge. |

| COMPA  | 13        | 0   | Error amplifier output of BuckA and compensation node for voltage-loop stability. The voltage at this node sets the target for the peak current through the inductor of BuckA. Clamping his voltage on the upper and lower ends provides current-limit protection for the external MOSFETs.                                          |

| СОМРВ  | 26        | 0   | Error amplifier output of BuckB and compensation node for voltage-loop stability. The voltage at this node sets the target for the peak current through the inductor of BuckB. Clamping his voltage on the upper and lower ends provides current-limit protection for the external MOSFETs.                                          |

| DLYAB  | 21        | 0   | The capacitor at the DLYAB pin sets the power-good delay interval used to de-glitch the outputs of the power-good comparators. Leaving this pin open sets the power-good delay to an internal default value of 20 µs typical.                                                                                                        |

| ENA    | 16        | I   | Enable input for BuckA (active-high with an internal pullup current source). An input voltage higher than 1.7 V enables the controller, whereas an input voltage lower than 0.7 V disables the controller. When both ENA and ENB are low, the device shuts down and consumes less than 4 µA of current.                              |

| ENB    | 17        | 1   | Enable input for BuckB (active-high with an internal pullup current source). An input voltage higher than 1.7 V enables the controller, whereas an input voltage lower than 0.7 V disables the controller. When both ENA and ENB are low, the device shuts down and consumes less than 4 µA of current.                              |

| EXTSUP | 37        | I   | One can use EXTSUP to supply the VREG regulator from one of the TPS43350-Q1 or TPS43351-Q1 buck regulator rails to reduce power dissipation in cases where there is an expectation of high VIN. If EXTSUP is unused, leave the pin open without a capacitor installed.                                                               |

| FBA    | 12        | I   | Feedback voltage pin for BuckA. The buck controller regulates the feedback voltage to the internal reference of 0.8 V. A suitable resistor divider network between the buck output and the feedback pin sets the desired output voltage.                                                                                             |

| FBB    | 27        | I   | Feedback voltage pin for BuckB. The buck controller regulates the feedback voltage to the internal reference of 0.8 V. A suitable resistor divider network between the buck output and the feedback pin sets the desired output voltage.                                                                                             |

## **PIN FUNCTIONS (continued)**

| NAME  | NO.                | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GA1   | 6                  | 0   | This output can drive the external high-side N-channel MOSFET for buck regulator BuckA. The output provides high peak currents to drive capacitive loads. The gate-drive reference is to a floating ground provided by PHA that has a voltage swing provided by CBA.                                                                                                                                                                                                                                                                                                                                              |

| GA2   | 8                  | 0   | This output can drive the external low-side N-channel MOSFET for buck regulator BuckA. The output provides high peak currents to drive capacitive loads. VREG provides the voltage swing on this pin.                                                                                                                                                                                                                                                                                                                                                                                                             |

| GB1   | 33                 | 0   | This output can drive the external high-side N-channel MOSFET for buck regulator BuckB. The output provides high peak currents to drive capacitive loads. The gate drive reference is to a floating ground provided by PHB that has a voltage swing provided by CBB.                                                                                                                                                                                                                                                                                                                                              |

| GB2   | 31                 | 0   | This output can drive the external low-side N-channel MOSFET for buck regulator BuckB. The output provides high peak currents to drive capacitive loads. VREG provides the voltage swing on this pin.                                                                                                                                                                                                                                                                                                                                                                                                             |

| GC2   | 4                  | 0   | This pin makes a floating output drive available to control the external P-channel MOSFET. This MOSFET can bypass the boost rectifier diode or a reverse-protection diode when the boost is not switching or if boost is disabled, and thus reduce power losses.                                                                                                                                                                                                                                                                                                                                                  |

| NC    | 2, 3,<br>18,<br>36 | _   | No connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PGNDA | 9                  | 0   | Power ground connection to the source of the low-side N-channel MOSFETs of BuckA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PGNDB | 30                 | 0   | Power ground connection to the source of the low-side N-channel MOSFETs of BuckB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PGA   | 15                 | 0   | Open-drain power-good indicator pin for BuckA. An internal power-good comparator monitors the voltage at the feedback pin and pulls this output low when the output voltage falls below 93% of the set value.                                                                                                                                                                                                                                                                                                                                                                                                     |

| PGB   | 24                 | 0   | Open-drain power-good indicator pin for BuckB. An internal power-good comparator monitors the voltage at the feedback pin and pulls this output low when the output voltage falls below 93% of the set value.                                                                                                                                                                                                                                                                                                                                                                                                     |

| PHA   | 7                  | 0   | Switching terminal of buck regulator BuckA, providing a floating ground reference for the high-side MOSFET gate-driver circuitry and used to sense current reversal in the inductor when discontinuous-mode operation is desired.                                                                                                                                                                                                                                                                                                                                                                                 |

| PHB   | 32                 | 0   | Switching terminal of buck regulator BuckB, providing a floating ground reference for the high-side MOSFET gate-driver circuitry and used to sense current reversal in the inductor when discontinuous-mode operation is desired.                                                                                                                                                                                                                                                                                                                                                                                 |

| RT    | 22                 | 0   | Connecting a resistor to ground on this pin sets the operational switching frequency of the buck and boost controllers. A short circuit to ground on this pin defaults operation to 400 kHz for the buck controllers and 200 kHz for the boost controller.                                                                                                                                                                                                                                                                                                                                                        |

| SA1   | 10                 | I   | High-impedance differential-voltage inputs from the current-sense element (sense resistor or inductor DCR) for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SA2   | 11                 | I   | each buck controller. Choose the current-sense element to set the maximum current through the inductor based on the current-limit threshold (subject to tolerances) and considering the typical characteristics across duty cycle and V <sub>IN</sub> . (SA1 positive node, SA2 negative node).                                                                                                                                                                                                                                                                                                                   |

| SB1   | 29                 | I   | High-impedance differential voltage inputs from the current-sense element (sense resistor or inductor DCR) for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SB2   | 28                 | I   | each buck controller. Choose the current-sense element to set the maximum current through the inductor based on the current-limit threshold (subject to tolerances) and considering the typical characteristics across duty cycle and V <sub>IN</sub> . (SB1 positive node, SB2 negative node).                                                                                                                                                                                                                                                                                                                   |

| SSA   | 14                 | 0   | Soft-start or tracking input for buck controller BuckA. The buck controller regulates the FBA voltage to the lower of 0.8 V or the SSA pin voltage. An internal pullup current source of 1 µA is present at the pin, and an appropriate capacitor connected here sets the soft-start ramp interval. Alternatively, a resistor divider connected to another supply can provide a tracking input to this pin.                                                                                                                                                                                                       |

| SSB   | 25                 | 0   | Soft-start or tracking input for buck controller BuckB. The buck controller regulates the FBB voltage to the lower of 0.8 V or the SSB pin voltage. An internal pullup current source of 1 $\mu$ A is present at the pin, and an appropriate capacitor connected here sets the soft-start ramp interval. Alternatively, a resistor divider connected to another supply can provide a tracking input to this pin.                                                                                                                                                                                                  |

| SYNC  | 20                 | I   | If an external clock is present on this pin, the device detects it, and the internal PLL locks on to the external clock. This overrides the internal oscillator frequency. The device can synchronize to frequencies from 150 kHz to 600 kHz. A high logic level on this pin ensures forced continuous-mode operation of the buck controllers and inhibits transition to low-power mode. An open or low allows discontinuous-mode operation and entry into low-power mode at light loads. On the TPS43351-Q1, a high level enables frequency-hopping spread spectrum, whereas an open or a low level disables it. |

| VBAT  | 1                  | I   | Supply pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VIN   | 38                 | I   | Main input pin. This is the buck controller input pin. Additionally, it powers the internal control circuits of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VREG  | 35                 | 0   | The device requires an external capacitor on this pin to provide a regulated supply for the gate drivers of the buck and boost controllers. TI recommends capacitance on the order of 4.7 $\mu$ F. The regulator obtain its power from either or EXTSUP. This pin has current-limit protection; do not use it to drive any other loads.                                                                                                                                                                                                                                                                           |

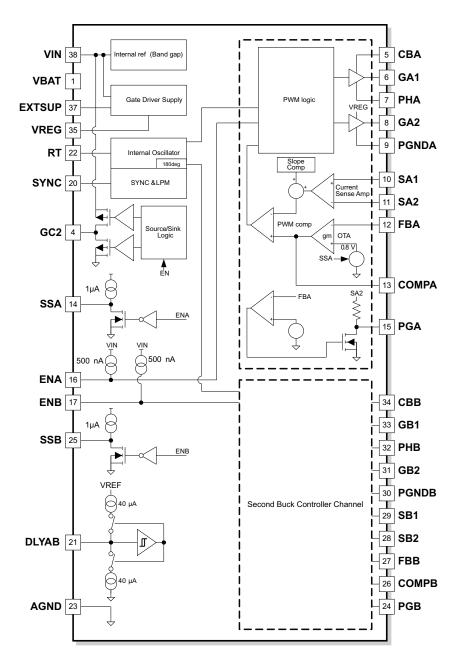

Figure 2. Functional Block Diagram

# **NSTRUMENTS**

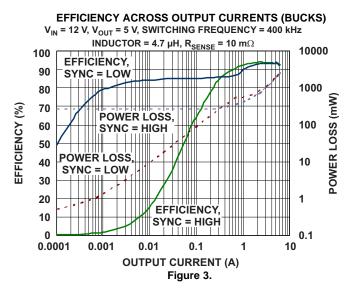

#### TYPICAL CHARACTERISTICS

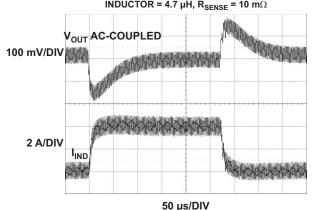

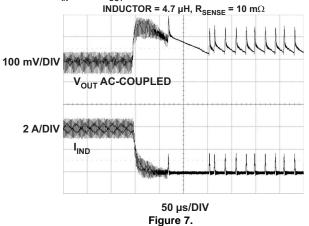

#### **BUCK LOAD STEP: FORCED CONTINUOUS MODE** (0 TO 4 A AT 2.5 A/µs)

$V_{IN}$  = 12 V,  $V_{OUT}$  = 5 V, SWITCHING FREQUENCY = 400 kHz INDUCTOR = 4.7  $\mu$ H, R<sub>SENSE</sub> = 10 m $\Omega$

#### Figure 5.

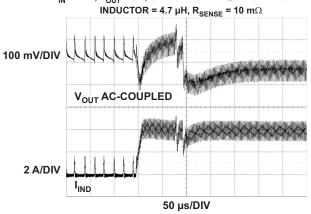

# BUCK LOAD STEP: LOW-POWER-MODE ENTRY 4 A TO 90 mA AT 2.5 A/µs

$V_{IN}$  = 12 V,  $V_{OUT}$  = 5 V, SWITCHING FREQUENCY = 400 kHz

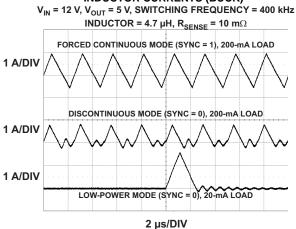

#### **INDUCTOR CURRENTS (BUCK)**

Figure 4.

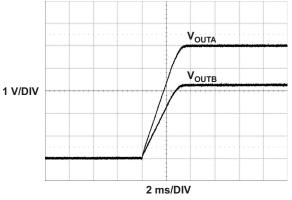

# **SOFT-START OUTPUTS (BUCK)**

Figure 6.

# BUCK LOAD STEP: LOW-POWER-MODE EXIT 90 mA TO 4 A AT 2.5 A/ $\mu s$

12 V, V<sub>OUT</sub> = 5 V, SWITCHING FREQUENCY = 400 kHz

Figure 8.

#### TYPICAL CHARACTERISTICS (continued)

Figure 9.

REGULATED FBx VOLTAGE versus TEMPERATURE (BUCK)

#### **DETAILED DESCRIPTION**

#### **BUCK CONTROLLERS: NORMAL MODE PWM OPERATION**

#### Frequency Selection and External Synchronization

The buck controllers operate using constant-frequency peak-current mode control for optimal transient behavior and ease of component choices. The switching frequency is programmable between 150 kHz and 600 kHz, depending upon the resistor value at the RT pin. A short circuit to ground at this pin sets the default switching frequency to 400 kHz. Using a resistor at RT, one can set another frequency according to the formula:

$$f_{SW} = \frac{X}{RT}$$

(X = 24 k $\Omega \times MHz$ )

$$f_{SW} = 24 \times \frac{10^9}{RT}$$

For example,

600 kHz requires 40 kΩ

150 kHz requires 160 k $\Omega$

It is also possible to synchronize to an external clock at the SYNC pin in the same frequency range of 150 kHz to 600 kHz. The device detects clock pulses at this pin, and an internal PLL locks on to the external clock within the specified range. The device can also detect a loss of clock at this pin, and on detection of this condition, the device sets the switching frequency to the internal oscillator. The two buck controllers operate at identical switching frequencies, 180 degrees out of phase.

#### **Enable Inputs**

Independent enable inputs from the ENA and ENB pins enable the buck controllers. These are high-voltage pins, with a threshold of 1.7 V for the high level, and with direct connection to the battery permissible for self-bias. The low threshold is 0.7 V. Both these pins have internal pullup currents of 0.5  $\mu$ A (typical). As a result, an open circuit on these pins enables the respective buck controllers. But with both buck controllers disabled, the device shuts down and consumes a current less than 4  $\mu$ A.

#### **Feedback Inputs**

The right resistor feedback divider network connected to the FBx (feedback) pins sets the output voltage. Choose this network such that the regulated voltage at the FBx pin equals 0.8 V. The FBx pins have a 100-nA pullup current source as a protection feature in case the pins open up as a result of physical damage.

#### **Soft-Start Inputs**

In order to avoid large inrush currents, the buck controllers have independent programmable soft-start timers. The voltage at the SSx pins acts as the soft-start reference voltage. The 1-µA pullup current available at the SSx pins, in combination with a suitably chosen capacitor, generates a ramp of the desired soft-start speed. After start-up, the pullup current ensures that this node is higher than the internal reference of 0.8 V, which then becomes the reference for the buck controllers. The following equation calculates the soft-start ramp time:

$$C_{SS} = \frac{I_{SS} \times \Delta t}{\Delta V}$$

(Farads)

where,

$I_{SS} = 1 \mu A \text{ (typical)}$

$\Delta V = 0.8 \ V$

$C_{SS}$  is the required capacitor for  $\Delta t$ , the desired soft-start time.

An alternative use of the soft-start pins is as tracking inputs. In this case, connect them to the supply to be tracked via a suitable resistor-divider network.

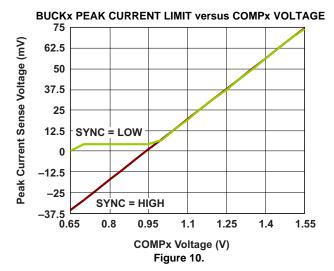

#### **Current-Mode Operation**

Peak-current-mode control regulates the peak current through the inductor to maintain the output voltage at its set value. The error between the feedback voltage at FBx and the internal reference produces a signal at the output of the error amplifier (COMPx) which serves as a target for the peak inductor current. The device senses the current through the inductor as a differential voltage at Sx1–Sx2 and compares voltage with this target during each cycle. A fall or rise in load current produces a rise or fall in voltage at FBx, causing COMPx to fall or rise respectively, thus increasing or decreasing the current through the inductor until the average current matches the load. This process maintains the output voltage in regulation.

The top N-channel MOSFET turns on at the beginning of each clock cycle and stays on until the inductor current reaches its peak value. Once this MOSFET turns off, and after a small delay (shoot-through delay) the lower N-channel MOSFET turns on until the start of the next clock cycle. In dropout operation, the high-side MOSFET stays on continuously. In every fourth clock cycle, there is a limit on the duty cycle of 95% in order to charge the bootstrap capacitor at CBx. This allows a maximum duty cycle of 98.75% for the buck regulators. During dropout, the buck regulator switches at one-fourth of its normal frequency.

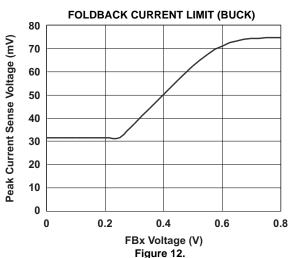

#### **Current Sensing and Current Limit With Foldback**

Clamping of the maximum value of COMPx is such as to limit the maximum current through the inductor to a specified value. When the output of the buck regulator (and hence the feedback value at FBx) falls to a low value due to a short-circuit or overcurrent condition, the clamped voltage at COMPx successively decreases, thus providing current foldback protection. This protects the high-side external MOSFET from excess current (forward-direction current limit).

Similarly, if a fault condition shorts the output to a high voltage and the low-side MOSFET turns fully on, the COMPx node drops low. A clamp is on its lower end as well, in order to limit the maximum current in the low-side MOSFET (reverse-direction current limit).

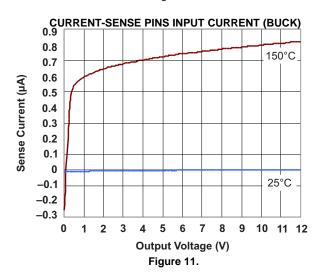

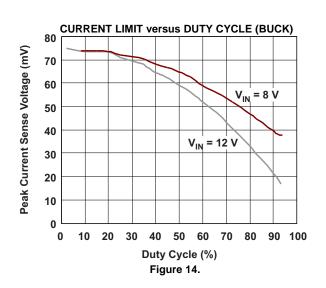

An external resistor senses the current through the inductor. Choose the sense resistor such that the maximum forward peak current in the inductor generates a voltage of 75 mV across the sense pins. This specified value is for low duty cycles only. At typical duty-cycle conditions around 40% (assuming 5-V output and 12-V input), 50 mV is a more reasonable value, considering tolerances and mismatches. The typical characteristics provide a guide for using the correct current-limit sense voltage.

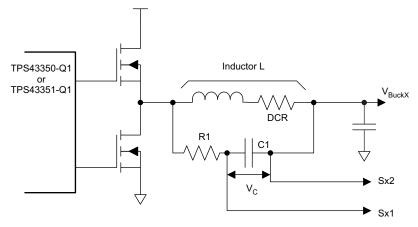

The current-sense pins Sx1 and Sx2 are high-impedance pins with low leakage across the entire output range. This allows DCR current sensing using the dc resistance of the inductor for higher efficiency. Figure 15 shows DCR sensing. Here, the series resistance (DCR) of the inductor is the sense element. Place the filter components close to the device for noise immunity. Remember that while the DCR sensing gives high efficiency, it is inaccurate due to the temperature sensitivity and a wide variation of the parasitic inductor series resistance. Hence, it may often be advantageous to use the more-accurate sense resistor for current sensing.

Figure 15. DCR Sensing Configuration

#### **Slope Compensation**

Optimal slope compensation, which is adaptive to changes in input voltage and duty cycle, allows stable operation at all conditions. For optimal performance of this circuit, choose the inductor and sense resistor according to the following:

$$\frac{L \times f_{SW}}{R_S} = 200$$

where

L is the buck regulator inductor in henries.

R<sub>S</sub> is the sense resistor in ohms.

f<sub>sw</sub> is the buck-regulator switching frequency in hertz.

#### **Power-Good Outputs and Filter Delays**

Each buck controller has an independent power-good comparator monitoring the feedback voltage at the FBx pins and indicating whether the output voltage has fallen below a specified power-good threshold. This threshold has a typical value of 93% of the regulated output voltage. The power-good indicator is available as an opendrain output at the PGx pins. An internal 50-k $\Omega$  pullup resistor to Sx2 is available, or use of an external resistor is possible. Shutdown of a buck controller causes an internal pulldown of the power-good indicator. Connecting the pullup resistor to a rail other than the output of that particular buck channel causes a constant current flow through the resistor when the buck controller is in the powered-down state.

In order to avoid triggering the power-good indicators due to noise or fast transients on the output voltage, the device uses an internal delay circuit for de-glitching. Similarly, when the output voltage returns to its set value after a long negative transient, assertion of the power-good indicator (release of the open-drain pin) occurs after the same delay. Use of this delay can pause the reset of circuits powered from the buck regulator rail. Program the duration of the delay of by using a suitable capacitor at the DLYAB pin according to the equation:

$$\frac{t_{DELAY}}{C_{DLYAB}} = \frac{1 \, ms}{1 \, nF}$$

When the DLYAB pin is open, the delay setting is for a default value of 20 µs typical. The power-good delay timing is common to both the buck rails, but the power-good comparators and indicators function independently.

#### **Light-Load PFM Mode**

An external clock or a high level on the SYNC pin results in forced continuous-mode operation of the bucks. An open or low on the SYNC pin allows the buck controllers to operate in discontinuous mode at light loads by turning off the low-side MOSFET on detection of a zero-crossing in the inductor current.

In discontinuous mode, as the load decreases, the duration when both the high-side and low-side MOSFETs turn off increases (deep discontinuous mode). In case the duration exceeds 60% of the clock period and VBAT > 8 V, the buck controller switches to a low-power operation mode. The design ensures that this typically occurs at 1% of the set full-load current if the inductor and the sense resistor have been chosen appropriately as recommended in the  $Slope\ Compensation$  section.

In low-power PFM mode, the buck monitors the FBx voltage and compares it with the 0.8-V internal reference. Whenever the FBx value falls below the reference, the high-side MOSFET turns on for a pulse duration inversely proportional to the difference – Sx2. At the end of this on-time, the high-side MOSFET turns off and the current in the inductor decays until it becomes zero. The low-side MOSFET does not turn on. The next pulse occurs the next time FBx falls below the reference value. This results in a constant volt-second  $t_{on}$  hysteretic operation with a total device quiescent current consumption of 30  $\mu$ A when a single buck channel is active and 35  $\mu$ A when both channels are active.

As the load increases, the pulses become more and more frequent and move closer to each other until the current in the inductor becomes continuous. At this point, the buck controller returns to normal fixed-frequency current-mode control. Another criterion to exit the low-power mode is when VIN falls low enough to require higher than 80% duty cycle of the high-side MOSFET.

The TPS43350-Q1 and TPS43351-Q1 can support the full current load during low-power mode until the transition to normal mode takes place. The design ensures that exit of the low-power mode occurs at 10% (typical) of full-load current if the selection of inductor and sense resistor is as recommended. Moreover, there is always a hysteresis between the entry and exit thresholds to avoid oscillating between the two modes.

In the event that both buck controllers are active, low-power mode is only possible when both buck controllers have light loads that are low enough for low-power-mode entry.

#### Frequency-Hopping Spread Spectrum (TPS43351-Q1 Only)

The TPS43351-Q1 features a frequency-hopping pseudo-random spectrum spreading architecture. On this device, whenever the SYNC pin is high, the internal oscillator frequency varies from one cycle to the next within a band of ±5% around the value programmed by the resistor at the RT pin. The implementation uses a linear feedback shift register that changes the frequency of the internal oscillator based on a digital code. The shift register is long enough to make the hops pseudo-random in nature and is designed in such a way that the frequency shifts only by one step at each cycle to avoid large jumps in the buck switching frequencies.

SYNC FREQUENCY SPREAD SPECTRUM (FSS) **COMMENTS TERMINAL** Device in forced continuous mode, internal PLL locks into external clock External clock Not active between 150 kHz and 600 kHz. Device can enter discontinuous mode. Automatic LPM entry and exit, Low or open Not active depending on load conditions TPS43350-Q1: FSS not active High Device in forced continuous mode TPS43351-Q1: FSS active

**Table 1. Frequency Hopping Control**

| Table | 2. N | lode | of | Op | eration |

|-------|------|------|----|----|---------|

|-------|------|------|----|----|---------|

| ENABL  | ENABLE AND INHIBIT PINS |      | BUCK CONTROLLED STATUS  | DEVICE STATUS                  | QUIESCENT CURRENT                 |

|--------|-------------------------|------|-------------------------|--------------------------------|-----------------------------------|

| ENA    | ENB                     | SYNC | BUCK CONTROLLER STATUS  | DEVICE STATUS                  | QUIESCENT CORRENT                 |

| Low    | Low                     | Х    | Shutdown                | Shutdown                       | Approximately 4 µA                |

| Law    | High                    | Low  | Duel Danier             | BuckB: LPM enabled             | Approximately 30 µA (light loads) |

| LOW    | Low High                | High | BuckB running           | BuckB: LPM inhibited           | mA range                          |

| Lliada |                         | Low  | BuckA running           | BuckA: LPM enabled             | Approximately 30 µA (light loads) |

| High   | Low                     | High |                         | BuckA: LPM inhibited           | mA range                          |

| Lliada |                         | Low  |                         | BuckA and BuckB: LPM enabled   | Approximately 35 µA (light loads) |

| High   | High                    | High | BuckA and BuckB running | BuckA and BuckB: LPM inhibited | mA range                          |

#### **Gate-Driver Supply (VREG, EXTSUP)**

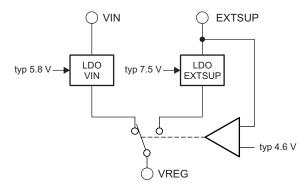

The gate-driver supplies of the buck and boost controllers are from an internal linear regulator whose output (5.8 V typical) is on the VREG pin and requires decoupling with a ceramic capacitor in the range of 3.3  $\mu$ F to 10  $\mu$ F. This pin has internal current-limit protection; do not use it to power any other circuits.

VIN powers the VREG linear regulator by default when the EXTSUP voltage is lower than 4.6 V (typical). In case VIN expected to go to high levels, there can be excessive power dissipation in this regulator, especially at high switching frequencies and when using large external MOSFETs. In this case, it is advantageous to power this regulator from the EXTSUP pin, which can be connected to a supply lower than  $V_{IN}$  but high enough to provide the gate drive. When the voltage on EXTSUP is greater than 4.6 V, the linear regulator automatically switches to EXTSUP as its input, to provide this advantage. Efficiency improvements are possible when using one of the switching regulator rails from the TPS4335x-Q1 or any other voltage available in the system to power EXTSUP. The maximum voltage for application to EXTSUP is 9 V.

Figure 16. Internal Gate-Driver Supply

Using a voltage above 5.8 V (sourced by VIN) for EXTSUP is advantageous, as it provides a large gate drive and hence better on-resistance of the external MOSFETs. When using EXTSUP, always keep the buck rail supplying EXTSUP enabled. Alternatively, if it is necessary to switch off the buck rail supplying EXTSUP, place a diode between the buck rail and EXTSUP. During low-power mode, the EXTSUP functionality is not available. The internal regulator operates as a shunt regulator powered from VIN and has a typical value of 7.5 V. Current-limit protection for VREG is available in low-power mode as well. If EXTSUP is unused, leave the pin open without a capacitor installed.

#### External P-Channel Drive (GC2) and Reverse-Battery Protection

The TPS4335x-Q1 includes a gate driver for an external P-channel MOSFET which can be connected across the reverse-battery diode. This is useful to reduce power losses and the voltage drop over a typical diode. The gate driver provides a swing of 6 V typical below the  $V_{IN}$  voltage in order to drive a P-channel MOSFET.

Figure 17. Reverse-Battery Protection Option

#### Undervoltage Lockout and Overvoltage Protection

The TPS4335x-Q1 starts up at a  $V_{IN}$  voltage of 6.5 V (minimum), required for the internal supply (VREG). Once it has started up, the device operates down to a  $V_{IN}$  voltage of 3.6 V; below this voltage level, the undervoltage lockout disables the device. Note: if  $V_{IN}$  drops,  $V_{REG}$  drops as well; hence, the gate-drive voltage decreases, whereas the digital logic is fully functional. A voltage of 46 V at  $V_{IN}$  triggers the overvoltage comparator, which shuts down the device. In order to prevent transient spikes from shutting down the device, under- and overvoltage protection have filter times of 5  $\mu$ s (typical).

When the voltages return to the normal operating region, the enabled switching regulators start including a new soft-start ramp for the buck regulators.

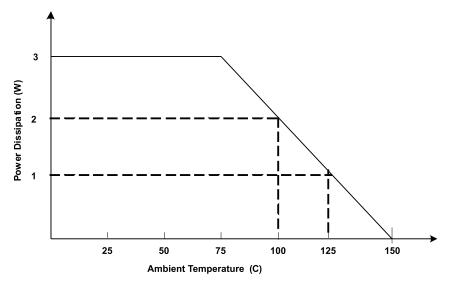

#### **Thermal Protection**

The TPS4335x-Q1 protects itself from overheating using an internal thermal shutdown circuit. If the die temperature exceeds the thermal shutdown threshold of 165°C due to excessive power dissipation (for example, due to fault conditions such as a short circuit at the gate drivers or VREG), the controllers turn off and then restart when the temperature has fallen by 15°C.

#### APPLICATION INFORMATION

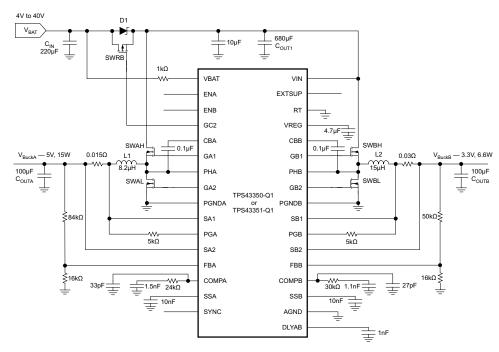

The following example illustrates the design process and component selection for the TPS43350-Q1. Table 3 lists the design-goal parameters.

**Table 3. Application Example**

| PARAMETER                                                             | V <sub>BuckA</sub>                              | V <sub>BuckB</sub>                              |

|-----------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|

| Input voltage                                                         | V <sub>IN</sub> = 6 V to 30 V<br>12 V - typical | V <sub>IN</sub> = 6 V to 30 V<br>12 V - typical |

| Output voltage, V <sub>OUTx</sub>                                     | 5 V                                             | 3.3 V                                           |

| Maximum output current, I <sub>OUTx</sub>                             | 3 A                                             | 2 A                                             |

| Load step output tolerance, $\Delta V_{OUT} + \Delta V_{OUT(Ripple)}$ | ±0.2 V                                          | ±0.12 V                                         |

| Current output load step, ∆I <sub>OUTx</sub>                          | 0.1 A to 3 A                                    | 0.1 A to 2 A                                    |

| Converter switching frequency, f <sub>SW</sub>                        | 400 kHz                                         | 400 kHz                                         |

This is a starting point, and theoretical representation of the values to be used for the application; improving the performance of the device may require further optimization of the derived components.

#### **BuckA Component Selection**

### Minimum ON Time, $t_{ON \ min}$

mum ON Time,

$$t_{ON min}$$

$$t_{ON min} = \frac{V_{OUTA}}{V_{IN max} \times f_{SW}} = \frac{5 \text{ V}}{30 \text{ V} \times 400 \text{ kHz}} = 416 \text{ ns}$$

This is higher than the minimum on-time specified (100 ns typical). Hence, the minimum duty cycle is achievable at this frequency.

17

#### Current-Sense Resistor R<sub>SENSE</sub>

Based on the typical characteristics for  $V_{SENSE}$  limit with  $V_{IN}$  versus duty cycle, the sense limit is approximately 65 mV (at  $V_{IN}$  = 12 V and duty cycle of 5 V / 12 V = 0.416). Allowing for tolerances and ripple currents, choose  $V_{SENSE}$  with a maximum of 50 mV.

$$R_{SENSE} = \frac{50 \text{ mV}}{3 \text{ A}} = 17 \text{ m}\Omega$$

Select 15 m $\Omega$ .

#### Inductor Selection L

As explained in the description of the buck controllers, for optimal slope compensation and loop response, the inductor should be chosen such that:

$$L = K_{FLR} \times \frac{R_{SENSE}}{f_{SW}} = 200 \times \frac{15 \text{ m}\Omega}{400 \text{ kHz}} = 7.5 \text{ }\mu\text{H}$$

K<sub>FLR</sub> = Coil selection constant = 200

Choose a standard value of  $8.2~\mu H$ . For the buck converter, the inductor saturation currents and core should be chosen to sustain the maximum currents.

#### Inductor Ripple Current IRIPPLE

At nominal input voltage of 12 V, this inductor value causes a ripple current of 30% of I<sub>O max</sub> ≈ 1 A.

#### **Output Capacitor Couta**

Select an output capacitance  $C_{OUTA}$  of 100  $\mu F$  with low ESR in the range of 10 m $\Omega$ . This gives  $\Delta V_{O(Ripple)} \approx 15$  mV and  $\Delta V$  drop of  $\approx 180$  mV during a load step, which does not trigger the power-good comparator and is within the required limits.

$$\begin{split} &C_{OUTA} \approx \frac{2 \times \Delta I_{OUTA}}{f_{SW} \times \Delta V_{OUTA}} = \frac{2 \times 2.9 \text{ A}}{400 \text{ kHz} \times 0.2 \text{ V}} = 72.5 \text{ }\mu\text{F} \\ &V_{OUTA(Ripple)} = \frac{I_{OUTA(Ripple)}}{8 \times f_{SW} \times C_{OUTA}} + I_{OUTA(Ripple)} \times \text{ESR} = \frac{1 \text{ A}}{8 \times 400 \text{ kHz} \times 100 \text{ }\mu\text{F}} + 1 \text{ A} \times 10 \text{ }m\Omega = 13.1 \text{ mV} \\ &\Delta V_{OUTA} = \frac{\Delta I_{OUTA}}{4 \times f_{C} \times C_{OUTA}} + \Delta I_{OUTA} \times \text{ESR} = \frac{2.9 \text{ A}}{4 \times 50 \text{ kHz} \times 100 \text{ }\mu\text{F}} + 2.9 \text{ A} \times 10 \text{ }m\Omega = 174 \text{ mV} \end{split}$$

#### Bandwidth of Buck Converter fc

Use the following guidelines to set frequency poles, zeroes and crossover values for a tradeoff between stability and transient response.

- Crossover frequency f<sub>C</sub> between f<sub>SW</sub> / 6 and f<sub>SW</sub> / 10. Assume f<sub>C</sub> = 50 kHz.

- Select the zero f<sub>z</sub> ≈ f<sub>C</sub> / 10.

- Make the second pole f<sub>P2</sub> ≈ f<sub>SW</sub> / 2.

#### Selection of Components for Type II Compensation

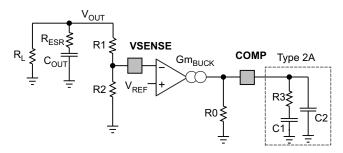

Figure 18. Buck Compensation Components

$$R3 = \frac{2\pi \times f_\text{C} \times V_\text{OUT} \times C_\text{OUTx}}{Gm_\text{BUCK} \times K_\text{CFB} \times V_\text{REF}} = \frac{2\pi \times 50 \text{ kHz} \times 5 \text{ V} \times 100 \mu\text{F}}{Gm_\text{BUCK} \times K_\text{CFB} \times V_\text{REF}} = 23.57 \text{ k}\Omega$$

Use the standard value of R3 = 24 k $\Omega$ ,

Where  $V_{OUT}$  = 5 V,  $C_{OUTx}$  = 100  $\mu$ F,  $Gm_{BUCK}$  = 1 mS,  $V_{REF}$  = 0.8 V