# 4.5-V To 18-V Input Voltage, 3.5-A/3.5-A Dual Synchronous Step-Down Converter With I<sup>2</sup>C

Controlled VID

### **FEATURES**

- 4.5-V to 18-V Wide Input Voltage Range

- I<sup>2</sup>C Controlled 7-Bits VID Programmable

Output Voltage from 0.68 V to 1.95 V with

10-mV Steps for Each Buck; Output Voltage

can also be Set by Resistor Divider

- Programmable Slew-Rate Control for Output-Voltage Transition

- Up to 3.5-A Maximum Continuous Output Current in Buck 1 and Buck 2

- Buck 1 and Buck 2 can be Paralleled to Deliver up to 7-A Current

- I<sup>2</sup>C Compatible Interface With Standard Mode (100 kHz) and Fast Mode (400 kHz)

- I<sup>2</sup>C Read Back Power Good Status and Die Temperature Warning

- Pulse-Skipping Mode to Achieve High Efficiency in Light Loads

- Adjustable Switching Frequency

200 kHz to 1.6 MHz Set by External Resistor

- Dedicated Enable and Soft-Start for Each Buck

- Peak Current-Mode Control With Simple Compensation Circuit

- Cycle-by-Cycle Overcurrent Protection

- 180° Out-of-Phase Operation to Reduce Input Filter and Power Supply Conduced Noise

- Overtemperature Protection

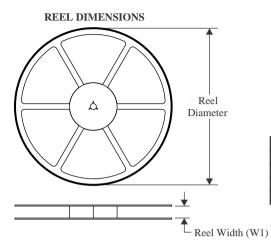

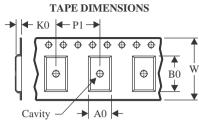

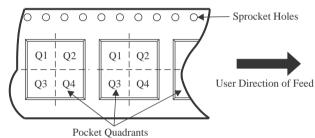

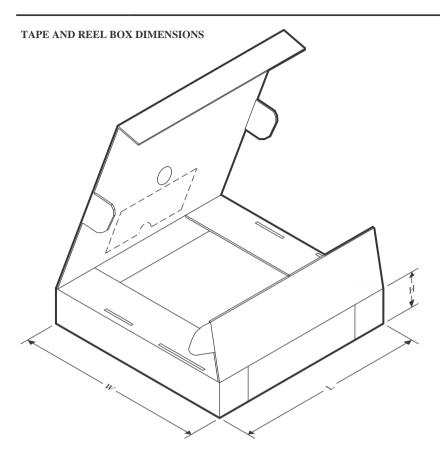

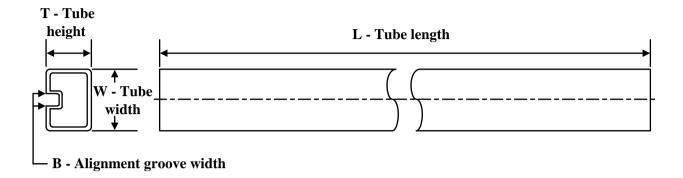

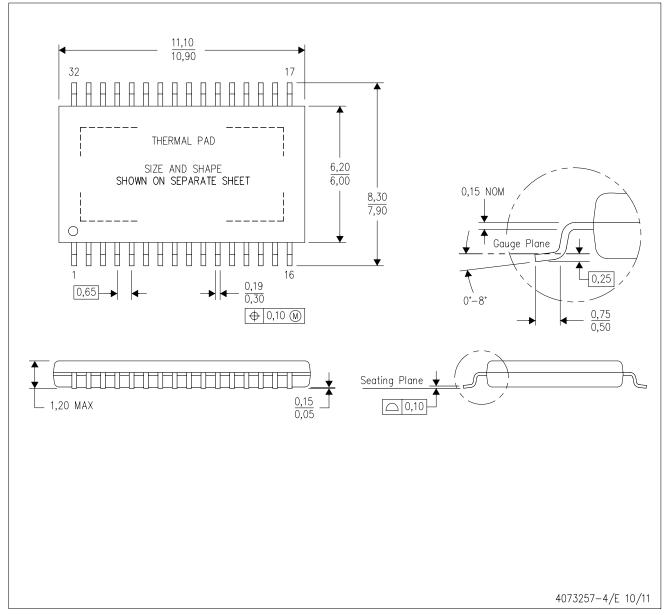

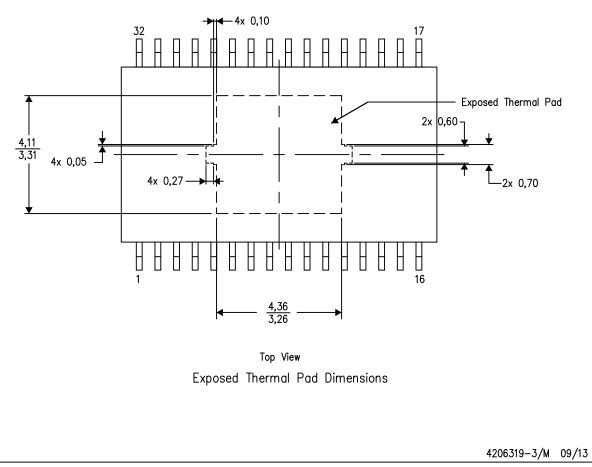

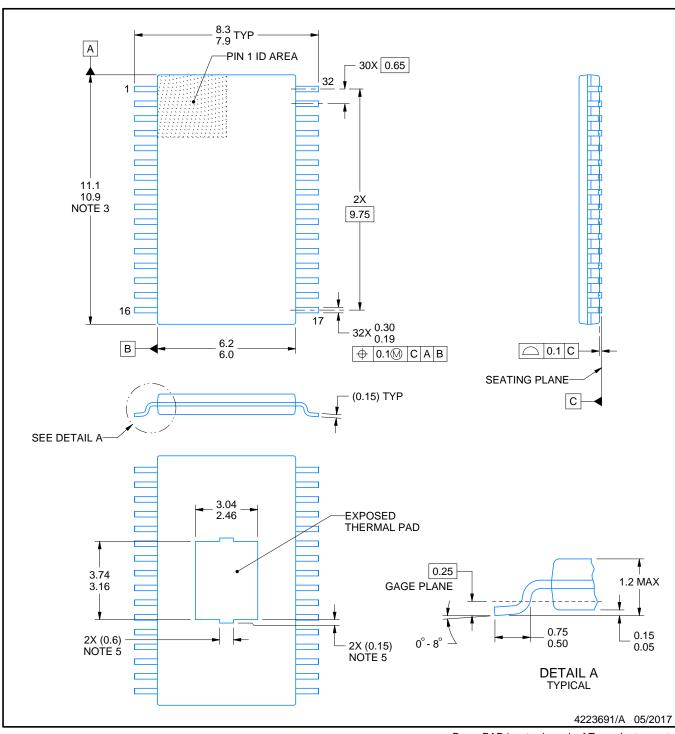

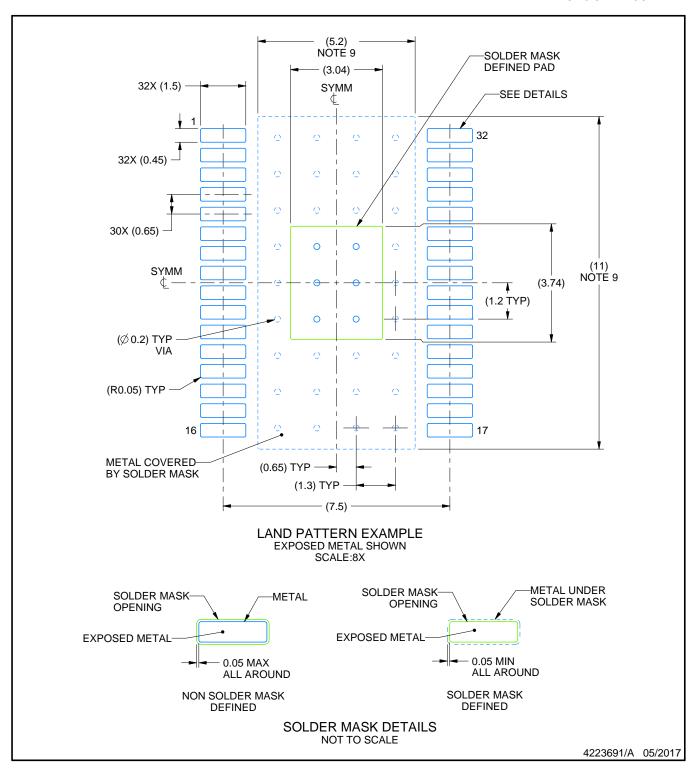

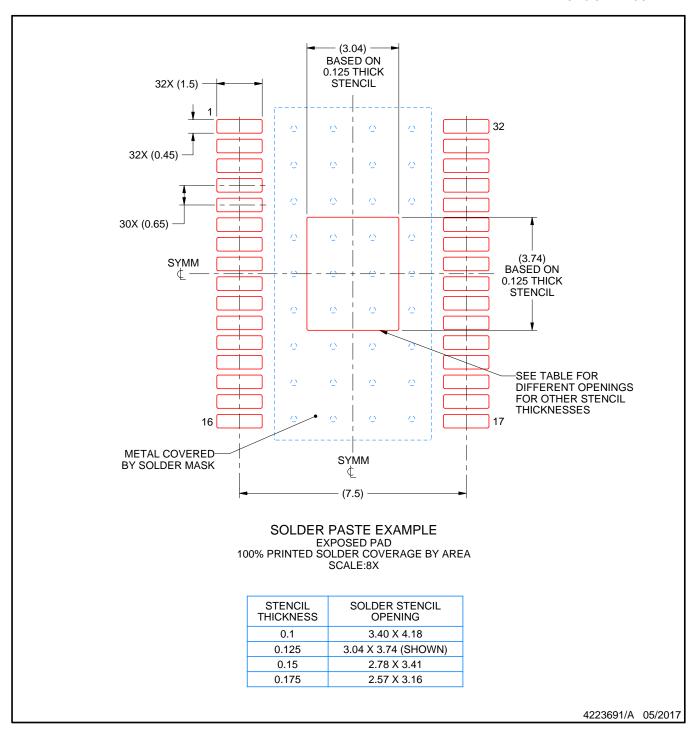

- Available in 32-Pin Thermally Enhanced HTSSOP (DAP) Package

### **APPLICATIONS**

- DTV

- TCON

- BDVD

- Set Top Boxes

- Tablet PC

### DESCRIPTION

The TPS563900 device is a monolithic dualsynchronous buck converter with a wide 4.5-V to 18-V operating input-voltage range that can operate in 5-, 9-, 12-, or 15-V bus voltages and battery chemistries. Constant-frequency peak-current mode control simplifies the loop compensation and provides fast transient response.

External feedback resistors can be used to set the initial start-up voltage for each buck converter in the TPS563900 device. The feedback voltage reference for this start-up option is 0.6 V. When the voltage-identification (VID) DAC is updated through the I<sup>2</sup>C, the buck converter switches the feedback resistors from external to internal feedback resistors. The output voltage in each buck is programmable from 0.68 V to 1.95 V with 10-mV steps by I<sup>2</sup>C-controlled 7-bit VID.

Each buck converter in the TPS563900 device can also be I<sup>2</sup>C controlled for enabling and disabling the output voltage, reading the output voltage, setting the pulse skipping mode, and reading the power good status and the warning of die temperature.

The TPS563900 device features a dedicated enable pin when the I<sup>2</sup>C interface is not used. An independent soft-start pin provides flexibility in power-up programmability. Cycle-by-cycle overcurrent protection and hiccup-mode operation limit MOSFET power dissipation in short circuit or over-loading fault conditions. Low-side reverse overcurrent protection also prevents excessive sinking current from damaging the converter.

The TPS563900 device also features a light-load pulse-skipping mode (PSM) that can be controlled by the I<sup>2</sup>C or MODE pin configuration. The PSM mode allows a power loss reduction on the input power supplied to the system to achieve high efficiency at light loading.

The TPS563900 device is available in a 32-lead thermally-enhanced HTSSOP (DAP) package.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

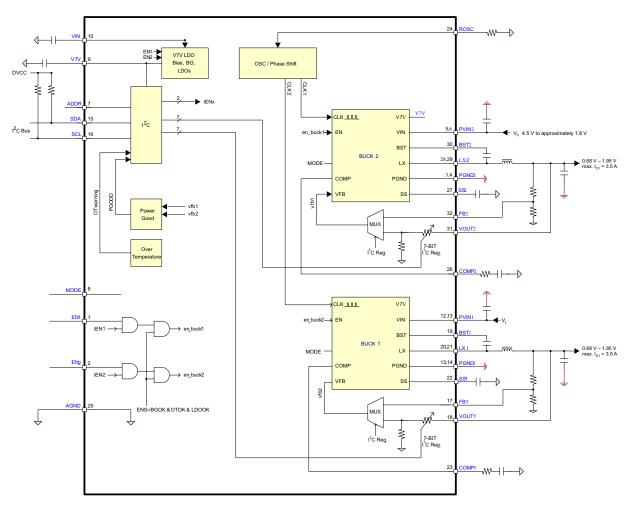

### **FUNCTIONAL BLOCK DIAGRAM**

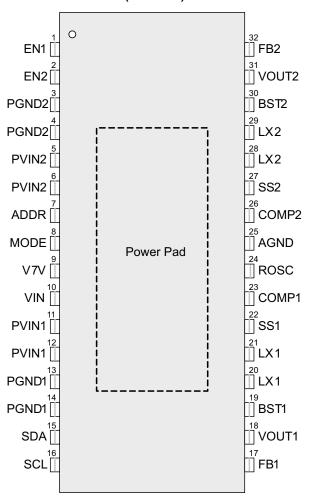

### **TERMINAL CONFIGURATION**

### DAP PACKAGE (TOP VIEW)

### TERMINAL FUNCTIONS

| TERMINAL FUNCTIONS        |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|---------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                      | NO.<br>(HTSSOP) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| EN1, EN2                  | 1, 2            | Enable pin. Adjust the input under-voltage lockout with two resistors.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PGND2                     | 3, 4            | Power ground of Buck 2, place the ground pin of this input capacitor as close as possible to this pin.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| PVIN2                     | 5, 6            | Power input. Input power supply to the power switches of the power converter 2.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| ADDR                      | 7               | I <sup>2</sup> C address configuration pin. Connect this pin to low, high, or leave it open to select different I <sup>2</sup> C slave address.                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| MODE                      | 8               | Operation-mode control pin. Connect this pin to ground to choose forced PWM mode; leave the pin open for pulse skipping mode (PSM) operation at light load condition.                                                                                                                                                                                                                                                                                                                          |  |  |  |

| V7V                       | 9               | Internal low-drop linear regulator (LDO) output to power internal driver and control circuits. Decouple this pin to power ground with a minimum 1-µF ceramic capacitor. The output regulates to 6.3 V (typical) for optimal conduction on-resistances of the internal power MOSFETs. In PCB design, the power ground and analog ground must have one-point common connection at the negative terminal of the V7V bypass capacitor. If VIN is lower than 6.3 V, V7V is slightly lower than VIN. |  |  |  |

| VIN                       | 10              | Power supply of the internal LDO and controllers                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| PVIN1                     | 11, 12          | Power input. Input power supply to the power switches of the power converter 1.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| PGND1                     | 13, 14          | Power ground of Buck 1, place the ground pin of the input capacitor as close as possible to this pin.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| SDA                       | 15              | I <sup>2</sup> C interface data pin                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| SCL                       | 16              | I <sup>2</sup> C interface clock pin                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| FB1                       | 17              | Feedback sensing pin for the external feedback resistors in Buck 1. Before I <sup>2</sup> C-controlled VID selection is enabled, an external resistor divider connected to this pin sets the initial output voltage.                                                                                                                                                                                                                                                                           |  |  |  |

| VOUT1                     | 18              | Buck 1 output voltage sensing pin; When I <sup>2</sup> C controlled VID selection is enabled, output voltage can be programmed from 0.68 V to 1.95 V with 10-mV steps.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| BST1                      | 19              | Supply input for the high-side NFET gate drive circuit of Buck 1. Connect a ceramic capacitor between the BST1 and LX1 pins.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| LX1                       | 20, 21          | Switching node of Buck 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| SS1                       | 22, 27          | Soft start and voltage tracking in Buck 1. An external capacitor connected to this pin sets the internal voltage reference rise time. Because the voltage on this pin overrides the internal reference, it can be used for tracking and sequencing.                                                                                                                                                                                                                                            |  |  |  |

| COMP1                     | 23              | Error amplifier output and loop compensation pin for Buck 1. Connect frequency compensation to this pin.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| ROSC                      | 24              | Oscillator frequency programmable pin. Connect an external resistor to set the switching frequency. When connected to an external clock, the internal oscillator synchronizes to the external clock.                                                                                                                                                                                                                                                                                           |  |  |  |

| AGND                      | 25              | Analog ground of the converter. Connect sensitive (such as SSx and FBx) returns to AGND at a single point.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| COMP2                     | 26              | Error amplifier output and loop compensation pin for Buck 2. Connect frequency compensation to this pin.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| SS2                       | 27              | Soft-start and voltage tracking in Buck 2. An external capacitor connected to this pin sets the internal voltage reference rise time. Since the voltage on this pin overrides the internal reference, it can be used for tracking and power sequencing.                                                                                                                                                                                                                                        |  |  |  |

| LX2                       | 28, 29          | Switching nodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| BST2                      | 30              | Supply input for high-side NFET gate drive circuit of Buck 2. Connect a ceramic capacitor between BST2 and LX2 pins.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| VOUT2                     | 31              | Buck 2 output voltage sensing pin. When I <sup>2</sup> C-controlled VID selection is enabled, the output voltage can be programmed from 0.68 V to 1.95 V with 10-mV steps.                                                                                                                                                                                                                                                                                                                     |  |  |  |

| FB2                       | 32              | Feedback sensing pin for the external feedback resistors in Buck 2. Before I <sup>2</sup> C-controlled VID selection is enabled, an external resistor divider connected to this pin sets the initial output voltage.                                                                                                                                                                                                                                                                           |  |  |  |

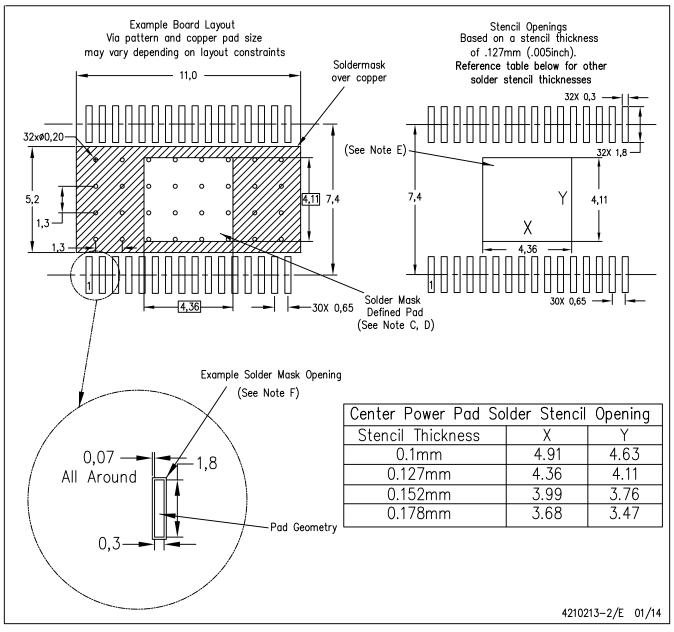

| Exposed<br>Thermal<br>Pad | 33              | Exposed thermal pad of the package. Connect to the power ground. There is no electric signal down bonded to the thermal pad inside the IC package. TI highly recommends to always solder this thermal pad to PCB board, and have as many vias as possible on the PCB to enhance power dissipation.                                                                                                                                                                                             |  |  |  |

SLVSCC7-DECEMBER 2013 www.ti.com

### ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

|                  |                                                                         | VALUE       | VALUE |    |

|------------------|-------------------------------------------------------------------------|-------------|-------|----|

|                  |                                                                         | MIN         | MAX   |    |

|                  | Voltage range at VIN, PVIN1,PVIN2                                       | -0.3        | 20    | V  |

|                  | Voltage range at LX1, LX2 (maximum withstand voltage transient < 20 ns) | -1          | 20    | V  |

|                  | Voltage at BST1, BST2, referenced to LX1, LX2 pin                       | -0.3        | 7     | V  |

|                  | Voltage at V7V, EN1, EN2, VOUT1, VOUT2, MODE                            | -0.3        | 7     | V  |

|                  | Voltage at SS1, SS2, FB1, FB2, COMP1, COMP2                             | -0.3        | 3     | V  |

|                  | Voltage at SDA, SCL, ADDR, EN1, EN2, ROSC                               | -0.3        | 7     | V  |

|                  | Voltage at AGND, PGND1, PGND2                                           | -0.3        | 0.3   | V  |

| $T_{J}$          | Operating virtual junction temperature range                            | -40         | 125   | °C |

| T <sub>stg</sub> | Storage temperature range                                               | <b>–</b> 55 | 150   | °C |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### THERMAL INFORMATION

|                  |                                                             | TPS563900 |       |

|------------------|-------------------------------------------------------------|-----------|-------|

|                  | THERMAL METRIC                                              | DAP       | UNITS |

|                  |                                                             | 32 PINS   |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance (1)                  | 35        |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance (2)               | 17.7      |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance (3)                    | 19        | 2004  |

| $\Psi_{JT}$      | Junction-to-top characterization parameter <sup>(4)</sup>   | 0.5       | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter <sup>(5)</sup> | 18.9      |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance (6)            | 1.3       |       |

- (1) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (3) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                |                         | MIN | NOM MAX | UNIT |

|----------------|-------------------------|-----|---------|------|

| VIN            | Input operating voltage | 4.5 | 18      | V    |

| T <sub>A</sub> | Ambient temperature     | -40 | 85      | °C   |

### **ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

|                           | MIN  | MAX | UNIT |

|---------------------------|------|-----|------|

| Human body model (HBM)    | 2000 |     | V    |

| Charge device model (CDM) | 500  |     | V    |

### **ELECTRICAL CHARACTERISTICS**

$T_1 = 25^{\circ}C$ .  $V_1 = 12 \text{ V}$  (unless otherwise noted)

|                           | PARAMETER                                                               | TEST CONDITIONS                                        | MIN   | TYP    | MAX   | UNIT   |

|---------------------------|-------------------------------------------------------------------------|--------------------------------------------------------|-------|--------|-------|--------|

| INPUT SUPPL               | LY                                                                      |                                                        |       |        | '     |        |

| V <sub>I</sub>            | Input voltage range                                                     | VIN1 and VIN2                                          | 4.5   |        | 18    | V      |

| IDD <sub>SD</sub>         | Shutdown supply current                                                 | EN1 = EN2 = low                                        |       | 10     |       | μΑ     |

| IDD <sub>Q_NSW</sub>      | Switching quiescent current with no load at DCDC output                 | EN1 = EN2 = 3.3 V<br>Without bucks switching           |       | 1.2    |       | mA     |

| IDD <sub>Q_SW</sub>       | Switching quiescent current with no load at DCDC output, Buck switching | EN1 = EN2 = 3.3 V<br>With bucks switching              |       | 10     |       | mA     |

|                           |                                                                         | Rising V <sub>I</sub>                                  |       | 4.25   | 4.5   |        |

| UVLO                      | V <sub>I</sub> under voltage lockout                                    | Falling V <sub>I</sub>                                 | 3.5   | 3.75   |       | V      |

|                           |                                                                         | Hysteresis                                             |       | 0.5    |       |        |

| V <sub>7V</sub>           | 6.3 V LDO                                                               | V7V load current = 0 A,<br>V <sub>I</sub> = 12 V       | 6.1   | 6.3    | 6.5   | V      |

| I <sub>OCP V7V</sub>      | Current-limit of V7V LDO                                                |                                                        |       | 200    |       | mA     |

| ENABLE                    |                                                                         | •                                                      | •     |        | l     |        |

| V <sub>ENR</sub>          | Enable threshold                                                        |                                                        |       | 1.21   | 1.26  | V      |

| V <sub>ENF</sub>          | Enable threshold                                                        |                                                        | 1.1   | 1.17   |       | V      |

| I <sub>ENR</sub>          | Enable Input current                                                    | EN = 1 V                                               |       | 3      |       | μΑ     |

| I <sub>ENF</sub>          | Enable hysteresis current                                               | EN = 1.5 V                                             |       | 3      |       | μA     |

| OSCILLATOR                | ?                                                                       | •                                                      | 1     |        | I     |        |

|                           |                                                                         |                                                        | 200   |        | 1600  |        |

| $f_{\sf SW}$              | Switching frequency                                                     | ROSC = 100 kΩ (1%)                                     | 340   | 400    | 460   | kHz    |

| T <sub>SYNC_w</sub>       | Clock sync minimum pulse width                                          |                                                        |       |        | 20    | ns     |

| V <sub>SYNC_HI</sub>      | Clock sync high threshold                                               |                                                        |       |        | 2     | V      |

| V <sub>SYNC_LO</sub>      | Clock sync low threshold                                                |                                                        | 0.8   |        |       | V      |

| V <sub>SYNC_D</sub>       | Clock falling edge to LX rising edge delay                              |                                                        |       | 66     |       | ns     |

| $f_{\sf SYNC}$            | Clock sync frequency range                                              |                                                        | 200   |        | 1600  | kHz    |

|                           | CK 2 CONVERTERS                                                         |                                                        | 1     |        |       |        |

| V <sub>ref(min)</sub>     | Voltage reference                                                       | 0 A < I <sub>O1.2</sub> < 3.5 A                        | 0.594 | 0.6    | 0.606 | V      |

| V <sub>O1,2</sub>         | Output voltage step size<br>(VID 0x00 – 0x7F)                           |                                                        | 8     | 10     | 12    | mV     |

| $\Delta V_{O(\Delta VI)}$ | Line regulation—DC                                                      | I <sub>O</sub> = 2 A                                   |       | 0.5    |       | %/V    |

| $\Delta V_{O(\Delta IL)}$ | Load regulation—DC                                                      | $I_O = (10 \text{ to } 90\%) \times I_{O \text{ max}}$ |       | 0.5    |       | %/A    |

| 9 <sub>m_EA3</sub>        | Error amplifier trans-conductance                                       | $-2 \mu A < I_{COMP} < 2 \mu A$                        |       | 1350   |       | μS     |

| 9 <sub>m_SRC3</sub>       | COMP voltage to inductor current G <sub>m</sub>                         | I <sub>LX</sub> = 0.5 A                                |       | 10     |       | A/V    |

| I <sub>SSx</sub>          | Soft-start pin charging current                                         | SS1, SS2                                               |       | 6      |       | μΑ     |

| I <sub>L1</sub>           | Buck 1 peak inductor current-limit                                      |                                                        |       | 4.5    |       | A      |

| I <sub>L2</sub>           | Buck 2 peak inductor current-limit                                      |                                                        |       | 4.5    |       | Α      |

| I <sub>LLSx</sub>         | Low-side sinking current-limit                                          |                                                        |       | -2.6   |       | Α      |

| R <sub>DS(on)x_HS</sub>   | On-resistance of high-side FET                                          | V7V = 6.3 V                                            |       | 90     |       | mΩ     |

| R <sub>DS(on)x_LS</sub>   | On-resistance of low-side FET                                           | V <sub>I</sub> = 12 V                                  |       | 65     |       | mΩ     |

| t <sub>on(min)</sub>      | Minimum on time                                                         |                                                        |       | 94     | 145   | ns     |

| V <sub>bootUV</sub>       | Boot-LX UVLO                                                            |                                                        |       | 2.1    | 3     | V      |

| t <sub>hiccupwait</sub>   | Hiccup wait time                                                        |                                                        |       | 512    |       | cycles |

| t <sub>hiccup_re</sub>    | Hiccup time before re-start                                             |                                                        | 1     | 16 384 |       | cycles |

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

## **ELECTRICAL CHARACTERISTICS (continued)**

$T_1 = 25$ °C,  $V_1 = 12$  V (unless otherwise noted)

|                           | PARAMETER                                                                             | TEST CONDITIONS                                        | MIN                       | TYP   | MAX | UNIT |

|---------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------|-------|-----|------|

| I <sup>2</sup> C READ BAC | K FAULT STATUS                                                                        |                                                        |                           |       |     |      |

|                           |                                                                                       | Feedback lower voltage rising (with respect to 0.6 V ) |                           | 94.0  |     |      |

| $V_{PGOOD}$               | PGOOD trip levels                                                                     | Feedback lower voltage falling (with respect to 0.6 V) |                           | 92.5  |     | 0/   |

| VPGOOD                    | PGOOD trip levels                                                                     | Feedback upper voltage rising (with respect to 0.6 V)  |                           | 107.5 |     | %    |

|                           |                                                                                       | Feedback upper voltage falling (with respect to 0.6 V) |                           | 105.5 |     |      |

| T <sub>warn</sub>         | Temperature warning threshold                                                         |                                                        |                           | 125   |     | °C   |

| THERMAL SH                | UTDOWN                                                                                |                                                        |                           |       |     |      |

| T <sub>TRIP</sub>         | Thermal protection trip point                                                         | Rising temperature                                     |                           | 160   |     | °C   |

| T <sub>hys</sub>          | Thermal protection hysteresis                                                         |                                                        |                           | 20    |     | °C   |

| I <sup>2</sup> C INTERFAC | E                                                                                     |                                                        |                           |       | 1   |      |

| V <sub>IH</sub> SDA, SCL  | Input high voltage                                                                    |                                                        |                           |       | 1.3 | V    |

| V <sub>IL</sub> SDA, SCL  | Input low voltage                                                                     |                                                        | 0.4                       |       |     | V    |

| l <sub>l</sub>            | Input current                                                                         | SDA, SCL, V <sub>I</sub> = 0.4 V to 4.5 V              | -10                       |       | 10  | μA   |

| V <sub>OL</sub> SDA       | SDA output low voltage                                                                | SDA open drain, I <sub>OL</sub> = 4 mA                 |                           |       | 0.4 | V    |

| $f_{\sf max}$             | Maximum SCL clock frequency                                                           |                                                        | 400                       |       |     | kHz  |

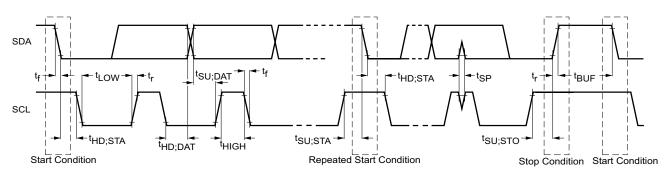

| t <sub>BUF</sub>          | Bus-free time between a STOP and START condition                                      |                                                        | 1.3                       |       |     | μs   |

| t <sub>h_STA</sub>        | Hold time (Repeated) START condition                                                  |                                                        | 0.6                       |       |     | μs   |

| t <sub>su_STO</sub>       | Setup time for STOP condition                                                         |                                                        | 0.6                       |       |     | μs   |

| $t_{LOW}$                 | LOW period of the SCL clock                                                           |                                                        | 1.3                       |       |     | μs   |

| t <sub>HIGH</sub>         | HIGH period of the SCL clock                                                          |                                                        | 0.6                       |       |     | μs   |

| t <sub>su_STA</sub>       | Setup time for a repeated START condition                                             |                                                        | 0.6                       |       |     | μs   |

| t <sub>SU_DAT</sub>       | Data setup time                                                                       |                                                        | 0.1                       |       |     | μs   |

| t <sub>h_DAT</sub>        | Data hold time                                                                        |                                                        | 0                         |       | 0.9 | μs   |

| t <sub>rCL</sub>          | Rise time of SCL signal                                                               | Capacitance of one bus line (pF)                       | 20 +<br>0.1C <sub>B</sub> |       | 300 | ns   |

| t <sub>rCL1</sub>         | Rise time of SCL signal after a repeated START condition and after an acknowledge BIT | Capacitance of one bus line (pF)                       | 20 +<br>0.1C <sub>B</sub> |       | 300 | ns   |

| $t_{fCL}$                 | Fall time of SCL sgnal                                                                | Capacitance of one bus line (pF)                       | 20 +<br>0.1C <sub>B</sub> |       | 300 | ns   |

| t <sub>rDA</sub>          | Rise time of SDA signal                                                               | Capacitance of one bus line (pF)                       | 20 +<br>0.1C <sub>B</sub> |       | 300 | ns   |

| t <sub>fDA</sub>          | Fall time of SDA signal                                                               | Capacitance of one bus line( pF)                       | 20 +<br>0.1C <sub>B</sub> |       | 300 | ns   |

| СВ                        | Capacitance of one bus line (SCL and SDA)                                             |                                                        |                           |       | 400 | pF   |

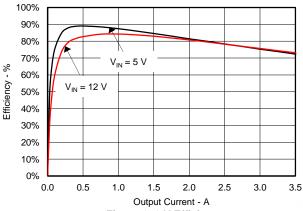

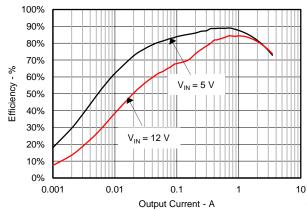

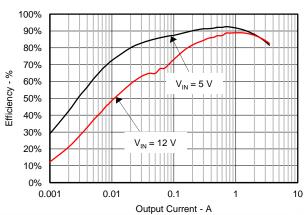

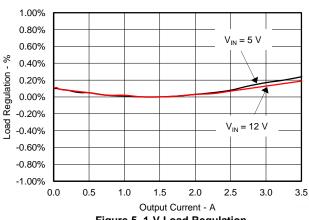

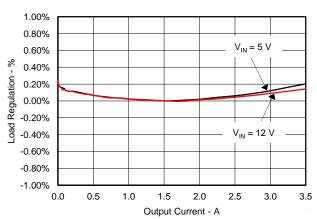

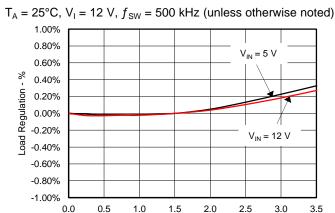

### TYPICAL CHARACTERISTICS

$T_A = 25$ °C,  $V_I = 12$  V,  $f_{SW} = 500$  kHz (unless otherwise noted)

Figure 1. 1-V Efficiency

Figure 2. 1-V Efficiency, Eco-mode™

Figure 3. 1.8-V Efficiency

Figure 4. 1.8-V Efficiency, Eco-mode

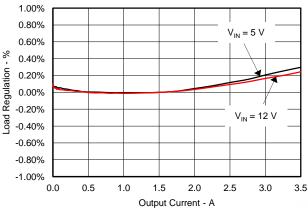

Figure 5. 1-V Load Regulation

Figure 6. 1-V Load Regulation, Eco-mode

**NSTRUMENTS**

# PRODUCT PREVIEW

### TYPICAL CHARACTERISTICS (continued)

Output Current - A Figure 7. 1.8-V Load Regulation

Figure 8. 1.8-V Load Regulation, Eco-mode

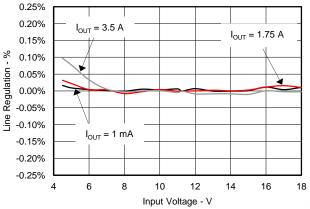

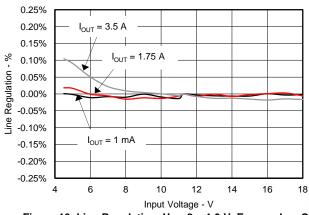

Figure 9. Line Regulation,  $V_{OUT}1 = 1.0 V$ , Eco-mode = OFF

Figure 10. Line Regulation, V<sub>OUT</sub>2 = 1.0 V, Eco-mode = OFF

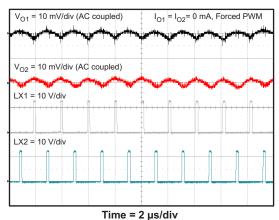

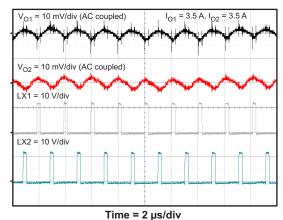

Figure 11. Output Ripple at 0 A, Forced PWM

Figure 12. Output Ripple at 3.5 A, Forced PWM

Copyright © 2013, Texas Instruments Incorporated

# TEXAS INSTRUMENTS

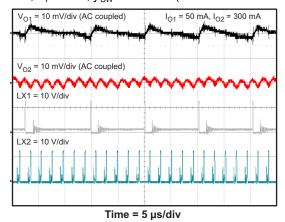

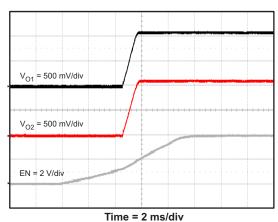

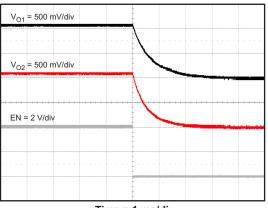

### TYPICAL CHARACTERISTICS (continued)

$T_A = 25$ °C,  $V_I = 12$  V,  $f_{SW} = 500$  kHz (unless otherwise noted)

Figure 13. Output Ripple, Buck1 at 0.05 A, Buck 2 at 0.3 A Auto PSM-PWM Mode

Figure 14. Startup With Enable

Time = 1 ms/div Figure 15. Shutdown With Enable

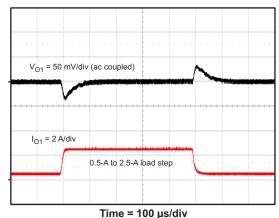

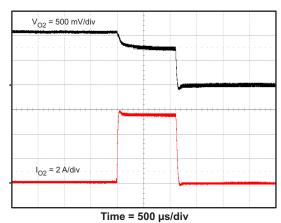

Figure 16. Load Transient, Buck 1 (0.5 A to 2.5 A)

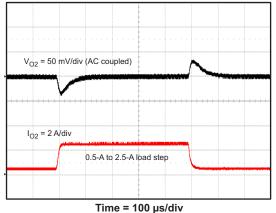

Figure 17. Load Transient, Buck 2 (0.5 A to 2.5 A)

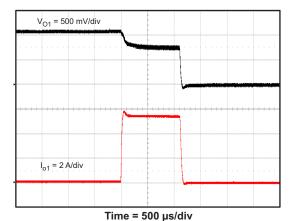

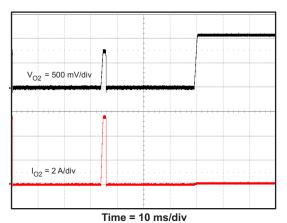

Figure 18. Overcurrent Protection, Buck 1

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

10

**ISTRUMENTS**

# PRODUCT PREVIEW

### **TYPICAL CHARACTERISTICS (continued)**

$T_A = 25$ °C,  $V_I = 12$  V,  $f_{SW} = 500$  kHz (unless otherwise noted)

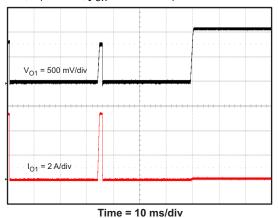

Figure 19. Hiccup Recover, Buck 1

Figure 20. Overcurrent Protection, Buck 2

Figure 21. Hiccup Recover, Buck 2

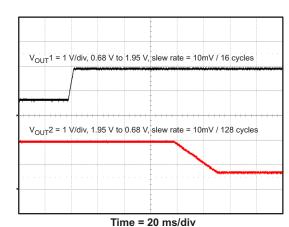

Figure 22. Voltage Change With I<sup>2</sup>C Control

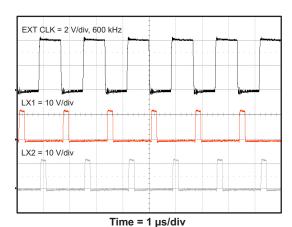

Figure 23. Synchronization at 600 kHz

Copyright © 2013, Texas Instruments Incorporated

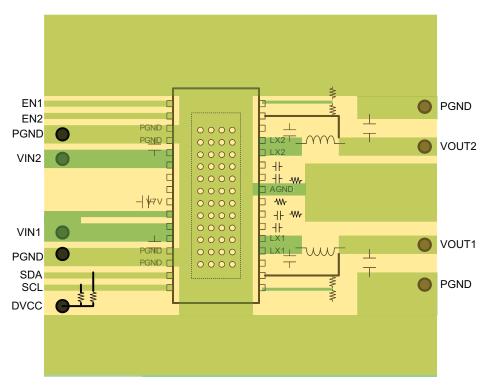

### OVERVIEW

The TPS563900 device is a dual 3.5-A/3.5-A output current, synchronous step-down (buck) converter with integrated N-channel MOSFETs. A wide 4.5-V to 18-V input supply range to buck encompasses most intermediate bus voltages operating off 9-V, 12-V, or 15-V power bus.

The TPS563900 device is equipped with an I<sup>2</sup>C-compatible bus for sophisticated control and communication with SoC. With an I<sup>2</sup>C interface, SoC can enable or disable the power converters, set the output voltage, and read status registers. The buck regulator has external feedback resistors that can be used for setting the initial start-up voltage. The feedback voltage reference for this start-up option is 0.6 V. When the voltage identification VID DAC is updated through the I<sup>2</sup>C, the output voltage of each channel can be independently programmed with 7-bit VID from 0.68 V to 1.95 V in 10-mV steps. The output-voltage transitions begin when the I<sup>2</sup>C interface receives the command for the GO bit in the command registers. In light loading condition, the I<sup>2</sup>C can control or select lowpulse skipping mode with MODE-pin configuration.

The TPS563900 device implements a constant frequency, peak current-mode control which simplifies external frequency compensation. The wide switching frequency of 200 kHz to 1600 kHz allows for efficiency and size optimization when selecting the output filter components. An external resistor to ground on the ROSC pin can adjust the switching frequency. The TPS563900 device also has an internal phase lock loop (PLL) controlled by the ROSC pin that can synchronize the switching cycle to the falling edge of an external system clock. 180° outof-phase operation between two channels reduces input filter and power-supply induced noise.

The TPS563900 device has been designed for safe monotonic startup into pre-biased loads. The default start-up occurs when VIN is at 4.5 V (typical). The EN pin has an internal pullup current source that can be used to adjust the undervoltage lockout (UVLO) of the input voltage with two external resistors. In addition, the EN pin can be left floating in order to automatically start up the TPS563900 device with the internal pullup current.

The integrated MOSFETs of each channel allow for high-efficiency power-supply designs with continuous output currents up to 3.5 A. The MOSFETs have been sized to optimize efficiency for lower duty-cycle applications.

The TPS563900 device reduces the external component count by integrating the boot-recharge circuit. The bias voltage for the integrated high-side MOSFET is supplied by a capacitor between the BOOT and LX pins. The boot-capacitor voltage is monitored by a BOOT to LX UVLO (BOOT-LX UVLO) circuit which allows the LX pin to be pulled low in order to recharge the boot capacitor. The TPS563900 device operates at 100% duty cycle as long as the boot-capacitor voltage is higher than the preset BOOT-LX UVLO threshold which is 2.1 V (typical).

The TPS563900 device has a power-good comparator (PWRGD) with hysteresis that monitors the output voltage through the internal feedback voltage. The I<sup>2</sup>C can read the power-good status with the commanding register.

The SS (soft-start/tracking) pin is used to minimize inrush currents or provide power-supply sequencing during power up. A small value capacitor or resistor divider must be coupled to the pin for soft-start or critical powersupply sequencing requirements.

The TPS563900 device is protected from output overvoltage, overload, and thermal fault conditions. The TPS563900 device minimizes excessive-output overvoltage transients by taking advantage of the power good comparator. When the overvoltage comparator is activated, the high-side MOSFET turns off and is prevented from turning on until the internal feedback voltage is lower than 108% of the 0.6-V reference voltage. The TPS563900 device implements both high-side MOSFET overload protection and bidirectional low-side MOSFET overload protection which help control the inductor current and avoid current runaway. If the overcurrent condition has lasted for more than the hiccup wait time, the TPS563900 device shuts down and restarts after the hiccup time. The TPS563900 device also shuts down if the junction temperature is higher than thermal shutdown trip point. When the junction temperature drops 20°C (typical) below the thermal-shutdown trip point, the built-in thermal-shutdown hiccup timer is triggered. The TPS563900 device restarts under the control of the soft-start circuit automatically after the thermal-shutdown hiccup time is over.

Furthermore, if the overcurrent condition occurs for more than the hiccup wait time, which is programmed for 512 switching cycles, the TPS563900 device shuts down and restarts after the hiccup time, which is set for 16 384 cycles. The hiccup mode helps to reduce the device power dissipation under severe overcurrent conditions.

The TPS563900 device operates at any load condition unless the COMP-pin voltage drops below the COMP-pin start-switching threshold which is 0.25 V (typically).

Product Folder Links: TPS563900

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

When PSM mode operation is enabled, the TPS563900 device monitors the peak switch current of the high-side MOSFET. When the peak switch current is lower than 1 A (typical), the device stops switching in order to boost the efficiency until the peak switch current is higher than 1 A (typical) again.

### **DETAILED DESCRIPTION**

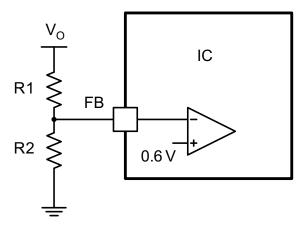

### **Adjusting the Output Voltage**

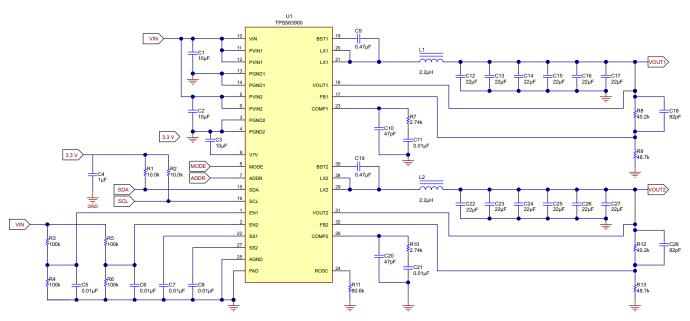

The output voltage is set with a resistor divider from the output node (VOUT) to the FB pin. TI recommends to use divider resistors with a 1% tolerance or better.

Figure 24. Voltage-Divider Circuit

$$R2 = R1 \times \left(\frac{0.6 \text{ V}}{V_0 - 0.6 \text{ V}}\right)$$

(1)

Begin with R1 at 40.2-k $\Omega$  and use Equation 1 to calculate R2. To improve efficiency at light loads consider using larger value resistors. If the values are too high, the regulator is more susceptible to noise and voltage errors from the FB input current are noticeable.

The I<sup>2</sup>C-controlled VID in a 7-bit register can also change the output voltage.

The minimum on time of the high-side MOSFET and bootstrap voltage (BOOT-PH voltage) can limit the minimum and maximum output voltages (see Bootstrap Voltage (BOOT) and Low Dropout Operation).

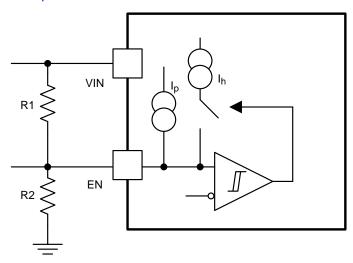

### **Enabling and Adjusting Undervoltage Lockout**

The EN pin provides electrical on and off control of the device. When the EN-pin voltage exceeds the threshold voltage, the device starts operation. If the EN-pin voltage is pulled below the threshold voltage, the regulator stops switching and enters low  $I_Q$  state.

The EN pin has an internal pullup current source which allows the user to float the EN pin to enable the device. If an application requires EN-pin control, use open-drain or open-collector output logic to interface with the pin.

The device implements internal UVLO circuitry on the VIN pin. The device disables when the VIN-pin voltage falls below the internal VIN-UVLO threshold. The internal VIN-UVLO threshold has a hysteresis of 500 mV.

If an application requires either a higher UVLO threshold on the VIN pin or a secondary UVLO on PVIN, in split rail applications, configure the EN pin as shown in Figure 25.

When using the external UVLO function TI recommends to set the hysteresis to be greater than 500 mV.

The EN pin has a small pullup current,  $I_p$ , which sets the default state of the pin to enable when no external components are connected. The pullup current is also used to control the voltage hysteresis for the UVLO function because it increases by  $I_h$  when the EN pin crosses the enable threshold. The UVLO thresholds can be calculated with Equation 2 and Equation 3.

Figure 25. Adjustable VIN Under-Voltage Lockout

$$R1 = \frac{V_{START}(\frac{V_{ENfalling}}{V_{ENrising}}) - V_{STOP}}{I_{p}(1 - \frac{V_{ENfalling}}{V_{ENrising}}) + I_{h}}$$

$$R2 = \frac{R1 \times V_{ENfalling}}{V_{STOP} - V_{ENfalling}} + R1(I_{h} + I_{p})$$

(2)

where

- I<sub>h</sub> = 3 μA

- $I_p = 3 \mu A$

- V<sub>ENrising</sub> = 1.21 V

V<sub>ENfalling</sub> = 1.17 V

(3)

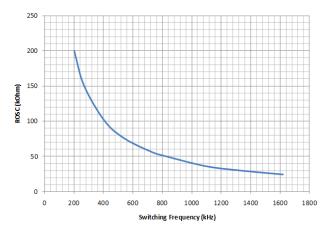

### Adjustable Switching Frequency and Synchronization

Adjustable Switching Frequency and Synchronization mode overrides the resistor mode. The device is able to detect the proper mode automatically and switch from synchronization mode to resistor mode.

### Adjustable Switching Frequency (Resistor Mode)

To determine the ROSC resistance for a given switching frequency, use Equation 4 or the curve in Figure 26. To reduce the solution size set the switching frequency as high as possible, however, tradeoffs of the supply efficiency and minimum controllable on time must be considered.

Figure 26. ROSC Versus Switching Frequency

ROSC

$$(k\Omega) = 45580 \times f_{SW}^{-1.019} (kHz)$$

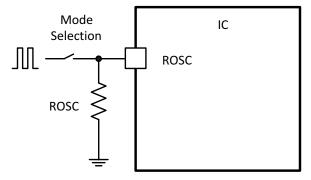

### **Synchronization**

An internal phase-locked loop (PLL) has been implemented to allow synchronization between 200 kHz and 1600 kHz, and to easily switch from Resistor mode to Synchronization mode.

To implement the synchronization feature, connect a square-wave clock signal to the ROSC pin with a duty cycle between 20% to 80%. The clock signal amplitude must transition lower than 0.8 V and higher than 2 V. The start of the switching cycle is synchronized to the falling edge of the ROSC pin.

In applications where both Resistor mode and Synchronization mode are required, configure the device as shown in Figure 27. Before the external clock is present, the device works in Resistor mode and the switching frequency is set by the ROSC resistor. When the external clock is present, the Synchronization mode overrides the Resistor mode. The first time the ROSC pin is pulled above the ROSC high threshold (2 V), the device switches from the Resistor mode to the Synchronization mode and the ROSC pin becomes high impedance as the PLL starts to lock onto the frequency of the external clock. Switching from the Synchronization mode back to the Resistor mode i snot recommended because the internal switching frequency first drops to 100 kHz before returning to the switching frequency set by the ROSC resistor.

Figure 27. Resistor Mode and Synchronization Mode

### **Soft-Start Time**

The start up of the buck output is controlled by the voltage on the respective SS pin. When the voltage on the SS pin is less than the internal 0.6-V reference, the TPS563900 device regulates the internal feedback voltage to the voltage on the SS pin instead of 0.6 V. The SS pin can be used to program an external soft-start function or to allow the output of the buck to track another supply during startup. The device has an internal pullup current source of 6  $\mu$ A that charges an external soft-start capacitor to provide a linear ramping voltage at the SS pin. The TPS563900 device regulates the internal feedback voltage according to the voltage on the SS pin which allows  $V_0$  to rise smoothly from 0 V to the final regulated voltage. The total soft-start time is calculated with Equation 5 (approximately).

$$t_{SS}$$

(ms) =  $C_{SS}$  (nF)  $\times \left(\frac{0.6 \times V}{6 \times \mu A}\right)$  (5)

### **VID Control**

When the I<sup>2</sup>C is not in use, the output voltage of TPS563900 device is solely set by an external resistor divider. If the system must control the output voltage, the voltage-identification (VID) DAC can be controlled through the I<sup>2</sup>C interface to the Output Voltage Selection register of 0x00H (Buck 1) and 0x1H (Buck 2). The output voltage is required to be preset by the external resistor divider. When the VID DAC is selected through the I<sup>2</sup>C interface and the GO bit in the command register is set, the output voltage is set with the internal voltage divider over the external voltage divider.

### **Out-of-Phase Operation**

In order to reduce the input ripple current, Buck 1 and Buck 2 operate 180° out-of-phase. This operation enables the system to have less input ripple to lower component cost, save board space, and reduce EMI.

### **Output Overvoltage Protection (OVP)**

The device incorporates an output overvoltage protection (OVP) circuit to minimize output voltage overshoot. For example, when the power supply output is overloaded the error amplifier compares the actual output voltage to the internal reference voltage. If the FB-pin voltage is lower than the internal reference voltage for a considerable time, the output of the error amplifier demands maximum output current. Once the condition is removed, the regulator output rises and the error amplifier output transitions to the steady state voltage. In some applications with small output capacitance, the power-supply output voltage can respond faster than the error amplifier. When the power-supply output voltage responds faster than the error amplifier, a possibility of an output overshoot occurs. The OVP feature minimizes the overshoot by comparing the FB-pin voltage to the OVP threshold. If the FB-pin voltage is greater than the OVP threshold the high-side MOSFET turns off which prevents current from flowing to the output and minimizing output overshoot. When the FB voltage drops lower than the OVP threshold, the high-side MOSFET turns on at the next clock cycle.

### **Bootstrap Voltage (BOOT) and Low Dropout Operation**

The device has an integrated boot regulator. A small ceramic capacitor between the BOOT and LX pins provides the gate drive voltage for the high-side MOSFET. The boot capacitor is charged when the BOOT-pin voltage is less than VIN and the BOOT-LX voltage is below regulation. The value of this ceramic capacitor must be 0.1  $\mu$ F. A ceramic capacitor with an X7R- or X5R-grade dielectric with a voltage rating of 10 V or higher is recommended because of the stable characteristics over temperature and voltage.

To improve drop out, the device is designed to operate at 100% duty cycle as long as the BOOT-LX-pin voltage is greater than the BOOT-LX UVLO threshold which is 2.1 V (typical). When the voltage between BOOT and LX drops below the BOOT-LX UVLO threshold, the high-side MOSFET turns off and the low-side MOSFET turns on which allows the boot capacitor to be recharged. In applications with split input voltage rails, 100% duty cycle operation can be achieved as long as (VIN – PVIN) > 4 V.

### **Overcurrent Protection**

The device is protected from overcurrent conditions by cycle-by-cycle current limiting on both the high-side MOSFET and the low-side MOSFET.

### **High-Side MOSFET Overcurrent Protection**

The device implements current mode control which uses the COMP-pin voltage to control the turn off of the high-side MOSFET and the turn on of the low-side MOSFET on a cycle-by-cycle basis. During each cycle the switch current and the current reference generated by the COMP-pin voltage are compared. When the peak switch current intersects the current reference the high-side switch turns off.

### **Low-Side MOSFET Overcurrent Protection**

While the low-side MOSFET is turned on, the conduction current of the low-side MOSFET is monitored by the internal circuitry. During normal operation the low-side MOSFET sources current to the load. At the end of every clock cycle, the low-side MOSFET sourcing current is compared to the internally-set low-side sourcing current-limit. If the low-side sourcing current is exceeded, the high-side MOSFET is not turned on and the low-side MOSFET stays on for the next cycle. The high-side MOSFET turns on again when the low-side current is below the low-side sourcing current-limit at the start of a cycle.

The low-side MOSFET can also sink current from the load. If the low-side sinking current-limit is exceeded the low-side MOSFET turns off immediately for the rest of that clock cycle. In this scenario both MOSFETs are off until the start of the next cycle.

Furthermore, if an output overload condition (as measured by the COMP-pin voltage) occurs for more than the hiccup wait time, which is programmed for 512 switching cycles, the device shuts down and restarts after the hiccup time of 16 384 cycles. The hiccup mode helps to reduce the device power dissipation under severe overcurrent conditions.

### **Thermal Shutdown**

The internal thermal-shutdown circuitry forces the device to stop switching if the junction temperature exceeds 160°C (typical). When the junction temperature drops below 140°C (typical), the internal thermal-hiccup timer begins to count. The device reinitiates the power-up sequence when the built-in thermal-shutdown hiccup time (16 384 cycles) is over.

### **Serial Interface Description**

The I<sup>2</sup>C is a 2-wire serial interface developed by Philips Semiconductor (see I<sup>2</sup>C-Bus Specification, Version 2.1, January 2000). The bus consists of a data line (SDA) and a clock line (SCL) with pullup structures. When the bus is idle, both SDA and SCL lines are pulled high. All of the I<sup>2</sup>C compatible devices connect to the I<sup>2</sup>C bus through open-drain I/O pins, SDA, and SCL. A master device, typically a microcontroller or a digital signal processor, controls the bus. The master is responsible for generating the SCL signal and device addresses. The master also generates specific conditions that indicate the START and STOP of data transfer. A slave device receives, transmits, or both receives and transmits data on the bus under control of the master device.

The TPS563900 device works as a slave and supports the following data transfer modes as defined in the I<sup>2</sup>C-Bus Specification: standard mode (100 kbps) and fast mode (400 kbps). The interface adds flexibility to the power-supply solution which enables most functions to be programmed to new values based on the instantaneous application requirements. Register contents remain intact as long as supply voltage remains above 4.5 V (typical).

The data transfer protocol for standard and fast modes is exactly the same, and therefore they are referred to as F/S-mode in this document. The TPS563900 device supports 7-bit addressing. The TPS563900 does not support 10-bit addressing and general call address.

The TPS563900 device has a 7-bit address with the two least-significant bits (LSB) bits set by the ADDR pin. Connecting ADDR to ground sets the address 0x60H, connecting ADDR to high sets the address 0x61H. Leaving this pin open sets the address 0x62H.

Table 1. I<sup>2</sup>C Address Selection

| ADDR PIN          | I <sup>2</sup> C ADDRESS |

|-------------------|--------------------------|

| Connect to ground | 0x60H                    |

| Open              | 0x61H                    |

| Connect to high   | 0x62H                    |

Figure 28. I<sup>2</sup>C Interface Timing Diagram

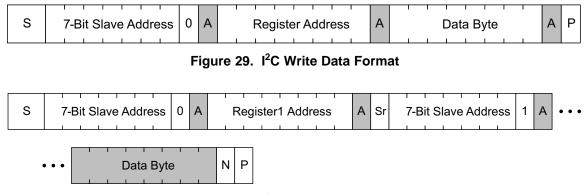

### TPS563900 I<sup>2</sup>C Update Sequence

The TPS563900 device requires a start condition, a valid I<sup>2</sup>C address, a register address byte, and a data byte for a single update. After the receipt of each byte, the TPS563900 device acknowledges by pulling the SDA line low during the high period of a single clock pulse. A valid I<sup>2</sup>C address selects the TPS563900 device. The TPS563900 device performs an update on the falling edge of the LSB byte.

When the TPS563900 device is in hardware shutdown (EN1 and EN2 pin tied to ground) the device cannot be updated through the  $I^2C$  interface. Conversely, the  $I^2C$  interface is fully functional during software shutdown (EN1 and EN2 bit = 0).

Figure 30. I<sup>2</sup>C Read Data Format

A: Acknowledge

N: Not Acknowledge

S: Start System Host

P: Stop

Sr: Repeated Start Chip

### **Register Description**

The following tables list the register descriptions.

**Table 2. Register Addresses**

| NAME       | BITS | ADDRESS |

|------------|------|---------|

| VOUT1_SEL  | 8    | 0x00H   |

| VOUT2_SEL  | 8    | 0x01H   |

| VOUT1_COM  | 8    | 0x02H   |

| VOUT2_COM  | 8    | 0x03H   |

| Sys_STATUS | 8    | 0x04H   |

### **Table 3. VOUT1 Voltage Selection Register**

|                | NUMBER OF BITS | ACCESS | NAME       | DEFAULT VALUE | DESCRIPTION                                                        |

|----------------|----------------|--------|------------|---------------|--------------------------------------------------------------------|

| VOUT1_SEL      | 7              |        |            |               | 10-mV step, from 0.68 V to 1.95 V                                  |

| address: 0x00H | Bit 7          | R/W    | VOUT1_Bit7 | 0             | GO bit, must be set '1' to enable I <sup>2</sup> C voltage control |

|                | Bit 6          | R/W    | VOUT1_Bit6 | 0             |                                                                    |

|                | Bit 5          | R/W    | VOUT1_Bit5 | 0             |                                                                    |

|                | Bit 4          | R/W    | VOUT1_Bit4 | 0             |                                                                    |

|                | Bit 3          | R/W    | VOUT1_Bit3 | 0             | 0x00H: 0.68 V; 0x7FH: 1.95 V                                       |

|                | Bit 2          | R/W    | VOUT1_Bit2 | 0             |                                                                    |

|                | Bit 1          | R/W    | VOUT1_Bit1 | 0             |                                                                    |

| _              | Bit 0          | R/W    | VOUT1_Bit0 | 0             |                                                                    |

### Table 4. VOUT2 Voltage Selection Register

|                | NUMBER OF BITS | ACCESS | NAME       | DEFAULT VALUE | DESCRIPTION                                                        |

|----------------|----------------|--------|------------|---------------|--------------------------------------------------------------------|

| VOUT2_SEL      | 7              |        |            |               | 10-mV step, from 0.68 V to 1.95 V                                  |

| address: 0x01H | Bit 7          | R/W    | VOUT2_Bit7 | 0             | GO bit, must be set '1' to enable I <sup>2</sup> C voltage control |

|                | Bit 6          | R/W    | VOUT2_Bit6 | 0             |                                                                    |

|                | Bit 5          | R/W    | VOUT2_Bit5 | 0             |                                                                    |

|                | Bit 4          | R/W    | VOUT2_Bit4 | 0             |                                                                    |

|                | Bit 3          | R/W    | VOUT2_Bit3 | 0             | 0x00H: 0.68 V; 0x7FH: 1.95 V                                       |

|                | Bit 2          | R/W    | VOUT2_Bit2 | 0             |                                                                    |

|                | Bit 1          | R/W    | VOUT2_Bit1 | 0             |                                                                    |

|                | Bit 0          | R/W    | VOUT2_Bit0 | 0             |                                                                    |

## **Table 5. VOUT1 Command Register**

|                | NUMBER OF BITS | ACCESS | NAME           | DEFAULT VALUE | DESCRIPTION                                                                                                                                      |

|----------------|----------------|--------|----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| VOUT1_COM      | 8              |        |                |               |                                                                                                                                                  |

| address: 0x02H | Bit 7          |        |                |               | Reserved                                                                                                                                         |

|                | Bit 6          | R/W    | Slew Rate 3    | 0             | VOUT slew rate control.                                                                                                                          |

|                | Bit 5          | R/W    | Slew Rate 2    | 0             | 000: 10 mV/cycle;<br>001: 10 mV/2 cycles;                                                                                                        |

|                | Bit 4          | R/W    | Slew Rate 1    | 0             | 010: 10 mV/4 cycles;<br>011: 10 mV/8 cycles;<br>100: 10 mV/16 cycles;<br>101: 10 mV/32 cycles;<br>110: 10 mV/64 cycles;<br>111: 10 mV/128 cycles |

|                | Bit 3          | R/W    | Soft Discharge | 0             | 0: Disable Soft Discharge<br>1: Enable Soft Discharge                                                                                            |

|                | Bit 2          | R/W    | PSM Mode       | 0             | 00: select by MODE pin;                                                                                                                          |

|                | Bit 1          | R/W    | PSM Mode       | 0             | 01: forced PWM mode;<br>10: auto PSM-PWM mode;<br>11: reserved                                                                                   |

|                | Bit 0          | R/W    | Disable1       | 0             | 0: output enabled;<br>1: output disabled                                                                                                         |

### **Table 6. VOUT2 Command Register**

|                | NUMBER OF BITS | ACCESS | NAME           | DEFAULT VALUE | DESCRIPTION                                                                                                                                      |

|----------------|----------------|--------|----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| VOUT2_COM      | 8              |        |                |               |                                                                                                                                                  |

| address: 0x03H | Bit 7          |        |                |               | Reserved                                                                                                                                         |

|                | Bit 6          | R/W    | Slew Rate 3    | 0             | VOUT slew-rate control.                                                                                                                          |

|                | Bit 5          | R/W    | Slew Rate 2    | 0             | 000: 10 mV/cycle;<br>001: 10 mV/2 cycles;                                                                                                        |

|                | Bit 4          | R/W    | Slew Rate 1    | 0             | 010: 10 mV/4 cycles;<br>011: 10 mV/8 cycles;<br>100: 10 mV/16 cycles;<br>101: 10 mV/32 cycles;<br>110: 10 mV/64 cycles;<br>111: 10 mV/128 cycles |

|                | Bit 3          | R/W    | Soft Discharge | 0             | Disable Soft Discharge     Enable Soft Discharge                                                                                                 |

|                | Bit 2          | R/W    | PSM Mode       | 0             | 00: select by MODE pin;                                                                                                                          |

|                | Bit 1          | R/W    | PSM Mode       | 0             | 10: forced PWM mode;<br>10: auto PSM-PWM mode;<br>11: reserved                                                                                   |

|                | Bit 0          | R/W    | Disable2       | 0             | 0: output enabled;<br>1: output disabled                                                                                                         |

### **Table 7. System Status Register**

|                | NUMBER OF BITS | ACCESS | NAME                          | DEFAULT VALUE | DESCRIPTION                                                                          |

|----------------|----------------|--------|-------------------------------|---------------|--------------------------------------------------------------------------------------|

| SYS_STATUS     | 8              |        |                               |               |                                                                                      |

| address: 0x04H | Bit 7          |        |                               |               | Reserved                                                                             |

|                | Bit 6          |        |                               |               | Reserved                                                                             |

|                | Bit 5          |        |                               |               | Reserved                                                                             |

|                | Bit 4          |        |                               |               | Reserved                                                                             |

|                | Bit 3          |        |                               |               | Reserved                                                                             |

|                | Bit 2          | R      | Temperature Warning (> 125°C) | 0             | 1: Die temperature over 125°C;<br>0: Die temperature below 125°C                     |

|                | Bit 1          | R      | PGOOD2                        | 0             | 0: VOUT2 in power good regulation range; 1: VOUT2 not in power good regulation range |

|                | Bit 0          | R      | PGOOD 1                       | 0             | 0: VOUT1 in power good regulation range; 1: VOUT1 not in power good regulation range |

# Table 8. Vout1 and Vout2 Output Voltage Setting

| VOUT_SEL<br><6:0> | OUTPUT<br>VOLTAGE (V) |

|-------------------|-----------------------|-------------------|-----------------------|-------------------|-----------------------|-------------------|-----------------------|

| 0                 | 0.68                  | 20                | 1                     | 40                | 1.32                  | 60                | 1.64                  |

| 1                 | 0.69                  | 21                | 1.01                  | 41                | 1.33                  | 61                | 1.65                  |

| 2                 | 0.7                   | 22                | 1.02                  | 42                | 1.34                  | 62                | 1.66                  |

| 3                 | 0.71                  | 23                | 1.03                  | 43                | 1.35                  | 63                | 1.67                  |

| 4                 | 0.72                  | 24                | 1.04                  | 44                | 1.36                  | 64                | 1.68                  |

| 5                 | 0.73                  | 25                | 1.05                  | 45                | 1.37                  | 65                | 1.69                  |

| 6                 | 0.74                  | 26                | 1.06                  | 46                | 1.38                  | 66                | 1.7                   |

| 7                 | 0.75                  | 27                | 1.07                  | 47                | 1.39                  | 67                | 1.71                  |

| 8                 | 0.76                  | 28                | 1.08                  | 48                | 1.4                   | 68                | 1.72                  |

| 9                 | 0.77                  | 29                | 1.09                  | 49                | 1.41                  | 69                | 1.73                  |

| Α                 | 0.78                  | 2A                | 1.1                   | 4A                | 1.42                  | 6A                | 1.74                  |

| В                 | 0.79                  | 2B                | 1.11                  | 4B                | 1.43                  | 6B                | 1.75                  |

| С                 | 0.8                   | 2C                | 1.12                  | 4C                | 1.44                  | 6C                | 1.76                  |

| D                 | 0.81                  | 2D                | 1.13                  | 4D                | 1.45                  | 6D                | 1.77                  |

| E                 | 0.82                  | 2E                | 1.14                  | 4E                | 1.46                  | 6E                | 1.78                  |

| F                 | 0.83                  | 2F                | 1.15                  | 4F                | 1.47                  | 6F                | 1.79                  |

| 10                | 0.84                  | 30                | 1.16                  | 50                | 1.48                  | 70                | 1.8                   |

| 11                | 0.85                  | 31                | 1.17                  | 51                | 1.49                  | 71                | 1.81                  |

| 12                | 0.86                  | 32                | 1.18                  | 52                | 1.5                   | 72                | 1.82                  |

| 13                | 0.87                  | 33                | 1.19                  | 53                | 1.51                  | 73                | 1.83                  |

| 14                | 0.88                  | 34                | 1.2                   | 54                | 1.52                  | 74                | 1.84                  |

| 15                | 0.89                  | 35                | 1.21                  | 55                | 1.53                  | 75                | 1.85                  |

| 16                | 0.9                   | 36                | 1.22                  | 56                | 1.54                  | 76                | 1.86                  |

| 17                | 0.91                  | 37                | 1.23                  | 57                | 1.55                  | 77                | 1.87                  |

| 18                | 0.92                  | 38                | 1.24                  | 58                | 1.56                  | 78                | 1.88                  |

| 19                | 0.93                  | 39                | 1.25                  | 59                | 1.57                  | 79                | 1.89                  |

| 1A                | 0.94                  | 3A                | 1.26                  | 5A                | 1.58                  | 7A                | 1.9                   |

| 1B                | 0.95                  | 3B                | 1.27                  | 5B                | 1.59                  | 7B                | 1.91                  |

| 1C                | 0.96                  | 3C                | 1.28                  | 5C                | 1.6                   | 7C                | 1.92                  |

| 1D                | 0.97                  | 3D                | 1.29                  | 5D                | 1.61                  | 7D                | 1.93                  |

| 1E                | 0.98                  | 3E                | 1.3                   | 5E                | 1.62                  | 7E                | 1.94                  |