# 带有脉宽调制 (PWM) 接口和自动相移的用于笔记本电脑的白光发光二级管 (WLED) 驱动器

查询样品: TPS61187

#### 特性

- 4.5V 至 24V 输入电压

- 38V 最大输出电压

- 集成的 2A 40V 金属氧化物半导体场效应晶体管 (MOSFET)

- 300 kHz 至 1 MHz 的可编程开关频率

- 自适应升压输出至 WLED 电压

- 宽 PWM 调光频率范围

- 直接 PWM 模式下为 100Hz 至 50KHz

- 频率可编程模式下为 100Hz 至 22KHz

- 20kHz 时的调光比为 100:1

- 200kHz 时的调光比为 1000:1 (直接 PWM 模式)

- 小型外部组件

- 集成环路补偿

- 六个 30mA (最大值) 电流吸入器

- 1.5% 的电流匹配(典型值)

- PWM 亮度界面控制

- PWM 相移模式亮度调节方法或者直接 PWM 调光方法

- 4kV 人体模型 (HBM) 静电放电 (ESD) 保护

- 可编程过压阀值

- 内置 WLED 开路/短路保护

- 热关断

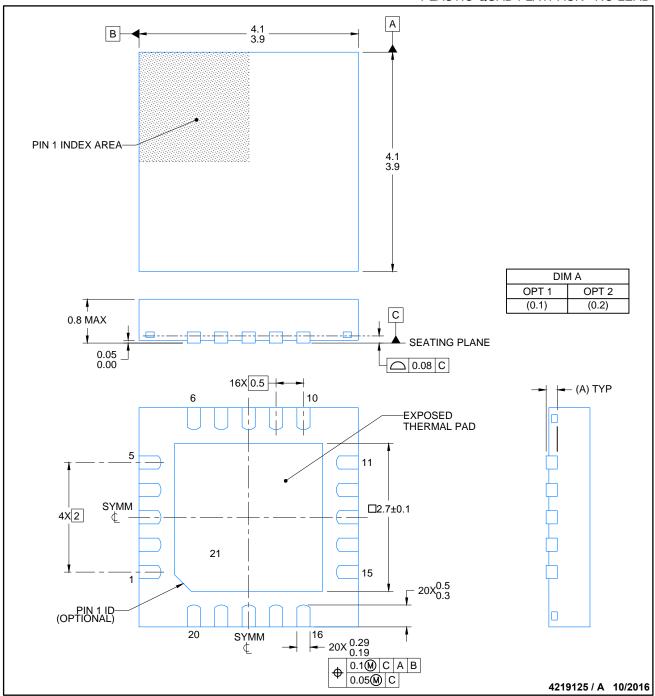

- 20 引脚 4mm x 4mm x 0.8mm 薄型四方扁平无引 线 (TQFN) 封装

#### 应用范围

笔记本电脑 LCD 显示器背光源

#### 说明

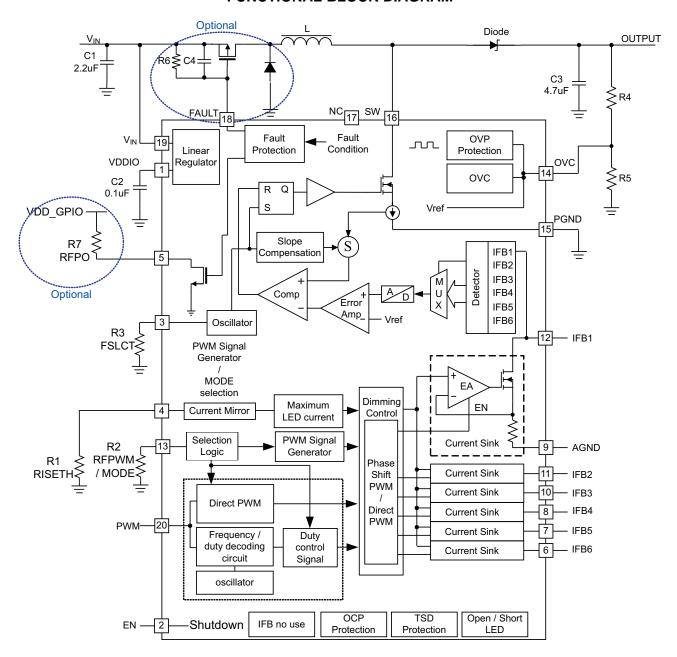

TPS61187 IC 为笔记本电脑 LCD 背光提供了一个高度集成的 WLED 驱动器解决方案。 这个器件具有一个内置的高效升压稳压器,此稳压器具有集成的 2.0A/40V 功率 MOSFET。 6 个电流宿稳压器提供了高精度的电流调节和匹配。 该器件总共能够支持多达 60 个 WLED。 此外,升压输出还可自动地将其电压调节至 WLED 正向电压以优化效率。

TPS61187 支持自动相移亮度调节方法和直接 PWM 亮度调节方法。 在相移 PWM 亮度调节期间,WLED 电流在由输入 PWM 信号控制的占空比上被接通/关闭并且根据集成脉宽调制 (PWM) 信号确定的频率,每个通道被移位。 这个信号的频率可由电阻器进行编程,同时占空比由一个输入到 PWM 引脚的外部 PWM 信号直接控制。 在直接 PWM 亮度调节期间,WLED 电流被与输入 PWM 信号同步接通/关闭。

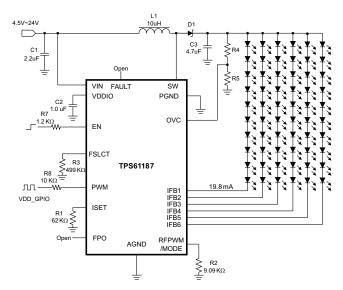

图 1. 典型应用-相移 PWM 模式

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### PACKAGE INFORMATION(1)

| PACKAGE     | PACKAGE MARKING |

|-------------|-----------------|

| TPS61187RTJ | TPS61187        |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                              |                       | VAL  | VALUE                         |      |

|------------------------------|-----------------------|------|-------------------------------|------|

|                              |                       | MIN  | MAX                           | UNIT |

|                              | VIN, FAULT            | -0.3 | 24                            | ٧    |

|                              | FPO                   | -0.3 | 7                             | >    |

| Voltage range (2)            | SW                    | -0.3 | 40                            | ٧    |

| voltage range V              | EN, PWM, IFB1 to IFB4 | -0.3 | 20                            | ٧    |

|                              | VDDIO                 | -0.3 | 3.7                           | ٧    |

|                              | All other pins        | -0.3 | 3.6                           | ٧    |

| HBM ESD rating               | •                     |      | 4                             |      |

| MM ESD rating                |                       |      | 200                           |      |

| CDM ESD rating               |                       |      | 1.5                           | kV   |

| Continuous power dissipation |                       |      | See Thermal Information Table |      |

| Operating junction temp      | erature range         | -40  | -40 150 °                     |      |

| Storage temperature ra       | nge                   | -65  | <b>-65</b> 150                |      |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

over ooperating free-air temperature range (unless otherwise noted)

|                    |                                                          | MIN | NOM | MAX               | UNIT |

|--------------------|----------------------------------------------------------|-----|-----|-------------------|------|

| V <sub>IN</sub>    | Input voltage range                                      | 4.5 |     | 24                | V    |

| V <sub>OUT</sub>   | Output voltage range                                     | VIN |     | 38                | V    |

| L1                 | Inductor, 600 kHz ~ 1 MHz switching frequency            | 10  |     | 22                | μΗ   |

| L1                 | Inductor, 300 kHz ~ 600 kHz swtching frequency           | 22  |     | 47                | μΗ   |

| C <sub>I</sub>     | Input capacitor                                          | 1   |     |                   | μF   |

| Co                 | Output capacitor                                         | 1.0 | 4.7 | 10                | μF   |

| F <sub>PWM_O</sub> | IFBx PWM dimming frequency - frequency programmable mode | 0.1 |     | 22 <sup>(1)</sup> | KHz  |

| F <sub>PWM_O</sub> | IFBx PWM dimming frequency - direct PWM mode             | 0.1 |     | 50                | KHz  |

| F <sub>PWM_I</sub> | PWM input signal frequency                               | 0.1 |     | 22                | KHz  |

| F <sub>BOOST</sub> | Boost regulator switching frequency                      | 300 |     | 1000              | KHz  |

| T <sub>A</sub>     | Operating free-air temperature                           | -40 |     | 85                | °C   |

| TJ                 | Operating junction temperature                           | -40 |     | 125               | °C   |

<sup>(1) 5</sup> µs min pulse on time.

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

#### THERMAL INFORMATION

|                         |                                              | TPS61187 |       |

|-------------------------|----------------------------------------------|----------|-------|

|                         | THERMAL METRIC <sup>(1)</sup>                | RTJ      | UNITS |

|                         |                                              | 20       |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 39.9     |       |

| $\theta_{JC(top)}$      | Junction-to-case(top) thermal resistance     | 34.0     |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 9.9      | 9C/M  |

| ΨЈТ                     | Junction-to-top characterization parameter   | 0.6      | °C/W  |

| ΨЈВ                     | Junction-to-board characterization parameter | 9.5      |       |

| θ <sub>JC(bottom)</sub> | Junction-to-case(bottom) thermal resistance  | 2        |       |

#### (1) 有关传统和新的热度量的更多信息,请参阅 *IC 封装热度量* 应用报告 SPRA953。

#### **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V, PWM/EN = high, IFB current = 20mA, IFB voltage = 500mV,  $T_A$  = -40°C to 85°C, typical values are at  $T_A$  = 25°C (unless otherwise noted)

| PARAMETER            |                                                          | TEST CONDITIONS                                                   | MIN   | TYP   | MAX   | UNIT |

|----------------------|----------------------------------------------------------|-------------------------------------------------------------------|-------|-------|-------|------|

| SUPPLY CU            | RRENT                                                    |                                                                   |       |       |       |      |

| V <sub>IN</sub>      | Input voltage range                                      |                                                                   | 4.5   |       | 24    | V    |

| I <sub>q_VIN</sub>   | Operating quiescent current into Vin                     | Device enable, switching 1MHz and no load, V <sub>IN</sub> = 24 V |       |       | 4.0   | mA   |

| VDDIO                | VDDIO pin output voltage                                 | Iload = 5 mA                                                      | 3.0   | 3.3   | 3.6   | V    |

|                      | Chutdayin ayınant                                        | V <sub>IN</sub> = 12 V , EN = low                                 |       |       | 11    |      |

| I <sub>SD</sub>      | Shutdown current                                         | V <sub>IN</sub> = 24 V, EN = low                                  |       |       | 16    | μA   |

| .,                   | Vdenelte ere le el est thue ele el el                    | V <sub>IN</sub> ramp down                                         |       |       | 3.50  | V    |

| V <sub>IN_UVLO</sub> | V <sub>IN</sub> under-voltage lockout threshold          | V <sub>IN</sub> ramp up                                           |       |       | 3.75  | V    |

| V <sub>IN_Hys</sub>  | V <sub>IN</sub> under-voltage lockout hysterisis         |                                                                   |       | 250   |       | mV   |

| PWM                  |                                                          |                                                                   | •     |       |       |      |

| V <sub>H</sub>       | EN Logic high threshold                                  | EN                                                                | 2.1   |       |       |      |

| $V_L$                | EN Logic low threshold                                   | EN                                                                |       |       | 0.8   |      |

| V <sub>H</sub>       | PWM Logic high threshold                                 | PWM                                                               | 2.1   |       |       |      |

| V <sub>L</sub>       | PWM Logic low threshold                                  | PWM                                                               |       |       | 0.8   |      |

| R <sub>PD</sub>      | Pull down resistor on PWM and EN                         |                                                                   | 400   | 800   | 1600  | kΩ   |

| CURRENT R            | REGULATION                                               |                                                                   |       |       |       |      |

| V <sub>ISET</sub>    | ISET pin voltage                                         |                                                                   | 1.204 | 1.229 | 1.253 | V    |

| K <sub>ISET</sub>    | Current multiplier                                       |                                                                   |       | 980   |       | -    |

|                      | 0                                                        | I <sub>ISET</sub> = 20 μA, 0°C to 70°C                            | -2%   |       | 2%    | -    |

| I <sub>FB</sub>      | Current accuracy                                         | I <sub>ISET</sub> = 20 μA, -40°C to 85°C                          | -2.3% |       | 2.3%  |      |

| K <sub>m</sub>       | (I <sub>max</sub> –I <sub>min</sub> ) / I <sub>AVG</sub> | I <sub>ISET</sub> = 20 μA                                         |       | 1.3%  |       | -    |

|                      | IED win lastrana arment                                  | IFB voltage = 15 V, each pin                                      |       | 2     | 5     |      |

| I <sub>leak</sub>    | IFB pin leakage current                                  | IFB voltage = 5 V, each pin                                       |       | 1     | 2     | μA   |

| I <sub>IFB_max</sub> | Current sink max output current                          | IFB = 350 mV                                                      | 30    |       |       | mA   |

| f <sub>dim</sub>     | PWM dimming frequency                                    | R <sub>FPWM</sub> = 9.09 kΩ                                       |       | 20    |       | kHz  |

|                      | FPUT REGULATION                                          |                                                                   |       |       |       |      |

| V <sub>IFB_L</sub>   | Output voltage up threshold                              | Measured on V <sub>IFB(min)</sub>                                 |       | 350   |       | mV   |

| V <sub>IFB_H</sub>   | Ouput voltage down threshold                             | Measured on V <sub>IFB(min)</sub>                                 |       | 650   |       | mV   |

| POWER SW             | ІТСН                                                     |                                                                   | 1     |       |       |      |

| R <sub>PWM_SW</sub>  | PWM FET on-resistance                                    | V <sub>IN</sub> = 12 V                                            |       | 0.25  | 0.35  | Ω    |

| I <sub>LN_NFET</sub> | PWM FET leakage current                                  | V <sub>SW</sub> = 40 V, T <sub>A</sub> = 25°C                     |       |       | 2     | μA   |

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN}$  = 12V, PWM/EN = high, IFB current = 20mA, IFB voltage = 500mV,  $T_A$  = -40°C to 85°C, typical values are at  $T_A$  = 25°C (unless otherwise noted)

| PARAMETER               |                                       | TEST CONDITIONS                                                | MIN  | TYP  | MAX  | UNIT |

|-------------------------|---------------------------------------|----------------------------------------------------------------|------|------|------|------|

| OSCILLATOR              |                                       |                                                                |      |      |      |      |

| f <sub>S</sub>          | Oscillator frequency                  | $R_{FSW} = 499 \text{ k}\Omega$                                | 0.8  | 1.0  | 1.2  | MHz  |

| D <sub>max</sub>        | Maximum duty cycle                    | IFB = 0                                                        |      | 94%  |      |      |

| OC, SC, OVP             | AND SS                                |                                                                |      |      |      |      |

| I <sub>LIM</sub>        | N-Channel MOSFET current limit        | D = D <sub>max</sub>                                           | 2.0  |      | 3.0  | Α    |

| V <sub>CLAMP_TH</sub>   | Ouput voltage clamp program threshold |                                                                | 1.90 | 1.95 | 2.00 | V    |

| V <sub>OVP_IFB</sub>    | IFB overvoltage threshold             | Measured on the IFBx pin, IFB on                               | 12   | 13.5 | 15   | V    |

| FPO, FAULT              |                                       |                                                                |      |      |      |      |

| V <sub>FPO_L</sub>      | FPO Logic low voltage                 | I_SOURCE = 0.5 mA                                              |      |      | 0.4  | V    |

| V <sub>FAULT_HIGH</sub> | Fault high voltage                    | Measured as V <sub>IN</sub> – V <sub>FAULT</sub>               |      | 0.1  |      | V    |

| V <sub>FAULT_LOW</sub>  | Fault low voltage                     | Measured as V <sub>IN</sub> – V <sub>FAULT</sub> , Sink, 10 μA | 6    | 8    | 10   | V    |

| I <sub>FAULT</sub>      | Maximum sink current                  | V <sub>IN</sub> – V <sub>FAULT</sub> = 0 V                     |      | 20   |      | μΑ   |

| THERMAL SH              | UTDOWN                                |                                                                |      |      |      |      |

| _                       | Thermal shutdown threshold            |                                                                |      | 150  |      | °C   |

| T <sub>shutdown</sub>   | Thermal shutdown hysteresis           |                                                                |      | 15   |      | °C   |

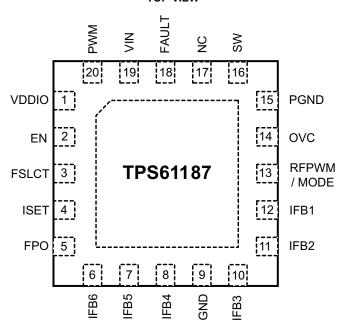

#### **DEVICE INFORMATION**

# 20 PIN 4mm × 4mm RTJ PACKAGE TOP VIEW

PowerPAD information goes here.

#### **PIN FUNCTIONS**

| P               | PIN DESCRIPTION    |                                                                                                 |  |  |  |  |

|-----------------|--------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME            | NO.                | DESCRIPTION                                                                                     |  |  |  |  |

| VDDIO           | 1                  | Internal pre_regulator. Connect a 1.0 µF ceramic capacitor to VDDIO.                            |  |  |  |  |

| EN              | 2                  | Enable                                                                                          |  |  |  |  |

| FSLCT           | 3                  | Switching frequency selection pin. Use a resistor to set the frequency between 300kHz to 1.0MHz |  |  |  |  |

| ISET            | 4                  | Full-scale LED current set pin. Connecting a resistor to the pin programs the current level.    |  |  |  |  |

| FPO             | 5                  | Fault protection output to indicate fault conditions including OVP, OC, and OT                  |  |  |  |  |

| IFB1 to IFB6    | 6,7,8,<br>10,11,12 | Regulated current sink input pins                                                               |  |  |  |  |

| GND             | 9,                 | Analog ground                                                                                   |  |  |  |  |

| RFPWM /<br>MODE | 13                 | Dimming frequency program pin with an external resistor / mode selection, see (1)               |  |  |  |  |

| OVC             | 14                 | Over-voltage clamp pin / voltage feedback, see (1)                                              |  |  |  |  |

| PGND            | 15                 | Power ground                                                                                    |  |  |  |  |

| SW              | 16                 | Drain connection of the internal power FET                                                      |  |  |  |  |

| NC              | 17                 | No connection                                                                                   |  |  |  |  |

| FAULT           | 18                 | Fault pin to drive external ISO FET                                                             |  |  |  |  |

| VIN             | 19                 | Supply input pin                                                                                |  |  |  |  |

| PWM             | 20                 | PWM signal input pin                                                                            |  |  |  |  |

(1) See Application Information section for details.

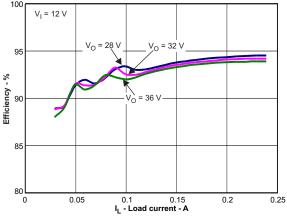

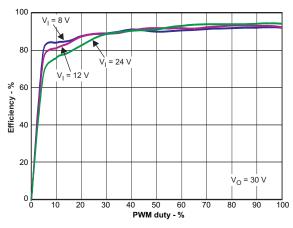

#### **TYPICAL CHARACTERISTICS**

#### **TABLE OF GRAPHS**

| TITLE                                                        | DESCRIPTION                                                                                                                                             | FIGURE    |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Efficiency vs Load current by output voltage                 | V <sub>IN</sub> = 12 V, V <sub>OUT</sub> = 28 V, 32 V, 36 V, L = 10 μH                                                                                  | Figure 2  |

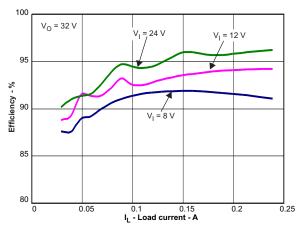

| Efficiency vs Load current by input voltage                  | V <sub>OUT</sub> = 32 V , V <sub>IN</sub> = 8 V, 12 V, 24 V, L = 10 μH                                                                                  | Figure 3  |

| Efficiency vs PWM duty                                       | $V_{OUT}$ = 32 V , $V_{IN}$ = 8 V, 12 V, 24 V, $F_{DIM}$ = 200 Hz, L = 10 $\mu$ H, $R_{ISET}$ = 62 $k\Omega$                                            | Figure 4  |

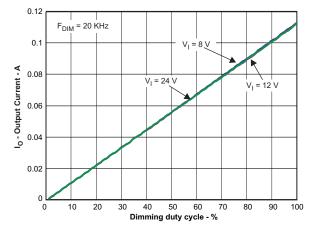

| Dimming linearity                                            | $V_{OUT}$ = 32 V, $V_{IN}$ = 8 V, 12 V, 24 V, $F_{DIM}$ = 20 KHz, L = 10 $\mu$ H, $R_{ISET}$ = 62 $k\Omega$                                             | Figure 5  |

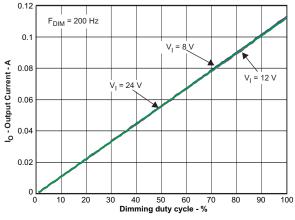

| Dimming linearity                                            | $V_{OUT} = 32 \text{ V}, V_{IN} = 8 \text{ V}, 12 \text{ V}, 24 \text{ V}, F_{DIM} = 200 \text{ Hz}, L = 10 \mu\text{H}, R_{ISET} = 62 \text{ k}\Omega$ | Figure 6  |

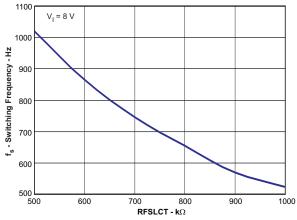

| Boost switching frequency                                    | $V_{IN}$ = 12 V, $V_{OUT}$ = 33.8 V, L = 10 $\mu$ H, $R_{ISET}$ = 62 $k\Omega$                                                                          | Figure 7  |

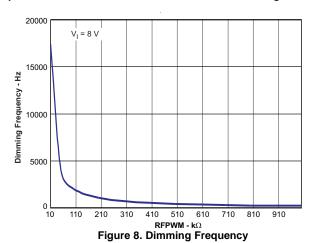

| Phase shift dimming frequency                                | $V_{IN}$ = 12 V, $V_{OUT}$ = 33.8 V, L = 10 $\mu$ H, $R_{ISET}$ = 62 $k\Omega$                                                                          | Figure 8  |

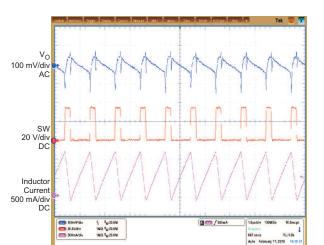

| Switch waveform                                              | $V_{IN} = 8 \text{ V}, V_{OUT} = 33.8 \text{ V}, F_{DIM} = 20 \text{ kHz}, Duty = 100\%, L = 10 \mu\text{H}, R_{ISET} = 62 \text{ k}\Omega$             | Figure 9  |

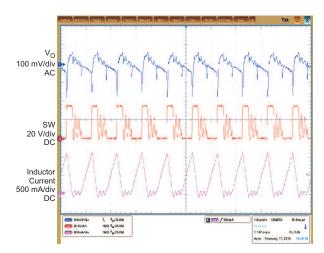

| Switch waveform                                              | $V_{IN}$ = 12 V, $V_{OUT}$ = 33.8 V, $F_{DIM}$ = 20 kHz, Duty = 100%, L = 10 $\mu$ H, $R_{ISET}$ = 62 $k\Omega$                                         | Figure 10 |

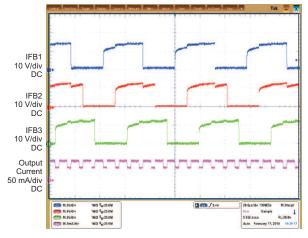

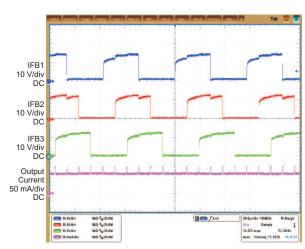

| Phase shift PWM dimming F <sub>DIM</sub> = 200Hz, duty = 50% | $V_{IN}$ = 12 V, $V_{OUT}$ = 33.8 V, $F_{DIM}$ = 20 kHz, Duty = 45%, L = 10 $\mu$ H, $R_{ISET}$ = 62 k $\Omega$                                         | Figure 11 |

| Phase shift PWM dimming F <sub>DIM</sub> = 20KHz, duty = 50% | $V_{IN}$ = 12 V, $V_{OUT}$ = 33.8 V, $F_{DIM}$ = 20 kHz, Duty = 51%, L = 10 $\mu$ H, $R_{ISET}$ = 62 $k\Omega$                                          | Figure 12 |

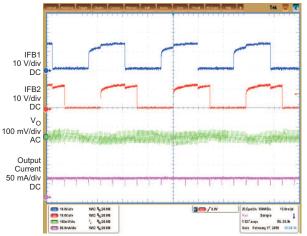

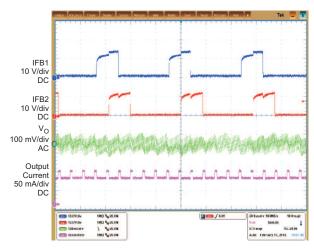

| Output ripple of Phase shift PWM dimming                     | $V_{IN}$ = 12 V, $V_{OUT}$ = 33.8 V, $F_{DIM}$ = 20 kHz, Duty = 50%, L = 10 $\mu$ H, $R_{ISET}$ = 62 $k\Omega$                                          | Figure 13 |

| Output ripple of Phase shift PWM dimming                     | $V_{IN}$ = 12 V, $V_{OUT}$ = 33.8 V, $F_{DIM}$ = 20 kHz, Duty = 70%, L = 10 $\mu$ H, $R_{ISET}$ = 62 $k\Omega$                                          | Figure 14 |

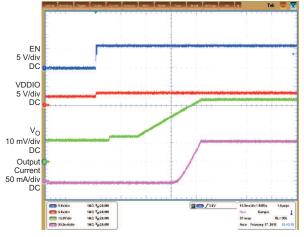

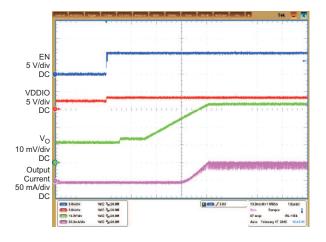

| Start up waveform                                            | $V_{IN}$ = 12 V, $V_{OUT}$ = 33.8 V, $F_{DIM}$ = 20 kHz, Duty = 100%, L = 10 $\mu$ H, $R_{ISET}$ = 62 $k\Omega$                                         | Figure 15 |

| Start up waveform                                            | $V_{IN} = 12 \text{ V}, V_{OUT} = 33.8 \text{ V}, F_{DIM} = 20 \text{ kHz}, Duty = 50\%, L = 10 \mu\text{H}, R_{ISET} = 62 \text{ k}\Omega$             | Figure 16 |

Figure 2. Efficiency

Figure 4. Efficiency

Figure 3. Efficiency

Figure 5. Output Current

Figure 6. Output Current

Figure 7. Switching Frequency

Figure 9. Switch Waveform

Figure 10. Switch Waveform

Figure 11. Phase Shift Waveform

Figure 12. Phase Shift Waveform

Figure 13. Output Ripple Waveform

Figure 14. Output Ripple Waveform

Figure 15. Start Up Waveform

Figure 16. Start Up Waveform

#### **FUNCTIONAL BLOCK DIAGRAM**

#### DETAILED DESCRIPTION

#### NORMAL OPERATION

The TPS61187 is a high efficiency, high output voltage white LED driver for notebook panel backlighting applications. The advantages of white LEDs compared to CCFL backlights are higher power efficiency and lower profile design. Due to the large number of white LEDs required to provide backlighting for medium to large display panels, the LEDs must be arranged in parallel strings of several LEDs in series. Therefore, the backlight driver for battery powered systems is almost always a boost regulator with multiple current sink regulators. Having more white LEDs in series reduces the number of parallel strings and therefore improves overall current matching. However, the efficiency of the boost regulator declines due to the need for high output voltage. Also, there must be enough white LEDs in series to ensure the output voltage stays above the input voltage range.

The TPS61187 IC has integrated all of the key function blocks to power and control up to 60 white LEDs. The device includes a 40 V / 2 A boost regulator, six 30 mA current sink regulators, and a protection circuit for over-current, over-voltage, Open LED, Short LED, and output short circuit failures.

The TPS61187 integrates auto phase shifted PWM dimming methods with the PWM interface to reduce the output ripple voltage and audible noise. An optional direct PWM mode is user selectable through the MODE selection function.

#### SUPPLY VOLTAGE

The TPS61187 IC has a built-in linear regulator to supply the IC analog and logic circuit. The VDDIO pin, output of the regulator, is connected to a 1  $\mu$ F bypass capacitor for the regulator to be controlled in a stable loop. VDDIO does not have high current sourcing capability for external use but it can be tied to the EN pin for start up.

#### **BOOST REGULATOR AND PROGRAMMABLE SWITCH FREQUENCY (FSCLT)**

The fixed-frequency PWM boost converter uses current-mode control and has integrated loop compensation. The internal compensation ensures stable output over the full input and output voltage ranges assuming the recommended inductance and output capacitance values shown in the Typical Application – Phase Shift PWM Mode figure are used. The output voltage of the boost regulator is automatically set by the IC to minimize voltage drop across the IFB pins. The IC regulates the lowest IFB pin to 350 mV, and consistently adjusts the boost output voltage to account for any changes in LED forward voltages. If the input voltage is higher than the sum of the white LED forward voltage drops (e.g., at low duty cycles), the boost converter is not able to regulate the output due to its minimum duty cycle limitation. In this case, increase the number of WLEDs in series or include series ballast resistors in order to provide enough headroom for the converter to boost the output voltage. Since the TPS61187 integrates a 2.0A/40V power MOSFET, the boost converter can provide up to a 38 V output voltage.

The TPS61187 switching frequency can be programmed between 300 kHz to 1.0MHz by the resistor value on the FSLCT pin according to Equation 1:

$$F_{SW} = \frac{5 \times 10^{11}}{R_{FSLCT}} \tag{1}$$

Where:  $R_{FSLCT} = FSCLT$  pin resistor

See Figure 7 for boost converter switching frequency adjustment resistor R<sub>FSLCT</sub> selection.

The adjustable switching frequency feature provides the user with the flexibility of choosing a faster switching frequency, and therefore, an inductor with smaller inductance and footprint or slower switching frequency, and therefore, potentially higher efficiency due to lower switching losses. Use Equation 1 or refer to Table 1 to select the correct value:

Table 1. R<sub>FSLCT</sub> Recommendations

| R <sub>FLCT</sub> | F <sub>SW</sub> |

|-------------------|-----------------|

| 833K              | 600 KHz         |

| 625K              | 800 KHz         |

| 499K              | 1 MHz           |

#### LED CURRENT SINKS

The six current sink regulators embedded in the TPS61187 can be collectively configured to provide up to a maximum of 30 mA each. These six specialized current sinks are accurate to within ±2% max for currents at 20 mA, with a string-to-string difference of ±1.5% typical.

The IFB current must be programmed to the highest WLED current expected using the ISETH pin resistor and Equation 2.

$$I_{FB} = \frac{V_{ISETH}}{R_{ISETH}} \times K_{ISET}$$

(2)

Where:

K<sub>ISET</sub> = 980 (current multiple) V<sub>ISETH</sub> = 1.229V (ISETH pin voltage) R<sub>ISETH</sub> = ISETH pin resistor

#### **ENABLE AND STARTUP**

The internal regulator which provides VDDIO wakes up as soon as  $V_{IN}$  is applied even when EN is low. This allows the IC to start when EN is tied to the VDDIO pin. VDDIO does not come to full regulation until EN is high. The TPS61187 checks the status of all current feedback channels and shuts down any unused feedback channels. It is recommended to short the unused channels to ground for faster startup.

After the device is enabled, if the PWM pin is left floating, the output voltage of the TPS61187 regulates to the minimum output voltage. Once the IC detects a voltage on the PWM pin, the TPS61187 begins to regulate the IFB pin current, as pre-set per the ISETH pin resistor, according to the duty cycle of the signal on the PWM pin. The boost converter output voltage rises to the appropriate level to accommodate the sum of the white LED string with the highest forward voltage drops plus the headroom of the current sink at that current.

Pulling the EN pin low shuts down the IC, resulting in the IC consuming less than 11 μA in shutdown mode.

#### **IFB PIN UNUSED**

The TPS61187 has open/short string detection. For an unused IFB string, simply short it to ground or leave it open. Shorting unused IFB pins to ground for faster startup is recommended.

#### **BRIGHTNESS DIMMING CONTROL**

The TPS61187 has auto phase shifted PWM dimming control with the PWM control interface.

The internal decoder block detects duty information from the input PWM signal, saves it in an eight bit register and delivers it to the output PWM dimming control circuit. The output PWM dimming control circuit turns on/off six output current sinks at the PWM frequency set by RFPWM and the duty cycle from the decoder block.

The TPS61187 also has direct PWM dimming control with the PWM control interface. In direct PWM mode, each current sink turns on/off at the same frequency and duty cycle as the input PWM signal. See the *Mode Selection* section for dimming mode selection.

When in phase shifted PWM mode, it is recommended to insert a series resistor of  $10k\Omega$  to  $20k\Omega$  value close to PWMIN pin. This resistor together with an internal capacitor forms a low pass R-C filter with 30ns to 60ns time constant. This prevents possible high frequency noises being coupled into the input PWM signal and causing interference to the internal duty cycle decoding circuit. However, it is not necessary for direct PWM mode since the duty cycle decoding circuit is disabled during the direct PWM mode.

#### ADJUSTBLE PWM DIMMING FREQUENCY AND MODE SELECTION (R\_FPWM / MODE)

The TPS61187 can operate in auto phase shift mode or direct PWM mode. Tying the RFPWM/MODE pin to VDDIO forces the IC to operate in direct PWM mode. A resistor between the RFPWM/MODE pin and ground sets the IC into auto phase shift mode and the value of the resistor determines the PWM dimming frequency. Use Equation 3 or refer to Table 2 to select the correct value:

$$\mathsf{F}_{\mathsf{DIM}} = \frac{1.818 \times 10^8}{\mathsf{R}_{\mathsf{FPWM}}} \tag{3}$$

Where:  $R_{FPWM} = RFPWM$  pin resistor

**Table 2. R<sub>FPWM</sub> Recommendations**

| R <sub>FPWM</sub> | F <sub>DIM</sub> |

|-------------------|------------------|

| 866 kΩ            | 210 Hz           |

| 432 kΩ            | 420 Hz           |

| 174 kΩ            | 1.05 kHz         |

| 9.09 kΩ           | 20 kHz           |

#### MODE SELECTION – PHASE SHIFT PWM OR DIRECT PWM DIMMING

The phase shift PWM dimming method or direct PWM dimming method can be selected through the RFPWM pin. By attaching an external resistor to the RFPWM pin, the default phase shift PWM mode can be selected. To select direct PWM mode, the RFPWM pin needs to be tied to the VDDIO pin. The RFPWM/MODE pin can be noise sensitive when R2 has high impedance. In this case, careful layout or a parallel bypassing capacitor improves noise sensitivity but the value of the parallel capacitor may not exceed 33 pF for oscillator stability.

Figure 17. Phase Shift PWM Dimming Mode Selection

Figure 18. Direct PWM Dimming Mode Selection

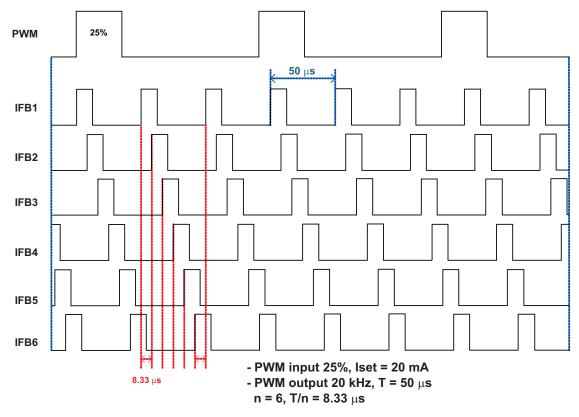

#### **PHASE SHIFT PWM DIMMING**

In phase shift PWM mode, all current feedback channels are turned on and off at F<sub>DIM</sub> frequency with a constant delay. However, the number of used channels and PWM dimming frequency determine the delay time between two neighboring channels per Equation 4.

$$T_{\text{delay}} = \frac{1}{n \times F_{\text{DIM}}}$$

(4)

Where: n is the number of used channels

F<sub>DIM</sub> is the PWM dimming frequency which is determined by the value of R<sub>FPWM</sub> on the RFPWM pin. Figure 19 provides the detailed timing diagram of the phase shift PWM dimming mode.

In phase shift PWM mode, the internal decoder converts the duty cycle information from the applied PWM signal at the PWM pin into an 8-bit digital signal and stores it into a register. The integrated dimming control circuit reconstructs the PWM duty cycle per the register value and sends it to each of the current sinks. In order to avoid any flickering while the duty cycle information is reconstructed from the register, one LSB (1/256) of duty cycle hysteresis is included which results in 1/256 resolution when incrementing the applied signal's duty cycle but 2/256 resolution when decrementing the duty cycle.

Figure 19. Phase Shift PWM Dimming Timing Diagram

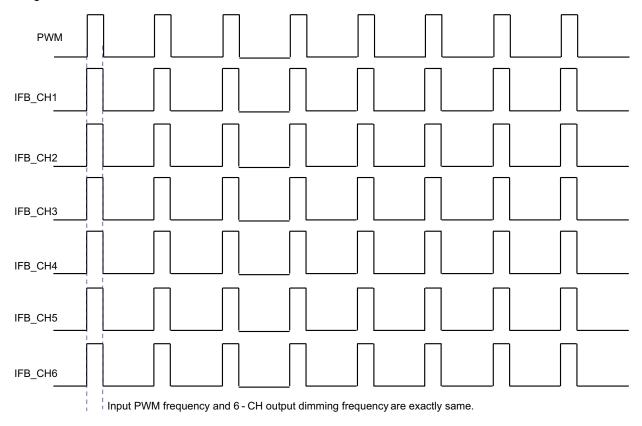

#### DIRECT PWM DIMMING

In direct PWM mode, all current feedback channels are turned on and off and are synchronized with the input PWM signal.

Figure 20. Direct PWM Dimming Timing Diagram

#### OVER VOLTAGE CLAMP / VOLTAGE FEEDBACK (OVC / FB)

The correct divider ratio is important for optimum operation of the TPS61187. Use the following guidelines to choose the divider value. It can be noise sensitive if  $R_{upper}$  and  $R_{down}$  have high impedance. Careful layout is required. Also, choose lower resistance values for  $R_{upper}$  and  $R_{down}$  when power dissipation allows.

Step1. Determine the maximum output voltage, Vo, for the system according to the number of series WLEDs.

Step2. Select an  $R_{upper}$  resistor value (1  $M\Omega$  for a typical application; a lower value such as 100  $k\Omega$  for a noisy environment).

Step3. Calculate R<sub>down</sub> using Equation 5.

$$V_{OVP} = \left(\frac{R_{upper}}{R_{down}} + 1\right) \times V_{OV\_TH}$$

(5)

Where:  $V_{OV TH} = 1.95 V$

When the IC detects that the OVC pin exceeds 1.95 V typical, indicating that the output voltage is over the set threshold point, the OVC circuitry clamps the output voltage to the set threshold.

#### **CURRENT SINK OPEN PROTECTION**

For the TPS61187, if one of the WLED strings is open, the IC automatically detects and disables that string. The IC detects the open WLED string by sensing no current in the corresponding IFB pin. As a result, the IC deactivates the open IFB pin and removes it from the voltage feedback loop. Subsequently, the output voltage drops and is regulated to the minimum voltage required for the connected WLED strings. The IFB current of the connected WLED strings remains in regulation.

If any IFB pin voltage exceeds the IFB over-voltage threshold (13.5 V typical), the IC turns off the corresponding current sink and removes this IFB pin from the regulation loop. The current regulation of the remaining IFB pins is not affected. This condition often occurs when there are several shorted WLEDs in one string. WLED mismatch typically does not create large voltage differences among WLED strings.

The IC only shuts down if it detects that all of the WLED strings are open. If an open string is reconnected again, a power-on reset (POR) or EN pin toggling is required to reactivate a previously deactivated string.

#### OVER CURRENT AND SHORT CIRCUIT PROTECTION

The TPS61187 has a pulse-by-pulse over-current limit of 2.0 A (min). The PWM switch turns off when the inductor current reaches this current threshold. The PWM switch remains off until the beginning of the next switching cycle. This protects the IC and external components during on overload conditions. When there is a sustained over-current condition, the IC turns off and requires a POR or EN pin toggling to restart. Under severe over-load and/or short circuit conditions, the boost output voltage can be pulled below the required regulated voltage to keep all of the white LEDs operating. Under this condition, the current flows directly from input to output through the inductor and schottky diode. To protect the TPS61187, the device shuts down immediately. The IC restarts after input POR or EN pin toggling.

#### THERMAL PROTECTION

When the junction temperature of the TPS61187 is over 150°C, the thermal protection circuit is triggered and shuts down the device immediately. Only a POR or EN pin toggling clears the protection and restarts the device.

#### APPLICATION INFORMATION

#### INDUCTOR SELECTION

Because selection of the inductor affects power supply steady state operation, transient behavior, and loop stability, the inductor is the most important component in switching power regulator design. There are three specifications most important to the performance of the inductor: inductor value, dc resistance, and saturation current. The TPS61187 is designed to work with inductor values between 10  $\mu$ H and 47  $\mu$ H. A 10  $\mu$ H inductor is typically available in a smaller or lower profile package, while a 47  $\mu$ H inductor may produce higher efficiency due to a slower switching frequency and/or lower inductor ripple. If the boost output current is limited by the overcurrent protection of the IC, using a 10  $\mu$ H inductor and the highest switching frequency maximizes controller output current capability.

Internal loop compensation for PWM control is optimized for the external component values, including typical tolerances, recommended in Table 3. Inductor values can have ±20% tolerance with no current bias. When the inductor current approaches saturation level, its inductance can decrease 20% to 35% from the 0 A value depending on how the inductor vendor defines saturation. In a boost regulator, the inductor dc current can be calculated with Equation 6.

$$I_{DC} = \frac{Vout \times Iout}{Vin \times \eta}$$

(6)

Where:

Vout = boost output voltage

lout = boost output current

Vin = boost input voltage

$\eta$  = power conversion efficiency, use 90% for TPS61187 applications

The inductor current peak-to-peak ripple can be calculated with Equation 7.

$$I_{PP} = \frac{1}{L \times \left(\frac{1}{Vout - Vin} + \frac{1}{Vin}\right) \times F_{S}}$$

(7)

Where:

I<sub>PP</sub> = inductor peak-to-peak ripple

L = inductor value

F<sub>S</sub> = Switching frequency

Vout = boost output voltage

Vin = boost input voltage

Therefore, the peak current seen by the inductor is calculated with Equation 8.

$$I_{P} = I_{DC} + \frac{I_{PP}}{2} \tag{8}$$

Select an inductor with a saturation current over the calculated peak current. To calculate the worst case inductor peak current, use the minimum input voltage, maximum output voltage, and maximum load current.

Regulator efficiency is dependent on the resistance of its high current path and switching losses associated with the PWM switch and power diode. Although the TPS61187 IC has optimized the internal switch resistances, the overall efficiency is affected by the inductor dc resistance (DCR). Lower DCR improves efficiency. However, there is a trade off between DCR and inductor footprint; furthermore, shielded inductors typically have higher DCR than unshielded ones. Table 3 lists the recommended inductors.

| Table 3 | Recommended | Inductor : | for TPS61187 |

|---------|-------------|------------|--------------|

|         |             |            |              |

|                    | L(µH) | DCR(mΩ) | Isat(A) | Size (L x W x H mm)         |

|--------------------|-------|---------|---------|-----------------------------|

| токо               |       |         |         |                             |

| A915AY – 4R7M      | 4.7   | 38      | 1.87    | $5.2 \times 5.2 \times 3.0$ |

| A915AY – 100M      | 10    | 75      | 1.24    | $5.2 \times 5.2 \times 3.0$ |

| TDK                |       |         |         |                             |

| SLF6028T - 4R7N1R6 | 4.7   | 38      | 1.87    | 5.2 × 5.2 × 3.0             |

| SLF6028T - 4R7N1R6 | 10    | 75      | 1.24    | 5.2 × 5.2 × 3.0             |

#### **OUTPUT CAPACITOR SELECTION**

The output capacitor is mainly selected to meet the requirement for output ripple and loop stability. This ripple voltage is related to the capacitance of the capacitor and its equivalent series resistance (ESR). Assuming a capacitor with zero ESR, the minimum capacitance needed for a given ripple can be calculated with Equation 9:

$$Cout = \frac{(Vout - Vin) \times lout}{Vout \times F_S \times Vripple}$$

(9)

Where:

Vripple = peak-to-peak output ripple. The additional part of the ripple caused by ESR is calculated using: Vripple ESR = lout x RESR

Due to its low ESR, Vripple\_ESR can be neglected for ceramic capacitors, but must be considered if tantalum or electrolytic capacitors are used. The controller output voltage also ripples due to the load transient that occurs during PWM dimming. The TPS61187 adopts a patented technology to limit this type of output ripple even with the minimum recommended output capacitance. In a typical application, the output ripple is less than 250 mV during PWM dimming with a 4.7  $\mu$ F output capacitor. However, the output ripple decreases with higher output capacitances.

#### ISOLATION FET SELECTION

The TPS61187 provides a gate driver to an external P channel MOSFET which can be turned off during device shutdown or fault condition. This MOSFET can provide a true shutdown function and also protect the battery from output short circuit conditions. The source of the PMOS should be connected to the input, and a pull-up resistor is required between the source and gate of the FET to keep the FET off during IC shutdown. To turn on the isolation FET, the FAULT pin is pulled low and clamped at 8 V below the VBAT pin voltage. During device shutdown or fault condition, the isolation FET is turned off, and the input voltage is applied on the isolation MOSFET. During a short circuit condition, the catch diode (D2 in the typical application circuit) is forward biased when the isolation FET is turned off. The drain of the isolation FET swings below ground. The voltage across the isolation FET can be momentarily greater than the input voltage. Therefore, select a 30 V PMOS for a 24 V maximum input. The on resistance of the FET has a large impact on power conversion efficiency since the FET carries the input voltage. Select a MOSFET with  $R_{ds(on)}$  less than 100 m $\Omega$  to limit the power losses.

#### LAYOUT CONSIDERATION

As for all switching power supplies, especially those providing high current and using high switching frequencies, layout is an important design step. If layout is not carefully done, the regulator could show instability as well as EMI problems. Therefore, use wide and short traces for high current paths. The input capacitor, C1 in the Typical Application – Phase Shift PWM Mode figure, needs not only to be close to the VIN pin, but also to the GND pin in order to reduce the input ripple seen by the IC. The input capacitor, C1 in the typical application circuit, should also be placed close to the inductor. C2 is the filter and noise decoupling capacitor for the internal linear regulator powering the internal digital circuits. It should be placed as close as possible between the VDDIO and AGND pins to prevent any noise insertion to the digital circuits. The SW pin carries high current with fast rising and falling edges. Therefore, the connection between the pin to the inductor and schottky diode should be kept as short and wide as possible. It is also beneficial to have the ground of the output capacitor C3 close to the PGND pin since there is a large ground return current flowing between them. When laying out signal grounds, it is recommended to use short traces separated from power ground traces, and connect them together at a single point, for example on the thermal pad. The thermal pad needs to be soldered on to the PCB and connected to the GND pin of the IC. An additional thermal via can significantly improve power dissipation of the IC.

### **REVISION HISTORY**

| Changes from Original (June 2010) to Revision A                                             | Page      |

|---------------------------------------------------------------------------------------------|-----------|

| Changed 典型应用图                                                                               | 1         |

| • Changed cermaic capacitor value, attached to VDDIO, from 0.1 to 1.0 µF                    | 5         |

| • Changed bypass capacitor value in SUPPLY VOLTAGE section from 0.1 to 1.0 μF               | 10        |

| Changed BRIGHTNESS DIMMING CONTROL section                                                  |           |

| Deleted PWM BRIGHTNESS CONTROL INTERFACE section                                            | 12        |

| Changes from Revision A (July 2010) to Revision B                                           | Page      |

| Changed in ABS MAX table, in row "All other pins", MAX col: from 3.6 to 3.7                 | <u> 2</u> |

| Changes from Revision B (April 2011) to Revision C                                          | Page      |

| Changed From: TPS61187 To: TPS61187RTJ in the PACKAGE INFORMATION table                     | 2         |

| Added a description paragraph and replaced Figure 19 in the PHASE SHIFT PWM DIMMING section | 12        |

| Changes from Revision C (September 2011) to Revision D                                      | Page      |

| Changed Figure 2 X axis unit from mA to A                                                   |           |

| Changed Figure 3 X axis unit from mA to A                                                   | 6         |

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                |                       |      | (4)                           | (5)                        |              |                  |

| TPS61187RTJR          | Active | Production    | QFN (RTJ)   20 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | TPS<br>61187     |

| TPS61187RTJR.A        | Active | Production    | QFN (RTJ)   20 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | TPS<br>61187     |

| TPS61187RTJT          | Active | Production    | QFN (RTJ)   20 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | TPS<br>61187     |

| TPS61187RTJT.A        | Active | Production    | QFN (RTJ)   20 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | TPS<br>61187     |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 11-Nov-2025

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 16-Aug-2025

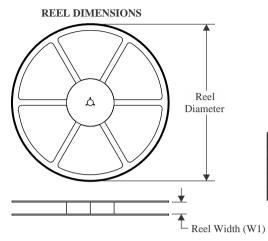

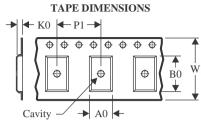

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

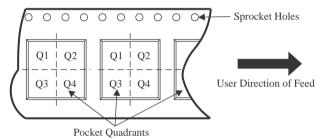

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | _   | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS61187RTJR | QFN | RTJ                | 20 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 16-Aug-2025

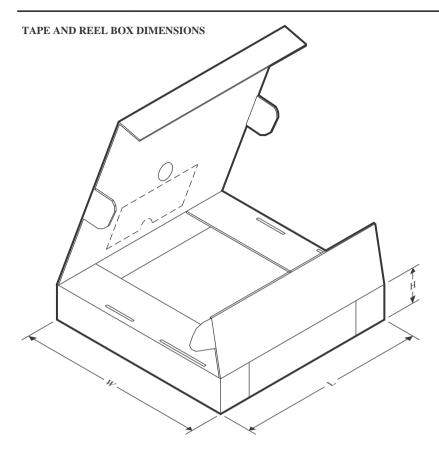

#### \*All dimensions are nominal

| Device Package Type |              | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------------|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ı                   | TPS61187RTJR | QFN          | RTJ             | 20   | 3000 | 353.0       | 353.0      | 32.0        |

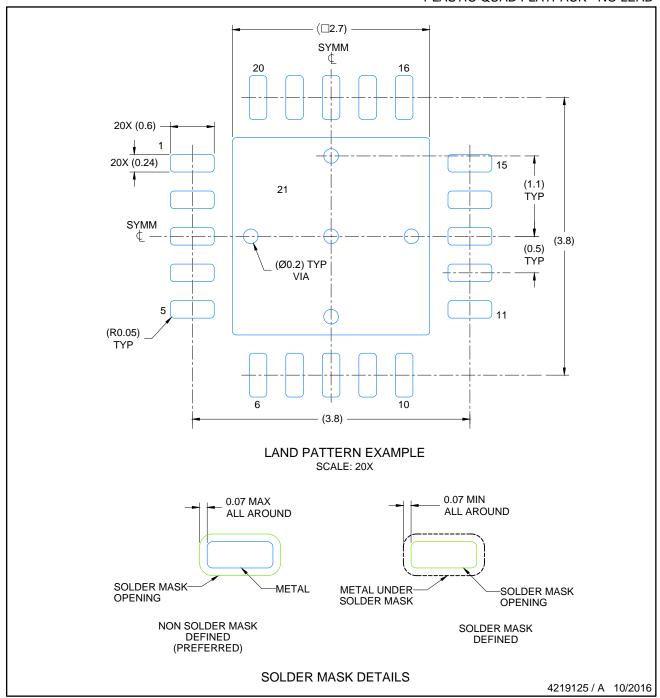

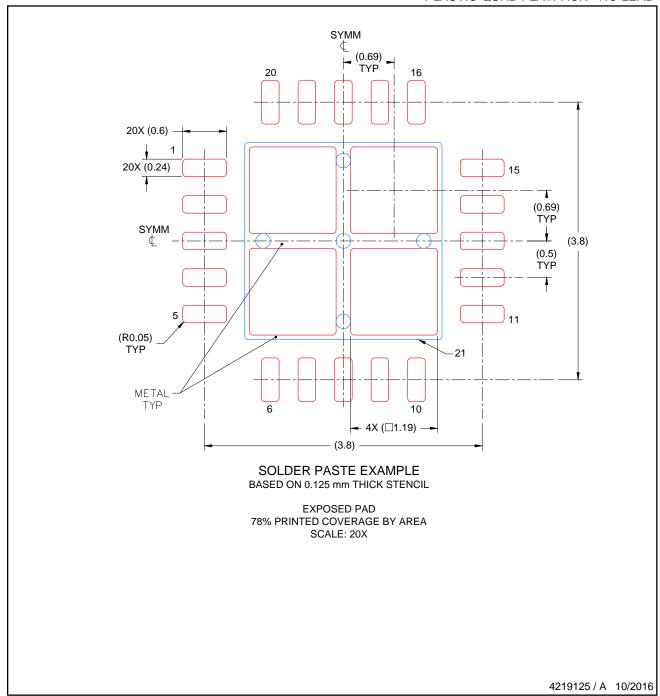

4 x 4, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

# DATA BOOK PACKAGE OUTLINE

LEADFRAME EXAMPLE 4222370

| DRAFTSMAN:<br>H. DENG           | DATE:<br>09/12/2016 | DIMENSIONS IN MILLIMETERS                              |

|---------------------------------|---------------------|--------------------------------------------------------|

| DESIGNER:<br>H. DENG            | DATE:<br>09/12/2016 |                                                        |

| CHECKER: V. PAKU & T. LEQUANG   | DATE:<br>09/12/2016 | SEMICONDUCTOR OPERATIONS 01295                         |

| ENGINEER:<br>T. TANG            | DATE:<br>09/12/2016 | ePOD, RTJ0020D / WQFN,                                 |

| APPROVED:<br>E. REY & D. CHIN   | DATE:<br>10/06/2016 | 20 PIN, 0.5 MM PITCH                                   |

| RELEASED:<br>WDM                | DATE:<br>10/24/2016 |                                                        |

| TEMPLATE INFO:<br>EDGE# 4218519 | DATE:<br>04/07/2016 | SCALE   SIZE   15X   A   4219125   REV   PAGE   1 OF 5 |

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations..

|     |                     | REVISION   | IS      |            |                  |        |

|-----|---------------------|------------|---------|------------|------------------|--------|

| REV | DESCRIPTION         |            | ECR     |            | ENGINEER / DRAFT |        |

| Α   | RELEASE NEW DRAWING |            | 2160736 | 10/24/2016 | T. TANG / H. DE  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     |            |         |            |                  |        |

|     |                     | SCALE SIZE |         | 4040405    | REV              | PAGE   |

|     |                     | NTS A      |         | 4219125    | A                | 5 OF 5 |

#### 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、与某特定用途的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保法规或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。对于因您对这些资源的使用而对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,您将全额赔偿,TI 对此概不负责。

TI 提供的产品受 TI 销售条款)、TI 通用质量指南 或 ti.com 上其他适用条款或 TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。 除非德州仪器 (TI) 明确将某产品指定为定制产品或客户特定产品,否则其产品均为按确定价格收入目录的标准通用器件。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

版权所有 © 2025, 德州仪器 (TI) 公司

最后更新日期: 2025 年 10 月