TPS63810, TPS63811

ZHCSKE6C - JULY 2019-REVISED FEBRUARY 2020

# TPS63810 和 TPS63811 - 具有 I<sup>2</sup>C 接口的 2.5A 降压/升压转换器

# 1 特性

- 输入电压范围: 2.2V 至 5.5V

- 输出电压范围: 1.8V 至 5.2V

- 运行和关断期间, I<sup>2</sup>C 可配置

- VSEL 引脚用于在两个输出电压预设之间切换

- 输出电流

- 当 V<sub>I</sub> ≥ 2.5V、V<sub>O</sub> = 3.3V 时可达 2.5A

- 当 V<sub>1</sub> ≥ 2.8V、V<sub>0</sub> = 3.5V 时可达 2.5A

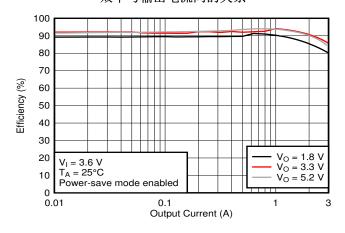

- 在整个负载范围内具有高效率

- 13μA 低工作静态电流

- 自动节电模式和强制 PWM 模式(I<sup>2</sup>C 可配置)

- 峰值电流降压/升压模式架构

- 可在降压、降压/升压和升压操作模式之间定义 转换

- 正向和反向电流运行

- 启动至预偏置输出

- 安全、可靠运行 特性

- 集成软启动

- 过热和过压保护

- 关断期间的真正负载断开

- 正向和反向电流限制

- 两个器件选项

- TPS63810: 预编程输出电压(3.3V、3.45V)

- TPS63811: 启动前的程序输出电压

- 解决方案尺寸小于 20 mm², 仅有四个外部器件

### 简化原理图 0.47 μΗ V١ V<sub>O</sub> 3.3 V I X1 I X2 2.2 V to 5.5 V VIN VOUT ΕN 10 μF 2 × 22 μF TPS63810 / TPS63811 SCL VSEL SDA AGND GND

### 2 应用

- 系统前置稳压器(智能手机、平板电脑、跟踪和远程信息处理、EPOS、TWS 耳机、医用助听器)

- 负载点调节(飞行时间摄像头传感器、端口/电缆适配器和加密狗)

- 热电器件电源(TEC、光纤模块)

- 宽带网络无线电或 SoC 电源(物联网、家庭自动 化、EPOS)

## 3 说明

TPS63810 和 TPS63811 是完全可编程(通过 I<sup>2</sup>C)的高效率、高输出电流降压/升压转换器。根据输入电压不同,当输入电压近似等于输出电压时,它们它会自动以升压、降压或全新的 4 周期降压/升压模式运行。

在定义的阈值内进行模式切换,避免不必要的模式内切换,以减少输出电压纹波。

两个可通过 I<sup>2</sup>C 访问的寄存器用于设置输出电压,VSEL 引脚用于选择哪个输出电压寄存器处于激活状态。这样,这些器件就能够支持动态电压调节。如果输出电压寄存器在运行过程中发生了更改或切换了VSEL 引脚,则器件将以定义的可编程斜坡速率转换运行模式。

### 器件信息<sup>(1)</sup>

| 器件型号     | 封装         | 封装尺寸 (标称值)    |

|----------|------------|---------------|

| TPS63810 | DCDCA (45) | 2.2000 1.4000 |

| TPS63811 | DSBGA (15) | 2.3mm × 1.4mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

效率与输出电流间的关系

| _ | $\Rightarrow$ |

|---|---------------|

| _ | ملب           |

| _ | w             |

| 1 2 | 特性                                     |    | 8.4 Device Functional Modes    |    |

|-----|----------------------------------------|----|--------------------------------|----|

| 3   | 说明1                                    |    | 8.6 Register Map               | 2  |

| 4   | 修订历史记录 2                               | 9  | Application and Implementation | 2  |

| 5   | 器件比较表2                                 |    | 9.1 Application Information    | 2  |

| 6   | Pin Configuration and Functions 3      |    | 9.2 Typical Applications       | 2  |

| 7   | Specifications                         | 10 | Power Supply Recommendations   | 34 |

| •   |                                        | 11 | Layout                         | 34 |

|     | 7.1 Absolute Maximum Ratings 4         |    | 11.1 Layout Guidelines         |    |

|     | 7.2 ESD Ratings4                       |    | •                              |    |

|     | 7.3 Recommended Operating Conditions 4 |    | 11.2 Layout Example            |    |

|     | 7.4 Thermal Information 5              | 12 | 器件和文档支持                        |    |

|     | 7.5 Electrical Characteristics         |    | 12.1 器件支持                      | 3  |

|     | 7.6 Timing Requirements 6              |    | 12.2 文档支持                      | 3  |

|     | 7.7 Switching Characteristics          |    | 12.3 相关链接                      | 3  |

|     | 7.8 Typical Characteristics            |    | 12.4 接收文档更新通知                  | 3  |

|     | **                                     |    | 12.5 支持资源                      | 3  |

| 8   | Detailed Description 8                 |    | 12.6 商标                        |    |

|     | 8.1 Overview 8                         |    |                                |    |

|     | 8.2 Functional Block Diagram 8         |    |                                |    |

|     | 8.3 Feature Description                | 13 | 机械、封装和可订购信息                    | 30 |

|     |                                        |    |                                |    |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

#

## 5 器件比较表

| 器件型号     | 输出启动状态 | 输出电压                              |

|----------|--------|-----------------------------------|

| TPS63810 | 己启用    | VSEL = 低: 3.3V<br>VSEL = 高: 3.45V |

| TPS63811 | 己禁用    | 启动时可编程                            |

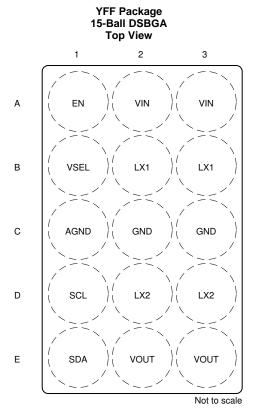

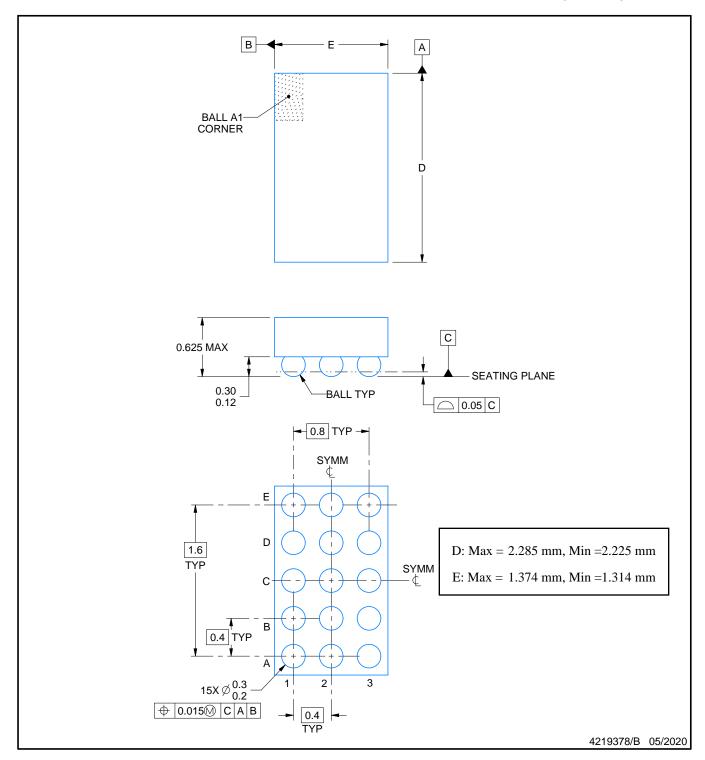

# 6 Pin Configuration and Functions

## **BGA Package (YFF) Pin Functions**

|     | PIN  | 1/0 | DESCRIPTION                                                                                                                                                                                                                            |

|-----|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME | I/O | DESCRIPTION                                                                                                                                                                                                                            |

| A1  | EN   | ı   | Device enable. A high logic level on this pin enables the device; a low logic level on this pin disables the device.                                                                                                                   |

| A2  | VIN  | _   | Supply voltage for power stage                                                                                                                                                                                                         |

| А3  | VIN  | _   | Supply voltage for power stage                                                                                                                                                                                                         |

| B1  | VSEL | I   | This pin selects which VOUT register is active. When a low logic level is applied to this pin, the VOUT1 register sets the output voltage. When a high logic level is applied to this pin, the VOUT2 register sets the output voltage. |

| B2  | LX1  | _   | Inductor connection                                                                                                                                                                                                                    |

| В3  | LX1  | _   | Inductor connection                                                                                                                                                                                                                    |

| C1  | AGND | _   | Analog ground                                                                                                                                                                                                                          |

| C2  | GND  |     | Power ground                                                                                                                                                                                                                           |

| C3  | GND  | _   | Power ground                                                                                                                                                                                                                           |

| D1  | SCL  | I/O | I <sup>2</sup> C serial interface clock. Pull this pin up to the I <sup>2</sup> C bus voltage with a resistor or a current source.                                                                                                     |

| D2  | LX2  | _   | Inductor connection                                                                                                                                                                                                                    |

| D3  | LX2  | _   | Inductor connection                                                                                                                                                                                                                    |

| E1  | SDA  | I/O | I <sup>2</sup> C serial interface data. Pull this pin up to the I <sup>2</sup> C bus voltage with a resistor or a current source.                                                                                                      |

| E2  | VOUT | _   | Converter output                                                                                                                                                                                                                       |

| E3  | VOUT | _   | Converter output                                                                                                                                                                                                                       |

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating junction temperature range (unless otherwise noted)(1)

|                                          |                                                                        | MIN  | MAX | UNIT |

|------------------------------------------|------------------------------------------------------------------------|------|-----|------|

| V <sub>I</sub> Input T <sub>J</sub> Oper | Input voltage (VIN, LX1, LX2, VOUT, SCL, SDA, EN, VSEL) <sup>(2)</sup> | -0.3 | 6   | V    |

|                                          | Input voltage for less than 10 ns (LX1, LX2) <sup>(2)</sup>            | -3   | 9   | V    |

| $T_{J}$                                  | Operating junction temperature                                         | -40  | 150 | °C   |

| T <sub>stg</sub>                         | Storage temperature                                                    | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal, unless otherwise noted.

### 7.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V/                 |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                      |                                              | MIN   | NOM | MAX     | UNIT |

|-------------------|--------------------------------------|----------------------------------------------|-------|-----|---------|------|

| VI                | Supply voltage                       |                                              | 2.2   |     | 5.5     | V    |

| \/                | Outrot caltere                       | Low range                                    | 1.8   |     | 4.975   | V    |

| Vo                | Output voltage                       | High range                                   | 2.025 |     | 5.2     | V    |

| $V_{IH}$          | High-level input voltage             | SCL, SDA, VSEL                               | 1.3   |     | $V_{I}$ | V    |

| V <sub>IL</sub>   | Low-level input voltage              | SCL, SDA, VSEL                               | 0     |     | 0.3     | V    |

| V <sub>(EN)</sub> | Input voltage                        | EN                                           | 0     |     | VI      | V    |

|                   | Output current <sup>(1)</sup>        | $V_0 = 3.3 \text{ V}, V_1 \ge 2.5 \text{ V}$ |       |     | 2.5     |      |

| l <sub>o</sub>    |                                      | $V_0 = 3.5 \text{ V}, V_1 \ge 2.5 \text{ V}$ |       |     | 2       | ۸    |

|                   |                                      | $V_0 = 3.5 \text{ V}, V_1 \ge 2.8 \text{ V}$ |       |     | 2.5     | Α    |

|                   |                                      | $V_0 = 3.3 \text{ V}, V_1 \ge 3 \text{ V}$   |       |     | 3       |      |

| Cı                | Input capacitance <sup>(2)</sup>     | ·                                            | 5     |     |         | μF   |

| Co                | Output capacitance <sup>(2)</sup>    |                                              | 13    | 16  |         | μF   |

| L                 | Inductance                           |                                              | 390   | 470 | 560     | nΗ   |

| T <sub>A</sub>    | Operating free-air temperature range |                                              | -40   |     | 85      | °C   |

| TJ                | Operating junction temperature range |                                              | -40   |     | 125     | °C   |

<sup>(1)</sup> The device can sustain the maximum recommended output current only for short durations before its junction temperature gets too hot. Users must verify that the thermal performance of the end application can support the maximum output current.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> Effective capacitance after DC bias effects have been considered.

### 7.4 Thermal Information

|                      | <b>(1)</b>                                   | TPS63810,<br>TPS63811 |      |

|----------------------|----------------------------------------------|-----------------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | YFF (DSBGA)           | UNIT |

|                      |                                              | 15 PINS               |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 80.5                  | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 0.6                   | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 20.5                  | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.3                   | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 20.5                  | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

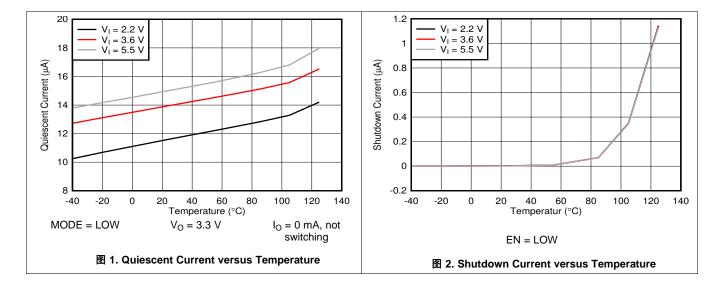

### 7.5 Electrical Characteristics

Over operating junction temperature range and recommended supply voltage range (unless otherwise noted). Typical values are at  $V_1 = 3.6 \text{ V}$ ,  $V_0 = 3.3 \text{ V}$  and  $T_J = 25 ^{\circ}\text{C}$  (unless otherwise noted).

|                      | PARAMETER                    |                   | TEST CONDITIONS                                                                                                                                                                                            | MIN   | TYP   | MAX   | UNIT   |

|----------------------|------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|

| SUPPLY               |                              |                   |                                                                                                                                                                                                            |       |       |       |        |

| I <sub>Q;VIN</sub>   | Supply current into VIN      |                   | $V_{I} = 3.6 \text{ V}, V_{O} = 3.3 \text{ V}, V_{(EN)} = 3.6 \text{ V},$ not switching, $T_{J} = 25^{\circ}\text{C}$                                                                                      |       | 13    |       | μΑ     |

|                      | Supply current into VIN      |                   | $\begin{aligned} &V_{I}=3.6 \text{ V, } V_{O}=0 \text{ V, } V_{(EN)}=3.6 \text{ V, } Output \\ &\text{disabled with ENABLE bit in Control} \\ &\text{Register} \\ &T_{J}=25^{\circ}\text{C} \end{aligned}$ |       | 15    |       | μΑ     |

| I <sub>SD</sub>      | Shutdown current into VIN    |                   | $V_{I} = 3.6 \text{ V}, V_{O} = 0 \text{ V}, V_{(EN)} = 0 \text{ V}$<br>$T_{J} = 25^{\circ}\text{C}$                                                                                                       |       | 0.35  |       | μA     |

| V <sub>IT+</sub>     | Positive-going UVLO thres    | hold voltage      |                                                                                                                                                                                                            | 2     | 2.1   | 2.2   | V      |

| V <sub>hys</sub>     | UVLO threshold voltage hy    | /steresis         |                                                                                                                                                                                                            |       | 200   |       | mV     |

| I/O SIGNAI           | LS                           |                   |                                                                                                                                                                                                            |       |       |       |        |

| V <sub>IT+</sub>     | Positive-going input         | SCL, SDA,<br>VSEL |                                                                                                                                                                                                            |       |       | 1.2   | V      |

|                      | threshold voltage            | EN                |                                                                                                                                                                                                            | 1.07  | 1.1   | 1.13  |        |

| $V_{IT-}$            | Negative-going input         | SCL, SDA,<br>VSEL |                                                                                                                                                                                                            | 0.4   |       |       | V      |

|                      | threshold voltage            | EN                |                                                                                                                                                                                                            | 0.97  | 1     | 1.03  |        |

| V <sub>hys</sub>     | Hysteresis voltage           | EN                |                                                                                                                                                                                                            | 40    |       |       | mV     |

| I <sub>IH</sub>      | High-level input current     | SCL, SDA,<br>VSEL | $V_{(SCL)} = V_{(SDA)} = V_{(VSEL)} = 1.8 \text{ V},$<br>no pullup resistor                                                                                                                                |       | ±0.01 | ±0.1  | μΑ     |

| I <sub>IL</sub>      | Low-level input current      | SCL, SDA,<br>VSEL | $V_{(SCL)} = V_{(SDA)} = V_{(VSEL)} = 0 \text{ V},$<br>no pullup resistor                                                                                                                                  |       | ±0.01 | ±0.1  | μΑ     |

| I <sub>OL</sub>      | Low-level output current     | SCL, SDA          | V <sub>OL</sub> = 0.4 V                                                                                                                                                                                    | 20    |       |       | mA     |

| I <sub>IB</sub>      | Input bias current           | EN                | V <sub>(EN)</sub> = 0 V to 5.5 V                                                                                                                                                                           |       | ±0.01 | ±0.1  | μΑ     |

| POWER ST             | TAGE                         | ·                 |                                                                                                                                                                                                            |       |       |       |        |

| V                    | 0.44                         |                   | Low range                                                                                                                                                                                                  | 1.8   |       | 4.975 | V      |

| Vo                   | Output voltage range         |                   | High range                                                                                                                                                                                                 | 2.025 |       | 5.2   | v<br>I |

|                      | 0.44                         |                   | PWM operation                                                                                                                                                                                              | -1.5  |       | 1.5   | %      |

|                      | Output voltage accuracy      |                   | PSM operation                                                                                                                                                                                              | -1.5  |       | 3.5   | %<br>  |

|                      | Defects autout cells are (DA | NOT 0)            | VSEL = low                                                                                                                                                                                                 |       | 3.3   |       | V      |

|                      | Default output voltage (RA   | INGE = 0)         | VSEL = high                                                                                                                                                                                                |       | 3.45  |       | v<br>I |

|                      |                              |                   | $V_I = 2.9 \text{ V}, V_O = 3.6 \text{ V},$ boost operation, output sourcing current                                                                                                                       | 5.2   |       | 6.5   |        |

|                      | Switch current limit         |                   | $V_I = 4.1 \text{ V}, V_O = 3.3 \text{ V},$ buck operation, output sourcing current                                                                                                                        | 3.8   | 4.3   | 5.2   | А      |

|                      |                              |                   | V <sub>I</sub> = 5 V, V <sub>O</sub> = 3.3 V,<br>reverse-boost operation, output sinking<br>current                                                                                                        | -1.3  |       | -0.35 |        |

| I <sub>T-(PSM)</sub> | PSM entry threshold (peak    | () current        | V <sub>I</sub> = 4.2 V; V <sub>O</sub> = 3.3 V                                                                                                                                                             |       | 0.85  |       | Α      |

## **Electrical Characteristics (continued)**

Over operating junction temperature range and recommended supply voltage range (unless otherwise noted). Typical values are at  $V_1 = 3.6 \text{ V}$ ,  $V_0 = 3.3 \text{ V}$  and  $T_J = 25^{\circ}\text{C}$  (unless otherwise noted).

|                         | PARAMETER                                   | TEST CONDITIONS                                | MIN | TYP | MAX | UNIT |

|-------------------------|---------------------------------------------|------------------------------------------------|-----|-----|-----|------|

|                         | Output discharge current                    | V <sub>I</sub> = 3.6 V, V <sub>O</sub> ≥ 0.8 V | 50  |     |     | mA   |

| V <sub>T+(PG)</sub>     | Positive-going power-good threshold voltage |                                                |     | 95  |     | %    |

| V <sub>T-(PG)</sub>     | Negative-going power-good threshold voltage |                                                |     | 90  |     | %    |

|                         | Positive-going input overvoltage threshold  | Reverse current operation                      |     | 5.7 |     | V    |

| I <sup>2</sup> C INTERF | ACE                                         |                                                |     |     |     |      |

|                         | 7-Bit slave address                         |                                                |     | 75h |     |      |

| THERMAL                 | SHUTDOWN                                    |                                                |     |     | •   |      |

|                         | Thermal shutdown threshold temperature      | T <sub>J</sub> rising                          |     | 150 |     | °C   |

|                         | Thermal shutdown hysteresis                 |                                                |     | 20  |     | °C   |

# 7.6 Timing Requirements

Over operating junction temperature range and recommended supply voltage range (unless otherwise noted)

|                     | PARAMETER                                          | TEST CONDITIONS | MIN                     | TYP MAX | UNIT |

|---------------------|----------------------------------------------------|-----------------|-------------------------|---------|------|

|                     |                                                    | Standard mode   | 0                       | 100     |      |

| SCL                 | SCL clock frequency                                | Fast mode       | 0                       | 400     | kHz  |

|                     |                                                    | Fast mode plus  | 0                       | 1000    |      |

|                     |                                                    | Standard mode   | 4.7                     |         |      |

| LOW                 | LOW period of the SCL clock                        | Fast mode       | 1.3                     |         | μs   |

|                     |                                                    | Fast mode plus  | 0.5                     |         |      |

|                     |                                                    | Standard mode   | 4.0                     |         |      |

| HIGH                | HIGH period of the SCL clock                       | Fast mode       | 0.6                     |         | μs   |

|                     |                                                    | Fast mode plus  | 0.26                    |         |      |

|                     |                                                    | Standard mode   | 4.7                     |         |      |

| BUF                 | Bus free time between a STOP and a START condition | Fast mode       | 1.3                     |         | μs   |

|                     | a START condition                                  | Fast mode plus  | 0.5                     |         |      |

| t <sub>su;sta</sub> |                                                    | Standard mode   | 4.7                     |         |      |

|                     | Set-up time for a repeated START condition         | Fast mode       | 0.6                     |         | μs   |

|                     |                                                    | Fast mode plus  | 0.26                    |         |      |

|                     | Hold time (repeated) START condition               | Standard mode   | 4.0                     |         |      |

| HD;STA              |                                                    | Fast mode       | 0.6                     |         | μs   |

|                     |                                                    | Fast mode plus  | 0.26                    |         |      |

|                     |                                                    | Standard mode   | 250                     |         |      |

| SU;DAT              | Data set-up time                                   | Fast mode       | 100                     |         | ns   |

|                     |                                                    | Fast mode plus  | 50                      |         |      |

|                     |                                                    | Standard mode   | 0                       |         |      |

| HD;DAT              | Data hold time                                     | Fast mode       | 0                       |         | μs   |

|                     |                                                    | Fast mode plus  | 0                       |         |      |

|                     |                                                    | Standard mode   |                         | 1000    |      |

| r                   | Rise time of both SDA and SCL signals              | Fast mode       | 20                      | 300     | ns   |

|                     | Signals                                            | Fast mode plus  |                         | 120     |      |

|                     |                                                    | Standard mode   |                         | 300     |      |

| f                   | Fall time of both SDA and SCL signals              | Fast mode       | 20×V <sub>DD</sub> /5.5 | 300     | ns   |

|                     | Signais                                            | Fast mode plus  | 20×V <sub>DD</sub> /5.5 | 120     |      |

|                     |                                                    | Standard mode   | 4.0                     |         |      |

| su;STO              | Set-up time for STOP condition                     | Fast mode       | 0.6                     |         | μs   |

|                     |                                                    | Fast mode plus  | 0.26                    |         |      |

## **Timing Requirements (continued)**

Over operating junction temperature range and recommended supply voltage range (unless otherwise noted)

|                      | PARAMETER                         | TEST CONDITIONS    | MIN TYP MAX | UNIT   |  |

|----------------------|-----------------------------------|--------------------|-------------|--------|--|

|                      |                                   | Standard mode      | 3.45        |        |  |

| $t_{VD;DAT}$         | Data valid time                   | Fast mode          | 0.9         | μs     |  |

|                      |                                   | Fast mode plus     | 0.45        |        |  |

|                      |                                   | Standard mode      | 3.45        |        |  |

| t <sub>VD;ACK</sub>  | Data valid acknowledge time       | Fast mode          | 0.9         | 0.9 µs |  |

| 75,71011             |                                   | Fast mode plus     | 0.45        | ļ      |  |

|                      |                                   | Standard mode      | 400         |        |  |

| C <sub>b</sub>       | Capacitive load for each bus line | Fast mode          | 400         |        |  |

|                      |                                   | Fast mode plus     | 550         |        |  |

| t <sub>w(VSEL)</sub> | VSEL pulse duration               | VSEL = high or low | 5           | μs     |  |

# 7.7 Switching Characteristics

Over operating junction temperature range and recommended input voltage range (unless otherwise noted). Typical values are at  $V_1 = 3.6 \text{ V}$ ,  $V_0 = 3.3 \text{ V}$ , and  $T_J = 25^{\circ}\text{C}$  (unless otherwise noted).

|                      | PARAMETER                                                                          | TEST CONDITIONS                                                            | MIN | TYP  | MAX | UNIT   |  |

|----------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|------|-----|--------|--|

| t <sub>d(EN)</sub>   | Delay between a rising edge on the EN pin and the start of the output voltage ramp | T <sub>J</sub> = 25°C, V <sub>I</sub> = 3.6 V                              |     | 229  | 440 | μs     |  |

| t <sub>d(PG)</sub>   | Power-good delay                                                                   | V <sub>O</sub> falling                                                     |     | 50   |     | μs     |  |

| SR                   |                                                                                    | SLEW = 00b, forced-PWM operation                                           |     | ±1   |     |        |  |

|                      | Slew rate of internal ramp during dynamic voltage scaling                          | SLEW = 01b, forced-PWM operation                                           |     | ±2.5 |     | V/ms   |  |

|                      |                                                                                    | SLEW = 10b, forced-PWM operation                                           |     | ±5   |     | V/IIIS |  |

|                      |                                                                                    | SLEW = 11b, forced-PWM operation                                           |     | ±10  |     |        |  |

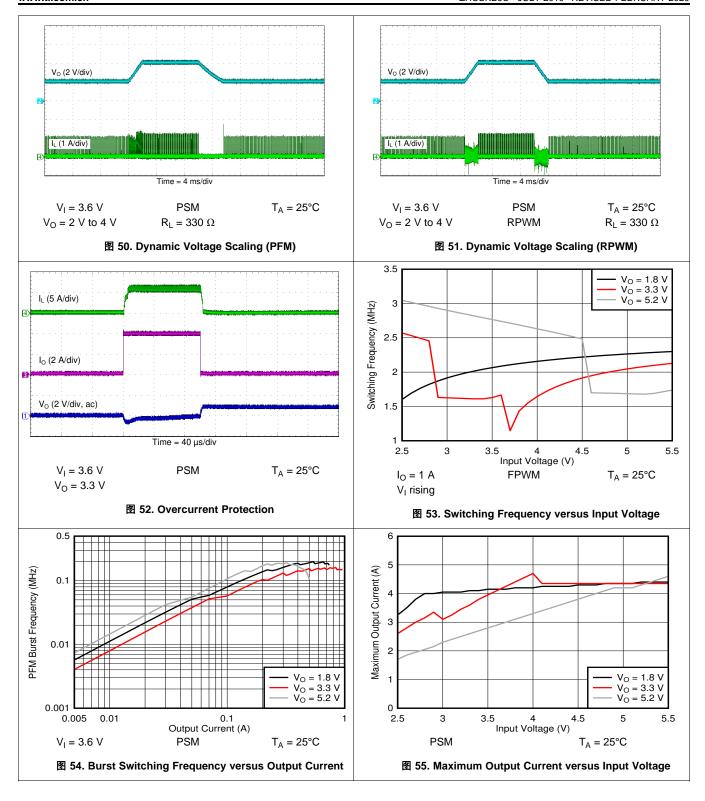

|                      | Inductor Switching Frequency, Boost Mode                                           | $V_I = 2.3 \text{ V}, V_O = 3.3 \text{ V}, \text{ no Load, PWM}$ operation |     | 2.6  |     | MHz    |  |

| $f_{SW}$             | Inductor Switching Frequency, Buck-<br>Boost Mode                                  | $V_I = 3.3 \text{ V}, V_O = 3.3 \text{ V}, \text{ no Load, PWM}$ operation |     | 1.6  |     | MHz    |  |

|                      | Inductor Switching Frequency, Buck<br>Mode                                         | $V_I = 4.3 \text{ V}, V_O = 3.3 \text{ V}, \text{ no Load, PWM}$ operation |     | 2.0  |     | MHz    |  |

| t <sub>d(VSEL)</sub> | Delay between rising edge of VSEL and start of DVS ramp                            | Measured from rising edge of VSEL to start of ramp.                        |     |      | 5   | μs     |  |

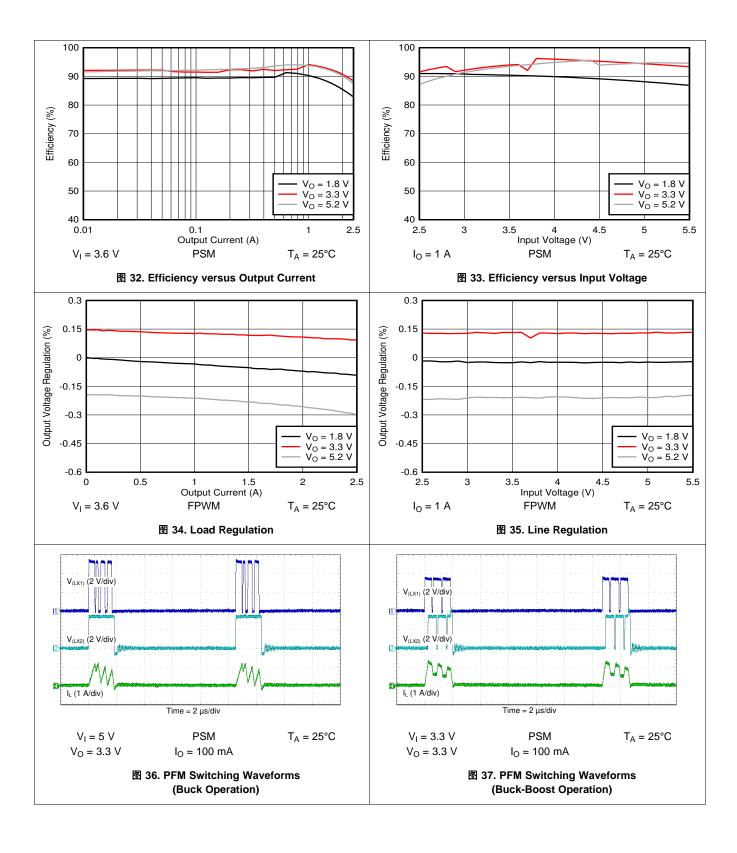

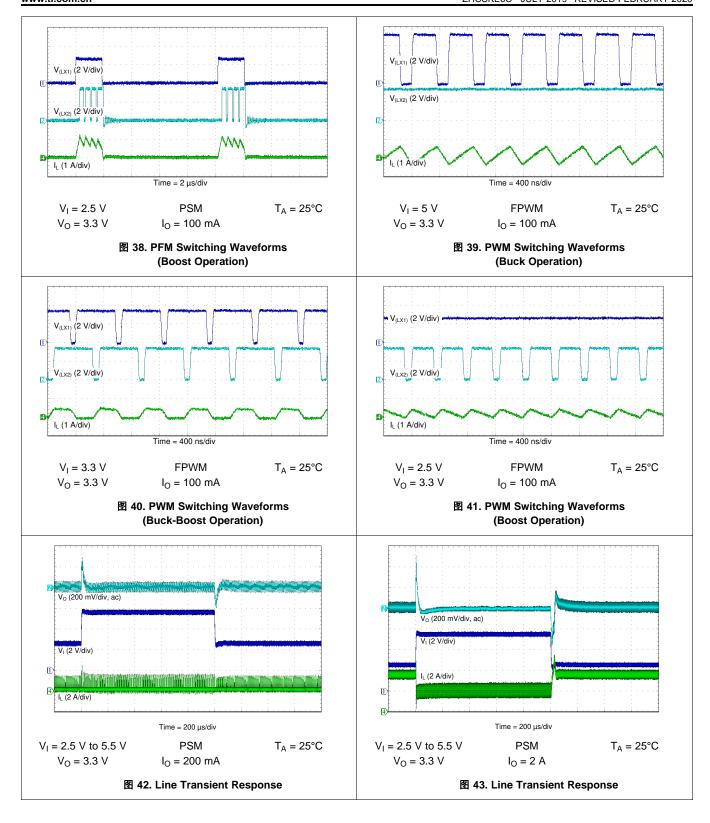

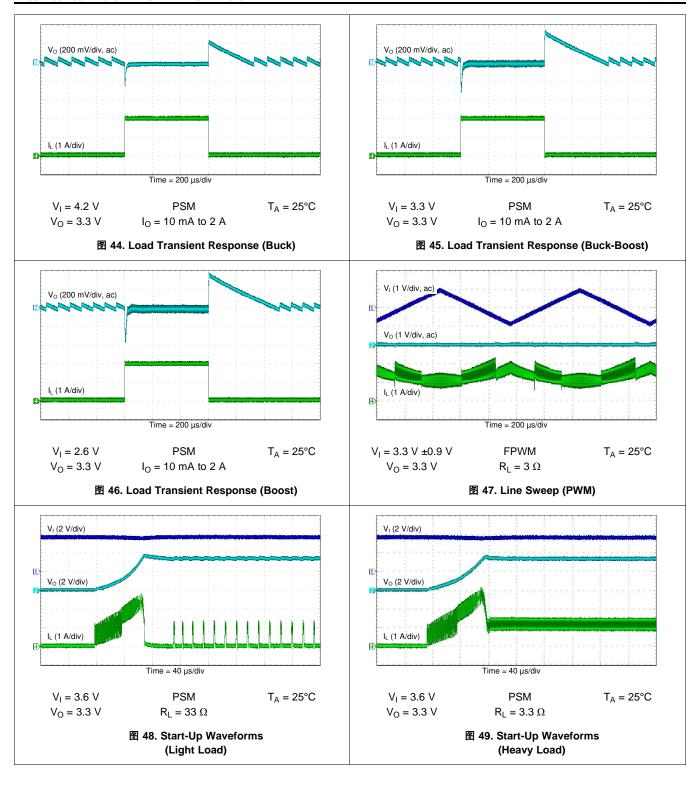

## 7.8 Typical Characteristics

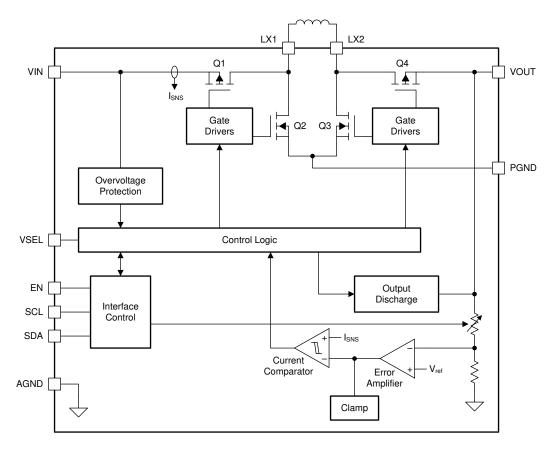

## 8 Detailed Description

#### 8.1 Overview

The TPS63810 and TPS63811 devices are high-efficiency buck-boost converters. Each device uses four switches to maintain synchronous power conversion under all operating conditions, so that the device achieves high efficiency power conversion over a wide range of input voltages and output currents. The device automatically switches between buck, boost, and buck-boost operation as required by the operating conditions. The device operates as a true buck converter when  $V_1 > V_0$  and as a true boost converter when  $V_1 < V_0$ . When  $V_1 \approx V_0$ , the device operates in a 4-cycle buck-boost mode. The RMS current through the switches and the inductor is thus kept to a minimum, minimizing switching and conduction losses. Controlling the switches this way lets the converter achieve high efficiency over the whole input voltage range.

### 8.2 Functional Block Diagram

## 8.3 Feature Description

### 8.3.1 Control Scheme

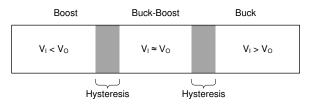

The device automatically selects the best switching scheme for the operating conditions. To make sure of stable operation, the selection logic includes hysteresis (see 3).

图 3. Switching Scheme Selection

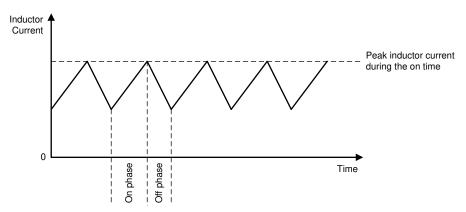

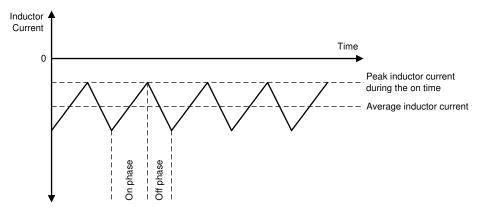

### 8.3.1.1 Buck Operation

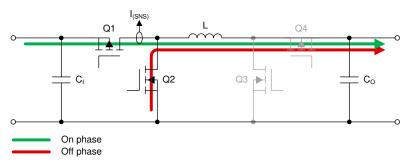

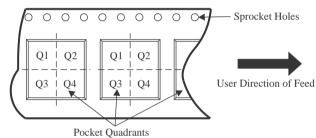

When  $V_1 > V_0$ , the device switches like a buck converter:

- Q1 is the switch.

- · Q2 is the rectifier.

- · Q3 is permanently off.

- · Q4 is permanently on.

See 8 4. During buck operation, one switching cycle comprises two phases: on-off.

图 4. Buck Switch Configuration

### 8.3.1.2 Boost Operation

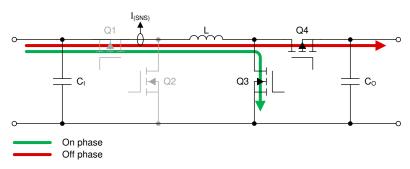

When  $V_1 < V_0$ , the device switches like a boost converter:

- · Q1 is permanently on.

- · Q2 is permanently off.

- · Q3 is the switch.

- · Q4 is the rectifier.

See \$\bigsep\$ 5. During boost operation, one switching cycle comprises two phases: on-off.

图 5. Boost Switch Configuration

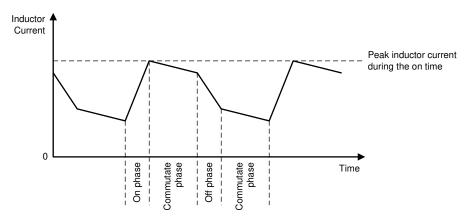

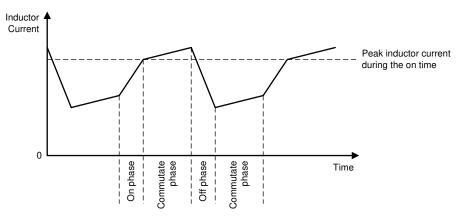

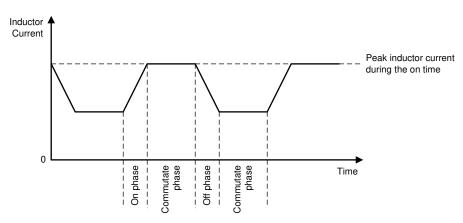

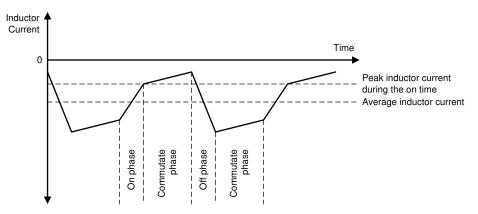

### 8.3.1.3 Buck-Boost Operation

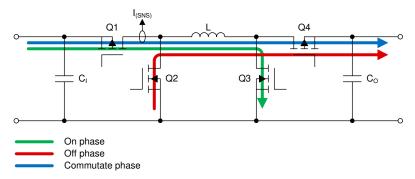

When  $V_1 \approx V_O$ , all four transistors switch continuously (see  $\boxtimes$  6). During buck-boost operation, one switching cycle comprises four phases: on–commutate–off–commutate.

图 6. Buck-Boost Switch Configuration

#### 8.3.2 Control Scheme

The device uses a constant off-time, peak-current-mode control scheme where an outer voltage control loop generates the demand signal for an inner current control loop. During the on-time, the inner current control loop monitors the inductor current, and when the inductor current equals the demand signal from the error amplifier, the on-time stops and the next part of the switching cycle starts.

The off-time is a function of V<sub>I</sub> and V<sub>O</sub> and the operating mode (buck, boost, or buck-boost) of the converter.

图 7. Peak Current Control (Buck and Boost Operation)

图 8. Peak Current Control – Buck-Boost Operation with  $V_I < V_O$

图 9. Peak Current Control – Buck-Boost Operation with  $V_1 > V_0$

图 10. Peak Current Control – Buck-Boost Operation with  $V_I = V_O$

During PWM operation, current can flow in the reverse direction (from output to input). In this case, the error amplifier provides a negative peak current target. Note that the average reverse current is greater (more negative) than the peak current (see § 11 and § 12).

图 11. Reverse Peak Current Control – Buck and Boost Operation

图 12. Reverse Peak Current Control – Buck-Boost Operation, with  $V_1 > V_0$

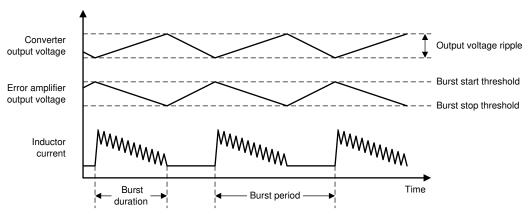

### 8.3.3 Power-Save Mode Operation (PSM)

To increase efficiency across a wide range of operating conditions, the device automatically changes from pulse-width modulation (PWM) at medium and high output currents to pulse-frequency modulation (PFM) at low output currents.

- During PWM operation, the device switches continuously and adjusts the duty cycle of each switching cycle

to regulate the output voltage.

- During PFM operation, the device switches in bursts of a few switching cycles, separated by periods when the device does not switch (see 图 13). PFM operation increases efficiency at low output currents because when the device does not switch, there are no switching losses and most of the internal circuitry is disabled, which reduces quiescent power consumption. A comparator with hysteresis compares the output voltage of the error amplifier to a predefined PFM threshold voltage. When the output voltage of the error amplifier is greater than the burst threshold voltage, the device starts switching. When the output voltage of the error amplifier is less than the burst threshold voltage, the device stops switching. This scheme automatically adjusts the frequency and the duration of the switching bursts to regulate the output voltage. During PFM operation, the output voltage ripple can be higher and the transient response is not as good as during PWM operation (see 表 1).

To enable power-save mode, clear the FPWM bit in the Control register to 0.

图 13. Pulse-Frequency Modulation

# 表 1. Forced-PWM versus Power-Save Mode Performance Comparison

| PERFORMANCE PARAMETER             | BEST OPERATING MODE   |

|-----------------------------------|-----------------------|

| Low-power efficiency              | Power-Save Mode (PSM) |

| Medium- and high-power efficiency | No difference         |

| DC Output voltage accuracy        | Forced-PWM            |

| Transient response                | Forced-PWM            |

| Output voltage ripple             | Forced-PWM            |

## 8.3.4 Forced-PWM Operation (FPWM)

During forced-PWM operation, the device uses PWM for all operating conditions. Forced-PWM operation has lower output voltage ripple and better transient response than power-save mode operation, but lower efficiency at low output currents (see 表 1).

Note that the device inhibits forced-PWM operation during start-up (that is, until the converter output has reached power-good for the first time).

To enable forced-PWM operation, set the FPWM bit in the Control register to 1.

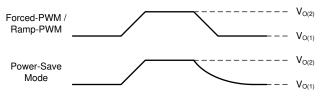

## 8.3.5 Ramp-PWM Operation (RPWM)

If Ramp-PWM operation is enabled, the device operates in forced-PWM when it ramps from one output voltage to another during dynamic voltage scaling. This function is useful if you want the device to operate in power-save mode, but you want to make sure that dynamic voltage scaling ramps the output voltage up and down in a controlled way. If the device operates in power-save mode and Ramp-PWM is disabled, the device cannot always control the ramp from a higher output voltage to a lower output voltage, because in power-save mode the device cannot sink current (see \$\mathbb{S}\$ 14).

To enable Ramp-PWM operation, set the RAMP bit in the Control register to 1. To disable Ramp-PWM operation, clear the RAMP bit in the Control register to 0.

图 14. Ramp-PWM Operation

### 8.3.6 Device Enable (EN)

The EN pin enables and disables the device.

- When the EN pin is high, the device is enabled.

- When the EN pin is low, the device is disabled.

You can also use the ENABLE bit in the Control register to enable and disable the output of the converter (see the *Register Map*).

| ENABLE PIN (EN) | ENABLE BIT | DEVICE STATE                 | OUTPUT STATE            |

|-----------------|------------|------------------------------|-------------------------|

| 0               | X          | Device in Shutdown           | Output Discharge Active |

| 1               | 0          | Programming Interface Active | Output Discharge Active |

| 1               | 1          | Device Active                | Output Enabled          |

### 8.3.7 Undervoltage Lockout (UVLO)

The device has an undervoltage lockout function that disables the device when the supply voltage is too low for correct operation.

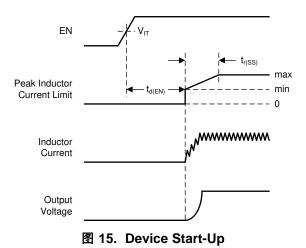

#### 8.3.8 Soft Start

To minimize inrush current and output voltage overshoot during start-up, the device has a soft-start function. At turn on, the switch current limit ramps gradually to its maximum value and the device starts up in a controlled way. The gradual increase of the current limit generates the smallest inrush current for no-load conditions. It is also possible to start into a high load as long as the load does not exceed the device current limit.

The rise time of the output voltage changes with the application circuit and the operating conditions. The output voltage rise time increases if the following occurs:

- · The output capacitance is large.

- · The load current is large.

- The device operates in boost mode.

See the Application and Implementation section for output voltage rise times in a typical application.

### 8.3.9 Output Voltage Control

The device can generate output voltages from 1.8 V to 5.2 V with a resolution of 25 mV. To set the output voltage, you must first program the RANGE bit in the Control register to select the output voltage range:

- When RANGE = 0, you can program the output voltage from 1.8 V to 4.975 V.

- When RANGE = 1, you can program the output voltage from 2.025 V to 5.2 V.

When you have selected the output voltage range, you can program the VOUT1 register and VOUT2 register to set the output voltage:

- When RANGE = 0,  $V_0 = (VOUT[6:0] \times 0.025) + 1.8 \text{ V}$

- When RANGE = 1,  $V_0 = (VOUT[6:0] \times 0.025) + 2.025 V$

VOUT[6:0] is the 7-bit value in the VOUT1 register or VOUT2 register, whichever is active.

The VSEL pin selects which VOUT register is active:

- When VSEL = low, the VOUT1 register sets the output voltage.

- When VSEL = high, the VOUT2 register sets the output voltage.

注

To prevent output voltage transients, TI recommends that you do not change the output voltage range while the converter is in operation. Instead, clear the ENABLE bit in the Control register to 0 to disable the DC/DC converter before you change the RANGE bit.

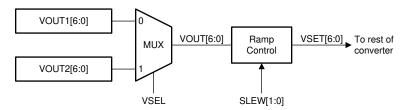

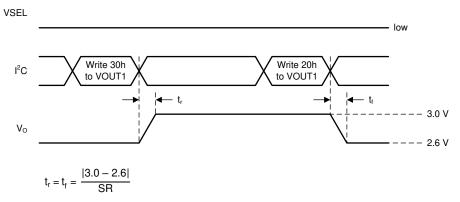

### 8.3.9.1 Dynamic Voltage Scaling

The device has a dynamic voltage scaling (DVS) function which lets you change the output voltage in a controlled way during operation.

16 shows a simplified block diagram of the DVS function. The VSEL pin controls a multiplexer which selects either the VOUT1 register or the VOUT2 register to control the set voltage. The ramp control block detects when the target output voltage is different from the actual output voltage and ramps the output voltage to the target voltage in 25-mV steps. You can use the 2-bit SLEW parameter in the Control register to select one of four slew rates from 0.5 V/ms to 10 V/ms.

The device starts a DVS ramp when you change the logic level on the VSEL pin or program to a new value in the active VOUT register.

图 16. Dynamic Voltage Scaling Block Diagram

Note that if you change the contents of the active VOUT register or change the state of the VSEL pin during start-up (that is, before the end of the soft start), the converter uses the new value immediately and does not ramp gradually to the final value.

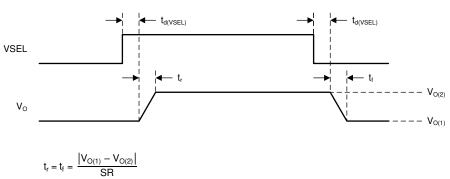

■ 17 shows the timing diagram when you use the VSEL pin to change between the output voltage values in the VOUT1 and VOUT2 registers.

#### Where

- V<sub>O(1)</sub> is the output voltage set by the VOUT1 register

- V<sub>O(2)</sub> is the output voltage set by the VOUT2 register

- SR is the slew rate set by the SLEW bits in the CONTROL register

图 17. DVS Timing Diagram Using the VSEL Pin

Where SR is the slew rate set by the SLEW bits in the CONTROL register.

图 18. DVS Timing Using the I<sup>2</sup>C Interface

#### 8.3.10 Protection Functions

## 8.3.10.1 Input Voltage Protection (IVP)

Under certain operating conditions, current can flow from the output of the device to the input. For example, this can occur during dynamic voltage scaling when the output ramps down to a lower voltage and the VOUT pin sinks current from the output capacitor. Under such conditions, if the voltage source supplying the device cannot sink current, the voltage on the VIN pin can rise uncontrollably.

To make sure the input voltage stays within the permitted range, the device stops switching if the voltage on the VIN pin is greater than 5.7 V. The device automatically starts to switch again when the voltage on the VIN pin is less than 5.7 V.

The device sets the  $\overline{PG}$  bit in the Status register when an input overvoltage event occurs. The device clears the  $\overline{PG}$  bit if the Status register is read when the power-not-good condition no longer exists.

### 8.3.10.2 Current Limit Mode and Overcurrent Protection

The device has a clamp circuit which limits the peak inductor current in the event of an overload. The exact value of the output current during an overload changes with the operating conditions  $(V_I \text{ and } V_O)$  and the switching mode (buck, buck-boost, or boost) – see  $\boxtimes 52$ .

Overloads increase the power dissipation in the device, which increases its temperature. If the device becomes too hot, the thermal shutdown function turns off the converter. When the device cools down, the thermal shutdown function automatically turns on the converter again. Thus, under a permanent overload condition, the device can periodically turn on and off, as it cools down and then heats up.

## 8.3.10.3 Thermal Shutdown

The device has a thermal shutdown function which turns off the converter if the junction temperature is greater than 150°C. The device automatically turns on the converter again when the junction temperature is less than 130°C. You can still use the I<sup>2</sup>C interface to read and write to the registers when the device is in an overtemperature condition.

When the device detects an overtemperature condition, it sets the TSD bit in the Status register to 1. The device clears the TSD bit to 0 if you read the Status register when the junction temperature of the device is less than 130°C.

### 8.3.11 Power Good

The device has a power-good function which indicates if the output of the DC/DC converter is in regulation or not. The device detects a power-good condition when the output voltage is greater than 95% of its nominal value and detects a power-not-good condition when the output voltage is less than 90% of its nominal value.

When a power-not-good condition occurs, the device sets the  $\overline{PG}$  bit in the Status register to 1. The device clears the  $\overline{PG}$  bit to 0 if you read the Status register when a power-good condition exists.

#### 8.3.12 Load Disconnect

During device shutdown, the input is disconnected from the output. This prevents any current flow from the output to the input or from the input to the output.

#### 8.3.13 Output Discharge

The device actively discharges the output when the EN pin is low or the ENABLE bit is set to zero.

#### 8.4 Device Functional Modes

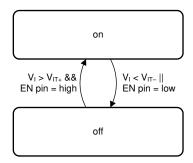

The device has two functional modes: off and on. The device enters the on mode when the voltage on the VIN pin is higher than the UVLO threshold and a high logic level is applied to the EN pin. The device enters the off mode when the voltage on the VIN pin is lower than the UVLO threshold or a low logic level is applied to the EN pin.

图 19. Device Functional Modes

## 8.5 Programming

#### 8.5.1 Serial Interface Description

I<sup>2</sup>C is a 2-wire serial interface developed by Philips Semiconductor, now NXP Semiconductors (see *NXP Semiconductors, UM10204 – PC-Bus Specification and User Manual*). The bus consists of a data line (SDA) and a clock line (SCL) with pullup structures. When the bus is idle, both SDA and SCL lines are pulled high. All the I<sup>2</sup>C-compatible devices connect to the I<sup>2</sup>C bus through open-drain I/O pins, SDA, and SCL. A master device, usually a microcontroller or a digital signal processor, controls the bus. The master is responsible for generating the SCL signal and device addresses. The master also generates specific conditions that indicate the START and STOP of data transfer. A slave device receives and transmits data on the bus under control of the master device.

The device works as a slave and supports the following data transfer modes, as defined in the I<sup>2</sup>C-Bus Specification:

- Standard-mode (100 kbps)

- Fast-mode (400 kbps)

- Fast-mode Plus (1 Mbps)

The interface adds flexibility to the power supply solution, enabling most functions to be programmed to new values, depending on the instantaneous application requirements. Register contents remain intact as long as supply voltage remains above 2.1 V.

The data transfer protocol for standard and fast modes is exactly the same, therefore, it is referred to as F/S-mode in this document. The device supports 7-bit addressing; 10-bit addressing and general call address are not supported. The device 7-bit address is 75h (1110101b).

To make sure that the I<sup>2</sup>C function in the device is correctly reset, it is recommended that the I<sup>2</sup>C master initiates a STOP condition on the I<sup>2</sup>C bus after the initial power up of SDA and SCL pullup voltages.

# Programming (接下页)

### 8.5.2 Standard-, Fast-, and Fast-Mode Plus Protocol

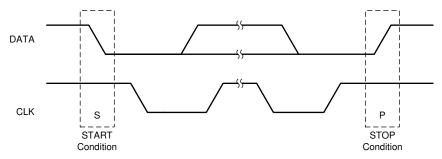

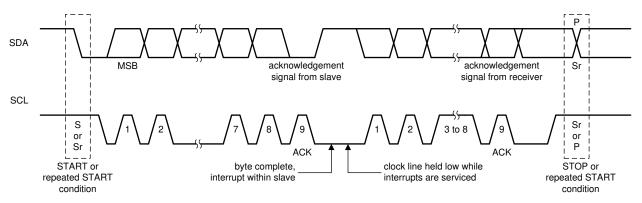

The master initiates a data transfer by generating a start condition. The start condition is when a high-to-low transition occurs on the SDA line while SCL is high, as shown in ₹ 20. All I²C-compatible devices recognize a start condition.

图 20. START and STOP Conditions

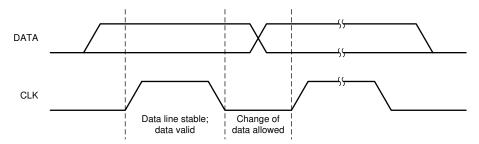

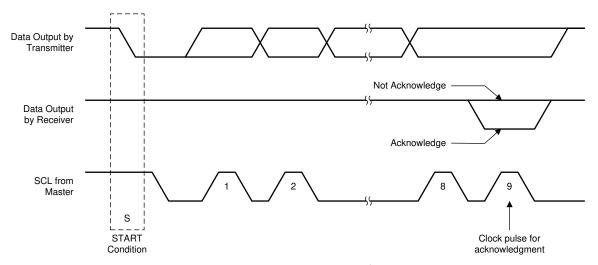

The master then generates the SCL pulses and transmits the 7-bit address and the read/write direction bit, R/W, on the SDA line. During all transmissions, the master ensures that data is valid. A valid data condition requires the SDA line to be stable during the entire high period of the clock pulse (see 图 21). All devices recognize the address sent by the master and compare it to their internal fixed addresses. Only the slave device with a matching address generates an acknowledge (see 图 22) by pulling the SDA line low during the entire high period of the ninth SCL cycle. Upon detecting this acknowledge, the master knows that communication link with a slave has been established.

图 21. Bit Transfer on the Serial Interface

The master generates further SCL cycles to either transmit data to the slave (R/W bit 1) or receive data from the slave (R/W bit 0). In either case, the receiver needs to acknowledge the data sent by the transmitter. An acknowledge signal can either be generated by the master or by the slave, depending on which one is the receiver. 9-bit valid data sequences consisting of 8-bit data and 1-bit acknowledge can continue as long as necessary.

To signal the end of the data transfer, the master generates a stop condition by pulling the SDA line from low to high while the SCL line is high (see 20). This releases the bus and stops the communication link with the addressed slave. All I<sup>2</sup>C-compatible devices must recognize the stop condition. Upon the receipt of a stop condition, all devices know that the bus is released and they wait for a start condition followed by a matching address.

Attempting to read data from register addresses not listed in this section results in 00h being read out.

# Programming (接下页)

图 22. Acknowledge on the I<sup>2</sup>C Bus

图 23. Bus Protocol

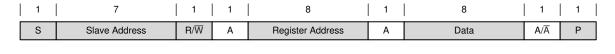

## 8.5.3 I<sup>2</sup>C Update Sequence

A single update requires the following:

- A start condition

- A valid I<sup>2</sup>C slave address

- A register address

- A data byte

To acknowledge the receipt of each byte, the device pulls the SDA line low during the high period of a single clock pulse. The device performs an update on the falling edge of the acknowledge signal that follows the last byte.

# Programming (接下页)

From master to slave

From slave to master

A = Acknowledge (SDA low)

$\overline{A}$  = Not acknowledge (SDA high)

S = START condition

Sr = REPEATED START condition

P = STOP condition

## 图 24. "Write" Data Transfer Format in Standard, Fast, and Fast-Plus Modes

| 1                                                                                          | 7                 | 1                        | 1 | 8 | 1  | 1             | 8   | 1        | 1    | 8                                                  | 1              | 1 |

|--------------------------------------------------------------------------------------------|-------------------|--------------------------|---|---|----|---------------|-----|----------|------|----------------------------------------------------|----------------|---|

| S                                                                                          | Slave Address     | s R/W A Register Address |   | Α | Sr | Slave Address | R/W | Α        | Data | A/Ā                                                | Р              |   |

|                                                                                            |                   |                          |   |   |    |               |     |          |      |                                                    |                |   |

|                                                                                            |                   | "0" Write                |   |   |    |               |     | "1" Read |      |                                                    |                |   |

| From master to slave  A = Acknowledge (SDA low) $\overline{A}$ = Not acknowledge (SDA high |                   |                          |   |   |    |               |     |          |      |                                                    |                |   |

| Fro                                                                                        | m slave to master |                          |   |   |    |               |     |          |      | S = START cond<br>Sr = REPEATED<br>P = STOP condit | ition<br>START |   |

图 25. "Read" Data Transfer Format in Standard, Fast, and Fast-Plus Modes

# 8.6 Register Map

# 8.6.1 Register Description

# 8.6.1.1 Register Map

| ADDRESS | ACRONYM | REGISTER NAME    | SECTION |

|---------|---------|------------------|---------|

| 0x01    | CONTROL | Control Register | Go      |

| 0x02    | STATUS  | Status Register  | Go      |

| 0x03    | DEVID   | DEVID Register   | Go      |

| 0x04    | VOUT1   | VOUT1 Register   | Go      |

| 0x05    | VOUT2   | VOUT2 Register   | Go      |

# 8.6.1.2 Register CONTROL (Slave address: 0b1110101; Register address: 0x01; Default: 0x00 or 0x20)

Return to Register Map.

## Figure 26. Register CONTROL Format

| 7        | 6     | 5      | 4        | 3    | 2    | 1         | 0 |

|----------|-------|--------|----------|------|------|-----------|---|

| RESERVED | RANGE | ENABLE | RESERVED | FPWM | RPWM | SLEW[1:0] |   |

| R/W      | R/W   | R/W    | R/W      | R/W  | R/W  | R/W       |   |

LEGEND: R/W = Read/Write; R = Read only

## **Table 3. Register CONTROL Field Descriptions**

| Bit | Field     | Туре | Reset | Description                                                                                                                                                                                   |  |  |  |

|-----|-----------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | RESERVED  | R/W  | 0     | Reserved for future use. This bit can be written to and read from but it has no function. For compatibility with possible future device variants, it is recommended to program this bit to 0. |  |  |  |

| 6   | RANGE     | R/W  | 0     | This bit selects the output voltage range.  0: Low range (1.800 V to 4.975 V)  1: High range (2.025 V to 5.200 V)                                                                             |  |  |  |

| 5   | ENABLE    | R/W  | X     | This bit controls operation of the converter.  0 : Converter operation disabled (Start-up value for TPS63811)  1 : Converter operation enabled (Start-up value for TPS63810)                  |  |  |  |

| 4   | RESERVED  | R/W  | 0     | Reserved for future use. This bit can be written to and read from but it has no function. For compatibility with possible future device variants, it is recommended to program this bit to 0. |  |  |  |

| 3   | FPWM      | R/W  | 0     | This bit controls the forced-PWM function.  0: Forced-PWM operation disabled  1: Forced-PWM operation enabled                                                                                 |  |  |  |

| 2   | RPWM      | R/W  | 0     | This bit controls the ramp-PWM function.  0: Ramp-PWM operation disabled  1: Ramp-PWM operation enabled                                                                                       |  |  |  |

| 1:0 | SLEW[1:0] | R/W  | 00    | These bits control the slew rate of the DVS function.  00: 1.0 V/ms  01: 2.5 V/ms  10: 5.0 V/ms  11: 10.0 V/ms                                                                                |  |  |  |

## 8.6.1.3 Register STATUS (Slave address: 0b1110101; Register address: 0x02; Default: 0x00)

Return to Register Map.

## Figure 27. Register STATUS Format

| 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|----------|---|---|---|---|---|---|-----|

| NIL[5:0] |   |   |   |   |   |   | PGn |

|          | R |   |   |   |   |   |     |

LEGEND: R/W = Read/Write; R = Read only

# **Table 4. Register STATUS Field Descriptions**

| Bit | Field    | Туре | Reset  | Description                                                                                                                                                                                                                        |

|-----|----------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | NIL[5:0] | R    | 000000 | Not used. These bits always return 0 when read.                                                                                                                                                                                    |

| 1   | TSD      | R    | 0      | This bit shows the status of the thermal shutdown function. This bit is cleared if the STATUS register is read when the overtemperature condition no longer exists.  0: Temperature good 1: An overtemperature event was detected. |

| 0   | PGn      | R    | 0      | This bit shows the status of the power-good comparator. This bit is cleared if the STATUS register is read when the power-not-good condition no longer exists.  0: Power-good 1: A power-not-good event was detected.              |

## 8.6.1.4 Register DEVID (Slave address: 0b1110101; Register address: 0x03; Default: 0x04)

Return to Register Map.

## Figure 28. Register DEVID Format

| 7 | 6                    | 5          | 4 | 3          | 2 | 1 | 0      |

|---|----------------------|------------|---|------------|---|---|--------|

|   | MANUFAC <sup>*</sup> | TURER[3:0] |   | MAJOR[1:0] |   |   | R[1:0] |

|   | F                    | ₹          |   | ı          | 3 | R |        |

LEGEND: R/W = Read/Write; R = Read only

### **Table 5. Register DEVID Field Descriptions**

| Bit | Field             | Туре | Reset | Description                                                                                                                                                         |

|-----|-------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | MANUFACTURER[3:0] | R    | 0000  | These bits identify the device manufacturer.  0000: Texas Instruments                                                                                               |

| 3:2 | MAJOR[1:0]        | R    | 01    | These bits identify the major silicon revision. 00: A (initial silicon) 01: B (first major revision) 10: C (second major revision) 11: D (third major revision)     |

| 1:0 | MINOR[1:0]        | R    | 00    | These bits identify the minor silicon revision.  00: 0 (initial silicon)  01: 1 (first minor revision)  10: 2 (second minor revision)  11: 3 (third minor revision) |

## 8.6.1.5 Register VOUT1 (Slave address: 0b1110101; Register address: 0x04; Default: 0x3C)

Return to Register Map.

## Figure 29. Register VOUT1 Format

| 7   | 6 5 |            | 4 | 3   | 2 | 1 | 0 |  |  |  |  |

|-----|-----|------------|---|-----|---|---|---|--|--|--|--|

| NIL |     | VOUT1[6:0] |   |     |   |   |   |  |  |  |  |

| R   |     |            |   | R/W |   |   |   |  |  |  |  |

LEGEND: R/W = Read/Write; R = Read only

### **Table 6. Register VOUT1 Field Descriptions**

| Bit | Field      | Туре | Reset   | Description                                                                                                                                                                                                                                            |

|-----|------------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | NIL        | R    | 0       | Not used This bit always returns 0 when read.                                                                                                                                                                                                          |

| 6:0 | VOUT1[6:0] | R/W  | 0111100 | These bits set the output voltage when the VSEL pin is low. Output voltage = $1.800 + (VOUT1[6:0] \times 0.025) \ V$ (low range) (default = $3.3 \ V$ ) Output voltage = $2.025 + (VOUT1[6:0] \times 0.025) \ V$ (high range) (default = $3.525 \ V$ ) |

## 8.6.1.6 Register VOUT2 (Slave address: 0b1110101; Register address: 0x05; Default: 0x42)

Back to Register Map.

## Figure 30. Register VOUT2 Format

| 7   | 6 5 |            | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|-----|-----|------------|---|---|---|---|---|--|--|--|--|

| NIL |     | VOUT2[6:0] |   |   |   |   |   |  |  |  |  |

| R   |     | R/W        |   |   |   |   |   |  |  |  |  |

LEGEND: R/W = Read/Write; R = Read only

### **Table 7. Register VOUT2 Field Descriptions**

| Bit | Field | Туре | Reset | Description                                   |

|-----|-------|------|-------|-----------------------------------------------|

| 7   | NIL   | R    | 0     | Not used This bit always returns 0 when read. |

# Table 7. Register VOUT2 Field Descriptions (continued)

| Bit | Field      | Туре | Reset   | Description                                                                                                                                                                                                                                                                      |

|-----|------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0 | VOUT2[6:0] | R/W  | 1000010 | These bits set the output voltage when the VSEL pin is high. Output voltage = $1.800 + (VOUT2[6:0] \times 0.025) \text{ V}$ (low range) (default = $3.45 \text{ V}$ ) Output voltage = $2.025 + (VOUT2[6:0] \times 0.025) \text{ V}$ (high range) (default = $3.675 \text{ V}$ ) |

# 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

The TPS63810 and TPS63811 devices are high efficiency, high current buck-boost converters, suitable for applications where the input voltage is higher, lower, or equal to the output voltage. The maximum peak current in the switches is limited to a typical value of 6 A.

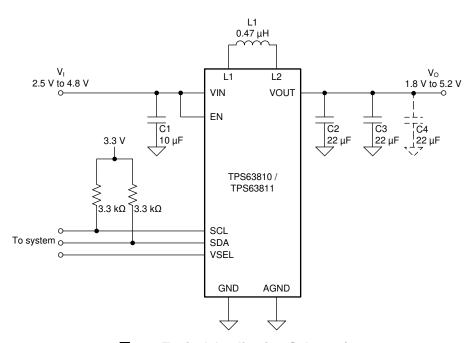

## 9.2 Typical Applications

### 9.2.1 1.8-V to 5.2-V Output Smartphone Power Supply

图 31. Typical Application Schematic

### 9.2.1.1 Design Requirements

This example uses the design parameters listed in 表 8.

# 表 8. Design Parameters

| DESIGN PARAMETER                 | SYMBOL           | EXAMPLE VALUE       |

|----------------------------------|------------------|---------------------|

| Input voltage                    | V <sub>I</sub>   | 2.5 V to 4.8 V      |

| Output voltage                   | Vo               | 1.8 V to 5.2 V      |

| Output current                   | I <sub>O</sub>   | 2 A                 |

| I <sup>2</sup> C bus voltage     | V <sub>BUS</sub> | 3.3 V               |

| I <sup>2</sup> C bus capacitance | C <sub>b</sub>   | 100 pF              |

| I <sup>2</sup> C bus speed       |                  | Fast-mode (400 kHz) |

### 9.2.1.2 Detailed Design Procedure

### 9.2.1.2.1 Input Capacitor Selection

TI recommends a minimum input capacitance (including DC bias effects) of 5  $\mu$ F. A 10- $\mu$ F, 10-V ceramic capacitor is suitable for typical applications. If the input supply is located more than a few centimeters from the converter, you may need to add additional bulk capacitance (a 47- $\mu$ F electrolytic or tantalum capacitor is a typical choice).

The output capacitance does not have an upper limit; you can make it as big as you want.

#### 9.2.1.2.2 Inductor Selection

TI recommends you use the TPS63810 device with 0.47-µH inductors. For high efficiencies, use an inductor with a low DC resistance (DCR) and low core losses.

The saturation current of the inductor must be greater than the maximum inductor current in your application. To include sufficient margin for worst-case and transient operating conditions, TI recommends you use an inductor with saturation current that is at least 20% higher than the maximum inductor current in your application. The maximum current in the inductor occurs when the device operates in boost mode and the following is true:

- The input voltage is at its minimum value.

- The output voltage is at its maximum value.

- · The output current is at its maximum value.

To calculate the maximum inductor current, first use  $\triangle \exists 1$  to calculate the maximum duty cycle during boost operation (which is when the maximum inductor current occurs).

$$D = \frac{V_O - V_I}{V_O}$$

where

- D is the duty cycle

- V<sub>1</sub> is the input voltage

- V<sub>O</sub> is the output voltage (1)

$$D = \frac{5 \text{ V} - 2.5 \text{ V}}{5 \text{ V}} = 0.5$$

Next, use 公式 2 to calculate the maximum inductor current.

$$I_{LM} = \frac{I_O}{\eta(1-D)} + \frac{DV_I}{2fL}$$

where

- I<sub>IM</sub> is the peak inductor current

- I<sub>O</sub> is the output current

- η is the converter efficiency (use the value from the application curves or assume 90%)

- D is the duty cycle (calculated with 公式 1)

- V<sub>I</sub> is the input voltage

- f is the switching frequency (assume 2 MHz)

- L is the inductance (use 0.47 μH)

$$I_{LM} = \frac{2 \text{ A}}{(0.9)(1 - 0.5)} + \frac{(0.5)(2.5 \text{ V})}{(2)(2 \text{ MHz})(0.47 \text{ }\mu\text{H})} = 5.1 \text{ A}$$

(2)

To include enough margin for transient conditions, TI recommends you use an inductor with a saturation current rating at least 20% higher than the calculated maximum current. In this example, TI recommends an inductor with a saturation current of at least 6.1 A.

### 9.2.1.2.3 Output Capacitor Selection

TI recommends a minimum output capacitance (including DC bias effects) of 16  $\mu$ F. Two 22- $\mu$ F, 10-V ceramic capacitors are suitable for typical applications with V<sub>O</sub>  $\leq$  3.6 V. For V<sub>O</sub> > 3.6 V, three 22- $\mu$ F or two 47- $\mu$ F ceramic capacitors are suitable. If you want to minimize switching noise on the output, connect a small ceramic capacitor (100 nF is a typical value) in parallel to the two main output capacitors and place it closest to the VOUT pin. Smaller capacitors have lower parasitic inductance and are more effective at filtering high frequencies than the two main output capacitors.

The output capacitance does not have an upper limit, however, very large values of output capacitance make the transient response of the converter slower.

It is important that the effective capacitance is given according to the recommended value in Recommended Operating Conditions. In general, consider DC bias effects resulting in less effective capacitance. The choice of the output capacitance is mainly a trade-off between size and transient behavior as higher capacitance reduces transient response overshoot and undershoot and increases transient response time. 表 9 lists possible output capacitors.

|                |                    |          | •                 |              |                  |

|----------------|--------------------|----------|-------------------|--------------|------------------|

| CAPACITOR [µF] | VOLTAGE RATING [V] | ESR [mΩ] | PART NUMBER       | MANUFACTURER | SIZE<br>(METRIC) |

| 22             | 6.3                | 10       | GRM187R60J226ME15 | Murata       | 0603 (1608)      |

| 22             | 10                 | 40       | GRM187R61A226ME15 | Murata       | 0603 (1608)      |

| 47             | 6.3                | 43       | GRM188R60J476ME15 | Murata       | 0603 (1608)      |

| 47             | 6.3                | 43       | GRM219R60J476ME44 | Murata       | 0805 (2012)      |

表 9. List of Recommended Capacitors<sup>(1)</sup>

### 9.2.1.2.4 I<sup>2</sup>C Pullup Resistor Selection

Refer to the NXP Semiconductors,  $UM10204 - {}^{\rho}C$ -Bus Specification and User Manual for the specifications relevant to your application.

Use 公式 3 to calculate the maximum permitted pullup resistor value for the bus speed used in the application.

$$R_P(max) = \frac{t_r}{0.8473 \times C_h}$$

where

- t<sub>r</sub> is the maximum permitted rise time (300 ns for Fast-mode)

- C<sub>b</sub> is the capacitive load on each bus line

$$R_P(max) = \frac{300 \text{ ns}}{0.8473 \times 100 \text{ pF}} = 3.541 \text{ k}\Omega$$

If you do not know what the bus capacitance is in your application, start with a 1-k $\Omega$  pullup resistor and measure the rise time with an oscilloscope. Use  $\Delta \vec{\Xi}$  3 to calculate the bus capacitance and thus the maximum permitted pullup resistor.

Use 公式 4 to calculate the minimum permitted pullup resistor value for different bus speeds.

$$R_{P}(min) = \frac{V_{BUS} - V_{OL}}{I_{OL}}$$

(3)

<sup>(1)</sup> See Third-party Products Disclaimer.

where

- V<sub>BUS</sub> is the I<sup>2</sup>C bus pullup voltage

- V<sub>OL</sub> is the low-level output voltage (0.4 V)

- I<sub>OL</sub> is the low-level output current (3 mA for Fast-mode) (4)

$$R_P(min) = \frac{3.3 \text{ V} - 0.4 \text{ V}}{3 \text{ mA}} = 967 \Omega$$

A pullup resistor value of 3.3  $\mbox{k}\Omega$  meets both of these requirements.

## 9.2.1.3 Application Curves

表 10 lists the components that were used for the measurements contained in the following pages.

# 表 10. Components for Application Characteristic Curves

| REFERENCE | DESCRIPTION                           | PART NUMBER       | MANUFACTURER      |

|-----------|---------------------------------------|-------------------|-------------------|

| C1        | Capacitor, 10 µF, 10 V, 0603, ceramic | GRM188R61A106ME69 | Murata            |

| C2, C3    | Capacitor, 22 µF, 10 V, 0603, ceramic | GRM187R61A226ME15 | Murata            |

| L1        | Inductor, 0.47 μH                     | XFL4015-471MEC    | Coilcraft         |

| U1        | Integrated circuit                    | TPS63810YFF       | Texas Instruments |

## 10 Power Supply Recommendations

The device is designed to operate with a DC supply voltage in the range 2.2 V to 5.5 V. If the input supply is more than a few centimeters from the device, TI recommends adding some bulk capacitance to the ceramic bypass capacitors. A  $47-\mu F$  electrolytic capacitor is a typical selection for the bulk capacitance.

# 11 Layout

## 11.1 Layout Guidelines

Correct PCB layout is necessary to obtain the full performance from the device. TI recommends to follow these basic principles:

- Place input and output capacitors close to the device to minimize the input and output loop areas.

- If you combine different-sized capacitors to make up the total input capacitance, place the smallest capacitor closest to the device. The same applies to the output capacitance.

- Keep PCB traces short and wide to minimize parasitic resistance and inductance.

- Use the following PCB layer stack (or something similar):

- Layer 1 (top): All components and all power traces

- Layer 2 (inner): Signals

- Layer 3 (inner): Signals

- Layer 4 (bottom): Ground plane

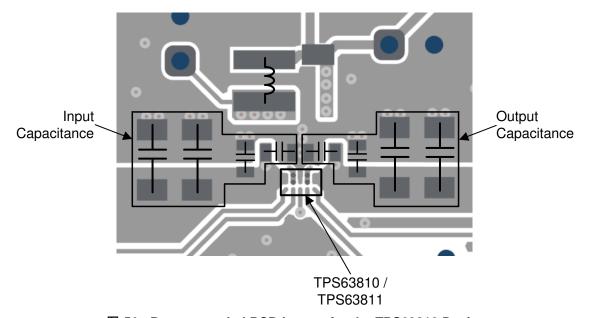

图 56 shows an example of the PCB layout used for all of the measurement data in *Application Curves*.

## 11.2 Layout Example

图 56. Recommended PCB Layout for the TPS63810 Device

## 12 器件和文档支持

### 12.1 器件支持

### 12.1.1 第三方产品免责声明

TI 发布的与第三方产品或服务有关的信息,不能构成与此类产品或服务或保修的适用性有关的认可,不能构成此类产品或服务单独或与任何 TI 产品或服务一起的表示或认可。

### 12.2 文档支持

### 12.2.1 相关文档

请参阅如下相关文档:

- NXP 半导体, 《UM10204 PC 总线规范和用户手册》

- 德州仪器 (TI), 《TPS63810 EVM 用户指南》

### 12.3 相关链接

下表列出了快速访问链接。类别包括技术文档、支持和社区资源、工具和软件,以及立即订购快速访问。