SLVS531A-JUNE 2004-REVISED MARCH 2005

# SINGLE-INDUCTOR QUADRUPLE-OUTPUT TFT LCD POWER SUPPLY

#### **FEATURES**

- Main Output, V<sub>MAIN</sub>

- Adjustable Voltage, 3.0 V to 5.6 V/25 mA

- Post-Regulated for Low Ripple (5mV<sub>PP</sub>)

- ±0.8% Typical Accuracy

- Efficiency up to 83%

- Positive Output, V<sub>GH</sub>

- Adjustable Voltage up to 20 V/2 mA

- ±3% Typical Accuracy

- Negative Output, V<sub>GL</sub>

- Adjustable Voltage down to -18 V/2 mA

- ±3% Typical Accuracy

- Auxiliary 1.8 V/3.3 V Linear Regulator

- Automatic or Programmable Power Sequencing

- Complete 1 mm Component Profile Solution

- 2.5 V to 5.5 V Input Voltage Range

- Output Short Circuit Protected

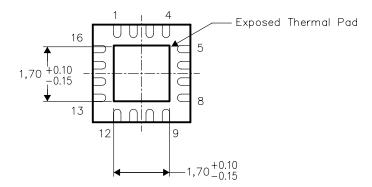

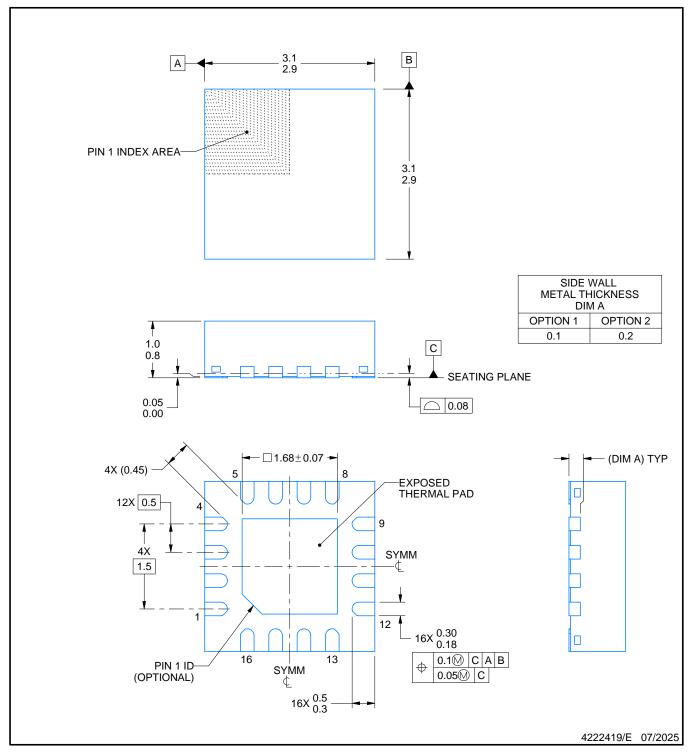

- 16-Pin QFN Package (3 x 3 x 0,9 mm)

#### **APPLICATIONS**

- Small Form Factor a-Si and LTPS TFT LCD

- Cell Phones, Smart Phones

- PDAs, Pocket PCs

- Portable DVD

- Digital-Still Cameras, Camcorders

- Handheld Instruments

- Portable GPS

- Car Navigation Systems

#### **DESCRIPTION**

The TPS6512x DC-DC converter supplies all three voltages required by amorphous-silicon (a-Si) and low-temperature poly-silicon (LTPS) TFT-LCD displays. The compact layout of the TPS6512x uses a single inductor to generate independently-regulated positive and negative outputs. A free-running variable peak current PWM control scheme time-multiplexes the inductor between outputs. This control architecture operates at a pseudo-fixed-frequency to provide fast response to line and load transients while maintaining a relatively constant switching frequency and high efficiency over a wide range of input and output voltages. Due to the high switching frequency capability of the device, inexpensive and ultra-thin 8.2 or 10 µH inductors can be used.

The main output,  $V_{MAIN}$ , is post-regulated to provide a low-ripple source drive voltage for the LCD display. The auxiliary outputs generate a boosted output voltage,  $V_{GH}$ , up to 20 V, and a negative output voltage,  $V_{GL}$ , down to -18 V for the LCD gate drive. The device has internal current limiting for high reliability under fault conditions. Additionally, the device offers a fixed output linear regulator for the LCD logic circuitry.

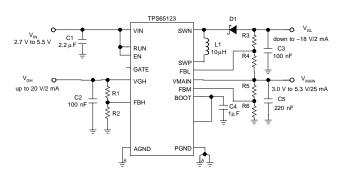

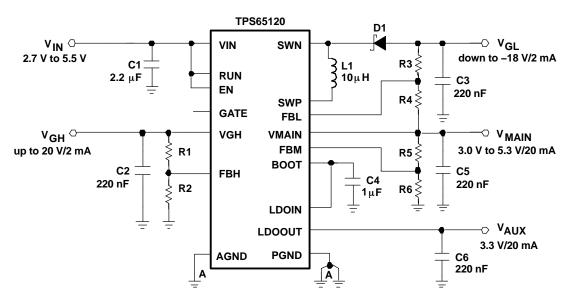

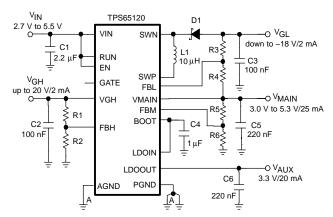

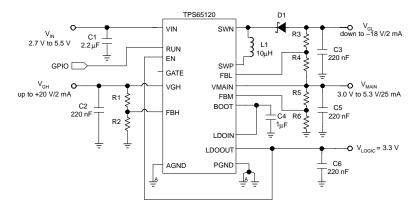

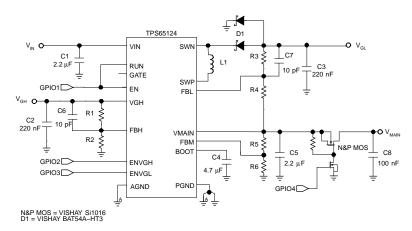

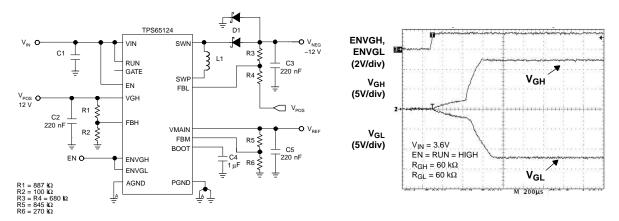

Figure 1. Typical Application

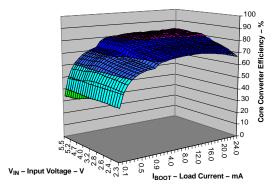

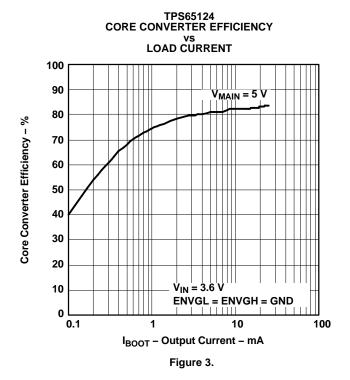

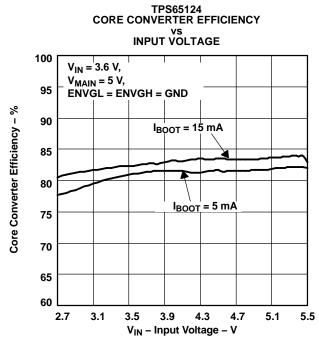

Figure 2. Core Converter Efficiency

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **ORDERING INFORMATION**

| T <sub>A</sub> | INTEGRATED<br>LINEAR REGULATOR | POWER SEQUENCING              | PACKAGE      | PART NUMBER <sup>(1)</sup> | PACKAGE<br>MARKING |

|----------------|--------------------------------|-------------------------------|--------------|----------------------------|--------------------|

|                | Fixed 3.3V output voltage      | Automatic Power-Up/Down       | 3 × 3 QFN-16 | TPS65120RGT                | BKA                |

|                | Fixed 1.8V output voltage      | Automatic Power-Up/Down       | 3 × 3 QFN-16 | TPS65121RGT                | BKB                |

| -40 to 85°C    | NO                             | Automatic Power-Up/Down       | 3 × 3 QFN-16 | TPS65123RGT                | BKC                |

|                | NO                             | Programmable<br>Power-Up/Down | 3 × 3 QFN-16 | TPS65124RGT                | BKD                |

<sup>(1)</sup> The xyz package is available in tape and reel. Add R suffix (xyzR) to order quantities of TBD parts. Add T suffix (xyzT) to order quantities of 250 parts.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                                                              |                                    | UNIT                               |

|--------------------------------------------------------------|------------------------------------|------------------------------------|

|                                                              | VIN                                | -0.3 V to +6 V                     |

| Input voltage <sup>(2)</sup>                                 | SWN                                | $V_{IN}$ - 24 V to $V_{IN}$ +0.3 V |

|                                                              | SWP                                | - 0.3 V to +23 V                   |

|                                                              | VGH                                | - 0.3 V to +21 V                   |

| Voltage <sup>(2)</sup>                                       | VMAIN, LDOIN, LDOOUT, ENVGL, ENVGH | - 0.3 V to +6 V                    |

|                                                              | BOOT                               | - 0.3 V to +6.2 V                  |

| Input voltage at GATE,                                       | EN, RUN <sup>(2)</sup>             | -0.3 V to V <sub>IN</sub> + 0.3 V  |

| Power dissipation                                            |                                    | Internally limited                 |

| Operating temperature range                                  |                                    | -40°C to 85°C                      |

| Maximum operating junction temperature, T <sub>J</sub> (max) |                                    | 135°C                              |

| Storage temperature range                                    |                                    | 65°C to 150°C                      |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **DISSIPATION RATINGS**(1)

| PACKAGE | $R_{\theta JA}$ | DERATING FACTOR ABOVE T <sub>A</sub> = 25°C |  |  |  |

|---------|-----------------|---------------------------------------------|--|--|--|

| RGT     | 68°C/W          | 15mW/°C                                     |  |  |  |

(1) Maximum power dissipation is a function of  $T_J(max)$ ,  $\theta_{JA}$  and  $T_A$ . The maximum allowable power dissipation at any allowable ambient temperature is  $P_D = [T_J(max) - T_A]/\theta_{JA}$ .

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 3.6 V, EN = RUN =  $V_{IN}$ , L = 10  $\mu$ H,  $T_A$  = -40 °C to 85 °C, typical values are at  $T_A$  = 25 °C (unless otherwise noted)

|                       | PARAMETER                                          | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                               | MIN      | TYP  | MAX  | UNIT |  |

|-----------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|------|--|

| CONVERT               | ER STAGE                                           |                                                                                                                                                                                                                                                                                                                                                               |          |      |      |      |  |

| $V_{IN}$              | Input voltage for full load operation              | $\begin{split} R_{L\_MAIN} &\geq 330~\Omega \text{ at V}_{MAIN} = 5~\text{V}, \\ R_{L\_VGH} &\geq 12~\text{k}\Omega \text{ at V}_{GH} = 12~\text{V}, \\ R_{L\_VGL} &\geq 12~\text{k}\Omega \text{ at V}_{GL} = -12~\text{V}, \\ V_{LDOIN} &= \text{GND}, T_A = -40^{\circ}\text{C to }85^{\circ}\text{C} \end{split}$                                         | 2.7      |      | 5.5  | V    |  |

| VIN                   | Minimum input voltage for start-up                 | $\begin{array}{l} {\rm R_{L\_MAIN}}{\geq}~660~\Omega~{\rm at}~{\rm V_{MAIN}} = 5~{\rm V},\\ {\rm R_{L\_VGH}}{\geq}~24~{\rm k}\Omega~{\rm at}~{\rm V_{GH}} = 12~{\rm V},\\ {\rm R_{L\_VGL}}{\geq}~24~{\rm k}\Omega~{\rm at}~{\rm V_{GL}} = -12~{\rm V},\\ {\rm V_{LDOIN}}{=}~{\rm GND},~{\rm T_A} = -20^{\circ}{\rm C}~{\rm to}~85^{\circ}{\rm C} \end{array}$ | 2.5      |      |      | V    |  |

| f                     | Switching frequency                                | $R_{L\_MAIN}$ = 250 $\Omega$ at $V_{MAIN}$ = 5 $V_{LDOIN}$ = ENVGH = ENVGL = GND                                                                                                                                                                                                                                                                              |          | 4.0  |      | MHz  |  |

| $P_GH$                | Output power on V <sub>GH</sub>                    | V <sub>IN</sub> ≥ 2.7 V<br>V <sub>IN</sub> ≥ 2.5 V                                                                                                                                                                                                                                                                                                            | 35<br>15 |      |      | mW   |  |

| _                     |                                                    | V <sub>IN</sub> ≥ 2.7 V                                                                                                                                                                                                                                                                                                                                       | 35       |      |      |      |  |

| $P_{GL}$              | Output power on V <sub>GL</sub>                    | V <sub>IN</sub> ≥ 2.5 V                                                                                                                                                                                                                                                                                                                                       | 15       |      |      | mW   |  |

|                       |                                                    | V <sub>IN</sub> ≥ 2.5 V                                                                                                                                                                                                                                                                                                                                       | 60       |      |      |      |  |

| P <sub>TOT</sub>      | Total output power on $V_{BOOT} + V_{GH} + V_{GL}$ | V <sub>IN</sub> ≥ 2.7 V                                                                                                                                                                                                                                                                                                                                       | 120      |      |      | mW   |  |

|                       |                                                    | V <sub>IN</sub> ≥ 3 V                                                                                                                                                                                                                                                                                                                                         | 150      |      |      |      |  |

|                       |                                                    | V <sub>IN</sub> ≥ 4.5 V                                                                                                                                                                                                                                                                                                                                       | 250      |      |      |      |  |

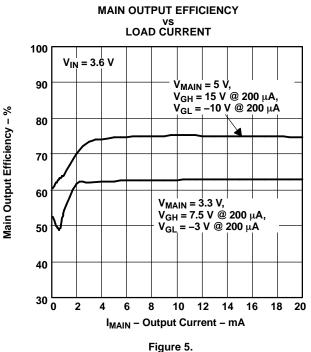

| η                     | Power efficiency                                   | $V_{MAIN} = 5.0 \text{ V}, I_{BOOT} = 20 \text{ mA}, \\ V_{GH} = 15 \text{ V}, V_{GL} = -10 \text{ V}, \\ I_{GH} = I_{GL} = 100  \mu\text{A}, V_{LDOIN} = \text{GND}$                                                                                                                                                                                         |          | 83%  |      |      |  |

| I <sub>LIM</sub>      | P-MOS1 current limit                               | 2.7 V ≤ V <sub>IN</sub> ≤ 5.5 V                                                                                                                                                                                                                                                                                                                               |          | 150  | 200  | mA   |  |

| I <sub>START-UP</sub> | P-MOS1 start-up current limit                      | 2.7 V ≤ V <sub>IN</sub> ≤ 5.5 V                                                                                                                                                                                                                                                                                                                               |          | 65   |      | mA   |  |

|                       | D MOCA switch on recistores                        | V <sub>IN</sub> = V <sub>GS</sub> = 3.6 V                                                                                                                                                                                                                                                                                                                     |          | 2.5  | 4.3  | 0    |  |

|                       | P-MOS1 switch on-resistance                        | $V_{IN} = V_{GS} = 2.5 \text{ V}$                                                                                                                                                                                                                                                                                                                             |          | 3.8  | 6.9  | Ω    |  |

|                       | N MOS1 quitab en registance                        | V <sub>BOOT</sub> = V <sub>GS</sub> = 3.7 V                                                                                                                                                                                                                                                                                                                   |          | 1.9  | 3.5  | Ω    |  |

| r <sub>DS(ON)</sub>   | N-MOS1 switch on-resistance                        | $V_{BOOT} = V_{GS} = 5 \text{ V}$                                                                                                                                                                                                                                                                                                                             |          | 1.4  | 2.3  | 22   |  |

|                       | P-MOS1 leakage current                             | V <sub>DS</sub> = 6 V, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                  |          | 0.01 |      | μA   |  |

|                       | N-MOS1 leakage current                             | V <sub>DS</sub> = 0 V, 1 <sub>A</sub> = 23 C                                                                                                                                                                                                                                                                                                                  |          | 0.01 |      | μΛ   |  |

|                       | N-MOS2 + P-MOS2 forward voltage drop               | $V_{GS} = V_{BOOT} = 5.5 \text{ V}, V_{SWP} = 2 \text{ V},$ $I_{BOOT} = I_D = 50 \text{ mA}$                                                                                                                                                                                                                                                                  |          | 400  | 600  | mV   |  |

|                       | N-MOS3 + D1 forward voltage drop                   | $V_{GS} = V_{BOOT} = 5.5 \text{ V}, V_{SWP} = 2 \text{ V}, \\ I_{GH} = I_{D} = 50 \text{ mA}$                                                                                                                                                                                                                                                                 |          | 900  | 1100 | mV   |  |

| CONVERT               | ER SUPPLY CURRENT                                  |                                                                                                                                                                                                                                                                                                                                                               |          |      |      |      |  |

|                       | Quiescent current into VIN                         | $I_{MAIN} = I_{GH} = I_{GL} = 0 \text{ mA},$                                                                                                                                                                                                                                                                                                                  |          | 140  | 170  |      |  |

|                       | Quiescent current into BOOT                        | $V_{GH} = +15 \text{ V}, V_{GL} = -15 \text{ V},$<br>$V_{MAIN} = 5 \text{ V}, V_{FBH} = V_{FBM} = +1.5 \text{ V},$                                                                                                                                                                                                                                            |          | 30   | 60   |      |  |

| lα                    | Quiescent current into VGH                         | V <sub>FBL</sub> = -0.2 V, V <sub>BOOT</sub> = 5.25 V,<br>V <sub>LDOIN</sub> = GND, EN = RUN = V <sub>IN</sub> ,<br>T <sub>A</sub> = 25°C                                                                                                                                                                                                                     |          | 0.1  | 1    | μA   |  |

| I <sub>SD</sub>       | Shutdown current                                   | T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                         |          | 0.1  | 1    | μA   |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN}$  = 3.6 V, EN = RUN =  $V_{IN}$ , L = 10  $\mu$ H,  $T_A$  = -40 °C to 85 °C, typical values are at  $T_A$  = 25 °C (unless otherwise noted)

|                        | PARAMETER                                  | TEST CONDITIONS                                                                                                                    | MIN                   | TYP   | MAX   | UNIT       |

|------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-------|------------|

| MAIN OUTI              | PUT                                        |                                                                                                                                    |                       |       |       |            |

| V <sub>MAIN</sub>      | Main output voltage range                  |                                                                                                                                    | 3.0                   |       | 5.6   | V          |

|                        | Manifester                                 | V <sub>MAIN</sub> ≤ 5.3 V                                                                                                          | 25                    |       |       |            |

| I <sub>MAIN</sub>      | Maximum main output current                | V <sub>MAIN</sub> ≥ 5.3 V                                                                                                          | 7.5                   |       |       | mA         |

| V                      | Feedback regulation voltage                | 2.7 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V, 100 $\mu$ A $\leq$ I <sub>MAIN</sub> $\leq$ 25 mA, T <sub>A</sub> = -20°C to 50°C       | 1.203                 | 1.213 | 1.223 | V          |

| $V_{FBM}$              | reeuback regulation voltage                | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V},$<br>$0 \text{ mA} \le \text{I}_{\text{MAIN}} \le 25 \text{ mA}$         | 1.195                 | 1.213 | 1.231 | V          |

| $I_{FBM}$              | Feedback input bias current                | $V_{FBM} = V_{REF}$                                                                                                                |                       | 0.01  | 0.1   | μA         |

|                        | Load regulation                            | $I_{MAIN} = 0$ to 25 mA, $V_{MAIN} = 5$ V                                                                                          |                       | 0.006 |       | %/mA       |

|                        | Minimum dropout voltage                    | I <sub>MAIN</sub> = 10 mA                                                                                                          |                       | 130   |       | mV         |

|                        | Main output voltage ripple                 | I <sub>MAIN</sub> = 10 mA                                                                                                          |                       | 5     |       | $mV_{P-P}$ |

| I <sub>SC_MAIN</sub>   | Short-circuit current limit                | V <sub>BOOT</sub> = 5.5 V                                                                                                          |                       |       | 50    | mA         |

| R <sub>DIS_VMAIN</sub> | Discharge resistor for power-down sequence |                                                                                                                                    |                       | 10    |       | kΩ         |

| VGH OUTP               | UT                                         |                                                                                                                                    |                       |       |       |            |

| $V_{GH}$               | V <sub>GH</sub> output voltage range       |                                                                                                                                    | V <sub>IN</sub> + 0.5 |       | 20    | V          |

| I <sub>GH</sub>        | Maximum DC output current                  |                                                                                                                                    |                       |       | 6     | mA         |

|                        | V <sub>GH</sub> precharge resistor         |                                                                                                                                    |                       | 1     |       | kΩ         |

| $V_{FBH}$              | Feedback regulation voltage                | $2.7 \text{ V} \le V_{IN} \le 5.5 \text{ V}, \text{ 0 mA} \le I_{GH} \le 2 \text{ mA}$                                             | 1.177                 | 1.213 | 1.249 | V          |

| I <sub>FBH</sub>       | Feedback input bias current                | V <sub>FBH</sub> = 0 V                                                                                                             |                       | 0.01  | 0.1   | μA         |

|                        | Load regulation                            | $I_{GH} = 0$ to 2 mA, $V_{GH} = 15$ V                                                                                              |                       | -0.11 |       | %/mA       |

|                        | Line regulation                            | $V_{IN} = 2.7 \text{ V to } 5.5 \text{ V}, I_{GH} = 100  \mu\text{A}$                                                              |                       | 0.01  |       | %/V        |

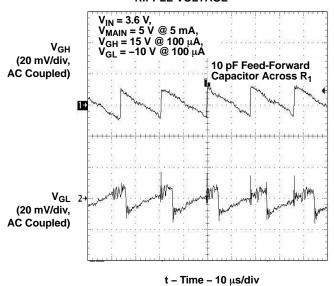

|                        | V <sub>GH</sub> output voltage ripple      | 200 $\mu$ A load, V <sub>GH</sub> = 15 V,<br>C <sub>OUT</sub> = 220 nF, C <sub>FF</sub> = 10 pF                                    |                       | 20    |       | mV         |

| R <sub>DIS_VGH</sub>   | Discharge resistor for power-down sequence |                                                                                                                                    |                       | 10    |       | kΩ         |

| VGL OUTP               | UT                                         |                                                                                                                                    |                       |       |       |            |

| $V_{GL}$               | V <sub>GL</sub> Output voltage range       |                                                                                                                                    | -18                   |       | -2.5  | V          |

| I <sub>GL</sub>        | Maximum DC output current                  |                                                                                                                                    |                       |       | 6     | mA         |

| $V_{FBL}$              | Feedback regulation voltage                | $2.7~\textrm{V} \leq \textrm{V}_{\textrm{IN}} \leq 5.5~\textrm{V},~0~\textrm{mA} \leq \textrm{I}_{\textrm{GL}} \leq 2~\textrm{mA}$ | -0.036                | 0     | 0.036 | V          |

| I <sub>FBL</sub>       | Feedback input bias current                | V <sub>FBL</sub> = 0 V                                                                                                             |                       | 0.01  | 0.1   | μΑ         |

|                        | Load regulation                            | $I_{GL}$ = 0 to 2 mA, $V_{GL}$ = -15 V                                                                                             |                       | 0.13  |       | %/mA       |

|                        | Line regulation                            | $V_{IN}$ = 2.7 V to 5.5 V, $I_{GL}$ = 100 $\mu$ A                                                                                  |                       | 0.1   |       | %/V        |

|                        | V <sub>GL</sub> output voltage ripple      | 200 $\mu$ A load, V <sub>GL</sub> = -15 V, C <sub>OUT</sub> = 220 nF                                                               |                       | 20    |       | mV         |

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN} = 3.6 \text{ V}$ , EN = RUN =  $V_{IN}$ , L = 10  $\mu$ H,  $T_A = -40 ^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$ , typical values are at  $T_A = 25 ^{\circ}\text{C}$  (unless otherwise noted)

| PARAMETER           |                                    | TEST CONDITIONS                                                                                                                 | MIN      | TYP   | MAX                        | UNIT |

|---------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------|-------|----------------------------|------|

| LINEAR R            | EGULATOR STAGE - AUXILIARY OUTP    | UT                                                                                                                              |          |       |                            |      |

| $V_{LDOIN}$         | Input voltage range                |                                                                                                                                 | 2.5      |       | 5.8                        | V    |

| $V_{LDOOUT}$        | Output voltage range               |                                                                                                                                 | 1.8      |       | V <sub>LDOIN</sub><br>-0.5 | V    |

| I <sub>LDOOUT</sub> | Maximum output current             |                                                                                                                                 | 20       |       |                            | mA   |

| I <sub>SC_LDO</sub> | Short-circuit current limit        | V <sub>LDOOUT</sub> = 0 V                                                                                                       |          |       | 50                         | mA   |

|                     | Minimum dropout voltage            | I <sub>LDOOUT</sub> = 10 mA                                                                                                     |          |       | 400                        | mV   |

|                     | Total accuracy                     | $2.5 \text{ V} \le \text{V}_{\text{LDOIN}} \le 5.5 \text{ V},$<br>$0 \text{ mA} \le \text{I}_{\text{LDOOUT}} \le 20 \text{ mA}$ |          |       | ±3%                        |      |

|                     | Load regulation                    | I <sub>LDOOUT</sub> = 0 to 20 mA                                                                                                |          | 0.006 |                            | %/mA |

|                     | Line regulation                    | V <sub>LDOIN</sub> = V <sub>LDOOUT</sub> + 0.5 V (min 2.5 V)<br>to 5.5 V, I <sub>LDOOUT</sub> = 20 mA                           |          | 0.013 |                            | %/V  |

| $I_{Q\_LDO}$        | Linear regulator quiescent current | $V_{LDOIN} = V_{LDOOUT} + 0.4 \text{ V (min 2.5 V)},$<br>$T_A = 25^{\circ}\text{C}$                                             |          | 11    | 20                         | μA   |

| I <sub>SD_LDO</sub> | Linear regulator shutdown current  | GATE = VIN                                                                                                                      |          | 0.2   | 1                          | μΑ   |

| GATE DR             | IVER                               |                                                                                                                                 |          |       |                            |      |

|                     | Gate output pull-down resistance   | V <sub>GATE</sub> < 500 mV                                                                                                      |          | 100   |                            | kΩ   |

|                     | Gate output pull-up resistance     |                                                                                                                                 |          | 100   |                            | kΩ   |

| V <sub>IH</sub>     | High level input voltage           |                                                                                                                                 | 1.4      |       |                            | V    |

| V <sub>IL</sub>     | Low level input voltage            |                                                                                                                                 |          |       | 0.4                        | V    |

| UNDERVO             | OLTAGE LOCKOUT                     |                                                                                                                                 |          |       |                            |      |

| $V_{UVLO}$          | Undervoltage lockout threshold     | V <sub>IN</sub> falling                                                                                                         |          | 2.15  | 2.3                        | V    |

| LOGIC SI            | GNALS EN, RUN, ENVGL, ENVGH        |                                                                                                                                 |          |       |                            |      |

| $V_{IH}$            | High level input voltage           |                                                                                                                                 | 1.4      |       |                            | V    |

| V <sub>IL</sub>     | Low level input voltage            |                                                                                                                                 |          |       | 0.4                        | V    |

| L                   | Logic input leakage current        | ENVGL, ENVGH = V <sub>IN</sub> or GND (TPS65124)                                                                                | 0.01     |       | 0.1                        | μA   |

| I <sub>LKG</sub>    | Logic input leakage current        | EN, RUN = V <sub>IN</sub>                                                                                                       | 0.01 0.1 |       |                            | μΛ   |

|                     | EN, RUN pin pull-down resistance   | EN, RUN ≤ 0.4 v                                                                                                                 |          | 100   |                            | kΩ   |

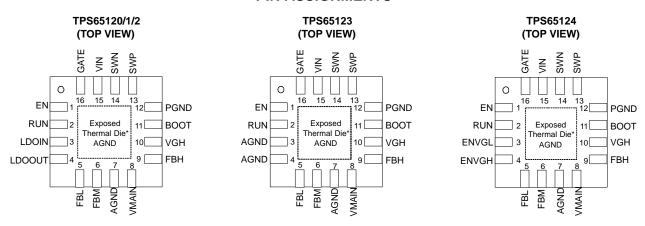

#### **PIN ASSIGNMENTS**

# **TERMINAL FUNCTIONS**

| TERM   | INAL    | 1/0 | DECODIFICAL                                                                                                                                                                                                                                                                      |

|--------|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                      |

| VIN    | 15      | I   | This is the input voltage pin of the device.                                                                                                                                                                                                                                     |

| GATE   | 16      | I/O | This pin can either be the gate driver output to an external small P-Channel MOSFET (see application section), or an active high control input. Pulling GATE above the 1.4 V logic-high level and RUN to a logic-low level disables the integrated active power-down sequencing. |

| RUN    | 2       | I   | RUN controls the external P-Channel MOSFET. This pin must be terminated and not be left floating. Forcing this pin to a logic-high level turns on the external MOSFET switch.                                                                                                    |

| EN     | 1       | I   | This is the enable pin of the multiple-output dc-to-dc converter. This pin must be terminated and not be left floating. A simultaneous logic-high level on EN and RUN enables the converter and a logic-low shuts down the device.                                               |

| SWN    | 14      | I/O | Connect the inductor to this pin. This pin is connected to the source of the high-side MOSFET switch.                                                                                                                                                                            |

| SWP    | 13      | I/O | Connect the inductor to this pin. This pin is connected to the drain of the low-side MOSFET switch.                                                                                                                                                                              |

| PGND   | 12      | 0   | Power ground. Connect to AGND underneath the IC.                                                                                                                                                                                                                                 |

| VGH    | 10      | 0   | Positive output                                                                                                                                                                                                                                                                  |

| воот   | 11      | 0   | Provides a bootstrapped supply for the rectifier MOSFET driver, enabling the gate of the MOSFET to be driven above the output voltage.                                                                                                                                           |

| VMAIN  | 8       | I   | Main output                                                                                                                                                                                                                                                                      |

| FBH    | 9       | I   | Feedback pin for the positive output voltage divider. Regulates to 1.213 V nominal.                                                                                                                                                                                              |

| FBL    | 5       | I   | Feedback pin for the negative output voltage divider. Regulates to 0 V nominal. Connect feedback resistor divider between VGL and main output.                                                                                                                                   |

| FBM    | 6       | I   | Feedback pin for the main output voltage divider. Regulates to 1.213V nominal.                                                                                                                                                                                                   |

| AGND   | 7, 3, 4 |     | Analog ground. Connect to power ground (PGND) underneath IC. Pins 3 and 4 are only used for AGND in TPS65123.                                                                                                                                                                    |

| LDOIN  | 3       | I   | Auxiliary linear regulator input. If this pin is connected to GND, the voltage regulator is disabled (TPS65120/1/2). The low-dropout series-pass regulator (LDO) is enabled according to the GATE signal timing.                                                                 |

| LDOOUT | 4       | 0   | Auxiliary linear regulator output (TPS65120/1/2).                                                                                                                                                                                                                                |

| ENVGL  | 3       | I   | Enable pin for negative output (TPS65124). This pin should be terminated and not be left floating.                                                                                                                                                                               |

| ENVGH  | 4       | I   | Enable pin for positive output (TPS65124). This pin should be terminated and not be left floating.                                                                                                                                                                               |

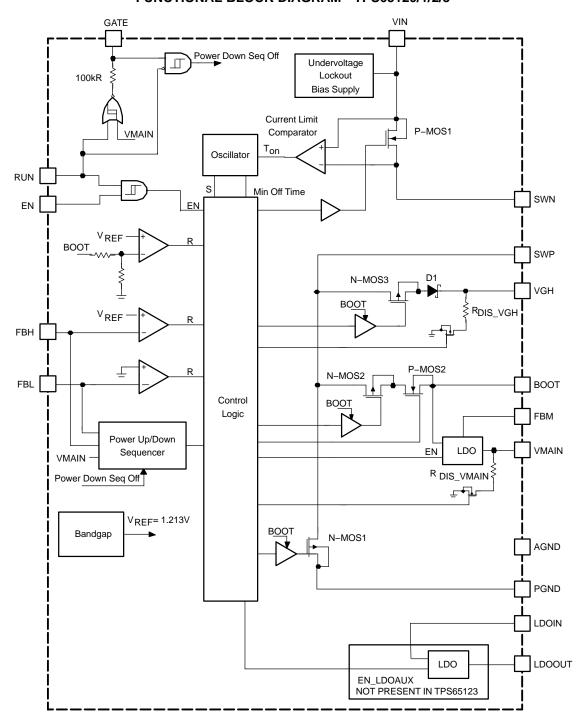

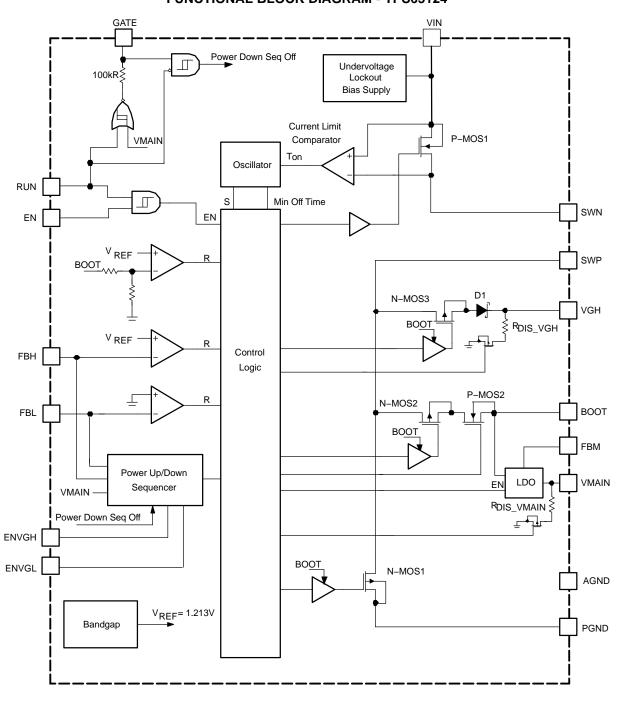

# **FUNCTIONAL BLOCK DIAGRAM - TPS65120/1/2/3**

# **FUNCTIONAL BLOCK DIAGRAM - TPS65124**

#### PARAMETER MEASUREMENT INFORMATION

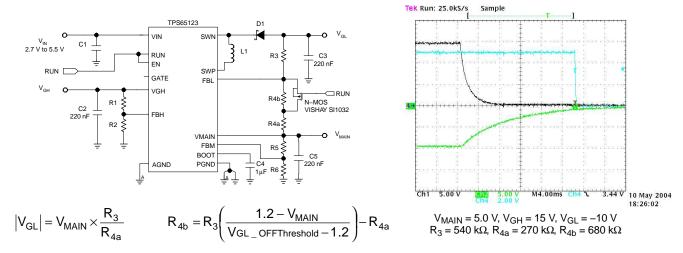

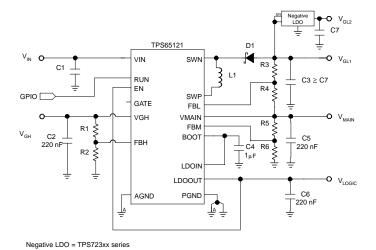

List of Components:  $\begin{array}{l} U_1 = \text{TPS6512x} \\ L_1 = \text{EPCOS SIMID1812-C} \\ D_1 = \text{ZETEX ZUMD54C} \\ C_X = \text{X5R/X7R} \end{array}$

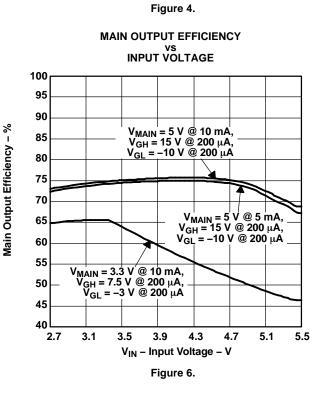

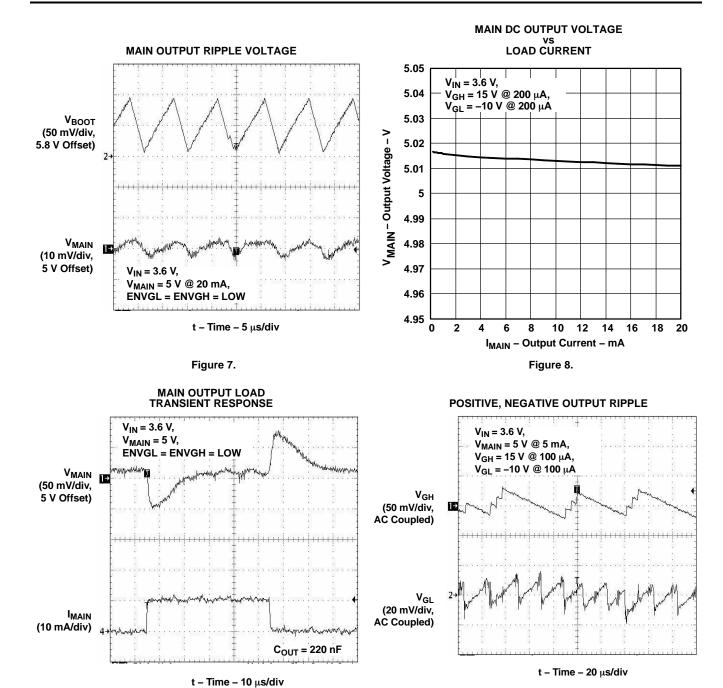

#### **TYPICAL CHARACTERISTICS**

#### **Table of Graphs**

|                     |                                          |                  | FIGURE |

|---------------------|------------------------------------------|------------------|--------|

| η                   | Core converter efficiency                | vs Load current  | 3      |

|                     |                                          | vs Input voltage | 4      |

|                     | Main output efficiency                   | vs Load current  | 5      |

|                     |                                          | vs Input voltage | 6      |

| V <sub>MAIN</sub>   | Output ripple voltage                    |                  | 7      |

|                     | DC output voltage                        | vs Load current  | 8      |

|                     | Load transient response                  |                  | 9      |

| $V_{GH}$ , $V_{GL}$ | Positive, negative output ripple voltage |                  | 10, 11 |

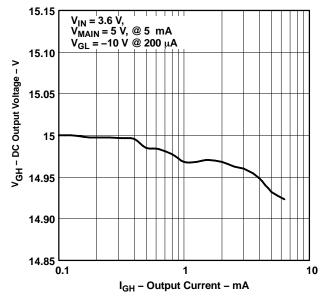

| $V_{GH}$            | DC output voltage                        | vs Load current  | 12     |

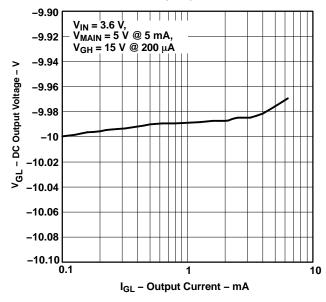

| $V_{GL}$            | DC output voltage                        | vs Load current  | 13     |

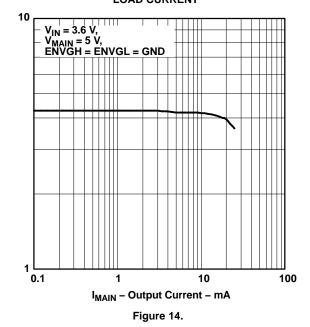

| f <sub>s</sub>      | Switching frequency                      | vs Load current  | 14     |

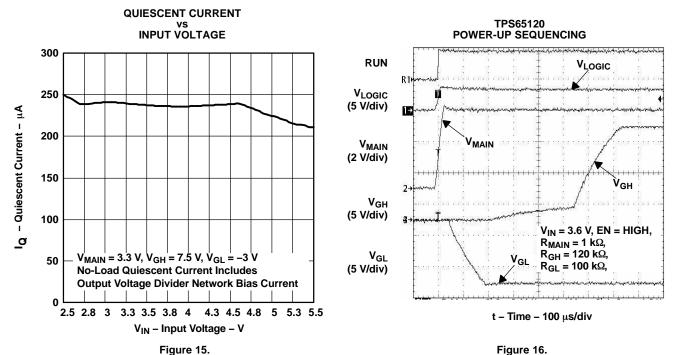

| IQ                  | No load quiescent current                | vs Input voltage | 15     |

|                     | Power-Up Sequencing (TPS65120)           |                  | 16     |

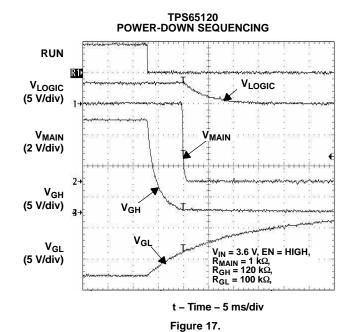

|                     | Power-Down Sequencing (TPS65120)         |                  | 17     |

Figure 10.

Figure 9.

11

# POSITIVE, NEGATIVE OUTPUT RIPPLE VOLTAGE

Figure 11.

## **NEGATIVE OUTPUT (VGL) LOAD REGULATION**

Figure 13.

#### **POSITIVE OUTPUT (VGH) LOAD REGULATION**

Figure 12.

# SWITCHING FREQUENCY vs LOAD CURRENT

Switching Frequency - MHz

Figure 16.

#### **DETAILED DESCRIPTION**

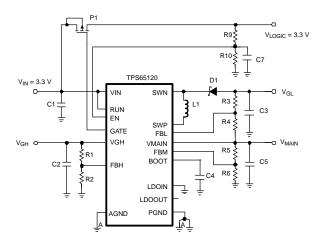

The standard application circuit (Figure 1) of the TPS65120 is a complete power supply for TFT LCD displays. The circuit generates four independent supplies for the source driver ( $V_{MAIN}$ ), the gate drivers ( $V_{GH}$ ,  $V_{GL}$ ) and a logic supply for the timing controller. The input voltage range is from 2.5 V to 5.5 V.

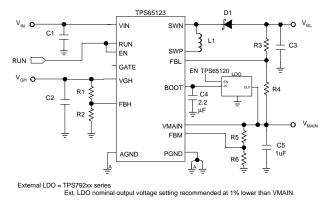

The TPS65120/1/2 contains a high-performance switching regulator and two low-dropout linear regulators (LDOs). One of the LDOs generates  $V_{MAIN}$  and the other powers the logic inside the panel. The TPS65123 includes only one linear regulator to provide the main output with low ripple voltage and can be set from 3.0 V to 5.3 V with an external resistor voltage divider. The TPS65124 integrates programmable power sequencing for highest flexibility.

#### **OPERATION**

The TPS6512x generates both positive and negative supply voltages using a single inductor. It alternates between acting as a step-up converter and an inverting converter on a cycle-by-cycle basis. All output voltages are independently regulated.

A free-running, variable-peak-current PWM control scheme is used to time-multiplex the inductor between BOOT,  $V_{GH}$ , and  $V_{GL}$  outputs. This inherently-stable control architecture operates at a pseudo fixed frequency, providing fast response to line and load transients while maintaining a relatively constant switching frequency and high efficiency over a wide range of input and output voltages.

During the first cycle of operation, internal switches N-MOS1 and P-MOS1 are turned on. SWN connects to VIN, SWP pulls to ground and the inductor current rises. Once the inductor current reaches the DC current limit ( $I_{LIM}$ ) of 150 mA (typ) the internal control logic can either turn off N-MOS1 or P-MOS1 to service the requesting output. Depending on the required output power, the converter starts another cycle or enters a pulse-skipping modulation scheme to increase efficiency under light loads. The current into the SWN pin measures the inductor current. The TPS6512x controls the inductor current to regulate BOOT,  $V_{GH}$ , and  $V_{GI}$  output voltages.

To achieve low ripple voltage and high accuracy, the main output ( $V_{MAIN}$ ) is post-regulated by an integrated LDO. This LDO regulator regulates energy from the BOOT output down to 5.3 V (max). To achieve the highest efficiency, the BOOT voltage is regulated to minimize the dropout voltage across the LDO to approximately  $V_{MAIN}$  + 0.5 V.

In addition, the VMAIN, VGH, VGL outputs are monitored for fault conditions that last longer than the fault-timer period of 100 µs (typ). The device goes into a latched shutdown state in case of a fault condition.

#### **Soft Start**

The TPS6512x has an internal soft-start circuit that limits the inrush current during startup. This prevents possible voltage drops of the input voltage in case the battery or a high impedance power source is connected to the input of the device.

The device powers up by precharging the BOOT output capacitor to VIN. During the precharge phase, the current through the rectifying switch N-MOS2 is limited. This also limits the output current under short-circuit conditions on the BOOT output. To ensure proper startup of the device, the BOOT output must be left unloaded during the precharge phase.

After the precharge phase, the converter operates with an I<sub>START-UP</sub> current limit of 65 mA (typ), then increases gradually to the full current limit of 150 mA (typ).

#### **Undervoltage Lockout**

To ensure that the input voltage is high enough for reliable operation, the TPS6512x includes an under-voltage lockout (UVLO) circuit. The UVLO threshold at the VIN pin is 2.15 V (typ) falling and 2.25 V (typ) rising. The 100 mV (typ) hysteresis prevents supply transients from causing restarts.

Once the input voltage exceeds the UVLO rising threshold, the controller can enable the reference voltage and precharges BOOT. When the input voltage falls below the UVLO falling threshold, the controller turns off the reference and all the regulator outputs, and pulls GATE high with an internal 100 k $\Omega$  resistor to turn off P1 (Figure 18).

#### **DETAILED DESCRIPTION (continued)**

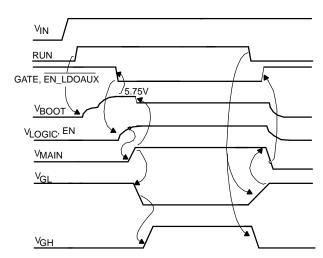

#### Enable and Power Sequencing (TPS65120/1/2/3)

To correctly power up most TFT panels, the gate-drive supplies must be sequenced such that the negative supply  $(V_{GL})$  powers up before the positive supply  $(V_{GH})$ . The TPS65120/1/2/3 controls this sequence through an enable pin.

Once RUN is high, the TPS65120/1/2/3 turns on the external P-channel MOSFET P1 (see Figure 18) by pulling GATE low. GATE is pulled down with a 100 k $\Omega$  resistor. The DC/DC converter then starts, enabling the BOOT output.

Pulling the enable pin (EN) high enables the MAIN output. When the output voltage  $V_{MAIN}$  has reached 90% of its nominal value, the negative output enables.  $V_{GH}$  is delayed until the negative voltage has reached 90% of its nominal value.

Pulling the RUN pin low shuts down the device. Power-down sequencing starts by switching off V<sub>GH</sub> and V<sub>GL</sub>.

The  $V_{GH}$  output capacitor is actively discharged by an internal resistor while  $V_{GL}$  is only discharged by its feedback voltage divider. The required time to discharge the output capacitor at  $V_{GL}$  output depends on the load current. Once  $V_{FBL}$  has reached 1.2 V (typ) the main output is turned off followed by the output voltage  $V_{LOGIC}$ . This sequence is shown in Figure 19.

When no power sequencing is required on the digital supply voltage (V<sub>LOGIC</sub>), tie EN and RUN signals together and GATE can be connected to a logic-high level to disable the power-down sequencer. Each output turns off depending upon load current and output capacitance.

Figure 18. Power Sequencing on Digital Supply Voltage,  $V_{\text{LOGIC}}$

Figure 19. TPS65120/1/2/3 Power Sequence

#### **DETAILED DESCRIPTION (continued)**

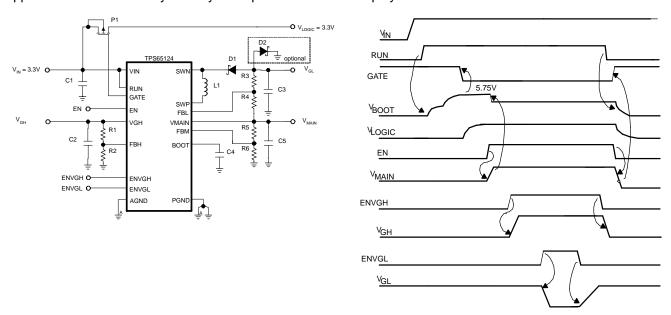

#### **Enable and Power Sequencing (TPS65124)**

The TPS65124 controls the power sequencing of  $V_{LOGIC}$ ,  $V_{MAIN}$ ,  $V_{GH}$  and  $V_{GL}$  with four separate enable pins. These pins must be terminated and not be left floating to prevent instability.

Once RUN is pulled high and the input voltage on VIN exceeds the rising input UVLO threshold, the reference is turned on and the external P-channel MOSFET P1 (see Figure 20) is switched on by pulling GATE low. The GATE is pulled down with a 100  $k\Omega$  resistor. The DC/DC converter then starts up, enabling the BOOT output.

Pulling enable pin high (EN) powers on the MAIN output. This power sequencing must occur before the gate voltages are enabled. Conversely  $V_{GL}$  and  $V_{GH}$  output voltages must be turned off by pulling ENVGL and ENVGH inputs to ground before the MAIN output is switch off.

To clamp the  $V_{GL}$  output near zero when the MAIN output is still on, an external diode (D2) can be used. In some applications this diode may already be implemented in the display.

Figure 20. Power Sequencing on Digital Supply Voltage,  $V_{\text{LOGIC}}$

Figure 21. TPS65124 Programmable Power Sequence

#### **Fault Protection**

All TPS6512x outputs are protected against a short circuit to ground. During steady-state operation, if the output  $V_{MAIN}$ ,  $V_{GH}$  or  $V_{GL}$  falls below its fault detection threshold the device simultaneously turns off all three outputs. Once  $V_{MAIN}$  comes down to 700 mV typ, the GATE output is pulled to  $V_{IN}$ , the auxiliary LDO (TPS65120/1/2) is disabled and the device enters a shutdown state.

The auxiliary LDO present in TPS65120/1/2 has an integrated current foldback circuit for reliable short-circuit protection.

The device can be enabled again by toggling the enable pins (RUN, EN) below 0.4 V or by cycling the input voltage below the UVLO falling threshold (2.15 V typ).

#### **APPLICATION INFORMATION**

#### **OUTPUT POWER CAPABILITY**

The first step in the design procedure is to calculate the maximum output current for each output under certain input and output voltage conditions. The TPS6512x uses time-multiplex operation to share the inductive storage element between BOOT, VGH and VGL outputs. To avoid complex calculations it is recommended to use the specified output-power data from the electrical characteristics table to determine the maximum output-power capability.

The following example shows how to proceed for given requirements:

- Input Voltage = 3.0 V

- MAIN Output = 5.0 V @ 10 mA

- VGH output = 12 V @ 500 μA

- VGL output = -12 V @ 300 μA

- 1. Calculate Maximum Output Power on VGH Output

$$P_{GH} = V_{GH} \times I_{GH}$$

2. Calculate Maximum Output Power on VGL Output

$$P_{GL} = |V_{GL}| \times I_{GL}$$

3. Calculate Maximum Output Power on BOOT Output

$$P_{BOOT} = P_{MAIN} \times \eta_{LDO\_MAIN} \approx \frac{{V_{MAIN}}^2}{{V_{MAIN}} + 0.5} \times I_{MAIN} \quad \text{ for } V_{IN} < V_{MAIN} + 0.5$$

$$P_{BOOT} = P_{MAIN} \times \eta_{LDO\_MAIN} \approx \frac{{V_{MAIN}}^2}{V_{IN}} \times I_{MAIN} \quad \text{ for } V_{IN} > V_{MAIN}$$

4. Maximum Output Power Verification

The electrical characteristics table states that for  $V_{IN} > 3.0 \text{ V}$ , the maximum power on VGH and VGL outputs must be lower than 35 mW each. Furthermore, the total output power ( $P_{BOOT} + P_{GH} + P_{GL}$ ) must be lower than 150 mW.

In our design example,  $P_{GH} = 6$  mW,  $P_{GL} = 3.6$  mW, and  $P_{BOOT} = 55$  mW. Since these numbers are well below the specified values, we can conclude that TPS6512x can reasonably power such a display.

#### SETTING THE OUTPUT VOLTAGE

The output voltages are defined as shown in Figure 22.

$$V_{MAIN} = V_{FBM} \times \frac{R5 + R6}{R6}$$

with an internal reference voltage  $V_{FBM}$  typical = 1.213V.

$$V_{GH} = V_{FBH} \times \frac{R1 + R2}{R2}$$

with an internal reference voltage  $V_{FBH}$  typical = 1.213V.

$$|V_{GL}| = V_{MAIN} \times \frac{R3}{R4}$$

To minimize the operating quiescent current, set R2, R4 and R6 in the range 100 k $\Omega$  to 300 k $\Omega$ . Great care should be taken to route the FBx lines away from noise sources such as the inductor or the SWN and SWP lines.

A feed-forward capacitor across the upper feedback resistor (R1, R3) on VGH and VGL outputs can be used to provide more overdrive for the error comparator. This feed-forward capacitor helps to reduce the output ripple voltage. A good starting value is 10 pF.

#### **APPLICATION INFORMATION (continued)**

The larger the feed-forward capacitor the worse the load regulation of the device. Therefore, when concern for load regulation is paramount, select a capacitor value as small as possible. Another possibility to further reduce ripple voltage on VGH and VGL outputs is to increase output-capacitor values (C2, C3).

Figure 22. Typical Application

#### INDUCTOR SELECTION

Since the control scheme of the TPS6512x device is inherently stable, the inductor value does not affect the stability of the converter. To operate the TPS6512x properly at full performance, choose inductors in the range  $8.2 \, \mu H$  to  $10 \, \mu H$ .

The selection of the inductor is primarily based on the required output power. The variable peak current PWM control scheme used in TPS6512x automatically adapts the peak inductor current (between 65mA typ. and 150mA typ.) depending on output power and input voltage.

At moderate loads, the converter typically operates with a peak inductor current in the range of 65mA to 100mA, allowing the use of inductors in the 0603 case size. In order not to saturate the inductor when operating at a higher output power, select an inductor with a higher saturation-current rating.

The inductor series in Table 1 from various suppliers have been used with the TPS6512x converter.

**Table 1. List of Inductors**

| MANUFACTURER | SERIES     | DIMENSIONS                                      |

|--------------|------------|-------------------------------------------------|

|              | LQ LB1608  | $1.6 \times 0.8 \times 0.8 = 1.02 \text{ mm}^3$ |

| TAIYO YUDEN  | LQ CB2012  | 2.0 x 1.2 x 1.2 = 2.88 mm <sup>3</sup>          |

|              | LQ CBL2012 | 2.0 x 1.2 x 1.0 = 2.40 mm <sup>3</sup>          |

| TDK          | GLF1608    | 1.6 x 0.8 x 0.8 = 1.02 mm <sup>3</sup>          |

| IDK          | GLF2012    | 2.0 x 1.2 x 1.2 = 2.88 mm <sup>3</sup>          |

#### **DIODE SELECTION**

To achieve high efficiency, use a Schottky diode. The voltage rating must be higher than the input voltage plus the absolute value of the negative output. The current rating of the diode must meet the converter peak inductor-current rating when servicing the VGL output. The main parameter affecting the efficiency of the converter is the forward voltage and the reverse leakage current of the diode, both should be as low as possible.

The following diodes from different suppliers listed in Table 2 have been used with the TPS6512x converter.

| MANUFACTURER | REFERENCE | REVERSE VOLTAGE |

|--------------|-----------|-----------------|

| ROHM         | RB521G-30 | 30 V            |

| VISHAY       | BAT54-HT3 | 30 V            |

| ZETEX        | ZUMD54    | 30 V            |

Table 2. List of Diodes

#### **CAPACITOR SELECTION**

The TPS65120 converter requires six capacitors. The input capacitor is primarily a function of the board layout. In designs with long traces, for good input filtering, we recommend a ceramic input capacitor (X5R/X7R type) of at least 1  $\mu$ F placed as close as possible to the converter.

To operate properly, the TPS6512x requires a bootstrap capacitor of 1 µF (or larger) on the BOOT output. Additionally the minimum BOOT capacitance must be larger than two times the capacitor value connected to the MAIN and AUXILIARY LDO outputs (in case LDO AUX is connected to the BOOT output).

The TPS6512x peak-current control scheme is inherently stable. The filtering capacitors on VGH and VGL outputs are basically determined as a function of the required current and permissible ripple voltage. For small form-factor TFT-LCD applications, typical values in the range of 100 nF to 1  $\mu$ F are usually required. A good starting point is 220 nF. For high output power on VGH and VGL outputs, the capacitance may need to approach 2  $\mu$ F.

For stable operation, TPS6512x requires a 220-nF ceramic capacitor on the MAIN and AUXILIARY LDO outputs. Larger capacitor values can be used to achieve lower output-voltage noise without sacrificing stability.

In general, ceramic X5R types are strongly recommended for their low ESR and ESL and capacitance-versus-bias-voltage stability. Be certain that the capacitors used are rated for the maximum voltage with adequate safety margin.

#### LAYOUT CONSIDERATIONS

As for all switching power supplies, the layout is an important step in the design. If the layout is not carefully done, the regulator could become unstable, displaying double or missing pulses as well as EMI problems. Therefore, use wide, short traces for the main current paths. Route these traces first.

Place the input capacitor as close as possible to the IC pins as well as the inductor and output capacitors. Place the inductor and diode as close as possible to the switch pins to minimize noise coupling into other circuits.

Use a common ground node for power ground and a different one for control ground (AGND) to minimize the effects of ground noise. Connect these ground nodes together (star point) at any place close to one of the ground pins of the IC and make sure that small-signal components returning to the AGND pin do not share the switching-current paths.

Feedback pins and divider networks are high-impedance nodes and should therefore be routed away from the inductor and shielded with a ground plane or trace to minimize noise coupling into the control loop.

#### **APPLICATION EXAMPLES**

Figure 23. Complete TFT-LCD Power Supply from 1 cell Li-lon

Figure 24.  $V_{GL} \rightarrow V_{MAIN}$  Power Down-Sequencing Threshold Shifting

Figure 25. Additional Negative Gate Driver Voltage

Figure 26. Fully Programmable Sequencing Featuring Very Low Gate Ripple Voltage

Figure 27. Dual Output Tracking Regulator with High Accuracy Reference Voltage

Figure 28. Boosting Main Output Current, I<sub>MAIN</sub> > 25mA

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB), the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to a ground plane or special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No—Lead (QFN) package and its advantages, refer to Application Report, Quad Flatpack No—Lead Logic Packages, Texas Instruments Literature No. SCBA017. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Bottom View

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

www.ti.com

11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                 |                       |      | (4)                           | (5)                        |              |                  |

| TPS65120RGTR          | Active | Production    | VQFN (RGT)   16 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | ВКА              |

| TPS65120RGTR.A        | Active | Production    | VQFN (RGT)   16 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | BKA              |

| TPS65120RGTT          | Active | Production    | VQFN (RGT)   16 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | BKA              |

| TPS65120RGTT.A        | Active | Production    | VQFN (RGT)   16 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | BKA              |

| TPS65121RGTR          | Active | Production    | VQFN (RGT)   16 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | BKB              |

| TPS65121RGTR.A        | Active | Production    | VQFN (RGT)   16 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | BKB              |

| TPS65123RGTR          | Active | Production    | VQFN (RGT)   16 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | BKC              |

| TPS65123RGTR.A        | Active | Production    | VQFN (RGT)   16 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | BKC              |

| TPS65123RGTT          | Active | Production    | VQFN (RGT)   16 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | BKC              |

| TPS65123RGTT.A        | Active | Production    | VQFN (RGT)   16 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | BKC              |

| TPS65124RGTR          | Active | Production    | VQFN (RGT)   16 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | BKD              |

| TPS65124RGTR.A        | Active | Production    | VQFN (RGT)   16 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | BKD              |

| TPS65124RGTT          | Active | Production    | VQFN (RGT)   16 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | BKD              |

| TPS65124RGTT.A        | Active | Production    | VQFN (RGT)   16 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | BKD              |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 11-Nov-2025

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com 12-Aug-2025

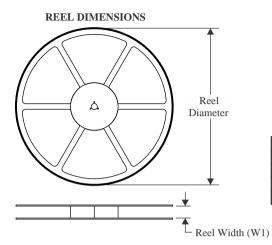

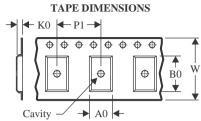

#### TAPE AND REEL INFORMATION

Texas Instruments

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

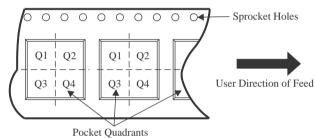

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS65120RGTT | VQFN            | RGT                | 16 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS65121RGTR | VQFN            | RGT                | 16 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS65123RGTR | VQFN            | RGT                | 16 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS65123RGTT | VQFN            | RGT                | 16 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS65124RGTR | VQFN            | RGT                | 16 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS65124RGTT | VQFN            | RGT                | 16 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

www.ti.com 12-Aug-2025

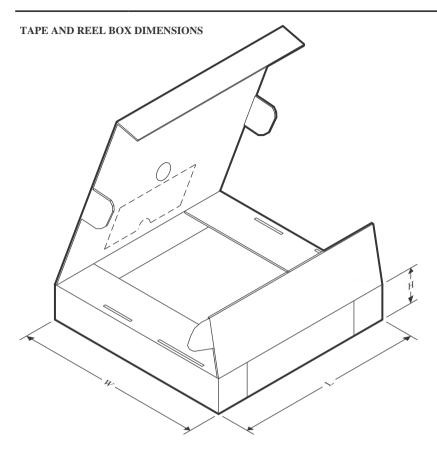

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS65120RGTT | VQFN         | RGT             | 16   | 250  | 210.0       | 185.0      | 35.0        |

| TPS65121RGTR | VQFN         | RGT             | 16   | 3000 | 350.0       | 350.0      | 43.0        |

| TPS65123RGTR | VQFN         | RGT             | 16   | 3000 | 350.0       | 350.0      | 43.0        |

| TPS65123RGTT | VQFN         | RGT             | 16   | 250  | 210.0       | 185.0      | 35.0        |

| TPS65124RGTR | VQFN         | RGT             | 16   | 3000 | 350.0       | 350.0      | 43.0        |

| TPS65124RGTT | VQFN         | RGT             | 16   | 250  | 210.0       | 185.0      | 35.0        |

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

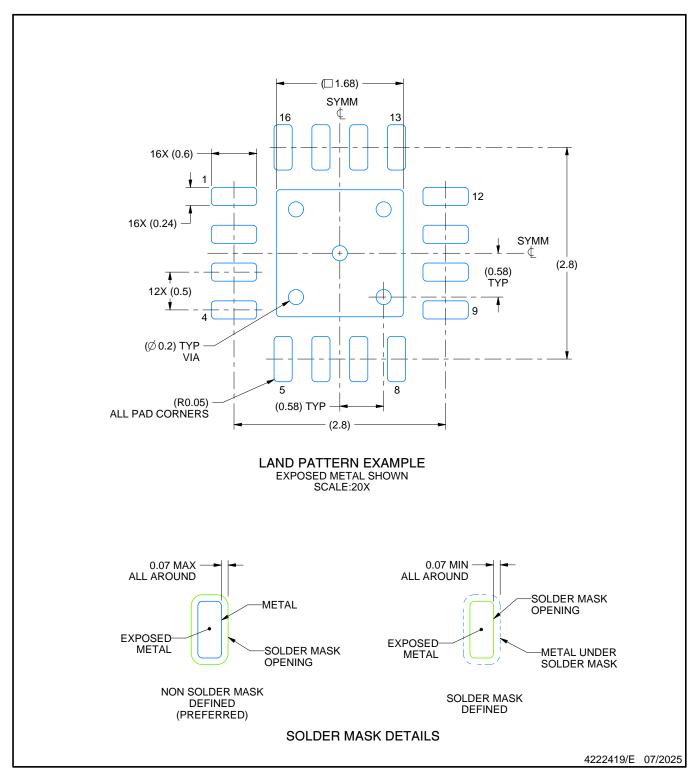

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

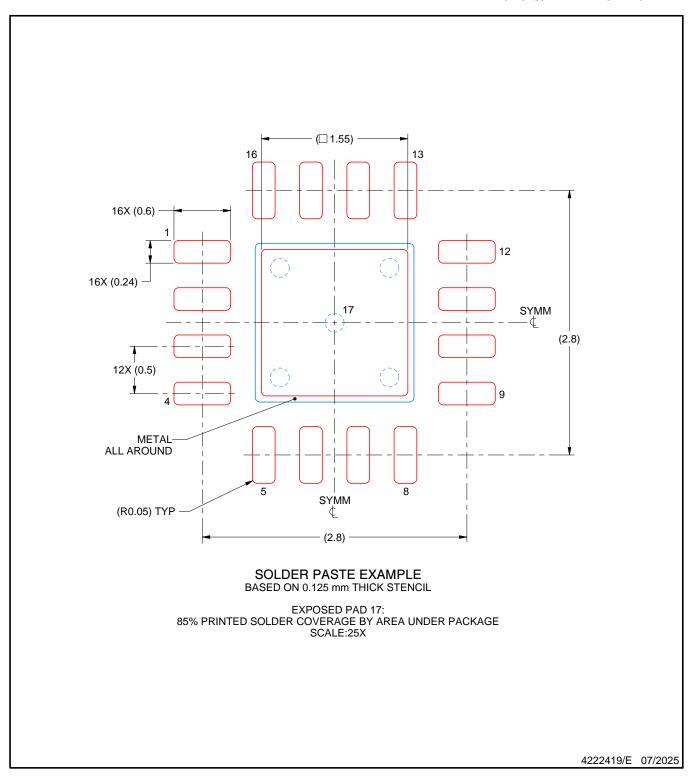

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025