**TPS65154**

ZHCSF63A - SEPTEMBER 2013 - REVISED JUNE 2016

# TPS65154 集成 WLED 驱动器的 LCD 偏置 IC

### 器件概述

#### 特性 1.1

- 2.0V 至 5.5V 输入电压范围

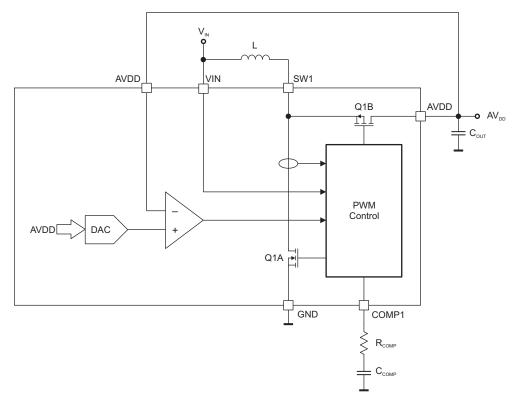

- 同步升压转换器 (AVDD)

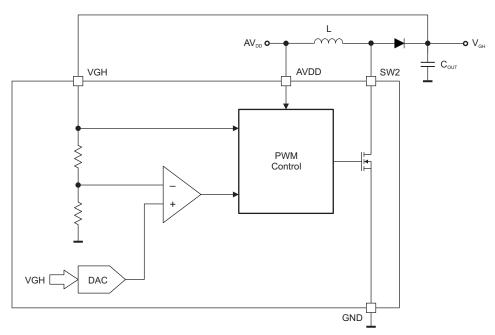

- 非同步升压转换器 (V<sub>GH</sub>)

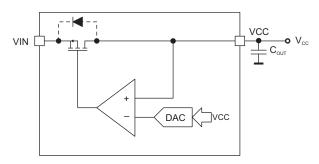

- 低压降线性稳压器 (Vcc)

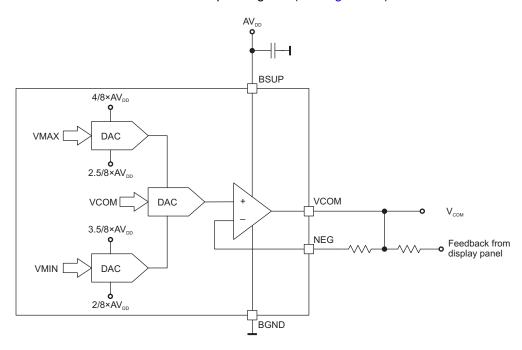

- 集成缓冲器放大器的可编程 V<sub>COM</sub> 校准器

- 6 通道 WLED 驱动器,支持直接调光和相移调光模

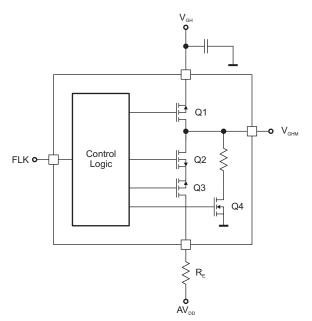

- 栅极电压整形

- 应用范围 1.2

- 笔记本电脑

- 面板复位信号 (XAO)

- T-CON 复位信号 (RST)

- 具有写保护的片上 EEPROM

- I<sup>2</sup>C 接口

- 热关断

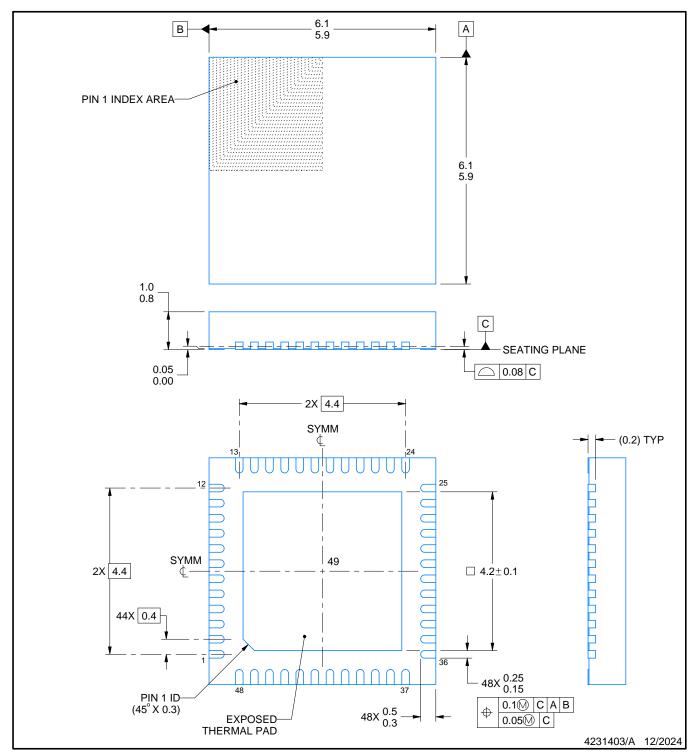

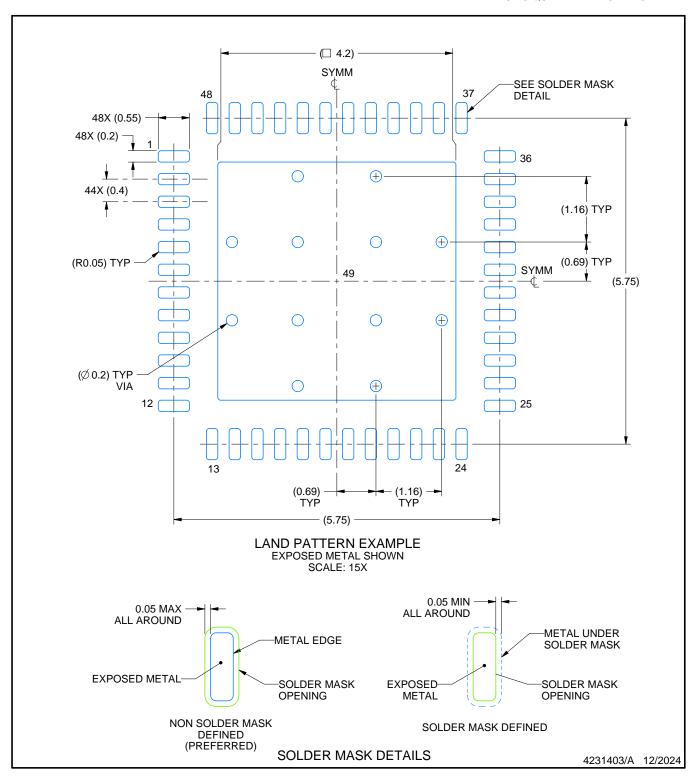

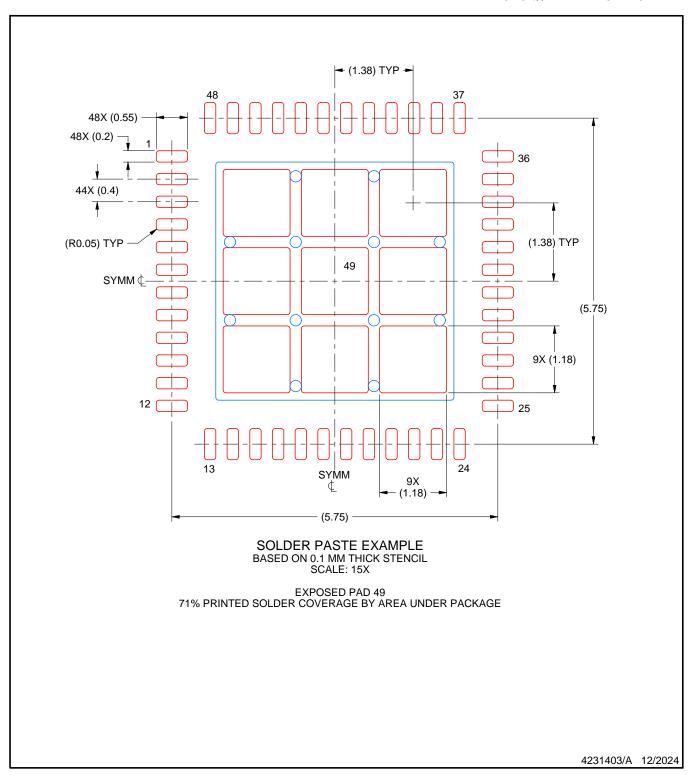

- 48 引脚、6mm×6mm、0.4mm 间距 VQFN

平板电脑

#### 1.3 说明

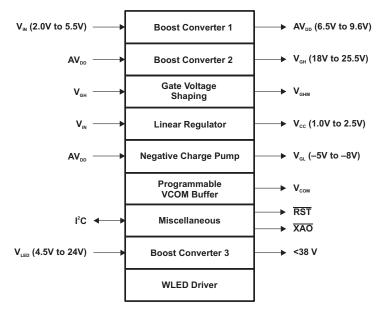

TPS65154 是一款紧凑型 LCD 偏置解决方案,此解决方案主要用于笔记本电脑和平板电脑。此器件配有两 个能够为 LCD 面板的源极驱动器和栅极驱动器供电的升压转换器、一个提供系统逻辑电压的线性稳压器、 一个带有高速放大器的可编程 V<sub>COM</sub> 以及一个 6 通道 WLED 驱动器,并且具备栅极电压整形功能。

#### 器件信息(1)

|          | BRITIES.  |                 |

|----------|-----------|-----------------|

| 器件型号     | 封装        | 封装尺寸 (标称值)      |

| TPS65154 | VQFN (48) | 6.00mm × 6.00mm |

(1) 要了解所有可用封装,请见数据手册末尾的可订购产品附录。

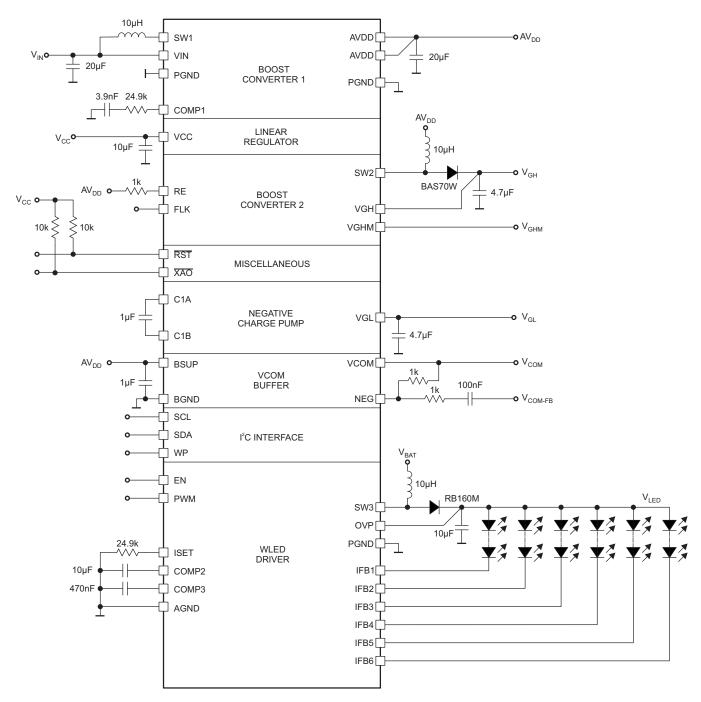

#### 1.4 简化系统图

Copyright © 2016, Texas Instruments Incorporated

| _نــ | ,,,,, |

|------|-------|

| ᇄ    | 7/2   |

| rı   | 70    |

| 1 | 器件    | 概述                               | 1          | 5.5  | Programming                 | 26 |

|---|-------|----------------------------------|------------|------|-----------------------------|----|

|   | 1.1   | 特性                               | 1          | 5.6  | Register Map                | 38 |

|   | 1.2   | 应用范围                             | 1 6        | Appl | lication and Implementation | 63 |

|   | 1.3   | 说明                               | <u>1</u>   | 6.1  | Application Information     | 63 |

|   | 1.4   | 简化系统图                            | 1          | 6.2  | Typical Application         | 63 |

| 2 | 修订    | 历史记录                             | _<br>2     | Pow  | er Supply Recommendations   | 75 |

| 3 | Pin ( | Configuration and Functions      | <u>3</u> 8 | Layo | out                         | 76 |

| 4 | Spec  | cifications                      | <u>5</u>   | 8.1  | Layout Guidelines           | 76 |

|   | 4.1   | Absolute Maximum Ratings         | <u>5</u>   | 8.2  | Layout Example              | 76 |

|   | 4.2   | ESD Ratings                      | <u>5</u> 9 | 器件   | 和文档支持                       | 78 |

|   | 4.3   | Recommended Operating Conditions | <u>5</u>   | 9.1  | 器件支持                        | 78 |

|   | 4.4   | Thermal Information              | <u>6</u>   | 9.2  | 接收文档更新通知                    | 78 |

|   | 4.5   | Electrical Characteristics       | 7          | 9.3  | 社区资源                        | 78 |

|   | 4.6   | Timing Requirements              | 9          | 9.4  | 商标                          | 78 |

| 5 | Deta  | illed Description 1              | 2          | 9.5  | 静电放电警告                      | 78 |

|   | 5.1   | Overview 1                       | 2          | 9.6  | Glossary                    | 78 |

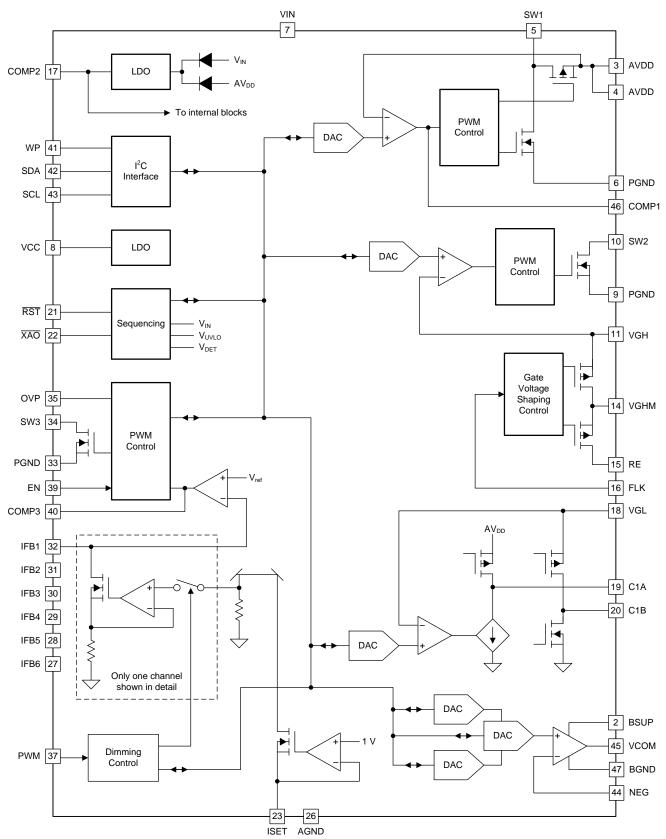

|   | 5.2   | Functional Block Diagram 1       | 2 10       | 机械   | 、封装和可订购信息                   | 79 |

|   | 5.3   | Feature Description 1            | 4          | 10.1 | 封装信息                        | 79 |

|   | 5.4   | Device Functional Modes          | 22         |      |                             |    |

|   |       |                                  |            |      |                             |    |

## 2 修订历史记录

## Changes from Original (September 2013) to Revision A

Page

# 3 Pin Configuration and Functions

Figure 3-1. RSL Package, 48-Pin VQFN (Top View)

#### **Pin Functions**

| PIN   | 1   |      | DECODURTION                                                                             |

|-------|-----|------|-----------------------------------------------------------------------------------------|

| NAME  | NO. | TYPE | DESCRIPTION                                                                             |

| NC    | 1   | N/A  | No internal connection.                                                                 |

| BSUP  | 2   | Р    | Positive supply for the VCOM buffer.                                                    |

| AVDD  | 3   | Р    | Boost converter 1 output voltage sense.                                                 |

| AVDD  | 4   | Р    | Boost converter 1 rectifier output.                                                     |

| SW1   | 5   | Р    | Boost converter 1 switch pin.                                                           |

| PGND  | 6   | Р    | Ground.                                                                                 |

| VIN   | 7   | Р    | Positive supply.                                                                        |

| VCC   | 8   | Р    | Linear regulator output.                                                                |

| PGND  | 9   | Р    | Ground.                                                                                 |

| SW2   | 10  | Р    | Boost converter 2 switch pin.                                                           |

| VGH   | 11  | Р    | V <sub>GH</sub> regulation point and positive supply for gate voltage shaping function. |

| NC    | 12  | N/A  | No internal connection.                                                                 |

| NC    | 13  | N/A  | No internal connection.                                                                 |

| VGHM  | 14  | Р    | Gate voltage shaping output.                                                            |

| RE    | 15  | I/O  | Gate votlage shaping discharge resistor connection.                                     |

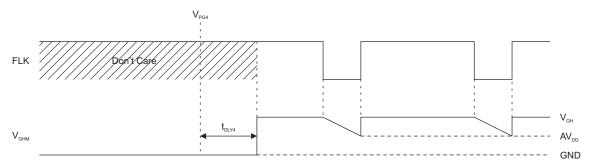

| FLK   | 16  | I/O  | Gate votlage shaping flicker clock input.                                               |

| COMP2 | 17  | I/O  | Internal linear regulator compensation network connection.                              |

| VGL   | 18  | Р    | Negative charge pump output and V <sub>GL</sub> regulation point.                       |

| C1A   | 19  | Р    | Negative charge pump flying capacitor connection.                                       |

| C1B   | 20  | Р    | Negative charge pump flying ccapacitor connection.                                      |

# Pin Functions (continued)

| PIN   | ı   |      |                                                              |

|-------|-----|------|--------------------------------------------------------------|

| NAME  | NO. | TYPE | DESCRIPTION                                                  |

| RST   | 21  | I/O  | Reset generator output.                                      |

| XAO   | 22  | I/O  | Panel discharge generator output.                            |

| ISET  | 23  | I/O  | WLED driver current-setting resistor connection.             |

| NC    | 24  | N/A  | No internal connection.                                      |

| NC    | 25  | N/A  | No internal connection.                                      |

| AGND  | 26  | Р    | Ground.                                                      |

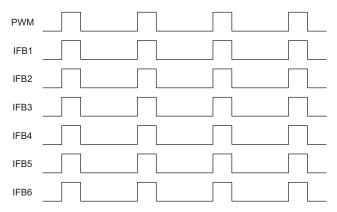

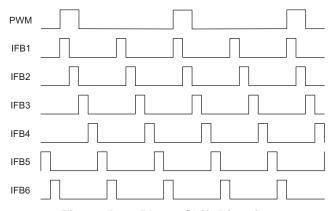

| IFB6  | 27  | I/O  | WLED driver channel 6 output.                                |

| IFB5  | 28  | I/O  | WLED driver channel 5 output.                                |

| IFB4  | 29  | I/O  | WLED driver channel 4 output.                                |

| IFB3  | 30  | I/O  | WLED driver channel 3 output.                                |

| IFB2  | 31  | I/O  | WLED driver channel 2 output.                                |

| IFB1  | 32  | I/O  | WLED driver channel 1 output.                                |

| PGND  | 33  | Р    | Ground.                                                      |

| SW3   | 34  | Р    | WLED driver boost converter switch pin.                      |

| OVP   | 35  | I/O  | WLED driver boost converter output voltage sensing pin.      |

| NC    | 36  | N/A  | No internal connection.                                      |

| NC    | 37  | N/A  | No internal connection.                                      |

| PWM   | 38  | I/O  | WLED driver PWM input.                                       |

| EN    | 39  | I/O  | WLED driver enable input.                                    |

| COMP3 | 40  | I/O  | WLED driver boost converter compensation network connection. |

| WP    | 41  | I/O  | EEPROM write protect input.                                  |

| SDA   | 42  | I/O  | I <sup>2</sup> C data.                                       |

| SCL   | 43  | I/O  | I <sup>2</sup> C clock.                                      |

| NEG   | 44  | I/O  | VCOM buffer inverting input.                                 |

| VCOM  | 45  | I/O  | VCOM buffer output.                                          |

| COMP1 | 46  | I/O  | Boost converter 1 compensation network connection.           |

| BGND  | 47  | Р    | Ground.                                                      |

| NC    | 48  | N/A  | No internal connection.                                      |

| GND   | Pad | Р    | Ground.                                                      |

### 4 Specifications

## 4.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|               |                                                        | MIN  | MAX | UNIT |

|---------------|--------------------------------------------------------|------|-----|------|

|               | VIN, VCC, SCL, SDA, FLK, WP, XAO, COMP1                | -0.3 | 7   | V    |

|               | AVDD, SW1, VCOM, NEG, BSUP, RST                        | -0.3 | 12  | V    |

|               | EN, PWM                                                | -0.3 | 20  | V    |

| Din voltogo   | COMP2, COMP3, ISET                                     | -0.3 | 3.6 | V    |

| Pin voltage   | C1A, C1B                                               | -10  | 12  | V    |

|               | VGL                                                    | -10  | 0.3 | V    |

|               | SW3, OVP                                               | -0.3 | 40  | V    |

|               | IFB1, IFB2, IFB3, IFB4, IFB5, IFB6, VGH, VGHM, RE, SW2 | -0.3 | 30  | V    |

| Pin current   | SW2                                                    |      | TBD | Α    |

| Ambient temp  | erature, T <sub>A</sub>                                | -40  | 85  | °C   |

| Junction temp | erature, T <sub>J</sub>                                | -40  | 150 | °C   |

| Storage tempe | erature, T <sub>STG</sub>                              | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 4.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | 2000  |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | 700   | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 4.3 Recommended Operating Conditions

|                       |                                     |                           | MIN  | NOM | MAX  | UNIT |

|-----------------------|-------------------------------------|---------------------------|------|-----|------|------|

| \/                    | lanut voltage range                 | Normal operation          | 2.0  |     | 5.5  | V    |

| V <sub>IN</sub>       | Input voltage range                 | EEPROM programming        | 2.6  |     | 5.5  | V    |

| dV <sub>IN</sub> /dt  | V <sub>IN</sub> rise time           |                           | 0.45 |     | 11   | ms   |

| $V_{BSUP}$            | Input voltage range                 |                           | 6.5  |     | 9.6  | V    |

| $V_{BAT}$             | Input voltage range                 |                           | 4.5  |     | 24   | V    |

| dV <sub>BAT</sub> /dt | V <sub>BAT</sub> rise time          |                           | 0.45 |     | 11   | ms   |

| LINEAR R              | EGULATOR (V <sub>CC</sub> )         |                           |      |     |      |      |

| $V_{CC}$              | Output voltage                      |                           | 1.0  |     | 2.5  | V    |

| I <sub>ICC</sub>      | Output current                      |                           |      |     | 300  | mA   |

| C <sub>OUT</sub>      | Output capacitance                  |                           | 4.7  | 10  | 22   | μF   |

| BOOST C               | ONVERTER 1 (AV <sub>DD</sub> )      |                           |      |     | ,    |      |

| $AV_{DD}$             | Boost converter 1 output voltage ra | ange                      | 6.5  |     | 9.6  | V    |

| $IAV_DD$              | Boost converter 1 output current at | : V <sub>IN</sub> = 3.7 V |      |     | 400  | mA   |

| L                     | Inductance                          |                           | 4.7  | 10  | 15   | μΗ   |

| C <sub>OUT</sub>      | Boost converter 1 output capacitar  | ice                       | 4.7  | 10  | 22   | μF   |

|                       | ONVERTER 2 (V <sub>GH</sub> )       |                           |      |     | •    |      |

| $AV_{DD}$             | Input voltage range                 |                           | 6.5  |     | 9.6  | V    |

| $V_{GH}$              | Output voltage range                |                           | 18   |     | 25.5 | V    |

| $I_{GH}$              | Output current                      | <u> </u>                  |      |     | 25   | mA   |

<sup>2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **Recommended Operating Conditions (continued)**

|                  |                                        | MIN            | NOM | MAX | UNIT |

|------------------|----------------------------------------|----------------|-----|-----|------|

| L                | Inductance                             | 4.7            | 10  | 15  | μΗ   |

| C <sub>OUT</sub> | Output capacitance                     | 1              | 4.7 | 10  | μF   |

| NEGATIV          | E CHARGE PUMP (V <sub>GL</sub> )       |                |     |     |      |

| $V_{GL}$         | Output voltage                         | <del>-</del> 5 |     | 8–  | ٧    |

| $I_{GL}$         | Output current                         |                |     | 25  | mΑ   |

| $C_{FLY}$        | Flying capacitance                     |                | 0.5 |     | μF   |

| C <sub>OUT</sub> | Output capacitance                     | 0.5            |     | 5   | μF   |

| BOOST C          | ONVERTER 3 (WLED)                      |                |     |     |      |

| $V_{OUT}$        | Output voltage                         |                |     | 38  | V    |

| I <sub>OUT</sub> | Output current                         |                |     | 250 | mΑ   |

| L                | Inductance                             | 4.7            | 10  | 15  | μΗ   |

| C <sub>OUT</sub> | Output capacitance                     | 2.2            | 4.7 | 10  | μF   |

| INTERNA          | L REGULATOR                            |                |     |     |      |

| C <sub>OUT</sub> | Capacitance connected to the TCOMP pin | 1              |     |     | μF   |

## 4.4 Thermal Information

|                      |                                              | TPS65154   |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RSL (VQFN) | UNIT |

|                      |                                              | 48 PIN     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 29.8       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 15.8       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 5.2        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 5.1        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 0.8        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics application report.

# 4.5 Electrical Characteristics

|                                                                 | PARAMETER                                                                                                                                  | TEST CONDITIONS                                                                                       | MIN  | TYP  | MAX  | UNIT     |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|------|----------|

| POWER                                                           | SUPPLY                                                                                                                                     |                                                                                                       |      |      |      |          |

| I <sub>IN</sub>                                                 | Supply current into VIN pin                                                                                                                | Converters not switching                                                                              |      | 0.1  | 1    | mA       |

| I <sub>AVDD</sub>                                               | Supply current into AVDD pins                                                                                                              | Pins 2 and 3 connected together                                                                       |      | 0.75 | 2.5  | mA       |

| I <sub>BSUP</sub>                                               | Supply current into BSUP pin                                                                                                               |                                                                                                       |      | 2.5  | 5    | mA       |

| I <sub>GH</sub>                                                 | Supply current into VGH pin                                                                                                                | No load on VGHM                                                                                       |      | 0.1  | 1    | mA       |

|                                                                 | OLTAGE LOCKOUT                                                                                                                             |                                                                                                       | l    |      | -    |          |

|                                                                 |                                                                                                                                            | V <sub>IN</sub> falling                                                                               | 1.75 |      |      |          |

| $V_{UVLO}$                                                      | Undervoltage lockout threshold                                                                                                             | V <sub>IN</sub> rising                                                                                |      |      | 2.2  | V        |

| 0120                                                            | Hysteresis                                                                                                                                 |                                                                                                       | 90   |      |      | mV       |

| LINEAR                                                          | REGULATOR (V <sub>CC</sub> )                                                                                                               |                                                                                                       |      |      |      |          |

|                                                                 | Linear regulator output voltage range                                                                                                      |                                                                                                       | 1.0  |      | 2.5  | V        |

| $V_{CC}$                                                        | Tolerance                                                                                                                                  | I <sub>CC</sub> = 10 mA                                                                               | -3%  |      | +3%  |          |

| V <sub>UVP</sub>                                                | Undervoltage protection threshold                                                                                                          | V <sub>CC</sub> falling                                                                               | 60%  | 70%  | 75%  |          |

| V <sub>SCP</sub>                                                | Short circuit protection threshold                                                                                                         | V <sub>CC</sub> falling                                                                               | 25%  | 30%  | 40%  |          |

| - 307                                                           | C. or on our protoction throughout                                                                                                         | $T_{\rm J} = 25^{\circ}\text{C to } 125^{\circ}\text{C}$                                              | 300  | 5570 | 1370 |          |

| $I_{LIM}$                                                       | Current limit                                                                                                                              | $V_{CC} = 5\%$ below value at 10 mA. $T_{J} = 23 \text{ C to } 123 \text{ C}$ $T_{J} = -40 \text{ C}$ | 250  |      |      | mA       |

| r <sub>nove</sub>                                               | Active pull-down resistance                                                                                                                | 1J = -+0 O                                                                                            | 10   | 21   | 35   | Ω        |

| r <sub>DS(ON)</sub>                                             | CONVERTER 1 (AV <sub>DD</sub> )                                                                                                            |                                                                                                       | 10   | 21   | 33   | 52       |

| B0031 (                                                         | Output voltage range                                                                                                                       |                                                                                                       | 6.5  |      | 9.6  | V        |

| $AV_{DD}$                                                       | Tolerance                                                                                                                                  |                                                                                                       |      |      |      | V        |

| \ <u>'</u>                                                      |                                                                                                                                            |                                                                                                       | -2%  | 700/ | +2%  |          |

| V <sub>UVP</sub>                                                | Undervoltage protection threshold                                                                                                          |                                                                                                       | 60%  | 70%  | 75%  |          |

| V <sub>SCP</sub>                                                | Short-circuit protection threshold                                                                                                         |                                                                                                       | 25%  | 30%  | 35%  |          |

| r <sub>DS(ON)</sub>                                             | Switch ON resistance                                                                                                                       | I <sub>SW</sub> = 1 A                                                                                 |      | 0.1  | 0.25 | Ω        |

| I <sub>LIM</sub>                                                | Switch current limit                                                                                                                       |                                                                                                       | 2.4  | 3.0  | 3.6  | Α        |

| r <sub>DS(ON)</sub>                                             | Rectifier ON resistance                                                                                                                    | I <sub>SW</sub> = 1 A                                                                                 |      | 0.25 | 0.4  | Ω        |

| $f_{SW}$                                                        | Switching frequency                                                                                                                        |                                                                                                       | 400  |      | 1000 | kHz      |

|                                                                 | Tolerance                                                                                                                                  |                                                                                                       | -20% |      | +20% |          |

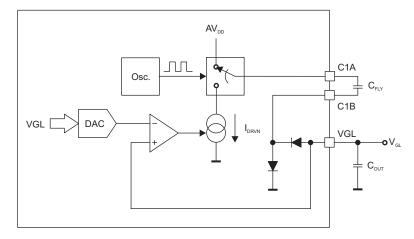

| NEGATI                                                          | VE CHARGE PUMP (V <sub>GL</sub> )                                                                                                          |                                                                                                       |      |      |      |          |

| $V_{GL}$                                                        | Output voltage range                                                                                                                       |                                                                                                       | -5   |      | -8   | V        |

| - GL                                                            | Output voltage tolerance                                                                                                                   |                                                                                                       | -3%  |      | 3.5% |          |

| $V_{UVP}$                                                       | Undervoltage protection threshold                                                                                                          | V <sub>GL</sub> rising                                                                                | 65%  | 70%  | 75%  |          |

| $V_{SCP}$                                                       | Short-circuit protection threshold                                                                                                         | V <sub>GL</sub> rising                                                                                | 25%  | 30%  | 35%  |          |

| ı                                                               | Maximum drive current                                                                                                                      | C1B sinking                                                                                           | 50   |      | 150  | mA       |

| I <sub>DRVN</sub>                                               | Maximum drive current                                                                                                                      | C1B sourcing                                                                                          | 60   |      | 160  | ША       |

| $V_{DO}$                                                        | Dropout voltage                                                                                                                            | $f_{SW}$ = 500 kHz, $C_{FLY}$ = 0.5 $\mu F$ , $I_{GL}$ = 10 mA                                        |      | 0.6  | 1.0  | V        |

| f <sub>SW</sub>                                                 | Switching frequency                                                                                                                        |                                                                                                       | 400  | 500  | 600  | kHz      |

| r <sub>DS(ON)</sub>                                             | Discharge ON resistance                                                                                                                    | I <sub>MEAS</sub> = 2 mA                                                                              | 2.1  | 3    | 3.9  | kΩ       |

| BOOST                                                           | CONVERTER 2 (V <sub>GH</sub> )                                                                                                             |                                                                                                       |      |      |      |          |

| \ <u></u>                                                       | Output voltage range                                                                                                                       |                                                                                                       | 18   |      | 25.5 | V        |

| $V_{GH}$                                                        | Tolerance                                                                                                                                  |                                                                                                       | -3%  |      | 3%   |          |

| V <sub>UVP</sub>                                                | Undervoltage protection threshold                                                                                                          | V <sub>GH</sub> falling                                                                               | 65%  | 70%  | 75%  |          |

|                                                                 | Short-circuit protection threshold                                                                                                         | V <sub>GH</sub> falling                                                                               | 25%  | 30%  | 35%  |          |

| $V_{SCP}$                                                       |                                                                                                                                            |                                                                                                       |      | 0.3  | 1.0  | Ω        |

| V <sub>SCP</sub>                                                | Switch ON resistance                                                                                                                       | $I_{SW} = 1 A$                                                                                        |      |      |      |          |

|                                                                 | Switch ON resistance  Maximum ton time                                                                                                     | ISW = 1 A                                                                                             | 1    | 2    | 2.5  | μs       |

| r <sub>DS(ON)</sub><br>t <sub>ON(MAX)</sub>                     | Maximum t <sub>ON</sub> time                                                                                                               | ISW = 1 A                                                                                             | 1 2  |      | +    | μs<br>μs |

| r <sub>DS(ON)</sub><br>t <sub>ON(MAX)</sub><br>t <sub>OFF</sub> | $\label{eq:maximum ton} \begin{aligned} & \text{Maximum t}_{\text{ON}} \text{ time} \\ & \text{t}_{\text{OFF}} \text{ time} \end{aligned}$ | ISW = TA                                                                                              |      | 2    | 2.5  |          |

| r <sub>DS(ON)</sub> t <sub>ON(MAX)</sub> t <sub>OFF</sub>       | Maximum t <sub>ON</sub> time t <sub>OFF</sub> time  CONVERTER 3                                                                            | ISW = TA                                                                                              | 2    | 2    | 2.5  | μs       |

| r <sub>DS(ON)</sub><br>t <sub>ON(MAX)</sub><br>t <sub>OFF</sub> | $\label{eq:maximum ton} \begin{aligned} & \text{Maximum t}_{\text{ON}} \text{ time} \\ & \text{t}_{\text{OFF}} \text{ time} \end{aligned}$ | ISW = TA                                                                                              |      | 2    | 2.5  |          |

# **Electrical Characteristics (continued)**

| 0.16<br>750<br>10<br>1.0<br>1.296 | 39<br>+5%<br>0.6<br>0.27<br>1250<br>+3%<br>0.048<br>%<br>+3%<br>1332 | V<br>V<br>V<br>kΩ<br>mA<br>bits                                                             |

|-----------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 750<br>10<br>1.0<br>1.296         | 0.6<br>0.27<br>1250<br>+3%<br>1%<br>0.048<br>%<br>+3%                | V<br>V<br>kΩ<br>mA<br>bits                                                                  |

| 750<br>10<br>1.0<br>1.296         | 0.27<br>1250<br>+3%<br>1%<br>0.048<br>%<br>+3%                       | V<br>V<br>kΩ<br>mA<br>bits                                                                  |

| 750<br>10<br>1.0<br>1.296         | 1250<br>+3%<br>1%<br>0.048<br>%<br>+3%                               | V<br>kΩ<br>mA<br>bits                                                                       |

| 750<br>10<br>1.0<br>1.296         | 1250<br>+3%<br>1%<br>0.048<br>%<br>+3%                               | kΩ<br>mA<br>bits                                                                            |

| 1.0 1.296                         | +3%<br>1%<br>0.048<br>%<br>+3%                                       | mA<br>bits                                                                                  |

| 1.0<br>1296                       | 1%<br>0.048<br>%<br>+3%                                              | bits                                                                                        |

| 1.0<br>1296                       | 1%<br>0.048<br>%<br>+3%                                              | bits                                                                                        |

| 1.0<br>1296                       | 1%<br>0.048<br>%<br>+3%                                              |                                                                                             |

| 1.0<br>1296                       | 0.048<br>%<br>+3%                                                    |                                                                                             |

| 1296                              | 0.048<br>%<br>+3%                                                    | V                                                                                           |

| 1296                              | %<br>+3%                                                             | V                                                                                           |

| 1296                              |                                                                      | V                                                                                           |

|                                   | 1332                                                                 |                                                                                             |

| 0.16                              |                                                                      |                                                                                             |

| 0.16                              | 0.6                                                                  | V                                                                                           |

| 0.16                              |                                                                      | V                                                                                           |

|                                   | 0.27                                                                 | V                                                                                           |

| 750                               | 1250                                                                 | kΩ                                                                                          |

|                                   |                                                                      |                                                                                             |

| 0.2                               | 0.5                                                                  | V                                                                                           |

|                                   | 1                                                                    | μA                                                                                          |

|                                   |                                                                      |                                                                                             |

|                                   | 7                                                                    |                                                                                             |

|                                   | 1                                                                    | LSB                                                                                         |

|                                   | 1                                                                    |                                                                                             |

|                                   | 7                                                                    |                                                                                             |

|                                   | 1                                                                    | LSB                                                                                         |

|                                   | 1                                                                    |                                                                                             |

|                                   | 1                                                                    |                                                                                             |

|                                   | 1                                                                    | LSB                                                                                         |

|                                   | 1                                                                    |                                                                                             |

| 21                                |                                                                      | MHz                                                                                         |

| 400                               |                                                                      |                                                                                             |

| 330                               |                                                                      | mA                                                                                          |

| 36                                |                                                                      |                                                                                             |

| 33                                |                                                                      | V/µs                                                                                        |

| -                                 | 1                                                                    | μА                                                                                          |

| 0.06                              | 0.1                                                                  |                                                                                             |

| 0.03                              | 0.1                                                                  | V                                                                                           |

|                                   |                                                                      |                                                                                             |

| 13                                | 25                                                                   | Ω                                                                                           |

| 26                                | 50                                                                   | Ω                                                                                           |

| 26                                | 50                                                                   | 32                                                                                          |

|                                   |                                                                      | V                                                                                           |

|                                   | 1.2                                                                  | V                                                                                           |

|                                   | 0.27                                                                 | V                                                                                           |

|                                   | 400<br>330<br>36<br>33<br>0.06<br>0.03                               | 21<br>400<br>330<br>36<br>33<br>1<br>0.06 0.1<br>0.03 0.1<br>13 25<br>26 50<br>26 50<br>1.2 |

## **Electrical Characteristics (continued)**

$V_{IN}$  = 3.3 V,  $V_{LED}$  = 12 V,  $V_{CC}$  = 2.5 V,  $AV_{DD}$  = 8 V,  $V_{GL}$  = -6.8 V,  $V_{GH}$  = 20 V,  $T_A$  = -40°C to 85°C. Typical values are at 25°C (unless otherwise noted).

|                                 | PARAMETER                              | TEST CONDITIONS                             | MIN               | TYP      | MAX  | UNIT      |

|---------------------------------|----------------------------------------|---------------------------------------------|-------------------|----------|------|-----------|

| I <sub>IL</sub>                 | FLK low input current                  | V <sub>FLK</sub> = 0 V                      | -100              |          | 100  | nA        |

| I <sub>IH</sub>                 | FLK high input current                 | V <sub>FLK</sub> = 1.8 V                    | -100              |          | 100  | nA        |

| PANEL R                         | ESET (XAO)                             |                                             |                   |          |      |           |

| V <sub>OL(xxxx)</sub>           | Output voltage                         | I <sub>XAO</sub> = 1 mA (sinking)           |                   | 0.16     | 0.5  | V         |

| I <sub>LK(xxo)</sub>            | Leakage current                        | V <sub>xxo</sub> = 1.8 V                    |                   |          | 1    | μΑ        |

|                                 | XAO Threshold voltage range            | - V <sub>IN</sub> falling                   | V <sub>UVLO</sub> |          | 3.0  | V         |

| $V_{DET}$                       | Tolerance                              |                                             | -3%               |          | +3%  |           |

|                                 | Hysteresis                             | V <sub>IN</sub> rising                      | 0.05              |          | 0.3  | V         |

| I <sup>2</sup> C INTER          | RFACE                                  |                                             |                   |          |      |           |

| 4000                            | Configuration parameters slave address |                                             |                   | 74h      |      |           |

| ADDR                            | Programmable VCOM slave address        |                                             |                   | 28h      |      |           |

| V <sub>IL</sub>                 | Low level input voltage                | SCL or SDA falling, standard and fast modes |                   |          | 0.6  | V         |

| V <sub>IH</sub>                 | High level input voltage               | SCL or SDA rising, standard and fast modes  | 1.0               |          |      | V         |

| $V_{\text{IH}} - V_{\text{IL}}$ | Input hysteresis                       |                                             | 0.05              |          |      | V         |

| V <sub>OL</sub>                 | Low level output voltage               | Sinking 3 mA                                |                   |          | 0.36 | V         |

| Cı                              | Input capacitance                      |                                             |                   |          | 10   | pF        |

| 0                               | Capacitive load on SDA and SCL         | Standard mode                               |                   |          | 400  | pF        |

| C <sub>B</sub>                  |                                        | Fast mode                                   |                   |          | 400  | þΓ        |

| EEPROM                          |                                        |                                             |                   |          |      |           |

| $V_{IL}$                        | WP low input voltage threshold         | V <sub>WP</sub> falling                     | 0.8               |          |      | V         |

| $V_{IH}$                        | WP high input voltage threshold        | V <sub>WP</sub> rising                      |                   |          | 1.2  | V         |

| $V_{IH}-V_{IL} \\$              | WP input voltage hysteresis            |                                             | 0.03              | 0.05     | 0.1  | V         |

| R <sub>PULL-UP</sub>            | WP internal pull-up resistor           |                                             | 20                | 60       | 100  | $k\Omega$ |

| $N_{\text{WRITE}}$              | Number of write cycles                 |                                             | 1000              |          |      |           |

|                                 | Data retention                         | Storage temperature = 150 °C                | 100               |          |      | 1000 hrs  |

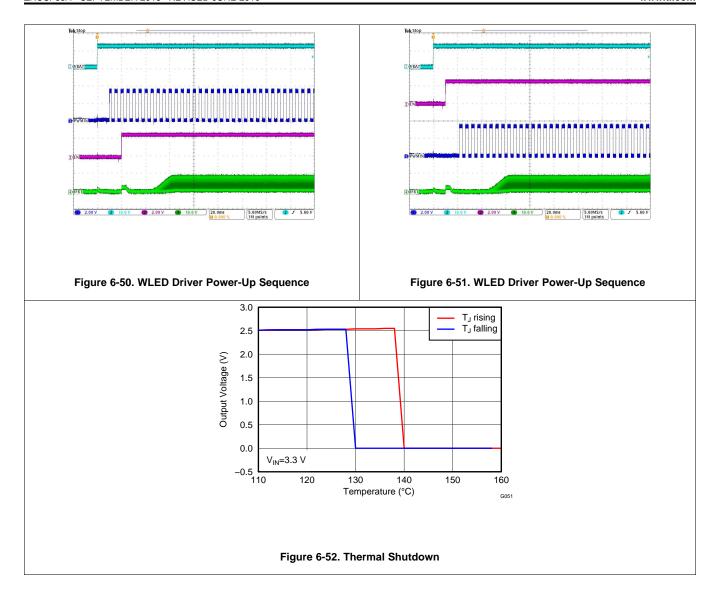

| THERMA                          | L SHUTDOWN                             |                                             |                   | <u>-</u> |      |           |

| <b>-</b>                        | Thermal shutdown temperature           |                                             |                   | 150      |      | °C        |

| T <sub>SD</sub>                 | Thermal shutdown hysteresis            |                                             |                   | 10       |      |           |

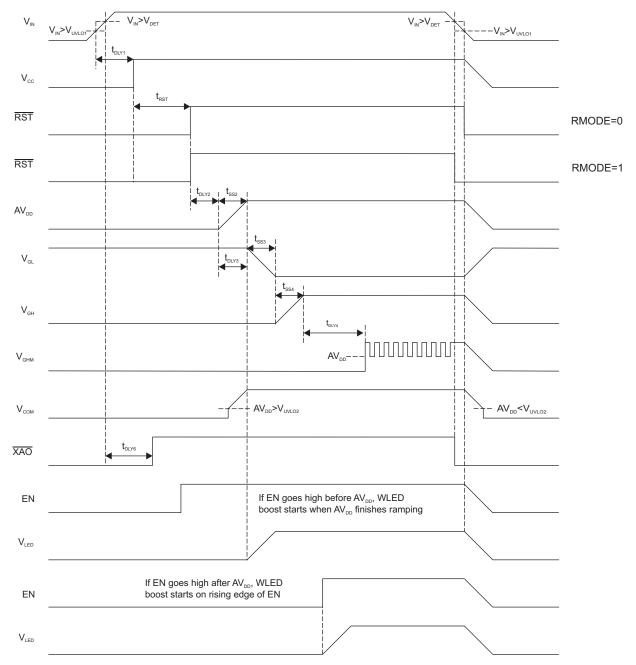

## 4.6 Timing Requirements

|                   |                                             | MIN      | TYP MAX  | UNIT |

|-------------------|---------------------------------------------|----------|----------|------|

| LINEAR F          | REGULATOR (V <sub>CC</sub> )                |          | <u> </u> |      |

| t <sub>DLY1</sub> | Linear regulator start-up delay time        | 0        | 75       | ms   |

|                   | Tolerance                                   | -20%     | 30%      |      |

| BOOST C           | ONVERTER 1 (AV <sub>DD</sub> )              |          |          |      |

| t <sub>SS2</sub>  | Boost converter 1 soft-start duration range | 0.5      | 75       | ms   |

|                   | Tolerance                                   | -20%     | 30%      |      |

| t <sub>DLY2</sub> | Boost converter 1 start-up delay range      | 0        | 75       | ms   |

|                   | Tolerance                                   | -20%     | 30%      |      |

| NEGATIV           | E CHARGE PUMP (V <sub>GL</sub> )            |          |          |      |

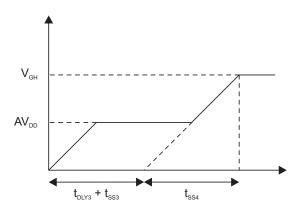

| t <sub>SS3</sub>  | Negative charge pump soft-start duration    | 0        | 35       | ms   |

|                   | Tolerance                                   | -20%     | 30%      |      |

| t <sub>DLY3</sub> | Negative charge pump start-up delay         | 0        | 35       | ms   |

|                   | Tolerance                                   | -20%     | 30%      |      |

| BOOST C           | ONVERTER 2 (V <sub>GH</sub> )               | <u> </u> |          |      |

# Timing Requirements (continued)

|                         |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MIN  | TYP | MAX  | UNIT  |

|-------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| too                     | Boost converter 2 soft-start of            | duration range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0    |     | 35   | ms    |

| t <sub>SS4</sub>        | Tolerance                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -20% |     | 30%  |       |

| BOOST CO                | ONVERTER 3                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |     |      |       |

| f                       | Switching frequency range                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 400  |     | 1000 | kHz   |

| t <sub>SW</sub>         | Tolerance                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -20% |     | 20%  |       |

| WLED DIM                | IMING                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |     |      |       |

| t <sub>PWMIN</sub>      | Input pulse width                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 500  |     |      | ns    |

|                         | Output frequency range                     | Direct dimming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.1  |     | 15   | kHz   |

| f <sub>OUT</sub>        |                                            | DPWM dimming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15   |     | 22   | NI IZ |

|                         | Tolerance                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -20% |     | 20%  |       |