SLVSCJ1B - SEPTEMBER 2014 - REVISED JANUARY 2017

**TPS68470**

# TPS68470 Power Management Unit with LED Flash Driver and Reference Clock Generation for Compact Camera Module (CCM) Applications

#### **Features**

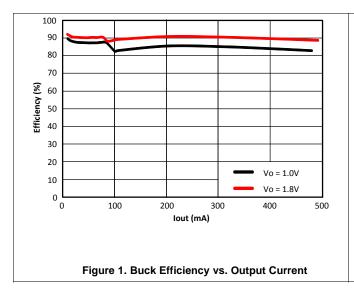

- High-Efficiency Buck Converter

- Output Current up to 500 mA

- Output Voltage Selectable: 0.9 V to 1.95 V

- **Dual Flash LED Driver**

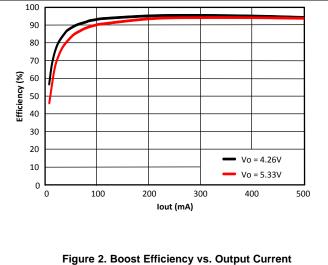

- High-Efficiency Boost Converter

- Adaptive Output Voltage Regulation Based

- Low Side LED Current Drivers

- Two 1-A Current Drivers

- LED Temperature Monitoring

- Open/Short LED Detection/Protection

- Controlled LED Current Ramp-Up/Down

- Linear Regulator for Sensor Analog Supply

- Output Voltage Programmable from 0.875 V to 3.1 V with 17.8-mV Steps

- Output Current up to 200 mA

- Linear Regulator for IO Supply

- Output Voltage Programmable from 0.875 V to 3.1 V with 17.8-mV Steps

- Output Current up to 50 mA

- Linear Regulator for VCM (Voice Coil Motor) **Driver Power**

- Output Voltage Programmable from 0.875 V to 3.1 V with 17.8-mV Steps

- Output Current up to 500 mA

- Linear Regulator for Auxiliary Power

- Output Voltage Programmable from 0.875 V to 3.1 V with 17.8-mV Steps

- Output Current up to 150 mA

- Linear Regulator for Auxiliary Power

- Output Voltage Programmable from 0.875 V to 3.1 V with 17.8-mV Steps

- Output Current up to 50 mA

- Linear Regulator for Sensor IO Supply

- Output Voltage Programmable from 0.875 V to 3.1 V with 17.8-mV Steps

- Output Current up to 150 mA

- Clock Generation

- Programmable PLL

- Crystal Oscillator

- I<sup>2</sup>C Interface

- 7 GPIOs

- System Reset

- Operating Temperature Range: 0°C to 85°C

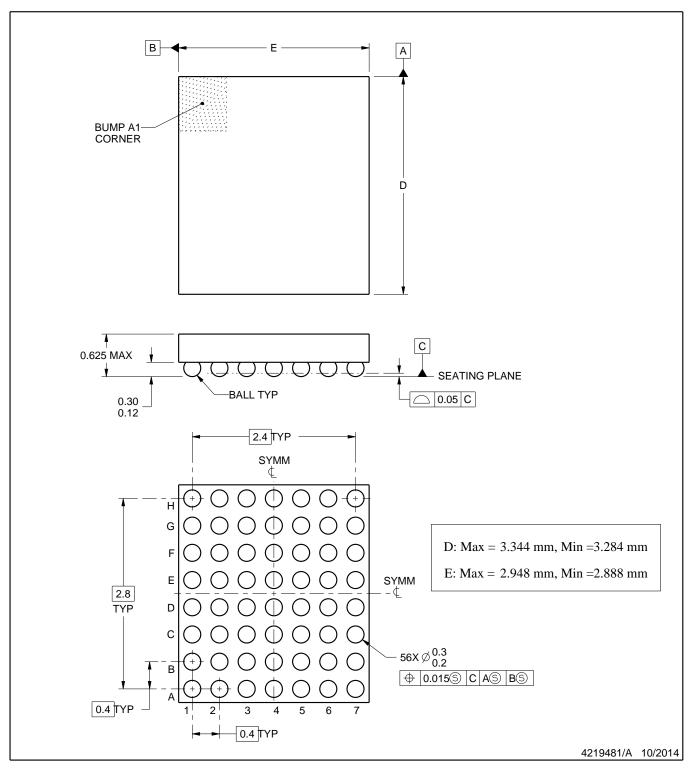

- DSBGA with Package Height of 0.625 mm

# **Applications**

- Detachable Ultrabooks

- **Tablets**

- **Smartphones**

- Compact Camera Modules (CCM)

# Description

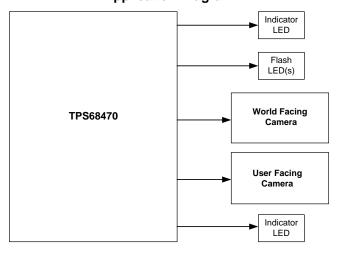

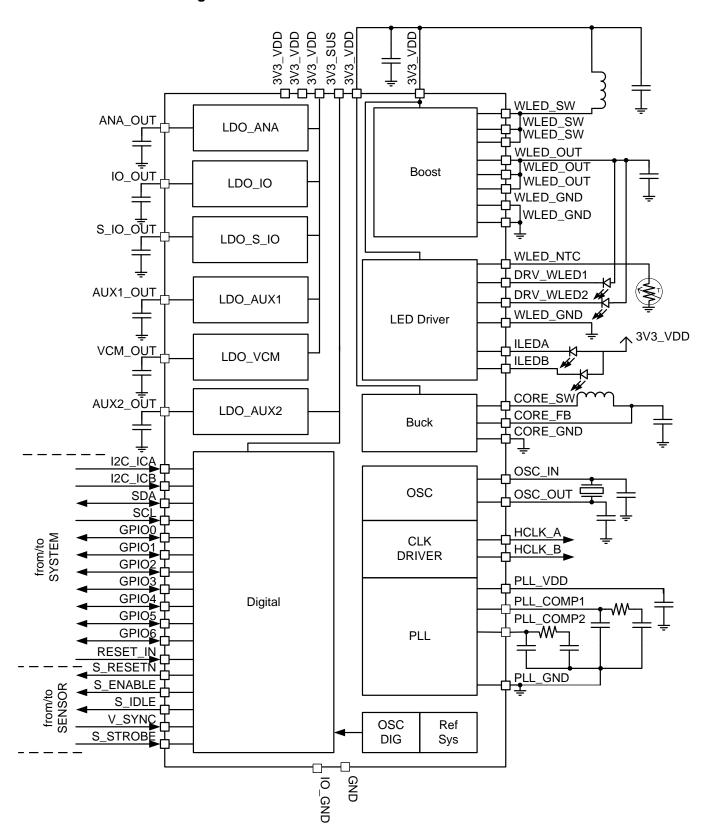

The TPS68470 device is an advanced power management unit that powers a Compact Camera Module (CCM), generates the clock for the image sensor, drives a dual LED for Flash and incorporates two LED drivers for general purpose indicators. The TPS68470 is capable of generating all needed power rails in a CCM.

The CORE voltage regulator is a state of the art buck converter which can be used for the image sensor digital supply. An LDO (LDO\_ANA) can be used for the image sensor analog supply.

The TPS68470 also has a high efficiency boost converter to support two 1A LED flash drivers. The LED currents are controlled with regulated low side current sources.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)     |

|-------------|------------|---------------------|

| TPS68470    | DSBGA (56) | 3.325 mm x 2.930 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

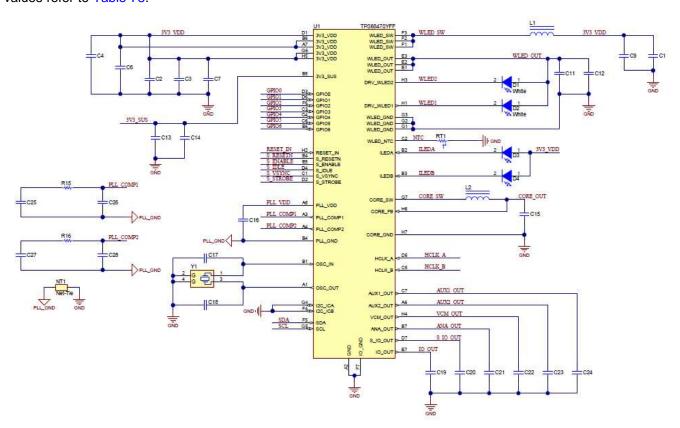

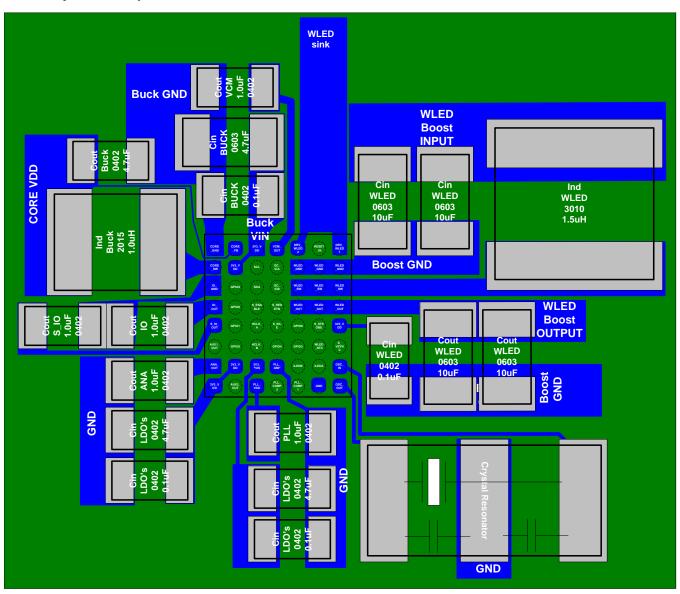

#### Application Diagram

# **Table of Contents**

| 1 | Features 1                                     |    | 8.4 Device Functional Modes                         | 35   |

|---|------------------------------------------------|----|-----------------------------------------------------|------|

| 2 | Applications 1                                 |    | 8.5 Register Map                                    | 36   |

| 3 | Description 1                                  | 9  | Application and Implementation                      | 85   |

| 4 | Revision History2                              |    | 9.1 Application Information                         | 85   |

| 5 | Description (continued) 3                      |    | 9.2 Typical Application                             | 85   |

| 6 | Pin Configuration and Functions                | 10 | Power Supply Recommendations                        | 93   |

| 7 | Specifications5                                | 11 | Layout                                              | 94   |

| • | 7.1 Absolute Maximum Ratings 5                 |    | 11.1 Layout Guidelines                              | 94   |

|   | 7.2 ESD Ratings                                |    | 11.2 Layout Example                                 | 95   |

|   | 7.3 Recommended Operating Conditions           | 12 | Device and Documentation Support                    | 96   |

|   | 7.4 Thermal Information                        |    | 12.1 Device Support                                 | 96   |

|   | 7.5 Electrical Characteristics                 |    | 12.2 Receiving Notification of Documentation Update | s 96 |

|   | 7.6 Timing Requirements - Data Transmission 15 |    | 12.3 Community Resources                            | 96   |

|   | 7.7 Typical Characteristics                    |    | 12.4 Trademarks                                     | 96   |

| 8 | Detailed Description 16                        |    | 12.5 Electrostatic Discharge Caution                | 96   |

| _ | 8.1 Overview                                   |    | 12.6 Glossary                                       | 96   |

|   | 8.2 Functional Block Diagram                   | 13 | Mechanical, Packaging, and Orderable Information    | 07   |

|   | 8.3 Feature Description                        |    | IIIOIIIIauoii                                       | 91   |

|   |                                                |    |                                                     |      |

# 4 Revision History

| Changes from Revision A (March 2015) to Revision B                                                                         | Page |

|----------------------------------------------------------------------------------------------------------------------------|------|

| Changed LDO_AUX2 Max output current from 50 mA to 80 mA                                                                    | 11   |

| Changes from Original (September 2014) to Revision A                                                                       | Page |

|                                                                                                                            |      |

| <ul> <li>Added Storage temperature to Absolute Maximum Ratings</li> </ul>                                                  | §    |

| <ul> <li>Added Storage temperature to Absolute Maximum Ratings</li> <li>Changed Handling Ratings to ESD Ratings</li> </ul> |      |

# 5 Description (continued)

The TPS68470 has five other LDOs. Two of them can be used for generic and sensor IO supply voltage generation (LDO\_IO and LDO\_S\_IO). One can be dedicated to the VCM driver supply (LDO\_VCM). The remaining two are auxiliary LDOs (LDO\_AUX1 and LDO\_AUX2).

# 6 Pin Configuration and Functions

56-Pin DSBGA YFF Package (Top View)

#### **Pin Functions**

| PIN     |        | 1/0 | DESCRIPTION                                    |  |  |

|---------|--------|-----|------------------------------------------------|--|--|

| NAME    | NUMBER | 1/0 | DESCRIPTION                                    |  |  |

| I2C_ICA | G4     | 1   | TPS68470 I <sup>2</sup> C Address select pin A |  |  |

| I2C_ICB | F4     | - 1 | TPS68470 I <sup>2</sup> C Address select pin B |  |  |

| SDA     | F5     | I/O | I <sup>2</sup> C data                          |  |  |

| SCL     | G5     | I   | l <sup>2</sup> C clk                           |  |  |

| GPIO0   | D3     | I/O | GPIO                                           |  |  |

# Pin Functions (continued)

| PIN       |             |     |                                                                    |

|-----------|-------------|-----|--------------------------------------------------------------------|

| NAME      | NUMBER      | 1/0 | DESCRIPTION                                                        |

| GPIO1     | D6          | I/O | GPIO (sensor SDA in daisy chain mode)                              |

| GPIO2     | F6          | I/O | GPIO (sensor SCL in daisy chain mode)                              |

| GPIO3     | C3          | I/O | GPIO or External Reference Clock when XTAL is disabled             |

| GPIO4     | C4          | I/O | GPIO                                                               |

| GPIO5     | C6          | I/O | GPIO                                                               |

| GPIO6     | E6          | I/O | GPIO                                                               |

| S_RESETN  | E4          | 0   | Sensor reset                                                       |

| S_ENABLE  | E5          | 0   | Sensor power enable / power down                                   |

| S_IDLE    | D4          | 0   | Sensor power down mode                                             |

| S_VSYNC   | C1          | 1   | Sensor activity indication enable                                  |

| RESET_IN  | H2          | I   | Platform reset input (active low)                                  |

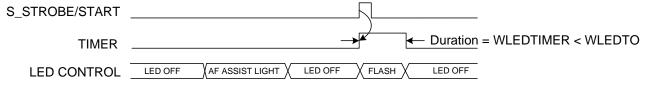

| S_STROBE  | D2          | 1   | White LED trigger input                                            |

| OSC_IN    | B1          | 1   | XTAL input                                                         |

| OSC_OUT   | A1          | 0   | XTAL output                                                        |

| HCLK_A    | D5          | 0   | Sensor Clock                                                       |

| HCLK_B    | C5          | 0   | Alternate Sensor Clock                                             |

| PLL_COMP1 | А3          | 0   | PLL compensation                                                   |

| PLL_COMP2 | A4          | 0   | SS PLL compensation                                                |

| VCM_OUT   | H4          | 0   | VCM LDO output                                                     |

| ANA_OUT   | B7          | 0   | Analog LDO output                                                  |

| IO_OUT    | E7          | 0   | IO LDO output                                                      |

| S_IO_OUT  | D7          | 0   | Sensor IO LDO output                                               |

| IO_GND    | F7          | -   | IO and digital GND                                                 |

| AUX1_OUT  | C7          | 0   | Auxiliary LDO1 output                                              |

| AUX2_OUT  | A6          | 0   | Auxiliary LDO2 output                                              |

| CORE_SW   | G7          | 0   | Core Buck SW                                                       |

| CORE_FB   | H6          | I   | Core Buck feedback                                                 |

| CORE_GND  | H7          | -   | Core Buck GND                                                      |

| WLED_SW   | F3, F2, F1  | 0   | White LED Boost SW                                                 |

| WLED_OUT  | E3, E2, E1  | 0   | White LED Boost output, connect 2 x 10uF capacitors to this output |

| WLED_GND  | G3, G2, G1  | -   | White LED Boost GND                                                |

| WLED_NTC  | C2          | I   | White LED Temperature sensor feedback                              |

| DRV_WLED1 | H1          | 1   | White LED 1 current sink (the source of current is from WLED_OUT)  |

| DRV_WLED2 | Н3          | - 1 | White LED 2 current sink (the source of current is from WLED_OUT)  |

| ILEDA     | B2          | 0   | Indicator LED A driver                                             |

| ILEDB     | В3          | 0   | Indicator LED B driver                                             |

| PLL_VDD   | A5          | 0   | PLL internal regulator (connect a 1µF capacitor to this pin)       |

| PLL_GND   | B4          | -   | PLL GND                                                            |

| 3V3_VDD   | H5, G6, D1, | I   | 3.3V input                                                         |

|           | B6, A7      |     | * H5 - LDO_VCM                                                     |

|           |             |     | * G6 - CORE Buck Converter                                         |

|           |             |     | * D1 - WLED Boost Converter                                        |

|           |             |     | * B6 - LDO_PLL                                                     |

|           |             |     | * A7 - LDO_AUX1, LDO_ANA, LDO_IO, LDO_SIO                          |

| 3V3_SUS   | B5          | I   | 3.3V Auxiliary sustaining rail input (LDO_AUX2)                    |

| GND       | A2          | -   | Ground                                                             |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|               |                                                        | MIN  | MAX                                      | UNIT  |

|---------------|--------------------------------------------------------|------|------------------------------------------|-------|

|               | 3V3_VDD, 3V3_SUS                                       | -0.3 | 3.96                                     |       |

|               | DRV_WLED1, DRV_WLED2                                   | -0.3 | 7.0                                      |       |

|               | WLED_SW, WLED_OUT                                      | -0.3 | 7.0                                      |       |

|               | CORE_SW                                                | -0.3 | 7.0                                      |       |

|               | I2C_ICA, I2C_ICB, SDA, SCL                             | -0.3 | 3.96                                     |       |

|               | GPI00-6                                                | -0.3 | 3.96                                     |       |

|               | S_RESETN, S_ENABLE, S_IDLE, S_VSYNC, S_STROBE          | -0.3 | 3.96                                     |       |

| Voltage       | RESET_IN                                               | -0.3 | 3.96                                     | V     |

| voltage       | OSC_IN, OSC_OUT                                        | -0.3 | .3 3.96<br>.3 3.96<br>.3 3.96<br>.3 3.96 | \ \ \ |

|               | HCLK_A, HCLK_B                                         | -0.3 | 3.96                                     |       |

|               | PLL_COMP1, PLL_COMP2                                   | -0.3 | 3.96                                     |       |

|               | VCM_OUT, ANA_OUT, IO_OUT, S_IO_OUT, AUX1_OUT, AUX2_OUT | -0.3 | 3.96                                     |       |

|               | CORE_FB                                                | -0.3 | 3.96                                     |       |

|               | WLED_NTC                                               | -0.3 | 3.96                                     |       |

|               | ILEDA, ILEDB                                           | -0.3 | 3.96                                     |       |

|               | PLL_VDD                                                | -0.3 | 3.96                                     |       |

| Continuous p  | ower dissipation, P <sub>D</sub>                       |      | 1.6                                      | W     |

| Operating jun | ction temperature, T <sub>J</sub>                      | -30  | 125                                      | °C    |

| Storage temp  | erature, T <sub>stg</sub>                              | -65  | 150                                      | °C    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                                   |                         |                                                                     | VALUE | UNIT |

|-----------------------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V (1)                             | Clastrostatia diasharas | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (2)              | 2000  | \/   |

| V <sub>(ESD)</sub> <sup>(1)</sup> | Flactrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (3) | 500   | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges in to the device.

<sup>(2)</sup> All voltage values are with respect to GND.

<sup>(2)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature (unless otherwise noted)

|              |                                                                                    | MIN  | NOM | MAX                      | UNIT |

|--------------|------------------------------------------------------------------------------------|------|-----|--------------------------|------|

|              | 3V3_VDD, 3V3_SUS                                                                   | 2.97 | 3.3 | 3.63                     |      |

|              | DRV_WLED1, DRV_WLED2                                                               |      |     | Setting<br>Depend<br>ent |      |

|              | WLED_SW, WLED_OUT                                                                  |      |     | Setting<br>Depend<br>ent |      |

|              | CORE_SW                                                                            |      |     | Setting<br>Depend<br>ent |      |

|              | I2C_ICA, I2C_ICB  SDA, SCL  GPIO0-6  S_RESETN, S_ENABLE, S_IDLE, S_VSYNC, S_STROBE |      |     |                          |      |

|              |                                                                                    |      |     | 3.3                      |      |

| Voltage      |                                                                                    |      |     | 3.3                      | V    |

|              |                                                                                    |      |     | 3.3                      |      |

|              | RESET_IN                                                                           |      |     | 3.3                      |      |

|              | OSC_IN, OSC_OUT                                                                    |      |     | 3.3                      |      |

|              | HCLK_A, HCLK_B                                                                     |      |     | 3.3                      |      |

|              | PLL_COMP1, PLL_COMP2                                                               |      |     | 3.3                      |      |

|              | VCM_OUT, ANA_OUT, IO_OUT, S_IO_OUT, AUX1_OUT, AUX2_OUT                             | 3.1  |     | 3.1                      |      |

|              | CORE_FB                                                                            |      |     | 1.95                     |      |

|              | WLED_NTC                                                                           |      |     | 3.3                      |      |

|              | ILEDA, ILEDB                                                                       |      |     | 3.3                      |      |

|              | PLL_VDD                                                                            |      |     | 3.3                      |      |

| Operating am | bient temperature, T <sub>A</sub>                                                  | 0    |     | 85                       | °C   |

# 7.4 Thermal Information

|                    | THERMAL METRIC <sup>(1)</sup>                | YFF (DSBGA)<br>56 PINS | UNIT |

|--------------------|----------------------------------------------|------------------------|------|

| $R_{\theta JA}$    | Junction-to-ambient thermal resistance       | 39.8                   |      |

| $R_{\theta JCtop}$ | Junction-to-case (top) thermal resistance    | 0.2                    |      |

| $R_{\theta JB}$    | Junction-to-board thermal resistance         | 6.6                    | °C/W |

| ΨЈТ                | Junction-to-top characterization parameter   | 0.5                    | C/VV |

| ΨЈВ                | Junction-to-board characterization parameter | 6.5                    |      |

| $R_{\theta JCbot}$ | Junction-to-case (bottom) thermal resistance | n/a                    |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

Over recommended free-air temperature and over recommended input voltage (typical at an ambient temperature range of 27°C) (unless otherwise noted)

|                         | PARAMETER                                      | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                          | MIN    | TYP   | MAX     | UNIT  |

|-------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|---------|-------|

| SUPPLY VOI              | TAGE and UVLO                                  | 1231 GONDINONG                                                                                                                                                                                                                                                                                                                                           | 141114 |       | AII/A/A | CINII |

| V <sub>I(3V3_VDD)</sub> | Operating input voltage                        |                                                                                                                                                                                                                                                                                                                                                          | 2.97   | 3.3   | 3.63    | V     |

| V <sub>I(3V3_SUS)</sub> | Operating input voltage                        |                                                                                                                                                                                                                                                                                                                                                          | 2.97   | 3.3   | 3.63    | V     |

| 1(3V3_3U3)              | operating input total                          | In ACTIVE mode, V <sub>I(3V3_VDD)</sub> = V <sub>I(3V3_SUS)</sub> = 3.3 V, LDO_IO enabled and with no load, LDO_PLL, LDO_ANA, LDO_S_IO, LDO_AUX1, LDO_VCM, CORE and WLED_OUT disabled and with no load LDO_AUX2 disabled and with no load                                                                                                                | 65     | 100   | 145     | μА    |

|                         |                                                | In ACTIVE mode, V <sub>I(3V3_VDD)</sub> = V <sub>I(3V3_SUS)</sub> = 3.3 V, LDO_IO enabled and with no load, LDO_PLL, LDO_ANA, LDO_S_IO, LDO_AUX1, LDO_VCM, CORE and WLED_OUT disabled and with no load LDO_AUX2 enabled and with no load - LDO_AUX2 current comes from 3V3_SUS                                                                           | 65     | 100   | 145     | μА    |

| I <sub>Q(3V3_VDD)</sub> | 3V3_VDD quiescent current                      | In ACTIVE mode, $V_{I(3V3\_VDD)} = V_{I(3V3\_SUS)} = 3.3$ V, LDO_ANA, LDO_IO, LDO_S_IO, LDO_AUX1, LDO_VCM, CORE and WLED_OUT enabled (default voltage settings) and with no load, LDO_PLL disabled, CORE and WLED_OUT running on internal oscillator LDO_AUX2 disabled and with no load                                                                  |        | 5     |         | mA    |

|                         |                                                | In ACTIVE mode, V <sub>I(3V3_VDD)</sub> = V <sub>I(3V3_SUS)</sub> = 3.3 V, LDO_IO enabled and with no load, LDO_PLL enabled, BUCKDIV [3:0] set to 5.2 MHz, BOOSTDIV [4:0] set to 2 MHz, POSTDIV for HCLK_A and HCLK_B set to 18 MHz LDO_ANA, LDO_S_IO, LDO_AUX1, LDO_VCM, CORE and WLED_OUT disabled and with no load LDO_AUX2 disabled and with no load |        | 0.91  |         | mA    |

|                         | 3V3_SUS quiescent current                      | In ACTIVE mode, $V_{I(3V3\_VDD)} = V_{I(3V3\_SUS)} = 3.3$ V, LDO_AUX2 disabled and with no load                                                                                                                                                                                                                                                          | 25     | 35    | 50      | μΑ    |

|                         |                                                | In ACTIVE mode, $V_{I(3V3\_VDD)} = V_{I(3V3\_SUS)} = 3.3$ V, LDO_AUX2 enabled and with no load                                                                                                                                                                                                                                                           | 70     | 102   | 130     | μΑ    |

|                         |                                                | In ACTIVE mode, $V_{I(3V3\_VDD)} = V_{I(3V3\_SUS)} = 3.3$ V, LDO_ANA, LDO_IO, LDO_S_IO, LDO_AUX1, LDO_VCM, CORE and WLED_OUT enabled (default voltage settings) and with no load, LDO_PLL disabled, CORE and WLED_OUT running on internal oscillator LDO_AUX2 disabled and with no load                                                                  |        | 255   |         | μА    |

| I <sub>Q(3V3_SUS)</sub> |                                                | In ACTIVE mode, $V_{I(3V3\_VDD)} = V_{I(3V3\_SUS)} = 3.3$ V, LDO_IO enabled and with no load, LDO_PLL enabled, BUCKDIV [3:0] set to 5.2 MHz, BOOSTDIV [4:0] set to 2 MHz, POSTDIV for HCLK_A and HCLK_B set to 18 MHz LDO_ANA, LDO_S_IO, LDO_AUX1, LDO_VCM, CORE and WLED_OUT disabled and with no load LDO_AUX2 disabled and with no load               |        | 1.367 |         | mA    |

|                         |                                                | In SLEEP mode, V <sub>I(3V3_VDD)</sub> = 0 V, V <sub>I(3V3_SUS)</sub> = 3.3 V, LDO_AUX2 disabled and with no load                                                                                                                                                                                                                                        |        | 0.3   | 1.1     | μΑ    |

|                         |                                                | In SLEEP mode, V <sub>I(3V3_VDD)</sub> = 0 V, V <sub>I(3V3_SUS)</sub> = 3.3 V, LDO_AUX2 enabled and with no load                                                                                                                                                                                                                                         | 75     | 100   | 125     | μΑ    |

|                         | Under voltage leeks at the select of           | V <sub>I(3V3_VDD</sub> ) going up                                                                                                                                                                                                                                                                                                                        | 2.6    | 2.75  | 2.85    |       |

| JVLO <sub>3V3_VDD</sub> | Under voltage lockout threshold at 3V3_VDD pin | V <sub>I(3V3_VDD</sub> ) going down                                                                                                                                                                                                                                                                                                                      | 2.55   | 2.65  | 2.75    | V     |

|                         | ·                                              | Hysteresis                                                                                                                                                                                                                                                                                                                                               |        | 0.1   |         |       |

Over recommended free-air temperature and over recommended input voltage (typical at an ambient temperature range of 27°C) (unless otherwise noted)

|                                   | PARAMETER                                       | TEST CONDITIONS                                                                                                                                              | MIN   | TYP  | MAX  | UNIT |

|-----------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|------|

|                                   |                                                 | V <sub>I(3V3_SUS</sub> ) going up                                                                                                                            | 2.6   | 2.75 | 2.85 |      |

| UVLO <sub>3V3_SUS</sub>           | Under voltage lockout threshold at 3V3_SUS pin  | V <sub>I(3V3_SUS</sub> ) going down                                                                                                                          | 2.55  | 2.65 | 2.75 | V    |

|                                   | 0.00_000 pm                                     | Hysteresis                                                                                                                                                   |       | 0.1  |      |      |

| BOOST CON                         | VERTER (WLED_OUT)                               |                                                                                                                                                              |       |      | ·    |      |

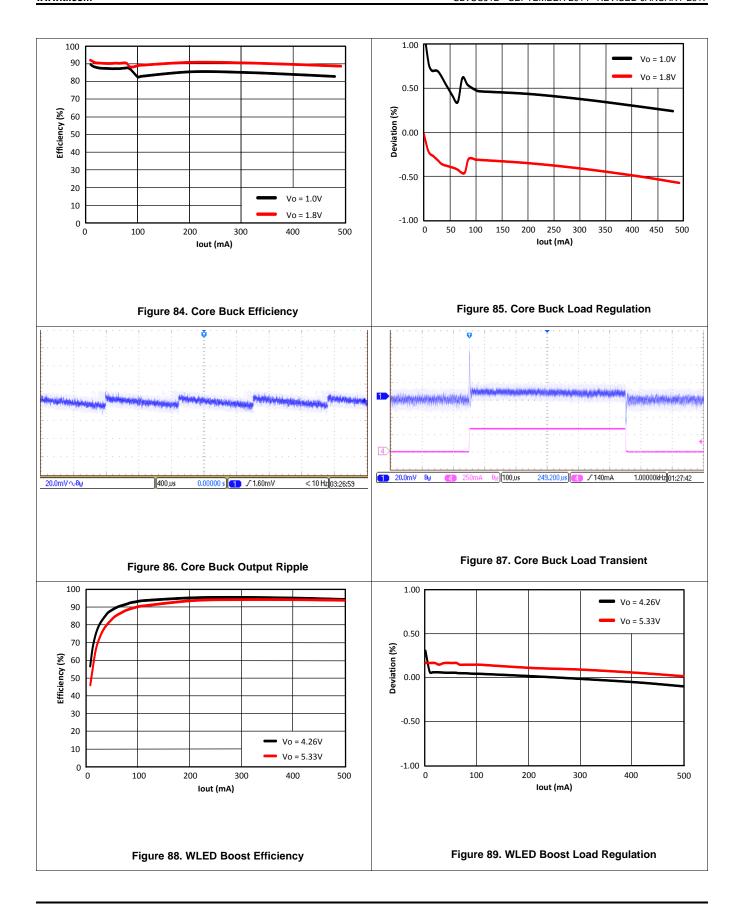

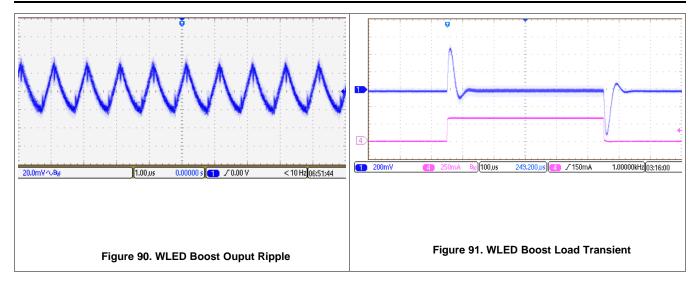

| VI(3V3_VDD)                       | Input Voltage                                   |                                                                                                                                                              | 2.97  | 3.3  | 3.63 | V    |

|                                   | 0                                               | Current regulation mode                                                                                                                                      | VIN   |      | 5.5  | V    |

| V <sub>O(WLED_OUT)</sub>          | Output voltage range                            | Voltage regulation mode                                                                                                                                      | 3.68  |      | 5.48 | V    |

| , – ,                             | Internal feedback voltage accuracy              | Boost mode, PWM voltage regulation                                                                                                                           | -2%   |      | 2%   |      |

|                                   | Output overvoltage protection                   | V <sub>O(WLED OUT)</sub> rising                                                                                                                              | 5.7   | 6.0  | 6.25 | V    |

| $V_{OVP}$                         | Output overvoltage protection hysteresis        | V <sub>O(WLED_OUT)</sub> falling                                                                                                                             |       | 100  |      | mV   |

| t <sub>start</sub>                | Start-up time                                   |                                                                                                                                                              |       | 1    |      | ms   |

| D <sub>WLED_SW</sub>              | Minimum duty cycle                              |                                                                                                                                                              |       | 7.5% |      |      |

|                                   | Switch MOSFET on-resistance                     |                                                                                                                                                              |       | 40   |      | mΩ   |

| R <sub>DS(ON)</sub>               | Rectifier MOSFET on-resistance                  | $V_{O(WLED\_OUT)} = Vgs = 3.6 V$                                                                                                                             |       | 40   |      | mΩ   |

| I <sub>LK(WLED SW)</sub>          | Switch MOSFET leakage                           | V <sub>WLED SW</sub> = 3.6 V, T <sub>A</sub> = 85°C                                                                                                          |       | 0.22 | 1.2  | μA   |

|                                   | Switch current limit                            | ILIM[3:0] = '1010'                                                                                                                                           |       | 4.0  |      |      |

| I <sub>LIM</sub>                  |                                                 | Selectable range (1)                                                                                                                                         | 2.0   |      | 5.0  | Α    |

| C <sub>IN</sub>                   | External Input capacitor                        |                                                                                                                                                              |       | 4.7  |      | μF   |

| C <sub>LC</sub>                   | External LC capacitance                         |                                                                                                                                                              | 10    | 20   | 26   | μF   |

| L <sub>LC</sub>                   | External LC inductance                          |                                                                                                                                                              | 1.3   | 2.2  | 2.9  | μH   |

| LED DRIVER                        |                                                 |                                                                                                                                                              |       |      |      |      |

|                                   | Maximum operating current per driver            | Driver on                                                                                                                                                    |       |      | 1    | А    |

|                                   | DDV W/ FD:                                      | $0.4 \text{ V} \le \text{V}_{\text{DRV}_{\text{WLEDx}}} \le 2.0 \text{ V},$<br>$0 \text{ mA} \le \text{I}_{\text{DRV}_{\text{WLEDx}}} \le 300 \text{ mA}$    | -10%  |      | 10%  |      |

| I <sub>DRV_WLEDx</sub>            | DRV_WLEDx current accuracy                      | $0.4 \text{ V} \le \text{V}_{\text{DRV}_{\text{WLEDx}}} \le 2.0 \text{ V},$<br>$300 \text{ mA} \le \text{I}_{\text{DRV}_{\text{WLEDx}}} \le 1000 \text{ mA}$ | -7.5% |      | 7.5% |      |

|                                   | DRV_WLED1 and DRV_WLED2 current matching        |                                                                                                                                                              | -10%  |      | 10%  |      |

| $I_{ILEDx}$                       | Indicator LEDx driver maximum operating current |                                                                                                                                                              |       |      | 16   | mA   |

|                                   | ILEDx current accuracy                          | $V_{ILEDx} = 1.0 \text{ V}$ at $I_{ILEDx} = 16 \text{ mA}$                                                                                                   | -10%  |      | 10%  |      |

| V <sub>SENSE(DRV_</sub><br>WLEDx) | DRV_WLEDx sense voltage                         | I <sub>DRV_WLEDx</sub> = full-scale current                                                                                                                  |       | 400  |      | mV   |

| I <sub>ILK(DRV_WLED</sub><br>x)   | DRV_WLEDx input leakage current                 | V <sub>DRV_WLEDx</sub> = 3.6 V, T <sub>A</sub> = 85°C                                                                                                        |       |      | 5    | μA   |

| I <sub>ILK(ILEDx)</sub>           | ILEDx input leakage current                     | $V_{ILEDx} = 0 \text{ V}, T_A = 85^{\circ}\text{C}$                                                                                                          |       | -    | 1    | μΑ   |

| LED TEMPER                        | ATURE MONITORING                                |                                                                                                                                                              |       |      |      |      |

| I <sub>O(WLED_NTC)</sub>          | Temperature sense current source                | Thermistor bias current                                                                                                                                      |       | 23.8 |      | μΑ   |

|                                   | TS resistance (warning temperature)             | LEDWARN bit = 1                                                                                                                                              | 0.92  | 1.05 | 1.19 | V    |

|                                   | TS resistance (hot temperature)                 | LEDHOT bit = 1                                                                                                                                               | 0.29  | 0.35 | 0.4  | V    |

<sup>(1)</sup> Boost current limit is selectable from register VWLEDILIM with 4-bits

Over recommended free-air temperature and over recommended input voltage (typical at an ambient temperature range of 27°C) (unless otherwise noted)

| - / (                   | PARAMETER                                  | TEST CONDITIONS                                                                                                  | MIN   | TYP  | MAX  | UNIT |

|-------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|------|------|------|

| BUCK CONV               | ERTER (CORE)                               |                                                                                                                  | 1     |      | '    |      |

| V <sub>I(3V3_VDD)</sub> | Input voltage                              |                                                                                                                  | 2.97  | 3.3  | 3.63 | V    |

| M                       | Regulated DC output voltage                | 0 mA ≤ I <sub>O</sub> ≤ 500 mA, DVOLT[5:0] = 0x0D                                                                | 1.15  | 1.2  | 1.25 | V    |

| $V_{O(CORE)}$           | Output voltage range                       | Range selectable with 25-mV steps                                                                                | 0.9   | 1.2  | 1.95 | V    |

| C                       | High-Side MOSFET on resistance             | $V_{I(3V3\_VDD)} = V_{(GS)} = 3.3 \text{ V}, 100\% \text{ Duty Cycle}$                                           |       | 180  |      | mΩ   |

| R <sub>DS(ON)</sub>     | Low-Side MOSFET on resistance              | $V_{I(3V3\_VDD)} = V_{(GS)} = 3.3 \text{ V}, 0\% \text{ Duty Cycle}$                                             |       | 150  |      | mΩ   |

| V <sub>SHORT</sub>      | Output short detection comparator          | V <sub>O(CORE)</sub> < V <sub>SHORT</sub> for greater than 10 ms                                                 |       | 0.5  |      | V    |

| R <sub>DIS</sub>        | Discharge resistor for power down sequence | Core Disabled                                                                                                    |       | 190  | 375  | Ω    |

| I <sub>O(CORE)</sub>    | Output operating current                   |                                                                                                                  |       |      | 500  | mA   |

|                         | P-MOS current limit                        |                                                                                                                  |       | 1000 |      | mA   |

| $f_{SW}$                | Clock frequency range                      |                                                                                                                  | 3     | 5.2  | 6    | MHz  |

| R <sub>FB</sub>         | Feedback input resistance                  |                                                                                                                  |       | 500  |      | kΩ   |

| t <sub>Ramp</sub>       | V <sub>O(CORE)</sub> ramp up time          | Time to ramp from 5% to 95% of V <sub>OUT</sub> (V <sub>O(CORE)</sub> =1.2 V) ,no load, typical C <sub>OUT</sub> |       | 85   | 200  | μs   |

| C <sub>IN</sub>         | External input capacitor                   |                                                                                                                  |       | 4.7  |      | μF   |

| C <sub>LC</sub>         | External LC capacitance                    |                                                                                                                  | 2.35  | 4.7  | 6.11 | μF   |

| L <sub>LC</sub>         | External LC inductance                     |                                                                                                                  | 0.5   | 1.0  | 1.3  | μH   |

| LDO_ANA                 |                                            |                                                                                                                  | •     |      | •    |      |

| V <sub>I(3V3_VDD)</sub> | Input voltage                              |                                                                                                                  |       | 3.3  |      | V    |

| M                       | Output voltage                             | See (2)                                                                                                          | 0.875 | 2.8  | 3.1  | V    |

| $V_{O(ANA\_OUT)}$       | Output DC accuracy                         | $V_{I(3V3\_VDD)} - V_{O(ANA\_OUT)} > 200 \text{ mV}$                                                             | -2%   |      | 2%   |      |

|                         | Dropout voltage                            | $V_{3V3\_VDD} = 0.975 \times V_{OUT(NOM)}, I_{OUT} = 200 \text{ mA}$                                             |       | 100  | 150  | mV   |

|                         | Load regulation                            | 0 mA ≤ I <sub>out</sub> ≤ 200 mA                                                                                 |       |      | 15   | mV   |

|                         | Line regulation                            | $V_{OUT(NOM)} + 0.3 \text{ V} \le V_{3V3\_VDD} \le 3.63 \text{ V},$<br>$I_{OUT} = 10 \text{ mA}$                 |       |      | 5    | mV   |

| I <sub>max</sub>        | Max output current                         |                                                                                                                  |       |      | 200  | mA   |

| DCDD                    | Davis available satisfaction and           | $f = 1 \text{ kHz}, V_1 = 3.3 \text{ V}, V_0 = 2.8 \text{ V}, I_{OUT} = 0.75*200 \text{ mA}$                     | 50    | 56   |      | -10  |

| PSRR                    | Power supply rejection ratio               | $f = 10 \text{ kHz}, V_I = 3.3 \text{ V}, V_O = 2.8 \text{ V}, I_{OUT} = 0.75*200 \text{ mA}$                    | 30    | 38   |      | dB   |

| V <sub>SHORT</sub>      | Output short detection comparator          | V <sub>O(ANA_OUT)</sub> < V <sub>SHORT</sub> for greater than 10ms                                               |       | 0.5  |      | V    |

| T <sub>start</sub>      | Startup time                               | $C_{OUT}$ = 1.0 $\mu$ F, $V_{O(ANA\_OUT)}$ from 0 V to 2.8 V                                                     |       | 100  |      | μs   |

| R <sub>DIS</sub>        | Discharge resistor in power down           |                                                                                                                  |       | 100  | 200  | Ω    |

| C <sub>OUT</sub>        | Output capacitance                         |                                                                                                                  | 0.5   | 1.0  | 1.3  | μF   |

<sup>(2)</sup> All LDO output voltages are selectable through a specific voltage adjustment register xVAL bits xVOLT[6:0] and can be adjusted from 0.875 V up to 3.1 V with steps of 17.8 mV. Output voltage register setting xVOLT[6:0] values (dec) can be calculated with the below formula:

$xVOLT(DEC) = round[(V_out - 0.875 V)/0.0178 V]$

Over recommended free-air temperature and over recommended input voltage (typical at an ambient temperature range of 27°C ) (unless otherwise noted)

|                          | PARAMETER                         | TEST CONDITIONS                                                                                  | MIN   | TYP | MAX | UNIT |

|--------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------|-------|-----|-----|------|

| LDO_VCM                  |                                   |                                                                                                  |       |     |     |      |

| V <sub>I(3V3_VDD)</sub>  | Input Voltage                     |                                                                                                  |       | 3.3 |     | V    |

|                          | Output voltage                    | See (2)                                                                                          | 0.875 | 2.8 | 3.1 | V    |

| $V_{O(VCM\_OUT)}$        | Output DC accuracy                | $V_{I(3V3\_VDD)} - V_{O(VCM\_OUT)} > 200 \text{ mV}$                                             | -2%   |     | 2%  |      |

|                          | Dropout voltage                   | $V_{3V3\_VDD} = 0.975 \times V_{OUT(NOM)}, I_{OUT} = 500 \text{ mA}$                             |       | 100 | 150 | mV   |

|                          | Load regulation                   | 0 mA ≤ I <sub>out</sub> ≤ 500 mA                                                                 |       |     | 15  | mV   |

|                          | Line regulation                   | $V_{OUT(NOM)} + 0.3 \text{ V} \le V_{3V3\_VDD} \le 3.63 \text{ V},$<br>$I_{OUT} = 10 \text{ mA}$ |       |     | 5   | mV   |

| I <sub>max</sub>         | Max output current                |                                                                                                  |       |     | 500 | mA   |

| PSRR                     | Dower supply rejection ratio      | $f = 1 \text{ kHz}, V_1 = 3.3 \text{ V}, V_0 = 2.8 \text{ V}, I_{OUT} = 0.75*500 \text{ mA}$     | 50    | 60  |     | dB   |

| FORK                     | Power supply rejection ratio      | $f = 10 \text{ kHz}, V_1 = 3.3 \text{ V}, V_0 = 2.8 \text{ V}, I_{OUT} = 0.75*500 \text{ mA}$    | 30    | 40  |     | ub   |

| $V_{SHORT}$              | Output short detection comparator | V <sub>O(VCM_OUT)</sub> < V <sub>SHORT</sub> for greater than 10ms                               |       | 0.5 |     | V    |

| T <sub>start</sub>       | Startup time                      | $C_{OUT}$ = 1.0 $\mu$ F, Vout from 0 V to 2.8 V                                                  |       | 100 |     | μs   |

| R <sub>DIS</sub>         | Discharge resistor in power down  |                                                                                                  |       | 100 | 200 | Ω    |

| C <sub>OUT</sub>         | Output capacitance                |                                                                                                  | 0.5   | 1.0 | 1.3 | μF   |

| LDO_AUX1                 |                                   |                                                                                                  |       |     |     |      |

| $V_{I(3V3\_VDD)}$        | Input voltage                     |                                                                                                  |       | 3.3 |     | V    |

| V                        | Output voltage                    | See (2)                                                                                          | 0.875 | 1.2 | 3.1 | V    |

| V <sub>O(AUX1_OUT)</sub> | Output accuracy                   | $V_{I(3V3\_VDD)}$ - $V_{O(AUX1\_OUT)}$ > 200 mV                                                  | -2%   |     | 2%  |      |

|                          | Dropout voltage                   | $V_{3V3\_VDD} = 0.975 \times V_{OUT(NOM)}, I_{OUT} = 150 \text{ mA}$                             |       | 100 | 150 | mV   |

|                          | Load regulation                   | 0 mA ≤ I <sub>out</sub> ≤ 150 mA                                                                 |       |     | 15  | mV   |

|                          | Line regulation                   | $V_{OUT(NOM)} + 0.3 \text{ V} \le V_{3V3\_VDD} \le 3.63 \text{ V},$<br>$I_{OUT} = 10 \text{ mA}$ |       |     | 5   | mV   |

| I <sub>max</sub>         | Max output current                |                                                                                                  |       |     | 150 | mA   |

| DCDD                     | Dower supply rejection ratio      | $f = 1 \text{ kHz}, V_I = 3.3 \text{ V}, V_O = 1.2 \text{ V}, I_{OUT} = 0.75*150 \text{ mA}$     | 50    | 56  |     | dB   |

| PSRR                     | Power supply rejection ratio      | $ f = 10 \text{ kHz}, \ V_I = 3.3 \ V, \ V_O = 1.2 \ V, \ I_{OUT} = 0.75*150 \ \text{mA} $       | 30    | 38  |     | dB   |

| V <sub>SHORT</sub>       | Output short detection comparator | V <sub>O(AUX1_OUT)</sub> < V <sub>SHORT</sub> for greater than 10 ms                             |       | 0.5 |     | V    |

| T <sub>start</sub>       | Startup time                      | $C_{OUT}$ = 1.0 $\mu$ F, Vout from 0 V to 1.2 V                                                  |       | 100 |     | μs   |

| R <sub>DIS</sub>         | Discharge resistor in power down  |                                                                                                  |       | 100 | 200 | Ω    |

| C <sub>OUT</sub>         | Output capacitance                |                                                                                                  | 0.5   | 1.0 | 1.3 | μF   |

Over recommended free-air temperature and over recommended input voltage (typical at an ambient temperature range of 27°C ) (unless otherwise noted)

|                         | PARAMETER                         | TEST CONDITIONS                                                                                  | MIN   | TYP | MAX | UNIT |

|-------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------|-------|-----|-----|------|

| LDO_AUX2                |                                   |                                                                                                  |       |     |     |      |

| V <sub>I(3V3_SUS)</sub> | Input voltage                     |                                                                                                  |       | 3.3 |     | V    |

| \ /                     | Output voltage                    | See (2)                                                                                          | 0.875 | 1.8 | 3.1 | V    |

| $V_{O(AUX2\_OUT)}$      | Output accuracy                   | $V_{I(3V3\_SUS)} - V_{O(AUX2\_OUT)} > 200 \text{ mV}$                                            | -2%   |     | 2%  |      |

|                         | Dropout voltage                   | $V_{3V3\_SUS} = 0.975 \text{ x } V_{OUT(NOM)},$ $I_{OUT} = 50 \text{ mA}$                        |       | 100 | 150 | mV   |

|                         | Load regulation                   | 0 mA ≤ lout ≤ 50 mA                                                                              |       |     | 15  | mV   |

|                         | Line regulation                   | $V_{OUT(NOM)} + 0.3 \text{ V} \le V_{3V3\_VDD} \le 3.63 \text{ V},$<br>$I_{OUT} = 10 \text{ mA}$ |       |     | 5   | mV   |

| I <sub>max</sub>        | Max output current                |                                                                                                  |       |     | 80  | mA   |

| PSRR                    | Down cumply rejection retio       | f = 1 kHz, V <sub>I</sub> = 3.3 V, V <sub>O</sub> = 1.8 V, I <sub>OUT</sub> = 0.75*50 mA         | 50    | 53  |     | dB   |

| PSRR                    | Power supply rejection ratio      | $f = 10 \text{ kHz}, V_1 = 3.3 \text{ V}, V_0 = 1.8 \text{ V}, I_{OUT} = 0.75*50 \text{ mA}$     | 30    | 38  |     | dB   |

| V <sub>SHORT</sub>      | Output short detection comparator | V <sub>O(AUX2_OUT)</sub> < V <sub>SHORT</sub> for greater than 10 ms                             |       | 0.5 |     | V    |

| T <sub>start</sub>      | Startup time                      | $C_{OUT} = 1.0 \mu F$ , Vout from 0 V to 1.8 V                                                   |       | 100 |     | μs   |

| R <sub>DIS</sub>        | Discharge resistor in power down  |                                                                                                  |       | 100 | 200 | Ω    |

| C <sub>OUT</sub>        | Output capacitance                |                                                                                                  | 0.5   | 1.0 | 1.3 | μF   |

| LDO_IO                  |                                   |                                                                                                  |       |     |     |      |

| $V_{I(3V3\_VDD)}$       | Input voltage                     |                                                                                                  |       | 3.3 |     | V    |

| V                       | Output voltage                    | See (2) and (3)                                                                                  | 1.6   | 1.8 | 3.1 | V    |

| $V_{O(IO\_OUT)}$        | Output DC accuracy                | $V_{I(3V3\_VDD)} - V_{O(IO\_OUT)} > 200 \text{ mV}$                                              | -2%   |     | 2%  |      |

|                         | Dropout voltage                   | $V_{3V3\_VDD} = 0.975 \times V_{OUT(NOM)}, I_{OUT} = 50 \text{ mA}$                              |       | 100 | 150 | mV   |

|                         | Load regulation                   | 0 mA ≤ I <sub>out</sub> ≤ 50 mA                                                                  |       |     | 15  | mV   |

|                         | Line regulation                   | $V_{OUT(NOM)} + 0.3 \text{ V} \le V_{3V3\_VDD} \le 3.63 \text{ V},$<br>$I_{OUT} = 10 \text{ mA}$ |       |     | 5   | mV   |

| I <sub>max</sub>        | Max output current                |                                                                                                  |       |     | 50  | mA   |

| DCDD                    | Davis a simply religion to the    | f = 1 kHz, V <sub>I</sub> = 3.3 V, V <sub>O</sub> = 1.8 V, I <sub>OUT</sub> = 0.75*50 mA         | 50    | 56  |     | dB   |

| PSRR                    | Power supply rejection ratio      | f = 10 kHz, V <sub>I</sub> = 3.3 V, V <sub>O</sub> = 1.8 V, I <sub>OUT</sub> = 0.75*50 mA        | 30    | 38  |     | dB   |

| V <sub>SHORT</sub>      | Output short detection comparator | V <sub>O(IO_OUT)</sub> < V <sub>SHORT</sub> for greater than 10 ms                               |       | 0.5 |     | V    |

| T <sub>start</sub>      | Startup time                      | C <sub>OUT</sub> = 1.0 μF, Vout from 0 V to 1.8 V                                                |       | 100 |     | μs   |

| R <sub>DIS</sub>        | Discharge resistor in power down  |                                                                                                  |       | 100 | 200 | Ω    |

| C <sub>OUT</sub>        | Output capacitance                |                                                                                                  | 0.5   | 1.0 | 1.3 | μF   |

<sup>(3)</sup> LDO\_IO should never be set below 1.6 V, otherwise I<sup>2</sup>C communication is not functional.

Over recommended free-air temperature and over recommended input voltage (typical at an ambient temperature range of 27°C ) (unless otherwise noted)

|                         | PARAMETER                         | TEST CONDITIONS                                                                                  | MIN   | TYP | MAX  | UNIT |

|-------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------|-------|-----|------|------|

| LDO_S_IO                |                                   |                                                                                                  |       |     |      |      |

| V <sub>I(3V3_VDD)</sub> | Input Voltage                     |                                                                                                  |       | 3.3 |      | V    |

|                         | Output voltage                    | See (2)                                                                                          | 0.875 | 1.8 | 3.1  | V    |

| $V_{O(S\_IO\_OUT)}$     | Output DC accuracy                | $V_{I(3V3\_VDD)} - V_{O(S\_IO\_OUT)} > 200 \text{ mV}$                                           | -2%   |     | 2%   |      |

|                         | Dropout voltage                   | $V_{3V3\_VDD} = 0.975 \text{ x } V_{OUT(NOM)}, I_{OUT} = 150 \text{ mA}$                         |       | 100 | 150  | mV   |

|                         | Load regulation                   | 0 mA ≤ lout ≤ 150 mA                                                                             |       |     | 15   | mV   |

|                         | Line regulation                   | $V_{OUT(NOM)} + 0.3 \text{ V} \le V_{3V3\_VDD} \le 3.63 \text{ V},$<br>$I_{OUT} = 10 \text{ mA}$ |       |     | 5    | mV   |

| I <sub>max</sub>        | Max output current                |                                                                                                  |       |     | 150  | mA   |

| PSRR                    | Power supply rejection ratio      | $f = 1 \text{ kHz}, V_I = 3.3 \text{ V}, V_O = 1.8 \text{ V}, I_{OUT} = 0.75*150 \text{ mA}$     | 50    | 53  |      | dB   |

| FSKK                    | rower supply rejection ratio      | $f = 10 \text{ kHz}, V_I = 3.3 \text{ V}, V_O = 1.8 \text{ V}, I_{OUT} = 0.75*150 \text{ mA}$    | 30    | 38  |      | dB   |

| $V_{SHORT}$             | Output short detection comparator | V <sub>O(S_IO_OUT)</sub> < V <sub>SHORT</sub> for greater than 10 ms                             |       | 0.5 |      | V    |

| T <sub>start</sub>      | Startup time                      | $C_{OUT} = 1.0 \mu F$ , Vout from 0 V to 1.8 V                                                   |       | 100 |      | ms   |

| R <sub>DIS</sub>        | Discharge resistor in power down  |                                                                                                  |       | 100 | 200  | Ω    |

| C <sub>OUT</sub>        | Output capacitance                |                                                                                                  | 0.5   | 1.0 | 1.3  | μF   |

| LDO_PLL (Fo             | or Internal Use Only)             |                                                                                                  |       |     |      |      |

| V <sub>I(3V3_VDD)</sub> | Input voltage                     |                                                                                                  |       | 3.3 |      | V    |

| $V_{O(PLL\_VDD)}$       | Output voltage                    | See (2)                                                                                          | 2.55  | 2.7 | 2.75 | V    |

|                         | Output DC accuracy                | $V_{I(3V3\_VDD)} - V_{O(PLL\_VDD)} > 200 \text{ mV}$                                             | -2%   |     | 2%   |      |

|                         | Dropout voltage                   | $V_{3V3\_VDD} = 0.975 \times V_{OUT(NOM)}, I_{OUT} = 50 \text{ mA}$                              |       | 150 | 200  | mV   |

|                         | Load regulation                   | 0 mA ≤ lout ≤ 50 mA                                                                              |       |     | 15   | mV   |

|                         | Line regulation                   | $V_{OUT(NOM)} + 0.3 \text{ V} \le V_{3V3\_VDD} \le 3.63 \text{ V},$<br>$I_{OUT} = 10 \text{ mA}$ |       |     | 5    | mV   |

| I <sub>max</sub>        | Max output current                |                                                                                                  |       |     | 50   | mA   |

| DCDD                    | Dougs cumply rejection ratio      | f = 1 kHz, V <sub>I</sub> = 3.3 V, V <sub>O</sub> = 2.7 V, I <sub>OUT</sub> = 0.75*50 mA         | 50    | 57  |      | dB   |

| PSRR                    | Power supply rejection ratio      | $f = 10 \text{ kHz}, V_I = 3.3 \text{ V}, V_O = 2.7 \text{ V}, I_{OUT} = 0.75*50 \text{ mA}$     | 30    | 40  |      | dB   |

| $V_{SHORT}$             | Output short detection comparator | V <sub>O(PLL_VDD)</sub> < V <sub>SHORT</sub> for greater than 10 ms                              |       | 0.5 |      | V    |

| T <sub>start</sub>      | Startup time                      | $C_{OUT}$ = 1.0 $\mu$ F, Vout from 0 V to 2.7 V                                                  |       | 100 |      | μs   |

| R <sub>DIS</sub>        | Discharge resistor in power down  |                                                                                                  |       | 100 | 200  | Ω    |

| C <sub>OUT</sub>        | Output capacitance                |                                                                                                  | 0.5   | 1.0 | 1.3  | μF   |

Over recommended free-air temperature and over recommended input voltage (typical at an ambient temperature range of  $27^{\circ}$ C ) (unless otherwise noted)

|                              | PARAMETER                             | TEST CONDITIONS                                                                        | MIN                           | TYP | MAX                                   | UNIT |

|------------------------------|---------------------------------------|----------------------------------------------------------------------------------------|-------------------------------|-----|---------------------------------------|------|

| CLOCK GENE                   | ERATION                               |                                                                                        |                               |     |                                       |      |

| f <sub>XTAL</sub>            | External reference clock              |                                                                                        | 3                             | 24  | 27                                    | MHz  |

| tstart                       | PLL start-up time                     | With FL2000044 crystal to 0.1% accuracy of the target frequency                        |                               | 1   |                                       | ms   |

| XTAL ESR                     |                                       |                                                                                        | 50                            |     | 150                                   | Ω    |

| ,                            | Output alout                          | minimum programmable frequency                                                         | 3.8                           | 4   | 4.2                                   | MHz  |

| f <sub>HCLK</sub>            | Output clock                          | maximum programmable frequency                                                         | 63.8                          | 64  | 64.2                                  | MHz  |

| D <sub>HCLK</sub>            | HCLKx duty cycle driven by PLL output |                                                                                        | 45%                           |     | 55%                                   |      |

| trise                        | HCLKx rise time                       | Measured from 10% to 90%, DRV_STR_x[1:0] = 2 mA                                        |                               | 2   | 5                                     | ns   |

| t <sub>fall</sub>            | HCLKx fall time                       | Measured from 90% to 10%, DRV_STR_x[1:0] = 2 mA                                        |                               | 2   | 5                                     | ns   |

| Т                            | HCLKx jitter                          | 3σ cycle-to-cycle. Greater than 1000 cycles. Difference between two consecutive cycles |                               |     | 600                                   | ps   |

| 0                            | HCLKx load                            | maximum load capacitance for frequencies between 4 MHz and 32 MHz                      |                               |     | 10                                    | ~F   |

| C <sub>load</sub> HCLKx load |                                       | maximum load capacitance for frequencies up to 64 MHz                                  |                               |     | 5                                     | pF   |

| V <sub>OH</sub>              | HCLKx output high voltage             | I <sub>OH</sub> = 8 mA                                                                 | 0.7*V <sub>S_IO</sub><br>_OUT |     |                                       | V    |

| $V_{OL}$                     | HCLKx output low voltage              | I <sub>OL</sub> = 8 mA                                                                 |                               |     | 0.2*<br>V <sub>S_I</sub><br>O_OU<br>T | V    |

| THERMAL SH                   | IUTDOWN                               |                                                                                        |                               |     | •                                     |      |

|                              | WILED DOOCT the arread about decision | Trip temperature                                                                       | 140                           | 160 |                                       | °C   |

|                              | WLED BOOST thermal shutdown           | Hysteresis                                                                             |                               | 20  |                                       | ٦.   |

|                              | Cons hard, the arread about decree    | Trip temperature                                                                       | 140                           | 160 |                                       | •••  |

|                              | Core buck thermal shutdown            | Hysteresis                                                                             |                               | 20  |                                       | °C   |

|                              | LDC thermal shutdown                  | Trip temperature                                                                       | 140                           | 160 |                                       | °C   |

|                              | LDO thermal shutdown                  | Hysteresis                                                                             |                               | 20  |                                       |      |

| OSCILLATOR                   | (for digital core)                    |                                                                                        |                               | -   |                                       |      |

| fosc                         | Oscillator frequency                  |                                                                                        | 1.8                           | 2   | 2.2                                   | MH   |

| S_VSYNC                      |                                       |                                                                                        |                               |     | ·                                     |      |

| V <sub>IH</sub>              | Input high level                      |                                                                                        | 1.0                           |     |                                       | V    |

| V <sub>IL</sub>              | Input low level                       |                                                                                        |                               |     | 0.4                                   | V    |

| R <sub>PD</sub> (S_VSYNC)    | S_VSYNC internal pull-down            | Only present when V <sub>S_VSYNC</sub> is below V <sub>IL</sub> threshold              | 5                             | 10  |                                       | kΩ   |

Over recommended free-air temperature and over recommended input voltage (typical at an ambient temperature range of 27°C) (unless otherwise noted)

|                                             | PARAMETER                                                       | TEST CONDITIONS                                                                             | MIN                   | TYP   | MAX                                   | UNIT      |

|---------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------|-------|---------------------------------------|-----------|

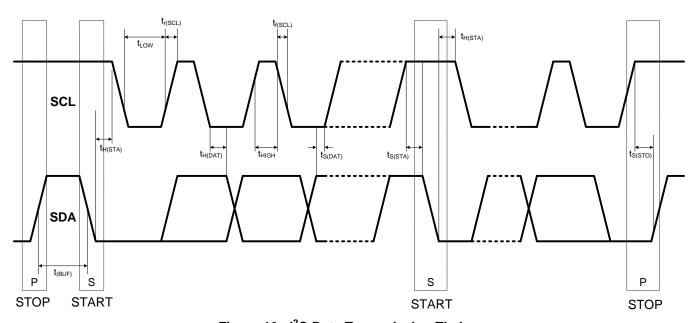

| I <sup>2</sup> C I/Os (SD/                  | A, SCL) (IO_OUT voltage)                                        |                                                                                             |                       |       |                                       |           |

| I <sub>LK</sub>                             | Input leakage current                                           | Clamped to GND or 3.3 V                                                                     | -1                    |       | 1                                     | μA        |

| V <sub>IH</sub>                             | Input high level                                                |                                                                                             | 0.7*V <sub>IO_O</sub> |       |                                       | V         |

| VIH                                         | input night level                                               |                                                                                             | UT                    |       |                                       | v         |

| $V_{IL}$                                    | Input low level                                                 |                                                                                             |                       |       | 0.3*<br>V <sub>IO</sub>               | V         |

| V IL                                        | input low level                                                 |                                                                                             |                       |       | OUT                                   | V         |

|                                             |                                                                 |                                                                                             |                       |       | 0.2*                                  |           |

| V <sub>OL(SDA)</sub> Output low level (SDA) |                                                                 | I <sub>OL</sub> = 3 mA                                                                      |                       |       | V <sub>IO</sub> _                     | V         |

| f <sub>SCL</sub>                            | I <sup>2</sup> C clock frequency                                |                                                                                             |                       |       | 0UT<br>400                            | kHz       |

|                                             | 00, GPIO1, GPIO2, GPIO3,GPIO4,GPIO                              | 5 and GPIO6)                                                                                |                       |       | 100                                   |           |

| V <sub>IH</sub>                             | Input high level                                                | Configured as Input                                                                         | 1.2                   |       |                                       | V         |

| V <sub>IL</sub>                             | Input low level                                                 | Configured as Input                                                                         |                       |       | 0.4                                   | V         |

| I <sub>LK</sub>                             | Input leakage current                                           | Configured as input, clamped to GND or 3.3 V                                                | -1                    |       | 1                                     | μA        |

| V <sub>OH_PP</sub>                          | Output high level for push-pull                                 | $V_{O(IO\_OUT)} = 1.8 \text{ V or } V_{I(3V3\_SUS)} = 3.3 \text{ V}, I_{OH} = 8$            | 0.8*VDD               |       |                                       | V         |

| VOH_PP                                      | configuration                                                   | mA                                                                                          | 0.0 VDD               |       |                                       | V         |

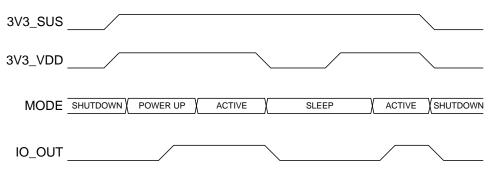

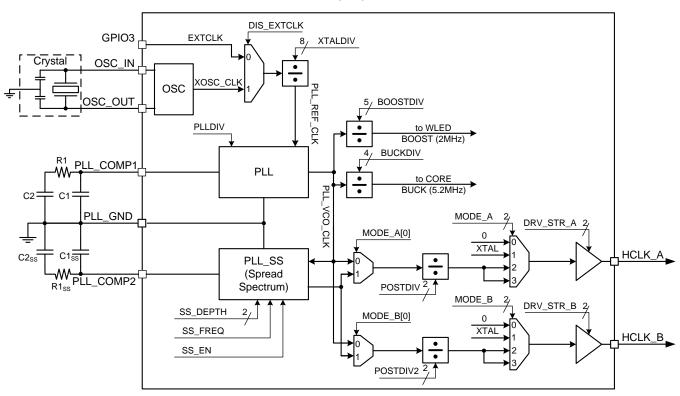

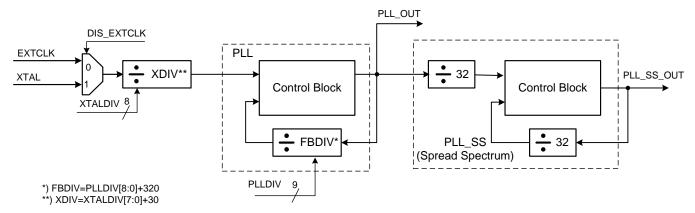

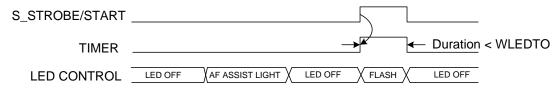

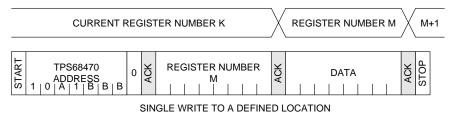

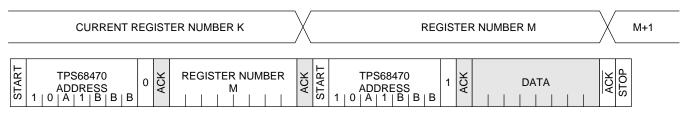

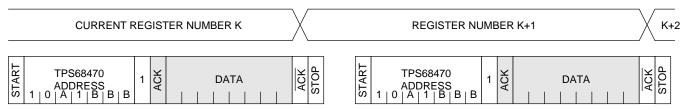

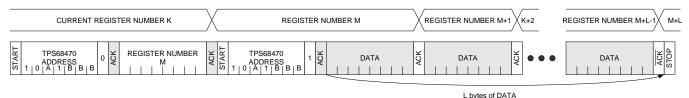

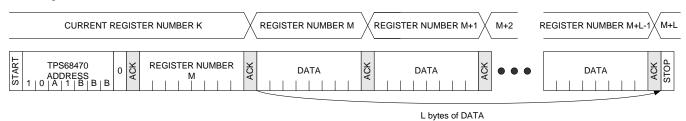

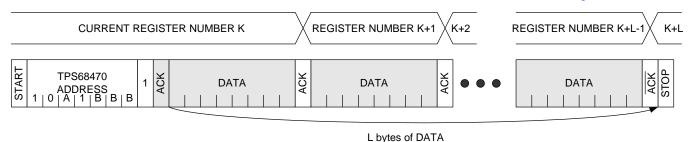

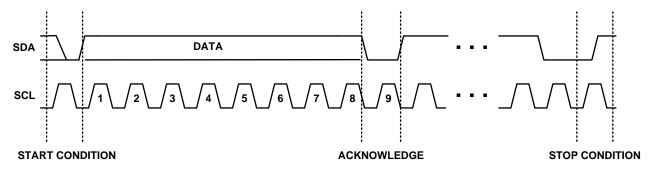

| V <sub>OL_PP</sub>                          | Output low level for push-pull configuration                    | $V_{O(IO\_OUT)} = 1.8 \text{ V or } V_{I(3V3\_SUS)} = 3.3 \text{ V}, I_{OL} = 8 \text{ mA}$ |                       |       | 0.2*<br>VDD                           | V         |