ZHCS863A - MAY 2012 - REVISED AUGUST 2013

# 具有自动检测和插槽专用双通道低压降稳压器 (LDO) 的 双电源 2:1 智能身份模块 (SIM) 卡复用器/转换器

查询样品: TXS02326A

### 特性

- 电平转换器

- VDDIO 范围介于 1.7V 至 3.3V 之间

- 低压降 (LDO) 稳压器

- 带有使能的 50mA LDO 稳压器

- 1.8V 至 2.95V 可选输出电压

- 2.3V 至 5.5V 输入电压范围

- 极低压降:电流为 50mA 时为 100mV (最大值)

- 通过配有基带处理器的 I<sup>2</sup>C 接口实现控制和通信

- 静电放电 (ESD) 保护性能超过 JESD 22 规范要求

- 2500V 人体模型 (A114-B)

- VSIM1, SIM1CLK, SIM1I/O, SIM1RST, VS IM2, SIM2CLK, SIM2I/O, SIM2RST 上的 6000V 人体模型 (A114-B)

- 1000V 充电器件模型 (C101)

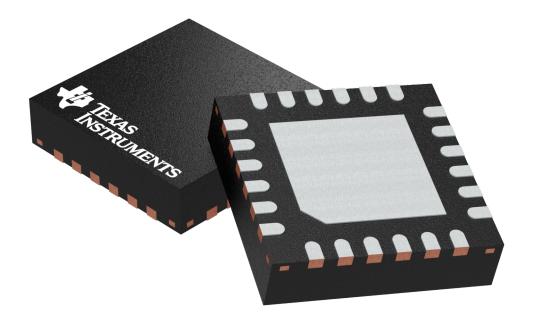

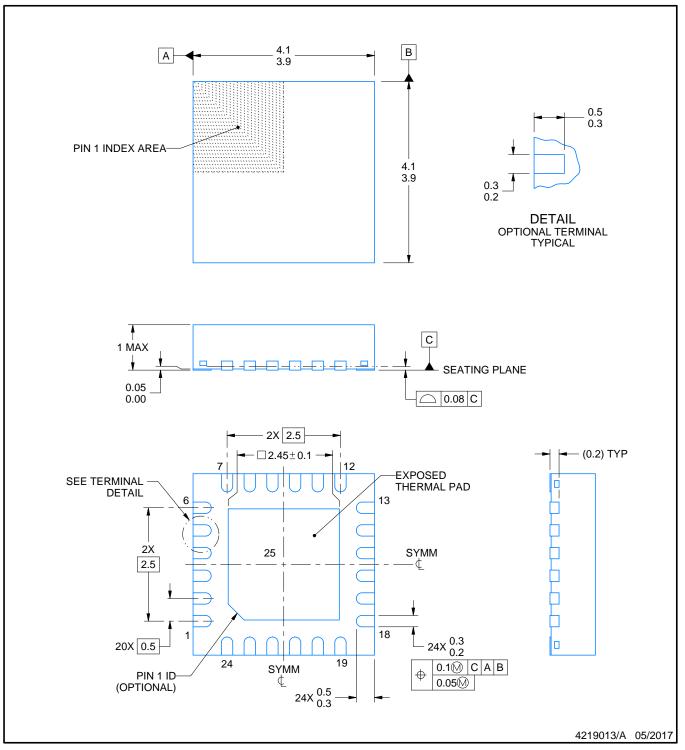

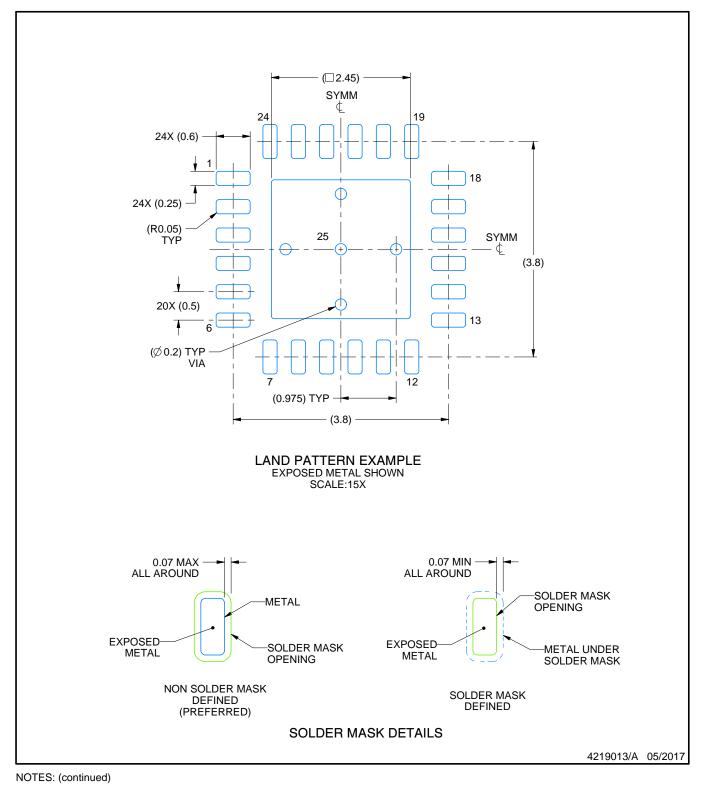

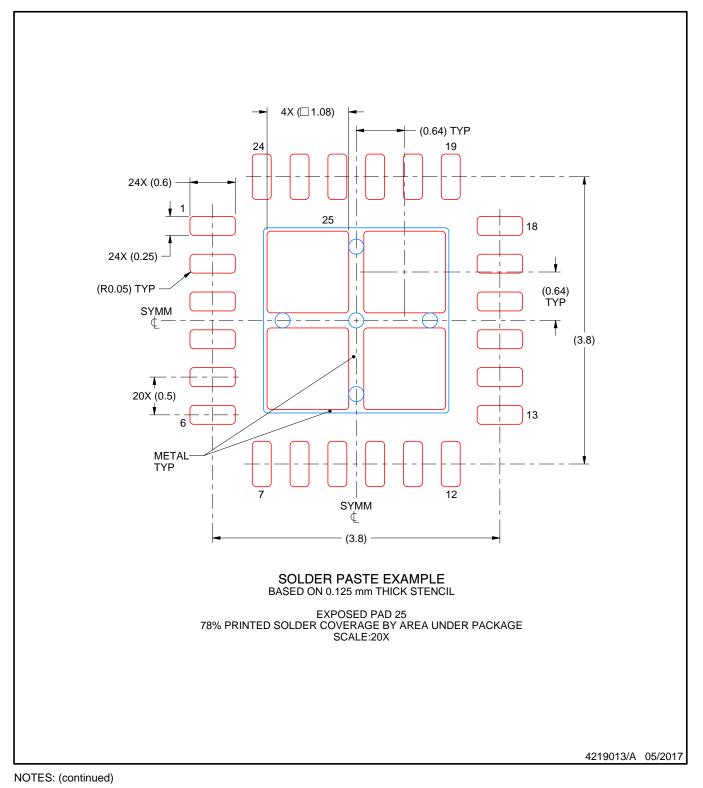

- 封装

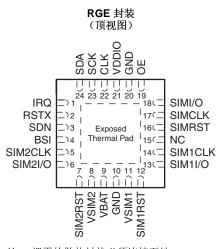

- 24 引脚四方扁平无引线封装 (QFN) (4mm x 4mm)

### 说明/订购信息

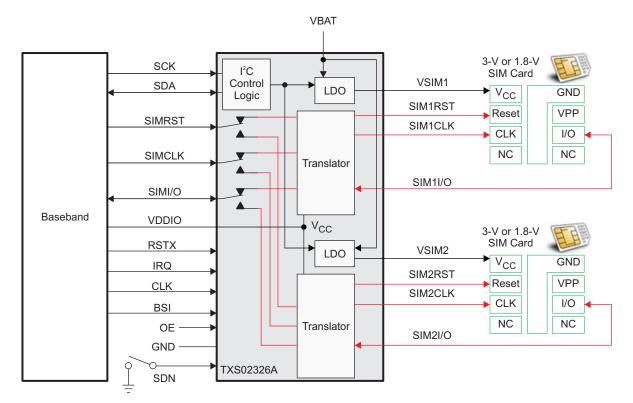

TXS02326A 是一款完全双电源待机智能身份模块 (SIM) 卡解决方案,此解决方案用于将无线基带处理器与两个单独的 SIM 用户卡接口相连,以存储移动手机应用程序的数据。 它是一个用于将一个单一 SIM/UICC 接口拓展成为 支持两个 SIM/UICC 接口的定制器件。

该器件不但符合 ISO/IEC 智能卡接口要求,而且还支持 GSM 与 3G 移动标准。 它包括一个能够支持 B 类 (2.95V) 和 C 类 (1.8V) 接口的高速电平转换器;两个具有可在 2.95V B 类和 1.8V C 类接口之间选择输出电压的低压降 (LDO) 稳压器;一个用于配置的集成型 "快速模式" 400kb/s "从" I<sup>2</sup>C 控制寄存器接口;和一个用于内部定时生成的 32kHz 时钟输入。 为了对两个 SIM 卡安全断电,TXS02326A 还包括一个关断输入和一个可检测电池组取出的比 较器输入。 关断输入和比较器输入装有两个由一个 8 位计数器实现的可编程防反跳计数器(即电池拆除关断保护 引脚 (BSI) 输入和备用 SIM 卡热交换引脚 (SDN) 输入)电路。

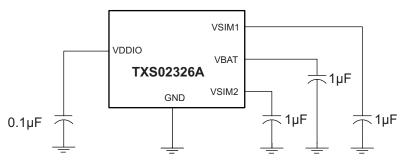

电压电平转换器具有两个电源电压引脚。 VDDIO 设定针对基带接口的基准并可在 1.7V 至 3.3V 的电压下运行。 VSIM1 和 VSIM2 的电压可被设定为 1.8V 或者 2.95V,均由一个独立内部 LDO 稳压器供电。 集成型 LDO 可接受 2.3V 至 5.5V 的输入电池电压,并向 B 侧电路及外部 B 类或 C 类 SIM 卡输出高达 50mA 的电流。

#### 订购信息

要获得最新封装和订购信息,请参阅本文档末尾的封装选项附录。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

注: 裸露的散热衬垫必须连接至地。

# TXS02326A

Texas Instruments

#### ZHCS863A-MAY 2012-REVISED AUGUST 2013

www.ti.com.cn

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

Figure 1. Interfacing With SIM Card

Texas

| NO. | NAME    | TYPE <sup>(1)</sup> | POWER<br>DOMAIN | DESCRIPTION                                                              |  |

|-----|---------|---------------------|-----------------|--------------------------------------------------------------------------|--|

| 1   | IRQ     | I/O                 | VDDIO           | Interrupt to baseband. This signal is used to set the I2C address.       |  |

| 2   | RSTX    | I                   | VDDIO           | Active-low reset input from baseband                                     |  |

| 3   | SDN     | I                   | VDDIO           | Power down SIM2; for example, from switch                                |  |

| 4   | BSI     | I                   | VDDIO           | Analog signal from battery. This input accepts input voltages up to 3 V. |  |

| 5   | SIM2CLK | 0                   | VSIM2           | SIM2 clock                                                               |  |

| 6   | SIM2I/O | I/O                 | VSIM2           | SIM2 data                                                                |  |

| 7   | SIM2RST | 0                   | VSIM2           | SIM2 reset                                                               |  |

| 8   | VSIM2   | 0                   | VSIM2           | 1.8 V/2.95 V supply voltage to SIM2                                      |  |

| 9   | VBAT    | Р                   | VBAT            | Battery power supply                                                     |  |

| 10  | GND     | G                   |                 | Ground                                                                   |  |

| 11  | VSIM1   | 0                   | VSIM1           | 1.8 V/2.95 V supply voltage to SIM1                                      |  |

| 12  | SIM1RST | 0                   | VSIM1           | SIM1 reset                                                               |  |

| 13  | SIM1I/O | I/O                 | VSIM1           | SIM1 data                                                                |  |

| 14  | SIM1CLK | 0                   | VSIM1           | SIM1 clock                                                               |  |

| 15  | NC      |                     |                 | No connect                                                               |  |

| 16  | SIMRST  | I                   | VDDIO           | UICC/SIM reset from baseband                                             |  |

| 17  | SIMCLK  | I                   | VDDIO           | UICC/SIM clock                                                           |  |

| 18  | SIMI/O  | I/O                 | VDDIO           | UICC/SIM data                                                            |  |

| 19  | OE      | I                   | VDDIO           | UICC/SIM data direction from baseband                                    |  |

| 20  | GND     | G                   |                 |                                                                          |  |

| 21  | VDDIO   | Р                   | VDDIO           | 1.8-V power supply for device operation and I/O buffers toward baseband  |  |

| 22  | CLK     | I                   | VDDIO           | 32-kHz clock                                                             |  |

| 23  | SCK     | Ι                   | VDDIO           | I <sup>2</sup> C clock                                                   |  |

| 24  | SDA     | I/O                 | VDDIO           | I <sup>2</sup> C data                                                    |  |

(1) G = Ground, I = Input, O = Output, P = Power

ZHCS863A - MAY 2012 - REVISED AUGUST 2013

# **TERMINAL FUNCTIONS**

#### ZHCS863A - MAY 2012 - REVISED AUGUST 2013

www.ti.com.cn

|                                                     |                                                                 |                                        |                                         | Ia                                  |                                                       | gister O                          |                                      |                                         |                                               |                     |                     |

|-----------------------------------------------------|-----------------------------------------------------------------|----------------------------------------|-----------------------------------------|-------------------------------------|-------------------------------------------------------|-----------------------------------|--------------------------------------|-----------------------------------------|-----------------------------------------------|---------------------|---------------------|

| B7                                                  | B6                                                              | В5                                     | REGISTE<br>B4                           | ER BITS<br>B3                       | B2                                                    | B1                                | B0                                   | COMMAND<br>BYTE                         | REGISTER                                      | READ<br>OR<br>WRITE | POWER-UP<br>DEFAULT |

| 0                                                   | 0                                                               | 0                                      | 1                                       | 0                                   | 0                                                     | 1                                 | 0                                    | (HEX)<br>00h                            | Device<br>hardware<br>revision<br>information | R                   | 0001 0010           |

| 0                                                   | 0                                                               | 0                                      | 0                                       | 0                                   | 0                                                     | 0                                 | 0                                    | 01h                                     | Software<br>revision<br>information           | R                   | 0000 0000           |

| SIM2 Interface SIM1 Interface Removal Battery Inter |                                                                 |                                        |                                         |                                     |                                                       | SDN<br>Interrupt<br>Status        | SDN<br>Status                        | 04h                                     | Status<br>Register                            | R                   | 0000 0000           |

|                                                     | SIM2 Interface<br>Status SIM2 SIM2 LDO<br>Select Disable Status |                                        |                                         |                                     | SIM1<br>Voltage<br>Select                             | SIM1<br>LDO<br>Enable/<br>Disable | 08h                                  | SIM<br>Interface<br>Control<br>Register | R/W                                           | 0000 0000           |                     |

|                                                     |                                                                 | BSI                                    | Debounce                                | Counter Va                          | lue                                                   |                                   |                                      | 0Ah                                     | BSI Input<br>Debounce<br>Counter              | R/W                 | 0000 0100           |

|                                                     |                                                                 | SDN                                    | l Debounce                              | Counter Va                          | llue                                                  |                                   |                                      | 0Bh                                     | SDN Input<br>Debounce<br>Counter              | R/W                 | 0000 0100           |

|                                                     |                                                                 | Re                                     | eserved / N                             | ot Supporte                         | d                                                     |                                   |                                      | 0Ch                                     | Reserved                                      | R/W                 | 0000 0000           |

| Clock<br>Source<br>Select                           |                                                                 |                                        | Clock C                                 | Control (Res                        | erved)                                                |                                   |                                      | 0Dh                                     | External<br>Clock<br>Control                  | R/W                 | 0000 0000           |

| SDN<br>Detection<br>Behavior<br>control             | SDN<br>Level<br>Detection<br>Select                             | SDN<br>Interrupt<br>Enable/<br>Disable | BSI<br>Detection<br>Behavior<br>Control | BSI<br>Level<br>Detection<br>Select | Battery<br>Removal<br>Interrupt<br>Enable/<br>Disable | OE<br>Direction<br>Control        | OE<br>Control<br>Select              | 0Eh                                     | Device<br>Control<br>Register                 | R/W                 | 0000 0000           |

|                                                     |                                                                 |                                        |                                         |                                     |                                                       |                                   |                                      | 10h-14h                                 | Device-<br>specific<br>testing                | R/W                 | xxxx xxxx           |

|                                                     | Reserved                                                        |                                        |                                         |                                     |                                                       |                                   | SDN<br>Pull-up<br>Enable/<br>Disable | 15h                                     | General<br>purpose                            | R/W                 | 0000 0000           |

#### Table 1. Register Overview

#### ZHCS863A - MAY 2012 - REVISED AUGUST 2013

#### www.ti.com.cn

Table 2. Device Hardware Revision Register (00h)

| Device HW Driver<br>Register | Bits(s) | Type (R/W) | Description                                                                                               |

|------------------------------|---------|------------|-----------------------------------------------------------------------------------------------------------|

| HW identification            | 7:0     | R          | This register contains the manufacturer and device $ID^{(1)}$ (value to be specified by the manufacturer) |

(1) The manufacturer ID part of this data shall remain unchanged when the HW revision ID is updated. The manufacturer ID shall uniquely identify the manufacturer. The manufacturer ID is encoded on the MSB nibble.

#### Table 3. Device Software Revision Register (01h)

| Device SW Driver<br>Register | Bits(s) | Type (R/W) | Description                                                                                                                                                                                                 |

|------------------------------|---------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW Driver Version            | 7:0     | R          | This register contains information about the SW driver required for this device. This information shall only be updated when changes to the device requires SW modifications. Initial register value is 00h |

#### Table 4. Status Register (04h)

| Status Register                                  | Bits(s)            | Type (R/W) | Description                                                                                                                                                                                               |

|--------------------------------------------------|--------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDN Status                                       | 0                  | R          | SDN signal state captured at the input pin<br>'0' SDN signal at GND<br>'1' SDN signal at VDDIO level                                                                                                      |

| SDN Interrupt 1 R                                |                    | R          | SDN interrupt status<br>'0' No interrupt<br>'1' Interrupt occurred, (the read operation will automatically clear this bit)                                                                                |

| Battery Status 2 R                               |                    | R          | '0' Battery present<br>'1' Battery not present, i.e. debounce counter expired                                                                                                                             |

| Battery Removal Interrupt 3                      |                    | R          | Battery removal interrupt status<br>'0' No interrupt<br>'1' Interrupt occurred, (the read operation will automatically clear this bit)                                                                    |

| SIM1 Interface Status [1:0] 5:4 <sup>(1)</sup> F |                    | R          | Status of SIM1 interface<br>'00' Powered down with pull-downs activated<br>'01' Isolated with pull-downs deactivated<br>'10' Powered with pull downs activated<br>'11' Active with pull downs deactivated |

| SIM2 Interface Status [1:0]                      | 7:6 <sup>(1)</sup> | R          | Status of SIM2 interface<br>'00' Powered down with pull-downs activated<br>'01' Isolated with pull-downs deactivated<br>'10' Powered with pull downs activated<br>'11' Active with pull downs deactivated |

(1) The content of bits 5:4 and 7:6 reflects the value written to the state bits in the SIM Interface control register 3:2 and 7:6 respectively and the setting of the regulator bits in the SIM interface control register 0 and 4 respectively.

#### Table 5. State and Status Bit Mapping

| SIM Interface Control Register<br>(08h)<br>SIM1 interface state bits 3:2<br>SIM2 interface state bits 7:6 | h) (08h)<br>I1 interface state bits 3:2 SIM1 regulator control bit 0 |                                             | Comment                                                                                    |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------|

| '00' Powered down state with pull-<br>downs activated                                                     | '0' Regulator is off, regulator output is pulled down                | '00' Powered down with pulldowns activated  |                                                                                            |

| '00' Powered down state with pull-<br>downs activated                                                     | '1' Regulator is powered on, regulator output pull-down is released  | '10' Powered with totem pole pull-<br>downs |                                                                                            |

| '01' Isolated state with pulldowns deactivated                                                            | '0' Regulator is off, regulator output is pulled down                | '00' Powered down with pulldowns activated  | The interface can<br>only be in isolated<br>state when the<br>interface is powered         |

| '01' Isolated state with pulldowns deactivated                                                            | '1' Regulator is powered on, regulator output pull-down is released  | '01' Isolated with pull-downs deactivated   |                                                                                            |

| '10' Not allowed                                                                                          | '0' Regulator is off, regulator output is pulled down                | '00' Powered down with pulldowns activated  | This combination<br>shall not be used. If<br>used the status bit<br>coding is as specified |

#### TEXAS INSTRUMENTS

www.ti.com.cn

#### ZHCS863A - MAY 2012 - REVISED AUGUST 2013

|                                                                                                           |                                                                                                         | · · · · · · · · · · · · · · · · · · ·                                     |                                                                                            |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

| SIM Interface Control Register<br>(08h)<br>SIM1 interface state bits 3:2<br>SIM2 interface state bits 7:6 | SIM Interface Control Register<br>(08h)<br>SIM1 regulator control bit 0<br>SIM2 regulator control bit 4 | SIM Status Register (04h)<br>SIM1 status bits 5:4<br>SIM2 status bits 7:6 | Comment                                                                                    |  |  |  |  |  |

| '10' Not allowed                                                                                          | '1' Regulator is powered on, regulator output pull-down is released                                     | '10' Powered with pull downs activated                                    | This combination<br>shall not be used. If<br>used the status bit<br>coding is as specified |  |  |  |  |  |

| '11' Active state with pull-downs deactivated                                                             | '0' Regulator is off, regulator output is pulled down                                                   | '00' Powered down with pulldowns activated                                | The interface can<br>only be active if it is<br>powered                                    |  |  |  |  |  |

| '11' Active state with pull-downs deactivated                                                             | '1' Regulator is powered on, regulator output pull-down is released                                     | '11' Active with pull-downs deactivated                                   |                                                                                            |  |  |  |  |  |

#### Table 5. State and Status Bit Mapping (continued)

# Table 6. SIM Interface Control Register (08h)<sup>(1) (2)</sup>

| Status<br>Register                        | Bit(s) | Type<br>(R/W) | Description                                                                                                                  |                                                                 |  |  |  |  |

|-------------------------------------------|--------|---------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|

| SIM1<br>Regulator<br>Control              | 0      | R/W           | '0' Regulator is off, regulator output is pulled down<br>'1' Regulator is powered on, regulator output pull-down is released |                                                                 |  |  |  |  |

| SIM1<br>Regulator<br>Voltage<br>Selection | 1      | R/W           | 0' 1.8 V<br>1' 2.95 V                                                                                                        |                                                                 |  |  |  |  |

|                                           |        |               | Status of SIM1 interface                                                                                                     |                                                                 |  |  |  |  |

|                                           |        |               | '00' state is dependent on bit 0:                                                                                            |                                                                 |  |  |  |  |

|                                           |        |               | If bit $0 = 0^{\circ}$ , then powered down state with pull-downs activated                                                   | Pull down resistor active                                       |  |  |  |  |

| SIM1<br>Interface                         | 3:2    | R/W           | If bit 0 = '1', then isolated state with pull-downs deactivated                                                              | Totem pole pull down                                            |  |  |  |  |

| State [1:0]                               |        | 0.2           | '01' Isolated state with pull-downs deactivated                                                                              | Output latched at previous state driven<br>by totem pole output |  |  |  |  |

|                                           |        |               | '10' Not allowed                                                                                                             | Not allowed                                                     |  |  |  |  |

|                                           |        |               | '11' Active state with pull-downs deactivated                                                                                | Outputs follow the inputs                                       |  |  |  |  |

| SIM2<br>Regulator<br>Control              | 4      | R/W           | 0' Regulator is off, regulator output is pulled down<br>1' Regulator is powered on, regulator output pull-down is released   |                                                                 |  |  |  |  |

| SIM2<br>Regulator<br>Voltage<br>Selection | 5      | R/W           | '0' 1.8 V<br>'1' 2.95 V                                                                                                      |                                                                 |  |  |  |  |

|                                           |        |               | Status of SIM2 interface                                                                                                     |                                                                 |  |  |  |  |

|                                           |        |               | '00' State is dependent on bit 4:                                                                                            |                                                                 |  |  |  |  |

| o                                         |        |               | If bit 4 = '0', then powered down state with pull-downs activated                                                            | Pull down resistor active                                       |  |  |  |  |

| SIM2<br>Interface                         | 7:6    | R/W           | If bit 4 = '1', then isolated state with pull-downs deactivated                                                              | Totem pole pull down                                            |  |  |  |  |

| State [1:0]                               |        |               | '01' Isolated state with pull-downs deactivated                                                                              | Output latched at previous state driven<br>by totem pole output |  |  |  |  |

|                                           |        |               | '10' Not allowed                                                                                                             | Not allowed                                                     |  |  |  |  |

|                                           |        |               | '11' Active state with pull-downs deactivated                                                                                | Outputs follow the inputs                                       |  |  |  |  |

(1) Reset value: 00h

(2) The state '10', on bits 3:2 and 7:6, is not prevented by HW but shall never be set by SW. State '10' means that the interface is powered with the pull-downs active, this state correspond to state '00' with the regulator being switched on. Setting the state to '10' does not have any impact on the corresponding regulator bit setting. The regulator control bits do not impact the state bits in this register. The regulator control bits however do impact the status bits in the status register.

# Table 7. Battery Presence Detection Debounce Counter (0Ah)<sup>(1) (2)</sup>

| BSI Debounce Counter            | Bits(s) | Type (R/W) | Description                                                                                                                      |

|---------------------------------|---------|------------|----------------------------------------------------------------------------------------------------------------------------------|

| Debounce Counter Value<br>[7:0] | 7:0     | R/W        | This register contains the BSI input debounce counter value. The value 00h means that the counter is not used, i.e. no debounce. |

(1) Reset value: 04h

(2) Updating the register causes the counter to restart with the new value if the counter is counting when the register is updated. The new value shall take affect no later than one clock cycle (32 KHz) after the register has been updated.

#### Table 8. SDN Input Debounce Counter (0Bh)<sup>(1) (2)</sup>

| SDN Debounce Counter            | Bits(s) | Type (R/W) | Description                                                                                                                      |

|---------------------------------|---------|------------|----------------------------------------------------------------------------------------------------------------------------------|

| Debounce Counter Value<br>[7:0] | 7:0     | R/W        | This register contains the SDN input debounce counter value. The value 00h means that the counter is not used, i.e. no debounce. |

(1) Reset value: 04h

(2) Updating the register causes the counter to restart with the new value if the counter is counting when the register is updated. The new value shall take affect no later than one clock cycle (32 KHz) after the register has been updated.

#### Table 9. External Clock Control (0Dh)<sup>(1)</sup>

| Clock Control Register | Bits(s) | Type (R/W) | Description                                                                               |

|------------------------|---------|------------|-------------------------------------------------------------------------------------------|

| Clock Control          | 6:0     | R/W        | Reserved                                                                                  |

| Clock Source Select    | 7       | R/W        | '0' Internal clock source used<br>'1' External clock source CLK (supplied on pin 22 used) |

(1) Reset value: 00h

#### TEXAS INSTRUMENTS

www.ti.com.cn

#### ZHCS863A - MAY 2012 - REVISED AUGUST 2013

Table 10. Device Control Register (0Eh)<sup>(1)</sup>

| <b>Clock Control Register</b>                                          | Bits(s)          | Type (R/W)                                                                                                                                              | Description                                                                                                                                                                                                  |

|------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OE Control                                                             | DE Control 0 R/W |                                                                                                                                                         | <ul> <li>'0' OE is not used to control the data direction on the selected SIM I/O and the base band I/O</li> <li>'1' OE controls the data direction, see below</li> </ul>                                    |

| OE Direction Control                                                   | 1 R/W            |                                                                                                                                                         | '0' OE input = '0' data direction Base band -> SIM<br>OE input = '1' data direction SIM -> base band<br>'1' OE input = '0' data direction SIM -> base band<br>OE input = '1' data direction Base band -> SIM |

|                                                                        |                  | <sup>(0)</sup> Battery removal interrupt disabled<br>(1) Battery removal detected causes interrupt on IRQ (interrupt sets b3 in<br>the status register) |                                                                                                                                                                                                              |

| BSI Level Detection 3 R/W BSI detection level<br>'0' 1.2V<br>'1' 1.65V |                  | '0' 1.2V                                                                                                                                                |                                                                                                                                                                                                              |

| BSI Detection Control 4 R/W                                            |                  | R/W                                                                                                                                                     | BSI detection behavior<br>'0' Battery not present causes automatic power down of both SIM<br>interfaces<br>'1' Battery not present doesn't cause automatic power down                                        |

| SDN Detection Interrupt 5 R/V                                          |                  | R/W                                                                                                                                                     | <sup>(0)</sup> SDN detection interrupt disabled<br>(1) SDN detected causes interrupt on IRQ (interrupt sets b1 in the status<br>register)                                                                    |

| SDN Detection Level 6 R/W                                              |                  | R/W                                                                                                                                                     | SDN input active level<br>'0' SDN is active low<br>i.e. automatic shutdown occurs when debounced SDN is low.<br>'1' SDN is active high<br>i.e. automatic shutdown occurs when debounced SDN is high          |

| SDN Detection Control                                                  | 7                | R/W                                                                                                                                                     | Disable automatic power down upon SDN detection<br>'0' SDN detection causes automatic power down of SIM2 interface<br>'1' SDN detection doesn't cause automatic power down of SIM2 interface                 |

(1) Reset value: 00h

# Table 11. General Purpose Register (15h)<sup>(1)</sup>

| Function              | Bit(s) | Type (R/W) | Description                                                     |

|-----------------------|--------|------------|-----------------------------------------------------------------|

| SDN pull-up control   | 0      | R/W        | '0' SDN input pull-up enabled<br>'1' SDN input pull-up disabled |

| SDN pull-down control | 1      | R/W        | '0' SDN pull-down disabled<br>'1' SDN pull-down enabled         |

| RFU                   | 7:2    | R/W        |                                                                 |

(1) The RFU bits shall allow for the write operation to complete but shall read as '0'. The SW should write '0' into these locations, reset value.

ZHCS863A - MAY 2012 - REVISED AUGUST 2013

### **BASIC DEVICE OPERATION**

The TXS02326A is controlled through a standard I<sup>2</sup>C interface reference to VDDIO. It is connected between the two SIM card slots and the SIM/UICC interface of the baseband. The device uses VBAT and VDDI/O as supply voltages. The supply voltage for each SIM card is generated by an on-chip low drop out regulator. The interface between the baseband and the TXS02326A is reference to VDDIO while the interface between the TXS02326A and the SIM card is referenced to the LDO output of either VSIM1 or VSIM2 depending on which slot is being selected. The VDDIO on the baseband side normally does not exceed 1.8V, thus voltage level shifting is needed to support a 3V SIM/UICC interface (Class B).

The TXS02326A has two basic states, the reset and operation state. The baseband utilizes information in the status registers to determine how to manipulate the control registers to properly switch between two SIM cards. These fundamental sequences are outlined below and are to help the user to successfully incorporate this device into the system.

#### DEVICE ADDRESS

The address of the device is shown below:

| • | • |   |   | Slave | Address | ; |     |     |  |

|---|---|---|---|-------|---------|---|-----|-----|--|

|   | 0 | 1 | 1 | 1     | 1       | 0 | IRQ | R/W |  |

Address Reference

| IRQ@ Reset | R/W   | Slave Address        |

|------------|-------|----------------------|

| 0          | 0 (W) | 120 (decimal), 78(h) |

| 0          | 1 (R) | 121 (decimal), 79(h) |

| 1          | 0 (W) | 122 (decimal), 7A(h) |

| 1          | 1 (R) | 123 (decimal), 7B(h) |

#### **RESET STATE**

In the reset state the device settings are brought back to their default values and any SIM card that has been active is deactivated. After reset, neither of the UICC/SIM interfaces is selected. The active pull-downs at the UICC/SIM interface are automatically activated. To ensure the system powers up in an operational state, device uses an internal 32 KHz clock for internal timing generation. After power up, the system has the option to continue to utilize the internal clock or select an external clock source. This clock source is selectable by the Clock Source Select I<sup>2</sup>C register bit.

- Power up the TXS02326A by asserting VBAT to enter the operation state

- I<sup>2</sup>C Interface becomes active with the VDD\_I/O supply

#### **RESET** summary:

- Any pending interrupts are cleared

- I<sup>2</sup>C registers are in the default state

- BSI and SDN counter value in the registers are set to four clock cycles or "0000 0100"

- Both on chip regulators are set to 1.8V and disabled

- All SIM1 and SIM2 signals are pulled to GND

#### SETTING UP THE SIM INTERFACE

The TXS02326A supports both Class C (1.8V) or Class B (2.95V) SIM cards. In order to support these cards types, the interface on the SIM side needs to be properly setup. After power up, the system should default to SIM1 card. The following sequence outlines a rudimentary sequence of preparing the SIM1 card interface:

- Configure the SIM1 regulator to 1.8V by asserting B1 = 0 in the SIM Interface Control Register (08h). The system by default should start in 1.8V mode.

- Configure the OE signal by asserting B0 = 0 in the Device Control Register (0Eh). The default value essentially disables the OE pin and the device is configured as an auto direction translator.

- The baseband SIM interface is set to a LOW state.

- Disable the SIM1 interface by asserting B2 = 0 and B3 = 0 in the SIM Interface Control Register.

- Disable the SIM2 interface by asserting B6 = 0 and B7 = 0 in the SIM Interface Control Register.

- VSIM1 voltage regulator should now be activated by asserting B0 = 1 in the SIM Interface Control Register.

- Enable the SIM1 interface by asserting B2 = 1 and B3 = 1 in the SIM Interface Control Register.

- The SIM1 interface (VSIM1, SIM1CLK, SIM1I/O) is now active. The TXS02326A relies on the baseband to perform the power up sequencing of the SIM card. If there is lack of communication between the baseband and the SIM card, the SIM1 interface must be powered-down and then powered up again through the regulator by configuring it to 2.95V by asserting B1 = 1 in the SIM Interface Control Register.

#### SWITCHING BETWEEN SIM CARDS

The following sequence outlines a rudimentary sequence of switching between the SIM1 card and SIM2 card:

- Put the SIM1 card interface into "clock stop" mode then assert B2 = 1 and B3 = 0 in the SIM Interface Control Register (08h). This will latch the state of the SIM1 interface (SIM1CLK, SIM1I/O, SIM1RST).

- There can be two scenarios when switching to SIM2 card:

- SIM2 may be in the power off mode, B6 = 0 and B7 = 0 in the Status Register (04h). If SIM2 is in power off mode, the SIM/UICC interface will need to be set to the power off state. In this case the baseband will most likely need to go through a power up sequence iteration

- SIM2 may already be in the "clock stop" mode, B6 = 1 and B7 = 0 in the Status Register (04h). If SIM2 is

in "clock stop" mode, the interface between the baseband and the device is set to the clock stop mode

levels that correspond to the SIM2 card interface.

- After determining whether the SIM2 card is either in power off mode or clock stop mode, the SIM2 card interface is then activated by asserting B6 = 1 and B7 = 1 in the SIM Interface Control Register (08h) and the negotiation between the baseband and card can continue.

- Switching from SIM2 to SIM1 done in the same manner.

#### **AUTOMATIC SHUTDOWN**

Both SIM card interfaces can be configured to automatically shut down upon disconnecting the battery. The shutdown threshold BSI<sub>Threshold</sub> is configured in B3 of the Device Control Register (0Eh). Two threshold levels are available for this configuration. When the BSI input level exceeds the BSI<sub>Threshold</sub> level that caused this powerdown, both SIM card interfaces will automatically be shut down. If the battery removal interrupt is enabled through B2 of the Device Control Register, then an interrupt will be issued to the baseband on IRQ. This case may happen if the user decides to remove the battery.

There are two scenarios for shutting down each SIM: SIMx is "active", or in "clock stop" mode. In clock stop mode, when the debounce timer expires, the SIMx signals all go low immediately, then the regulator is disabled one 32KHz cycle later. If SIMx is active, the signals go low and the regulator is disabled in a particular sequence to be described in the next section.

The SIM2 interface can also be configured to automatically shut down via the SDN pin.

FXAS

NSTRUMENTS

www.ti.com.cn

ZHCS863A - MAY 2012 - REVISED AUGUST 2013

#### **BSI / SDN DEBOUNCE AND AUTOMATIC SHUTDOWN SEQUENCE TIMING**

There are two debounce counters: one each for the BSI and SDN inputs. For each counter, when the device is reset or the related input is "false", the counter is loaded with the value in the associated Debounce Counter register and the debounced signal (i.e. BSI\_DEB or SDN\_DEB) is subsequently set to a "false" state. When the related input becomes "true", the counter begins counting down on subsequent CLK rising-edges. (CLK is either the internal or external 32 kHz clock as selected by Clock Source Select)

If the input changes state during the count, the counter is again loaded with the register value. The debounce counter propagates the input signal to the output when the counter expires.

For BSI and BSI\_DEB, the "true" state is high. For SDN and SDN\_DEB, the "true" state is the state stored in the SDN Detection Level register. Once either count reaches zero, the debounced signal switches to the "true" state on the next CLK rising edge. Writing a new value to the SDN detection level register such that SDN is now in the TRUE state will force the debounce counter to zero, but will not generate an interrupt nor initiate a shutdown sequence.

If BSI\_DEB goes high and Battery Removal Interrupt (bit 2 of the Device Control Register) is 1, an interrupt is generated and appears on IRQ. Also, if BSI\_DEB goes high and BSI Detection Control (bit 4 of the Device Control Register) is 0, the Automatic Shutdown sequence begins for both SIM's.

If SDN\_DEB goes "true" and SDN Detection Interrupt (bit 5 of the Device Control Register) is 1, an interrupt is generated and appears on IRQ. Also, if SDN\_DEB goes "true" and SDN Detection Control (bit 7 of the Device Control Register) is 0, the Automatic Shutdown sequence begins for SIM2 only, leaving SIM1 unaffected.

| CLK      |               | 11             | 12             | 13             | 14         | 15 | 16 17 | L |

|----------|---------------|----------------|----------------|----------------|------------|----|-------|---|

| DEB CNT  | 4 3 2 4 3 2 1 | 1              | 0              |                |            |    | 4     |   |

| BSI      |               | <br> <br>      | <br> <br> <br> | <br> <br> <br> |            | ļ  |       |   |

| BSI_DEB  |               |                |                |                |            |    |       |   |

| IRQ      |               |                | <br> <br> <br> |                | L<br> <br> |    |       |   |

| SIMCLK   |               | ΓΛ             | Πſ             | LU I           |            | M  | ſΩΩ   | Л |

| SIM1 RST |               |                |                |                |            |    |       |   |

| SIM1 CLK | www.www.www.  | Γſ             | Π              |                |            |    |       |   |

| SIM1 I/O | Active Data   | 1              | 1              |                |            |    |       |   |

| SIM1 VCC |               | <br> <br> <br> | <br> <br> <br> |                |            |    |       |   |

| SIM2 RST | Latched RST   |                |                |                |            |    |       |   |

| SIM2 CLK | Latched Clock |                | <br> <br>      |                |            |    |       |   |

| SIM2 I/O | Latched Data  |                | <br> <br> <br> |                |            |    |       |   |

| SIM2 VCC |               |                |                |                |            |    |       |   |

Figure 2. BSI Debounce Timing – SIM1 Active and SIM2 Isolated

#### Notes:

BSI debounce count value set to 4 SIM1 Active, SIM2 powered but Isolated BSI Detection Control set to 0 Battery Removal Interrupt set to 1

#### ZHCS863A - MAY 2012 - REVISED AUGUST 2013

www.ti.com.cn

Once BSI is high for four cycles, BSI\_DEB goes high causing automatic shutdown sequence on both SIMs. Since SIM1 is active with SIMCLK running, it follows the staged shutdown sequence. Since SIM2 is powered up but inactive, it follows the instant shutdown sequence.

| CLK      |               | 11 12 | 13 14 | 15 16 17 |

|----------|---------------|-------|-------|----------|

| DEB CNT  | 4 3 2 4 3 2 1 | 0     |       | 4        |

| BSI      |               |       |       |          |

| BSI_DEB  |               |       |       |          |

| IRQ      |               |       |       |          |

| SIMCLK   |               |       |       |          |

| SIM1 RST |               |       |       |          |

| SIM1 CLK | Clock stopped |       |       |          |

| SIM1 I/O | Active Data   |       |       |          |

| SIM1 VCC |               |       |       |          |

| SIM2 RST | Latched RST   |       |       |          |

| SIM2 CLK | Latched Clock |       |       |          |

| SIM2 I/O | Latched Data  |       |       |          |

| SIM2 VCC |               |       |       |          |

#### Figure 3. BSI Debounce Timing – SIM1 Clock Stop and SIM2 Isolated

#### Notes:

BSI debounce counter set to 4 SIM1 Active in Clock Stop Mode SIM2 powered but Isolated BSI Detection Control set to 0 Battery Removal Interrupt set to 1

Once BSI is high for four cycles, BSI\_DEB goes high causing automatic shutdown sequence on both SIMs. Since SIM1 is active with SIMCLK stopped, it follows the instant shutdown sequence. Since SIM2 is powered up but inactive, it follows the instant shutdown sequence.

| CLK      |               | 11        | 12        | 13                | 14             | 15 | 16 | 17 |

|----------|---------------|-----------|-----------|-------------------|----------------|----|----|----|

| DEB CNT  | 4 3 2 4 3 2 1 | <br> <br> | 0         |                   | 1              |    | 4  |    |

| BSI      |               | <br> <br> | <br> <br> |                   |                |    |    |    |

| BSI_DEB  |               |           | <br> <br> | <br> <br>         |                |    |    |    |

| IRQ      |               |           | <br> <br> | <u> </u><br> <br> | <br> <br>      |    |    |    |

| SIMCLK   | www.www.      | Γſ        | ΠΠ        | ЛЛ                | ГЛ             | ГЛ | Л  | ЛЛ |

| SIM1 RST | Latched RST   |           |           | -                 |                |    |    |    |

| SIM1 CLK | Latched Clock |           |           |                   | <br> <br>      |    |    |    |

| SIM1 I/O | Latched Data  |           |           |                   | <br> <br>      |    |    |    |

| SIM1 VCC |               | <br> <br> |           |                   | <br> <br>      |    |    |    |

| SIM2 RST |               |           |           | <br> <br> <br>    | <br> <br>      |    |    |    |

| SIM2 CLK | www.www.www.  | ПЛ        | Г         |                   | <br> <br> <br> |    |    |    |

| SIM2 I/O | Active Data   |           |           | 1                 |                |    |    |    |

| SIM2 VCC |               |           |           |                   |                |    |    |    |

|          |               |           |           |                   |                |    |    |    |

#### Notes:

BSI debounce counter set to 4

SIM2 Active

SIM1 powered but Isolated

BSI Detection Control set to 0

Battery Removal Interrupt set to 1

Once BSI is high for four cycles, BSI\_DEB goes high causing automatic shutdown sequence on both SIMs. Since SIM2 is active with SIMCLK running, it follows the staged shutdown sequence. Since SIM1 is powered up but inactive, it follows the instant shutdown sequence.

# TXS02326A

TEXAS INSTRUMENTS

| ZHCS863A – MAY | 2012-REVISED AU | GUST 2013 |

|----------------|-----------------|-----------|

www.ti.com.cn

| CLK      |                       | 12           | 13             | 14 | 15 16 17 |

|----------|-----------------------|--------------|----------------|----|----------|

| DEB CNT  | 4 3 2 1 7 6 5 4 3 2 1 | 0            |                |    | 4        |

| Wt. 0Ah  | Ŋ                     |              |                | 1  |          |

| BSI      |                       | <br> <br>    |                |    |          |

| BSI_DEB  |                       |              |                |    |          |

| IRQ      |                       |              | <br> <br>      |    |          |

| SIMCLK   | www.www.www.          | ГЛ           | ПЛ             | ЛЛ | hhh      |

| SIM1 RST |                       |              |                |    |          |

| SIM1 CLK | www.www.www.www.      | ЛЛ           | Г              |    |          |

| SIM1 I/O | Active Data           | I.<br>1<br>1 | <br> <br>      | 1  |          |

| SIM1 VCC |                       | <br> <br>    | <br> <br> <br> |    |          |

| SIM2 RST | Latched RST           |              | <br> <br>      |    |          |

| SIM2 CLK | Latched Clock         | 1            | <br> <br>      |    |          |

| SIM2 I/O | Latched Data          | 1            | <br> <br>      |    |          |

| SIM2 VCC |                       |              |                |    |          |

#### Figure 5. BSI Debounce Timing – Debounce Count Value Write During Debounce

#### Notes:

BSI debounce count value set to 4, but written to 7 during debounce

SIM1 Active

SIM2 powered but Isolated

BSI Detection Control set to 0

Battery Removal Interrupt set to

BSI\_DEB goes high causing automatic shutdown sequence on both SIM's. Since SIM1 follows the staged shutdown sequence. SIM2 follows the instant shutdown sequence. BSI returning low does not interrupt shutdown sequence.

TEXAS INSTRUMENTS

www.ti.com.cn

ZHCS863A - MAY 2012 - REVISED AUGUST 2013

| CLK      |                                          | 11        | 12 13 14        | 15 16 17 |

|----------|------------------------------------------|-----------|-----------------|----------|

| DEB CNT  | 4 3 2 4 3 2 1                            | <br> <br> | 0               | 4        |

| SDN      |                                          | <br> <br> | <br> <br> <br>  | L        |

| SDN_DEB  |                                          |           | <br> <br> <br>  | L        |

| IRQ      |                                          |           | 1<br> <br> <br> |          |

| SIMCLK   | www.www.www.www.                         | ПЛ        | hunn            | www      |

| SIM1 RST |                                          | <br> <br> | I<br> <br> <br> |          |

| SIM1 CLK | www.www.www.www.                         | Γſ        | MMM             | www      |

| SIM1 I/O | Active Data                              |           |                 |          |

| SIM1 VCC |                                          | <br> <br> |                 |          |

| SIM2 RST | Latched RST                              |           |                 |          |

| SIM2 CLK | Latched Clock                            |           |                 |          |

| SIM2 I/O | Latched Data                             |           |                 |          |

| SIM2 VCC |                                          |           |                 |          |

|          | Figure 6. SDN Debounce Timing – SDN Dete | ction     | Level High      |          |

#### Notes:

SDN debounce count value set to 4

SIM1 Active

SIM2 powered but Isolated

SDN Detection Control set to 0

SDN Detection level set to 1

SDN Detection Interrupt set to 1

Once SDN is high for four cycles, SDN\_DEB goes high causing automatic shutdown sequence on SIM2. SIM1 is unaffected. Since SIM2 is powered up but inactive, it follows the instant shutdown sequence.

# TXS02326A

TEXAS INSTRUMENTS

| ZHCS863A – MAY | 2012-REVISED | AUGUST 2013 |

|----------------|--------------|-------------|

|                |              | 100001 2010 |

www.ti.com.cn

| CLK      | 1 2 3 4 5 6 7 8 9 10                   | 11        | 12 13 14 15 16 17 |

|----------|----------------------------------------|-----------|-------------------|

| DEB CNT  | 4 3 2 4 3 2 1                          |           | 0 4               |

| SDN      |                                        | <br> <br> |                   |

| SDN_DEB  |                                        | <u> </u>  |                   |

| IRQ      |                                        |           |                   |

| SIMCLK   | www.www.                               | ПЛ        | mmmm              |

| SIM1 RST |                                        | <br> <br> |                   |

| SIM1 CLK | www.www.                               | hυ        | mmmm              |

| SIM1 I/O | Active Data                            |           |                   |

| SIM1 VCC |                                        |           |                   |

| SIM2 RST | Latched RST                            |           |                   |

| SIM2 CLK | Latched Clock                          |           |                   |

| SIM2 I/O | Latched Data                           |           |                   |

| SIM2 VCC |                                        |           |                   |

|          | Figure 7 CDN Dehourses Timing CDN Deta |           |                   |

Figure 7. SDN Debounce Timing – SDN Detection Level Low

#### Notes:

SDN debounce count value set to 4

SIM1 Active

SIM2 powered but Isolated

SDN Detection Control set to 0

SDN Detection level set to 0

SDN Detection Interrupt set to 1

Once SDN is low for four cycles, SDN\_DEB goes low causing automatic shutdown sequence on SIM2. SIM1 is unaffected. Since SIM2 is powered up but inactive, it follows the instant shutdown sequence.

| Ţexas       |

|-------------|

| INSTRUMENTS |

| www.ti.com.c | n                                            | Z     | HCS86 | 3A – MA        | Y 2012         | 2-REVISE | D AUG | SUST 2013 |

|--------------|----------------------------------------------|-------|-------|----------------|----------------|----------|-------|-----------|

| CLK          |                                              |       | 12    | 13             | 14             | 15       | 16    | 17        |

| DEB CNT      | 4 3 2 4 3 2 1                                |       | 0     | 1              | 1              |          | 4     |           |

| SDN          |                                              |       |       | <br> <br> <br> |                |          |       |           |

| SDN_DEB      |                                              |       |       | <br> <br>      | 1              |          |       |           |

| IRQ          |                                              |       |       | 1<br>1<br>1    | <br> <br>      |          |       |           |

| SIMCLK       | www.www.                                     | M     | JL    | Γſ             | ת              | M        | ЛЛ    | ЛЛ        |

| SIM1 RST     | Latched RST                                  |       | 1     | <br> <br>      | <br> <br>      |          |       |           |

| SIM1 CLK     | Latched Clock                                |       |       |                |                |          |       |           |

| SIM1 I/O     | Latched Data                                 |       | 1     |                | <br> <br>      |          |       |           |

| SIM1 VCC     |                                              |       |       | 1              | 1              |          |       |           |

| SIM2 RST     |                                              |       |       |                | <br>           |          |       |           |

| SIM2 CLK     | www.www.                                     | ΠÚ    |       | <br> <br> <br> | <br> <br> <br> |          |       |           |

| SIM2 I/O     | Active Data                                  |       |       |                | <br> <br>      |          |       |           |

| SIM2 VCC     |                                              |       |       |                |                |          |       |           |

|              | Figure 8. SDN Debounce Timing – SIM1 Isolate | d and | SIM   | 2 Acti         | ive            |          |       |           |

#### Notes:

SDN debounce count value set to 4

SIM1 powered but Isolated

SIM2 Active

SDN Detection Control set to 0

SDN Detection level set to 1

SDN Detection Interrupt set to 1

SDN\_DEB goes high causing automatic shutdown sequence on SIM2. Since SIM2 is active with SIMCLK running, it follows the staged shutdown sequence, SIM1 is unaffected.

ZHCS863A-MAY 2012-REVISED AUGUST 2013

www.ti.com.cn

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)

### Level Translator<sup>(1)</sup>

|                  |                                                    |                                                                           |                                                                                     | MIN  | MAX  | UNIT |  |  |

|------------------|----------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|------|------|--|--|

| VDDIO            | Supply voltage range                               |                                                                           |                                                                                     | -0.3 | 4.0  | V    |  |  |

|                  |                                                    |                                                                           | VDDIO-port                                                                          | -0.5 | 4.6  |      |  |  |

| VI               | Input voltage range                                |                                                                           | VSIMx-port                                                                          | -0.5 | 4.6  | V    |  |  |

|                  |                                                    |                                                                           | Control inputs                                                                      | -0.5 | 4.6  | .6   |  |  |

| V                | Voltage range applied to any output in the         | range applied to any output in the high-impedance or power-off VDDIO-port |                                                                                     | -0.5 | 4.6  | V    |  |  |

| Vo               | state                                              |                                                                           | VSIMx-port                                                                          | -0.5 | 4.6  | v    |  |  |

| M                |                                                    | high on low state                                                         | VDDIO-port                                                                          | -0.5 | 4.6  | V    |  |  |

| Vo               | Voltage range applied to any output in the         | nigh or low state                                                         | VSIMx-port                                                                          | -0.5 | 4.6  | V    |  |  |

| I <sub>IK</sub>  | Input clamp current                                | V <sub>1</sub> < 0                                                        |                                                                                     | -50  | mA   |      |  |  |

| I <sub>OK</sub>  | Output clamp current                               |                                                                           | V <sub>O</sub> < 0                                                                  |      | -50  | mA   |  |  |

| I <sub>O</sub>   | Continuous output current                          |                                                                           | ±50                                                                                 | mA   |      |      |  |  |

|                  | Continuous current through V <sub>CCA</sub> or GND |                                                                           | ±100                                                                                | mA   |      |      |  |  |

| T <sub>stg</sub> | Storage temperature range                          |                                                                           |                                                                                     | -65  | 150  | °C   |  |  |

|                  |                                                    | Human-Body Model (HBM)                                                    | All pins                                                                            |      | 2.5  | kV   |  |  |

|                  | ESD rating                                         | Human-Body Model (HBM-<br>HV)                                             | Baseband Side I/O:<br>SIM1CLK, SIM1I/O,<br>SIM1RST,<br>SIM2CLK, SIM2I/O,<br>SIM2RST |      | 6    | Kv   |  |  |

|                  |                                                    | Charge-Device Model (CDM)                                                 | )                                                                                   |      | 1000 | V    |  |  |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### LDO<sup>(1)</sup>

|                  |                            |                            |                             | MIN  | MAX  | UNIT |

|------------------|----------------------------|----------------------------|-----------------------------|------|------|------|

| V <sub>IN</sub>  | Input voltage range        |                            |                             | -0.3 | 6    | V    |

| V <sub>OUT</sub> | Output voltage range       | -0.3                       | 6                           | V    |      |      |

| TJ               | Junction temperature range | -55                        | 150                         | °C   |      |      |

| T <sub>stg</sub> | Storage temperature range  |                            |                             | -55  | 150  | °C   |

|                  | ESD rating                 | Human-Body Model (HBM-HV)  | LDO Output:<br>VSIM1, VSIM2 |      | 6    | kV   |

|                  | -                          | Charged-Device Model (CDM) |                             |      | 1000 | V    |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### ZHCS863A - MAY 2012 - REVISED AUGUST 2013

#### THERMAL IMPEDANCE RATINGS

|               |                                          |             |    | UNIT |

|---------------|------------------------------------------|-------------|----|------|

| $\theta_{JA}$ | Package thermal impedance <sup>(1)</sup> | RGE package | 45 | °C/W |

(1) The package thermal impedance is calculated in accordance with JESD 51-7.

#### **RECOMMENDED OPERATING CONDITIONS**<sup>(1)</sup> Level Translator

|                 |                                    | Description                                            | MIN         | MAX         | UNIT |

|-----------------|------------------------------------|--------------------------------------------------------|-------------|-------------|------|

| VDDIO           | Supply voltage                     |                                                        | 1.7         | 3.3         | V    |

| VIH             | High-level input voltage           | Applies to pins: RESET, SDN,                           | VDDIO × 0.7 | 1.9         | V    |

| V <sub>IL</sub> | Low-level input voltage            | SCL, SDA, IRQ, OE, 32kHz,<br>SIM_RST, SIM_CLK, SIM_I/O | 0           | VDDIO × 0.3 | V    |

| Δt/Δv           | Input transition rise or fall rate |                                                        |             | 5           | ns/V |

| T <sub>A</sub>  | Operating free-air temperature     |                                                        | -40         | 85          | °C   |

(1) All unused data inputs of the device must be held at V<sub>CCI</sub> or GND to ensure proper device operation. Refer to the TI application report, *Implications of Slow or Floating CMOS Inputs*, literature number SCBA004.

ZHCS863A - MAY 2012 - REVISED AUGUST 2013

www.ti.com.cn

#### ELECTRICAL CHARACTERISTICS Level Translator

over recommended operating free-air temperature range (unless otherwise noted)

| PA              | RAMETER        | TEST CONDITIONS                        | VDDIO                | VSIM1                                  | VSIM2                                  | MIN            | TYP <sup>(1)</sup> | MAX         | UNIT |

|-----------------|----------------|----------------------------------------|----------------------|----------------------------------------|----------------------------------------|----------------|--------------------|-------------|------|

| SIM1_RST        |                | I <sub>OH</sub> = -100 μA              |                      |                                        |                                        | VSIM1 × 0.8    |                    |             |      |

|                 | SIM1_CLK       | Push-Pull                              |                      |                                        |                                        | VSIM1 × 0.8    |                    |             |      |

|                 | SIM1_I/O       | l <sub>OH</sub> = −10 μA<br>Open-Drain |                      |                                        |                                        | VSIM1 × 0.8    |                    |             |      |

|                 | SIMIT_I/O      | I <sub>OH</sub> = −100 μA<br>Push-Pull |                      |                                        |                                        | V SIIVIT X 0.8 |                    |             |      |

|                 | SIM2_RST       | I <sub>OH</sub> = −100 μA              | 1.7 V                | 1.8 V / 2.95 V                         | 1.8 V / 2.95 V                         | VSIM2 × 0.8    |                    |             |      |

| V <sub>он</sub> | SIM2_CLK       | Push-Pull                              | to 3.3               | (Supplied by                           | (Supplied by                           | VSIM2 × 0.8    |                    |             | V    |

|                 | SIM2_I/O       | I <sub>OH</sub> = −10 μA<br>Open-Drain | V                    | LDO)                                   | LDO)                                   | VSIM2 × 0.8    |                    |             |      |

|                 | 3110/2_1/0     | I <sub>OH</sub> = −100 μA<br>Push-Pull |                      |                                        |                                        | V 311V12 × 0.0 |                    |             |      |

|                 | SIM_I/O        | I <sub>OH</sub> = −10 μA<br>Open-Drain |                      |                                        |                                        | VDDIO × 0.8    |                    |             |      |

|                 | SIM_I/O        | I <sub>OH</sub> = −100 μA<br>Push-Pull |                      |                                        |                                        |                |                    |             |      |

|                 | SIM1_RST       | I <sub>OL</sub> = 1 mA<br>Push-Pull    |                      |                                        |                                        |                |                    | VSIM1 × 0.2 |      |

|                 | SIM1_CLK       | I <sub>OL</sub> = 1 mA<br>Push-Pull    |                      |                                        |                                        |                |                    | VSIM1 × 0.2 |      |

|                 | SIM1_I/O       | I <sub>OL</sub> = 1 mA<br>Open-Drain   |                      |                                        |                                        |                |                    | 0.3         |      |

|                 | 01011_00       | I <sub>OL</sub> = 1 mA<br>Push-Pull    |                      |                                        |                                        |                |                    | 0.5         |      |

| N/              | SIM2_RST       | I <sub>OL</sub> = 1 mA<br>Push-Pull    | 1.7 V<br>to 3.3      | 1.8 V / 2.95 V<br>(Supplied by<br>LDO) | 1.8 V / 2.95 V<br>(Supplied by         |                |                    | VSIM2 × 0.2 | v    |

| V <sub>OL</sub> | SIM2_CLK       | I <sub>OL</sub> = 1 mA<br>Push-Pull    | V V                  |                                        | (Supplied by<br>LDO)                   |                |                    | VSIM2 × 0.2 | v    |

|                 | SIM2_I/O       | I <sub>OL</sub> = 1 mA<br>Open-Drain   |                      |                                        |                                        |                |                    | 0.3         |      |

|                 | 3111/2_1/0     | I <sub>OL</sub> = 1 mA<br>Push-Pull    |                      |                                        |                                        |                |                    | 0.3         |      |

|                 | SIM I/O        | I <sub>OL</sub> = 1 mA<br>Open-Drain   |                      |                                        |                                        |                |                    | 0.3         |      |

|                 | SIM_I/O        | I <sub>OL</sub> = 1 mA<br>Push-Pull    |                      |                                        |                                        |                |                    | 0.3         |      |

| I,              | Control inputs | V <sub>I</sub> = OE                    | 1.7 V<br>to 3.3<br>V | 1.8 V / 2.95 V<br>(Supplied by<br>LDO) | 1.8 V / 2.95 V<br>(Supplied by<br>LDO) |                |                    | ±1          | μA   |

| <u>_</u>        | SIM_I/O port   |                                        |                      |                                        |                                        |                | 7                  |             | ~    |

| C <sub>io</sub> | SIMx port      |                                        |                      |                                        |                                        |                | 4                  |             | pF   |

| C <sub>i</sub>  | Control inputs | V <sub>I</sub> = VDDIO or GND          |                      |                                        |                                        |                | 3                  |             | pF   |

| U <sub>i</sub>  | Clock input    |                                        |                      |                                        |                                        |                | Э                  |             | pr   |

(1) All typical values are at  $T_A = 25^{\circ}C$ .

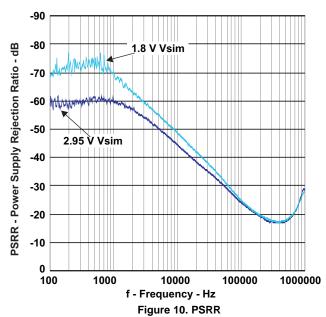

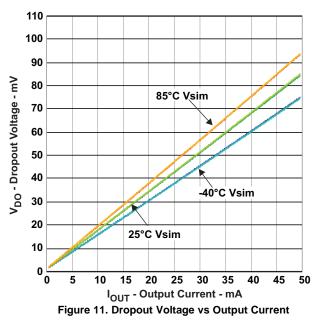

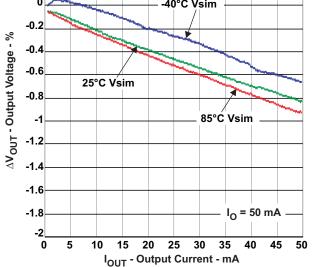

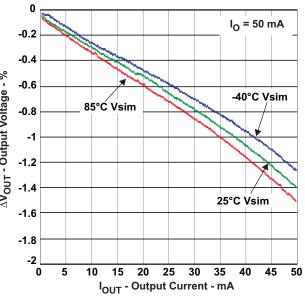

### ELECTRICAL CHARACTERISTICS LDO (Control Input Logic = High)

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                      | TEST CONDITION                                                                                                      | ONS                                                                      | MIN  | TYP <sup>(1)</sup> | MAX | UNIT |

|----------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|--------------------|-----|------|

| VBAT                 | Input voltage                  |                                                                                                                     |                                                                          | 2.3  |                    | 5.5 | V    |

| V                    | Output voltage                 | Class-B Mode                                                                                                        | 2.85                                                                     | 2.95 | 3.05               | V   |      |

| V <sub>OUT</sub>     | Output voltage                 | Class-C Mode                                                                                                        |                                                                          | 1.7  | 1.8                | 1.9 | V    |

| V <sub>DO</sub>      | Dropout voltage                | I <sub>OUT</sub> = 50 mA                                                                                            |                                                                          |      |                    | 100 | mV   |

|                      | Ground-pin current             | I <sub>OUT</sub> = 0 mA                                                                                             |                                                                          |      | 35                 |     |      |

| GND                  | Ground-pin current             | I <sub>OUT</sub> = 50 mA                                                                                            |                                                                          |      | 150                | μA  |      |