# 具有电流感测和故障保护功能的数字控制兼容型同步降压栅极驱动器

查询样品: UCD7232

# 特性

- 双通道高电流驱动器。

- 完全兼容于 TI Fusion 数字电源控制器(如 UCD91xx 及 UCD92xx 系列)

- 工作开关频率 2 MHz

- 具有独立可调门限的高侧 FET 和输出电流限制保护

- 具有故障标记输出的快速高侧过流感测电路 可逐个周期地防止出现破坏性的电流水平

- 差分高增益电流感测放大器

- 电压与负载电流监视器输出成正比

- 宽输入电压范围: 4.7 V 至15 V

利用一个外部 4.5 V 至 6.5 V 偏置电源支持 2.2 V

的工作输入电压

- 用于栅极驱动及内部电路的板载稳压电压

- 集成型热关断功能电路

- 可选的操作模式:

- 具有自动死区时间控制功能的 **PWM** 及同步整 流器使能 **(SRE)**

- 用于 DirectFET 控制的直接高侧栅极及低侧栅极输入

- 用于功率级关断的三态 PWM 输入

- · UVLO 内务处理电路

- 额定规格针对 -40°C 至 +125°C 的结温范围而拟订

# 应用

- 针对单相和多相应用的数字控制同步降压功率级

- 数字控制式电源模块

#### 说明

UCD7232 高电流驱动器专为数字控制、负载点、同步降压型开关电源而特别设计。 两个驱动器电路可在同步降压电路中为高侧 NMOS 开关和低侧 NMOS 同步整流器提供高充电及放电电流。 MOSFET 栅极由一个内部稳压 V<sub>GG</sub> 电源驱动。 禁用内部 V<sub>GG</sub> 稳压器可允许用户提供其特有的栅极驱动电压。 这种高灵活性支持 2.2 V 至 15 V 的宽泛功率转换输入电压。内部欠压闭锁 (UVLO) 逻辑可在允许芯片工作之前确保 V<sub>GG</sub> 为良好。

驱动器逻辑模块可支持两种操作模式(由 SRE 模式引脚负责选择)中的一个。 在同步模式下,该逻辑模块可使用 PWM 信号来控制高侧与低侧栅极驱动器信号。 死区时间可自动调节以防止发生交叉传导。 同步整流器使能 (SRE) 引脚用于控制在 PWM 信号为低电平时是否接通低侧 FET。 在独立模式中,PWM 和 SRE 引脚可直接控制高侧及低侧栅极。 在该模式中未使用抗交叉传导逻辑电路。

板载比较器负责监视高侧开关两端的电压及一个外部电流感测元件两端的电压,以避免突发的高电流负载损坏功率级。由单个电阻器设定了高侧比较器的消隐延迟,以避免与开关边缘噪声同时发生的误报告。 在发生高侧故障或过流故障的情况下,高侧 FET 关断且故障标记 (FLT) 被置为有效,以向数字控制器发出提示信号。 故障门限由 HS 感测和 ILIM 引脚独立设定。

输出电流由一个高精度、高增益的开关电容差分放大器进行测量与监视,该放大器负责处理一个外部电流感测元件两端的电压。 经过放大的信号可供 I<sub>MON</sub> 引脚上的数字控制器使用。 电流感测放大器具有 0.5V 的输出失调,因而可检测正(供应)和负(吸收)电流。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

**ISTRUMENTS**

www.ti.com.cn

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# 说明(继续)

ZHCS028 - MAY 2011

一个片上温度感测监视器用于监视芯片温度。 如果芯片温度超过大约 165°C,则温度传感器将启动热关断,从而暂停输出开关操作并设定 FLT 标记。 当芯片温度下降约 20℃ 时,温度故障将自动清除。

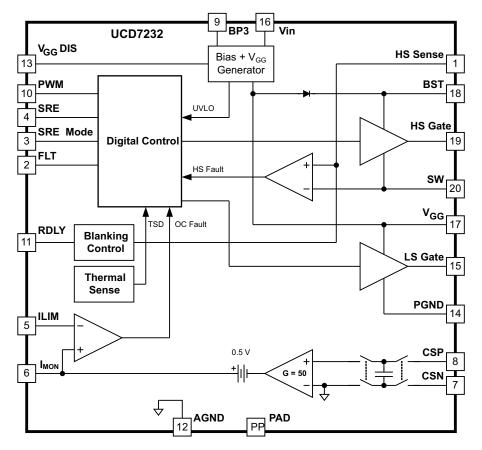

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. UCD7232 Block Diagram

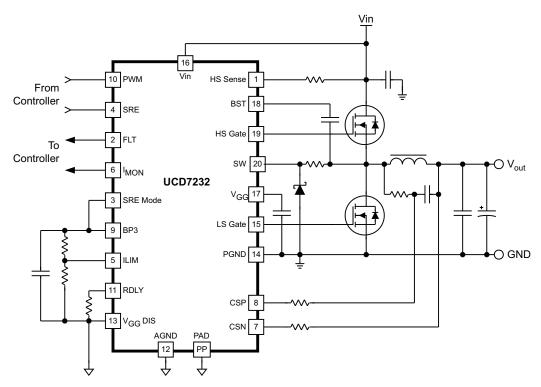

# SIMPLIFIED APPLICATION DIAGRAM

Figure 2. Typical Synchronous Buck Power Stage

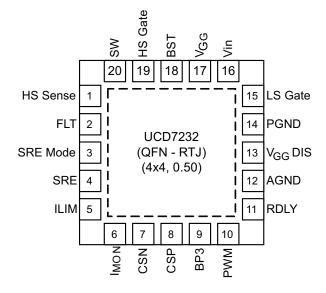

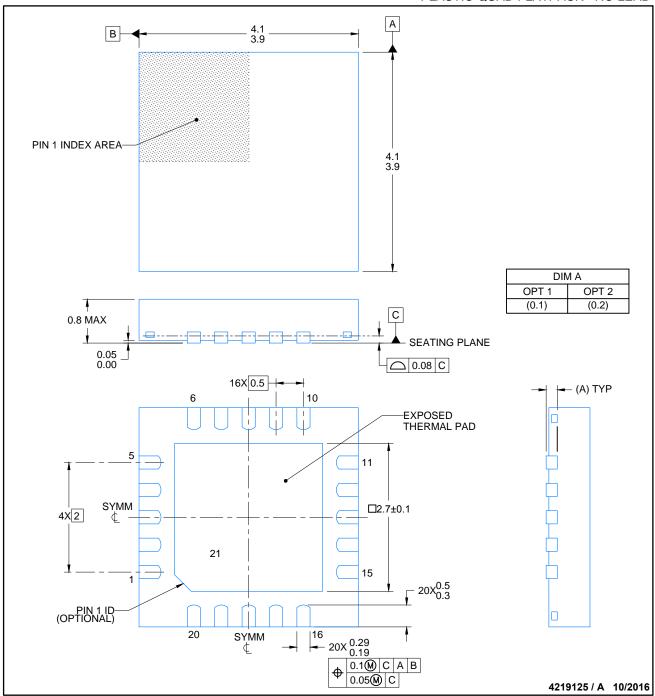

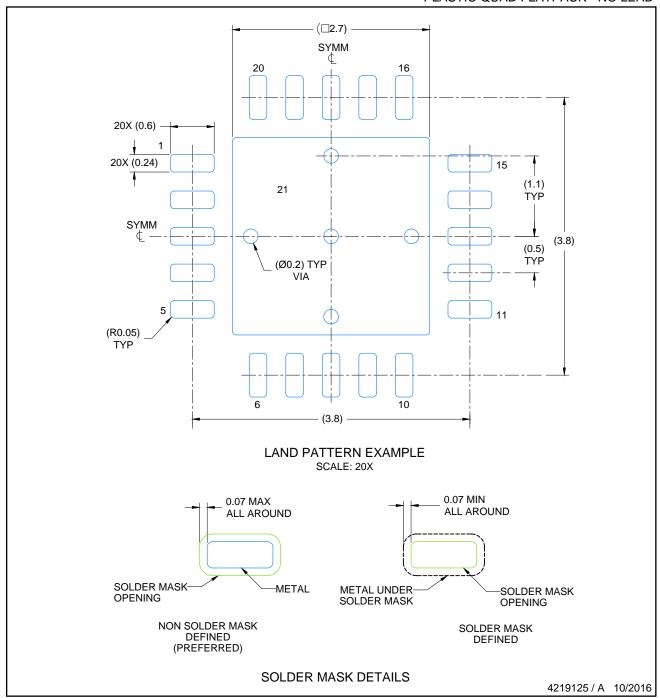

# **CONNECTION DIAGRAM**

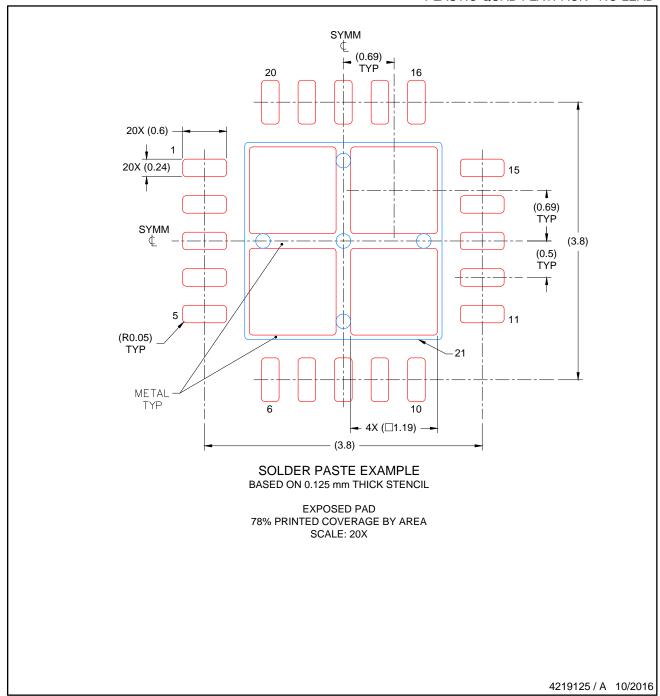

#### **ORDERING INFORMATION**

| TEMPERATURE RANGE PACKAGE |                       | TAPE AND REEL QTY | PART NUMBER |

|---------------------------|-----------------------|-------------------|-------------|

| -40°C to +125°C           | Disatis OFN 90 (DT I) | 250               | UCD7232RTJT |

|                           | Plastic QFN-20 (RTJ)  | 2500              | UCD7232RTJR |

# ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

| <b>n</b>                                       | A D A METED                                             | VALU       | JE                   | LINUT |  |  |

|------------------------------------------------|---------------------------------------------------------|------------|----------------------|-------|--|--|

| P                                              | ARAMETER                                                | MIN        | MAX                  | UNIT  |  |  |

| Supply voltage, V <sub>IN</sub>                |                                                         | -0.3       | 16                   | V     |  |  |

|                                                | V <sub>BST</sub> DC                                     | -0.3       | 23                   |       |  |  |

| Do etetror velto re                            | V <sub>BST</sub> Pulse (V <sub>SW</sub> at 20V < 400ns) | -0.3       | 27                   |       |  |  |

| Bootstrap voltage                              | V <sub>BST</sub> Pulse (V <sub>SW</sub> at 22V < 64ns)  | -0.3       | 29                   | V     |  |  |

|                                                | V <sub>BST</sub> Pulse (V <sub>SW</sub> at 30V < 16ns)  | -0.3       | 37                   |       |  |  |

| Gate drive supply voltage                      | V <sub>GG</sub> (Externally supplied)                   | -0.3       | 7                    | V     |  |  |

| Output mate differential                       | HS Gate – SW                                            | -0.3       | 7                    |       |  |  |

| Output gate drive voltage                      | LS Gate                                                 | PGND - 0.3 | V <sub>GG</sub> +0.3 | V     |  |  |

|                                                | V <sub>SW</sub> DC                                      | -1         | 16                   |       |  |  |

| Switch node voltage                            | V <sub>SW</sub> Pulse < 400 ns, E = 20 μJ               | -2         | 20                   | V     |  |  |

|                                                | V <sub>SW</sub> Pulse < 64 ns                           | -5         | 22                   | V     |  |  |

|                                                | V <sub>SW</sub> Pulse < 16 ns                           | -10        | 30                   |       |  |  |

|                                                | CSP, CSN, RDLY                                          | -0.3       | 5.6                  |       |  |  |

| Analog inputs                                  | ILIM                                                    | -0.3       | 3.6                  | V     |  |  |

|                                                | HS Sense                                                | -0.3       | 16                   |       |  |  |

| Districtions                                   | PWM, SRE, SRE Mode                                      | -0.3       | 5.6                  |       |  |  |

| Digital inputs                                 | V <sub>GG</sub> DIS                                     | -0.3       | 3.6                  | V     |  |  |

| Analog outputs                                 | I <sub>MON</sub>                                        | -0.3       | 3.6                  | V     |  |  |

| Digital outputs                                | FLT                                                     | -0.3       | 3.6                  | V     |  |  |

| FOR Posters                                    | Human body model                                        |            | 2000                 |       |  |  |

| ESD Rating                                     | Charged device model                                    |            | 500                  | V     |  |  |

| Operating ambient temperature, T <sub>A</sub>  |                                                         | -40        | 125                  | °C    |  |  |

| Operating junction temperature, T <sub>J</sub> |                                                         | -40        | 150                  | °C    |  |  |

| Storage temperature, T <sub>STG</sub>          |                                                         | -65        | 150                  | °C    |  |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltages are with respect to AGND. Currents are positive into, negative out of the specified terminal. Consult company packaging information for thermal limitations and considerations of packages.

# THERMAL INFORMATION

|                         | THEDMAN METRIC(1)                            | UCD7232       | LINUTO |

|-------------------------|----------------------------------------------|---------------|--------|

|                         | THERMAL METRIC <sup>(1)</sup>                | RTJ (20 PINS) | UNITS  |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 38.2          |        |

| $\theta_{JCtop}$        | Junction-to-case (top) thermal resistance    | 34.4          |        |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 15.7          | °C/W   |

| ΨЈТ                     | Junction-to-top characterization parameter   | 0.4           | C/VV   |

| ΨЈВ                     | Junction-to-board characterization parameter | 15.7          |        |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | 5.9           |        |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|          |                                                             | MIN | TYP | MAX | UNIT |

|----------|-------------------------------------------------------------|-----|-----|-----|------|

| $V_{IN}$ | Power Input Voltage (Internally generated V <sub>GG</sub> ) | 4.7 | 12  | 15  | V    |

| $V_{IN}$ | Power Input Voltage (Externally supplied V <sub>GG</sub> )  | 2.2 | -   | 15  | V    |

| $V_{GG}$ | Externally supplied gate drive voltage                      | 4.6 | 6   | 6.5 | V    |

| $T_{J}$  | Operating junction temperature range                        | -40 | _   | 125 | °C   |

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V, 4.7  $\mu F$  from  $V_{GG}$  to PGND, 1  $\mu F$  from BP3 to AGND, 0.22  $\mu F$  from BST to SW,  $T_A = T_J = -40^{\circ} C$  to 125°C, RDLY = 8.06k $\Omega$ , SRE Mode = 3.3V,  $V_{GG}$  DIS tied to AGND (unless otherwise noted)

|                       | PARAMETER                                                         | TEST CONDITIONS                                                                                             | MIN  | TYP  | MAX | UNIT |  |  |

|-----------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|------|-----|------|--|--|

| SUPPLY SE             | CTION                                                             |                                                                                                             |      |      |     |      |  |  |

|                       | Supply current                                                    | Outputs not switching, V <sub>IN</sub> = 5 V, PWM = LOW                                                     |      | 8    | 10  | mA   |  |  |

|                       | Supply current                                                    | Outputs not switching, V <sub>IN</sub> = 15 V, PWM = LOW                                                    |      | 8    | 10  | mA   |  |  |

| GATE DRIV             | E UNDER-VOLTAGE LOCKOUT                                           |                                                                                                             |      |      |     |      |  |  |

| $V_{GG}$              | UVLO OFF                                                          | V <sub>GG</sub> rising                                                                                      |      | 4.4  | 4.6 | V    |  |  |

| $V_{GG}$              | UVLO ON                                                           | V <sub>GG</sub> falling                                                                                     | 4.1  | 4.3  |     | V    |  |  |

| $V_{GG}$              | UVLO hysteresis                                                   |                                                                                                             |      | 80   |     | mV   |  |  |

| V <sub>GG</sub> SUPPL | Y GENERATOR                                                       |                                                                                                             |      |      |     |      |  |  |

| \/                    |                                                                   | $V_{IN} \ge 7 \text{ V, I}_{GG} \le 100 \text{ mA}$                                                         | 5    |      |     | V    |  |  |

| $V_{GG}$              |                                                                   | V <sub>IN</sub> = 12 V, I_V <sub>GG</sub> ≤ 80 mA                                                           | 5.6  | 6.2  | 6.8 | V    |  |  |

|                       | Dropout                                                           | $V_{IN} = 4.75 \text{ V}, I_{QG} \le 100 \text{ mA}$                                                        |      |      | 350 | mV   |  |  |

| DIGITAL INI           | PUT SIGNALS (PWM, SRE)                                            |                                                                                                             |      |      |     |      |  |  |

| V <sub>IH_PWM</sub>   | Positive-going input threshold voltage                            |                                                                                                             |      | 1.8  | 2   | V    |  |  |

| $V_{IL\_PWM}$         | Negative-going input threshold voltage                            |                                                                                                             | 0.80 | 0.90 |     | V    |  |  |

| PWM                   | Input voltage hysteresis, $(V_{IH} - V_{IL})$                     |                                                                                                             |      | 0.90 |     | V    |  |  |

| V <sub>IH_SRE</sub>   | Positive-going input threshold voltage                            |                                                                                                             |      | 1.5  | 1.7 | V    |  |  |

| $V_{IL\_SRE}$         | Negative-going input threshold voltage                            |                                                                                                             | 0.9  | 1.00 |     | V    |  |  |

| SRE                   | Input voltage hysteresis, (V <sub>IH</sub> – V <sub>IL</sub> )    |                                                                                                             |      | 0.45 |     | V    |  |  |

|                       | Input current                                                     | V <sub>PWM</sub> = 5 V                                                                                      |      | 140  |     |      |  |  |

| I <sub>PWM</sub>      |                                                                   | V <sub>PWM</sub> = 3.3 V                                                                                    |      | 70   |     | μΑ   |  |  |

|                       |                                                                   | V <sub>PWM</sub> = 0 V                                                                                      |      | -63  |     |      |  |  |

|                       |                                                                   | V <sub>SRE</sub> = 5 V                                                                                      |      | 190  |     |      |  |  |

| I <sub>SRE</sub>      | Input current                                                     | V <sub>SRE</sub> = 3.3 V                                                                                    |      | 12   |     |      |  |  |

|                       |                                                                   | V <sub>SRE</sub> = 0 V                                                                                      |      | -330 |     |      |  |  |

| t <sub>HLD_R</sub>    | 3-state hold-off time <sup>(1)</sup>                              | V <sub>PWM</sub> transition from 0 V to 1.65 V,<br>Time until V <sub>LS Gate</sub> falls to 0 V             | 450  | 600  | 750 | ns   |  |  |

| t <sub>HLD_R</sub>    | 3-state recovery time (1)                                         | V <sub>PWM</sub> transition from 1.65 V to 0 V,<br>Time until V <sub>LS Gate</sub> rises to V <sub>GG</sub> | 150  | 330  | 500 | ns   |  |  |

| t <sub>min</sub>      | PWM minimum pulse to force HS gate pulse <sup>(1)</sup>           | C <sub>L</sub> = 3 nF at HS gate, VPWM = 3.3 V                                                              | 50   |      |     | ns   |  |  |

|                       | PWM frequency <sup>(1)</sup>                                      | $Qg_{HS} + Qg_{LS} < 46 \text{ nC}, V_{GG} = 6.4 \text{ V}$                                                 |      |      | 2   | MHz  |  |  |

| OUTPUT CL             | JRRENT LIMIT (ILIM)                                               |                                                                                                             |      |      |     |      |  |  |

|                       | ILIM Input impedance <sup>(1)</sup>                               |                                                                                                             |      | 250  |     | kΩ   |  |  |

|                       | ILIM set point range <sup>(1)</sup>                               |                                                                                                             | 0.5  |      | 3   | V    |  |  |

|                       | FLT output high level                                             | I <sub>LOAD</sub> = -2 mA                                                                                   | 2.7  | 3.3  |     | V    |  |  |

|                       | FLT output low level <sup>(1)</sup>                               | I <sub>LOAD</sub> = 2 mA                                                                                    |      | 0.1  | 0.6 | V    |  |  |

| t <sub>FAULT_HS</sub> | Fault detection time. Delay until HS Gate falling. <sup>(1)</sup> | V <sub>(ILIM)</sub> = 1.50 V, (CSP – CSN) = 20 mV,<br>CSN = 1.80 V                                          |      | 100  | 150 | ns   |  |  |

| t <sub>FAULT_LS</sub> | Fault detection time. Delay until LS Gate rising. (1)             | V <sub>(ILIM)</sub> = 1.50 V, (CSP - CSN) = 20 mV,<br>CSN = 1.80 V                                          |      | 150  | 200 | ns   |  |  |

<sup>(1)</sup> As designed and characterized. Not 100% tested in production.

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{IN}$  = 12V, 4.7  $\mu F$  from  $V_{GG}$  to PGND, 1  $\mu F$  from BP3 to AGND, 0.22  $\mu F$  from BST to SW,  $T_A = T_J = -40^{\circ} C$  to 125°C,

RDLY =  $8.06k\Omega$ , SRE Mode = 3.3V,  $V_{GG}$  DIS tied to AGND (unless otherwise noted)

|                                     | PARAMETER                                                                              | TEST CONDITIONS                                                                                                                                       | MIN  | TYP  | MAX  | UNIT     |

|-------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----------|

| t <sub>FAULT_FLT</sub>              | Fault detection time. Delay until FLT asserted (2)                                     | $V_{(ILIM)} = 1.50 \text{ V}, (CSP - CSN) = 20 \text{ mV},$<br>CSN = 1.80  V                                                                          |      | 85   | 170  | ns       |

|                                     | Propagation delay from PWM to reset FLT <sup>(2)</sup>                                 | PWM falling to FLT falling after a current limit event is cleared. PWM pulse width ≥100 ns.                                                           |      | 85   | 200  | ns       |

| CURRENT SE                          | ENSE BLANKING (RDLY, HS Sense)                                                         |                                                                                                                                                       |      |      |      |          |

| I <sub>RDLY</sub>                   | RDLY source current                                                                    | $8.06~k\Omega$ resistor from RDLY to AGND                                                                                                             | 80   | 90   | 100  | μΑ       |

|                                     | RDLY resistance range <sup>(2)</sup>                                                   |                                                                                                                                                       | 7.5  | 8.06 | 10   | kΩ       |

| t <sub>BLANK</sub>                  | HS blanking time                                                                       | RDLY = 8.06 k $\Omega$ . From SW rising to HS fault comparator enabled                                                                                | 110  | 125  | 140  | ns       |

| I <sub>HS Sense</sub>               | HS Sense sink current                                                                  | $R_{HS \ Sense} = 2. \ k\Omega \ to \ V_{IN}, \ V_{IN} = 12 \ V$                                                                                      |      | 100  |      | μΑ       |

| t <sub>HSFAULT_HS</sub>             | HS fault detection time. Delay after $t_{\rm BLANK}$ until HS Gate falling $^{(2)}$    | RDLY = 8.06 k $\Omega$ , R <sub>HS Sense</sub> = 2 k $\Omega$ to V <sub>IN</sub> , V <sub>IN</sub> = 12 V, V <sub>IN</sub> - V <sub>SW</sub> = 220 mV |      | 20   |      | ns       |

| t <sub>HSFAULT_LS</sub>             | HS fault detection time. Delay after $t_{\text{BLANK}}$ until LS Gate falling $^{(2)}$ | RDLY = 8.06 k $\Omega$ , R <sub>HS Sense</sub> = 2 k $\Omega$ to V <sub>IN</sub> , V <sub>IN</sub> = 12 V, V <sub>IN</sub> - V <sub>SW</sub> = 220 mV |      | 30   |      | ns       |

| CURRENT SE                          | ENSE AMPLIFER (I <sub>MON</sub> , CSP, CSN)                                            |                                                                                                                                                       |      |      |      |          |

|                                     | V(I <sub>MON</sub> ) at no load                                                        | CSP = CSN = 1.8 V                                                                                                                                     | 460  | 500  | 540  | mV       |

|                                     | Closed loop DC gain                                                                    | CSP - CSN = 10 mV; 0.5 V ≤ CSN ≤ 3.3 V                                                                                                                | 48   | 50.2 | 52.4 | V/V      |

|                                     |                                                                                        | Gain with 2.49k resistors in series with CSP, CSN                                                                                                     | 45.6 | 47.8 | 49.9 | V/V      |

|                                     | Input impedance (2)                                                                    | Differential, CSP – CSN                                                                                                                               |      | 100  |      | kΩ       |

| V <sub>CM</sub>                     | Input common mode voltage range <sup>(2)</sup>                                         | V <sub>CM</sub> (max) is limited to (V <sub>GG</sub> – 1.2 V)                                                                                         | -0.3 |      | 5.6  | V        |

| V(I <sub>MON</sub> ) <sub>MIN</sub> |                                                                                        | CSP = 1.2 V; CSN = 1.3 V; I(I <sub>MON</sub> ) = -250 μA                                                                                              |      | 0.1  | 0.15 | V        |

| V(I <sub>MON</sub> ) <sub>MAX</sub> |                                                                                        | CSP = 1.3 V; CSN = 1.2 V; I(I <sub>MON</sub> ) = 500 μA                                                                                               | 3    | 3.2  | 3.3  | V        |

|                                     | Sampling Rate <sup>(2)</sup>                                                           |                                                                                                                                                       |      | 5    |      | Msps     |

| LOW-SIDE O                          | UTPUT DRIVER (LS Gate)                                                                 |                                                                                                                                                       |      |      |      |          |

|                                     | Peak Source Current <sup>(2)</sup>                                                     | V <sub>GG</sub> = 6.2 V, PWM = Low, LS Gate = 3 V                                                                                                     |      | 6    |      | Α        |

|                                     | Peak Sink Current (2)                                                                  | $V_{GG} = 6.2 \text{ V}$ , PWM = High, LS Gate = 3 V                                                                                                  |      | 6    |      | Α        |

| t <sub>RL</sub>                     | Rise Time <sup>(2)</sup>                                                               | $C_L = 6 \text{ nF}, V_{IN} = 12 \text{ V}, V_{GG} = 6.2 \text{ V}$                                                                                   |      | 30   |      | ns       |

| t <sub>FL</sub>                     | Fall Time <sup>(2)</sup>                                                               | $C_L = 6 \text{ nF}, V_{IN} = 12 \text{ V}, V_{GG} = 6.2 \text{ V}$                                                                                   |      | 20   |      | ns       |

| YL.                                 | Output with V <sub>GG</sub> <uvlo <sup="">(2)</uvlo>                                   | $V_{GG} = 1 \text{ V, Isink} = 10 \text{ mA}$                                                                                                         |      | 0    | 0.5  | V        |

|                                     | Propagation Delay from PWM to LS Gate <sup>(2)</sup>                                   | $V_{GG} = 1$ V, ISHIK = 10 HIA<br>$C_L = 3$ nF, PWM falling SW = 0 V, $V_{GG} = 6.2$ V                                                                |      | 46   | 0.5  |          |

| HICH CIDE O                         |                                                                                        | CL = 3 IIF, FWW Idilling SW = 0 V, VGG = 0.2 V                                                                                                        |      | 40   |      | ns       |

| nign-Side O                         | Source current <sup>(2)</sup>                                                          | V <sub>IN</sub> = 12 V, BST = 6.2 V, PWM = High,<br>HS Gate = 3 V                                                                                     |      | 4    |      | A        |

|                                     | Sink current <sup>(2)</sup>                                                            | V <sub>IN</sub> = 12 V, BST = 6.2 V, PWM = Low,<br>HS Gate = 3 V                                                                                      |      | 4    |      | A        |

| •                                   | Rise time (2)                                                                          | $C_L = 3 \text{ nF HS Gate to SW}, V_{GG} = 6.2 \text{ V}$                                                                                            |      | 27   |      |          |

| t <sub>RH</sub>                     | Fall time (2)                                                                          | $C_L = 3$ nF HS Gate to SW, $V_{GG} = 0.2$ V<br>$C_L = 3$ nF HS Gate to SW, $V_{GG} = 6.2$ V                                                          |      | 21   |      | ns<br>ns |

| t <sub>FH</sub>                     | Propagation delay from PWM to HS Gate <sup>(2)</sup>                                   | $C_L = 3$ III 1/3 Gate to SW, $V_{GG} = 0.2$ V $C_L = 3$ nF HS Gate to SW, PWM rising, $SW = 0$ V, $V_{GG} = 6.2$ V                                   |      | 50   |      | ns       |

| SWITCHING 1                         | TIME                                                                                   | J. J., V.G. – V.Z. V                                                                                                                                  |      |      |      |          |

|                                     | HS gate turn-off propagation delay <sup>(2)</sup>                                      | C <sub>L</sub> = 3 nF                                                                                                                                 |      | 16   |      | ns       |

| t <sub>DLH</sub>                    | LS gate turn-off propagation delay <sup>(2)</sup>                                      |                                                                                                                                                       |      | 15   |      |          |

| t <sub>DLL</sub>                    | Dead time LS; Gate off to HS; Gate on <sup>(2)</sup>                                   | C <sub>L</sub> = 3 nF<br>C <sub>L</sub> = 3 nF                                                                                                        |      | 12   |      | ns       |

| t <sub>DTH</sub>                    | Dead time LS; Gate off to LS; Gate on <sup>(2)</sup>                                   |                                                                                                                                                       |      |      |      | ns       |

| t <sub>DTL</sub>                    |                                                                                        | C <sub>L</sub> = 3 nF                                                                                                                                 |      | 15   |      | ns       |

| BOOTSTRAP                           |                                                                                        | Forward him ourrent 400 m/s                                                                                                                           |      | 0.4  |      |          |

| V <sub>F</sub>                      | Forward voltage (2)                                                                    | Forward bias current 100 mA                                                                                                                           |      | 0.4  |      | V        |

| THERMAL SH                          |                                                                                        |                                                                                                                                                       | 455  | 405  | 475  |          |

|                                     | Rising threshold <sup>(2)</sup>                                                        |                                                                                                                                                       | 155  | 165  | 175  | °C       |

|                                     | Falling threshold <sup>(2)</sup>                                                       |                                                                                                                                                       | 135  | 145  | 155  | °C       |

|                                     | Hysteresis <sup>(2)</sup>                                                              |                                                                                                                                                       | 1    | 20   |      | °C       |

<sup>(2)</sup> As designed and characterized. Not 100% tested in production.

# **PIN FUNCTIONS**

|        | PIN                 | .,_ | FINICEIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|--------|---------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| QFN-20 | NAME                | 1/0 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 1      | HS Sense            | I   | High-side current fault threshold set pin. A resistor is connected from this pin directly to the drain of the high-side FET. The voltage drop across this resistor sets the maximum voltage drop allowed across the high-side FET after the blanking time set by RDLY. Exceeding this threshold will assert FLT and truncate the HS Gate pulse. This pin sinks a constant 100µA of current.                                                                                                                                                       |  |  |  |  |

| 2      | FLT                 | 0   | Fault Flag. The FLT signal is a 3.3v digital output which is asserted high when an over-current, over-temperature, or UVLO fault is detected. After an over-current event is detected, the flag is reset low on the falling edge of the next PWM pin, provided the over-current condition is no longer detected during the on-time of the PWM signal. For UVLO and over-temperature faults, the flag is reset when the fault condition is no longer present.                                                                                      |  |  |  |  |

| 3      | SRE Mode            | I   | Synchronous Rectifier Enable Mode select pin. When high, the high-side and low-side gate drive timing is controlled by the PWM pin. Anti-cross-conduction logic prevents simultaneous application of high-side and low-side gate drive. When low, independent operation of the high-side and low-side gate is selected. The high-side gate is directly controlled by the PWM signal. The low-side gate is directly controlled by the SRE signal. No anti-cross-conduction circuitry is active in this mode. This pin should not be left floating. |  |  |  |  |

| 4      | SRE                 | I   | Synchronous Rectifier Enable or Low-Side Input. This pin is a digital input capable of accepting 3.3V or 5V logic level signals. A Schmitt trigger input comparator desensitizes this pin from external noise. When SRE Mode is high, this signal, when low, disables the synchronous rectifier FET. The LS Gate signal is held off. When SRE Mode is high, this signal, when high, allows the LS Gate signal to function according to the state of the PWM pin. When SRE Mode is low, this pin is a direct input to the LS Gate driver.          |  |  |  |  |

| 5      | ILIM                | I   | Output current limit threshold set pin. The voltage on this pin sets the fault threshold voltage on the $I_{MON}$ pin. The nominal threshold voltage range is 0.5 V to 3.0 V. When $V(I_{MON})$ exceeds $V_{(ILIM)}$ , the FLT pin is asserted and the HS Gate pulse is truncated.                                                                                                                                                                                                                                                                |  |  |  |  |

| 6      | I <sub>MON</sub>    | 0   | Current Sense Linear Amplifier Output. The output voltage level on this pin represents the average output current. $V(I_{MON}) = 0.5 \text{ V} + 50.2 \text{ (V(CSP)} - V_{(CSN)})$ .                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 7      | CSN                 | 1   | Inverting input of the output current sense amplifier and current limit comparator.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 8      | CSP                 | ı   | Non-inverting input of the output current sense amplifier and current limit comparator.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 9      | BP3                 | 0   | Bypass capacitor for internal 3.3V supply. Connect a 1µF (minimum) ceramic capacitor from this pin to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 10     | PWM                 | I   | PWM input. This pin is a digital input capable of accepting 3.3 V or 5 V logic level signals. A Schmitt trigger input comparator desensitizes this pin from external noise. When SRE Mode is high, this pin controls both gate drivers. When SRE Mode is low, this pin only controls the high-side driver. This pin can detect when the input drive signal has switched to a high impedance (3-state) mode. When the high impedance mode is detected, both the HS Gate and LS Gate signals are held low.                                          |  |  |  |  |

| 11     | RDLY                | I   | Requires a resistor to AGND for setting the Current Sense blanking time for the high-side current sense comparator and output current limit circuitry.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 12     | AGND                | -   | Analog ground return for all circuits except the LS Gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 13     | V <sub>GG</sub> DIS | I   | $V_{GG}$ Disable pin. When pulled high, the on-chip $V_{GG}$ linear regulator is disabled. When disabled, an externally supplied gate voltage must be connected to the $V_{GG}$ pin. Connect this pin to AGND to use the on-chip regulator.                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 14     | PGND                | -   | Power Ground pin. This pin provides a return path for the low-side gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 15     | LS Gate             | 0   | The Low-Side high-current driver output. Drives the gate of the low-side synchronous MOSFET between $V_{\text{GG}}$ and PGND.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 16     | Vin                 | ı   | Input Voltage to the buck power stage and driver circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 17     | $V_{GG}$            | I/O | Gate Drive voltage supply. When $V_{GG}$ DIS is low, $V_{GG}$ is generated by an on-chip linear regulator. Nominal output voltage is 6.2 V. When $V_{GG}$ DIS is high, an externally supplied gate voltage can be applied to this pin. Connect a 4.7 $\mu$ F capacitor from this pin to PGND.                                                                                                                                                                                                                                                     |  |  |  |  |

| 18     | BST                 | I/O | Floating bootstrap supply for high side driver. Connect the bootstrap capacitor between this pin and the SW node. The bootstrap capacitor provides the charge to turn on the high-side MOSFET.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 19     | HS Gate             | 0   | The High-Side high-current driver output. Drives the gate of the high side buck MOSFET between BST and SW.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 20     | SW                  | I/O | Switching node connection to buck inductor. This pin provides a return path for the high-side gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| PP     | PAD                 | _   | Power Pad. Connect directly to AGND for better thermal performance and EMI reduction.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

#### DETAILED DESCRIPTION

#### **GENERAL**

The UCD7232 is designed primarily to be a synchronous buck driver with current measurement and fault detection capabilities that make it an ideal partner with digital power controllers. This device incorporates two high-current gate drive stages and sophisticated current measurement circuitry that allows for the monitoring and reporting of output load current. Two separate fault detection blocks protect the power stage from excessive load current or short circuits. On-chip thermal shutdown protects the device in case of severe over-temperature conditions. Detected faults immediately truncate the power conversion cycle in progress, without controller intervention, and assert a digital fault flag (FLT). Gate drive voltage is supplied by an on-chip linear regulator. If desired, this regulator can be disabled and an external gate drive voltage can be supplied. Mode selection pins allow the device to be used in synchronous mode or independent mode. In synchronous mode, the high-side and low-side gate timing is controlled by a single PWM input. Anti-cross-conduction dead-time intervals are applied automatically to the gate drives. In independent mode, the high-side and low-side gate drive signals are controlled directly by the PWM and SRE pins. The automatic dead-time logic is disabled in this mode. When operating in synchronous mode, the use of the low-side FET can be disabled under the control of the SRE pin. This feature facilitates start-up into a pre-bias voltage and is also used in some applications to reduce power consumption at light loads.

#### **PWM INPUT**

The PWM input pin accepts the digital signal from the controller that represents the desired high-side FET on-time duration. This input is designed to accept 3.3V logic levels, but is also tolerant of 5V input levels. The SRE Mode pin sets the behavior of the PWM pin. When the SRE Mode pin is asserted high, the device is placed in synchronous mode. In this mode, the timing duration of the high-side gate drive and the low-side gate drive are both controlled PWM input signal. When PWM is high, the high-side gate drive (HS Gate) is on and the low-side gate drive (LS Gate) is off. When PWM is low, the high-side gate drive is off and the low-side gate drive is on. Automatic anti-cross-conduction logic monitors the gate to source voltage of the FETs to verify that the proper FET is turned off before the other FET is turned on. When the SRE Mode pin is asserted low, the device is placed in independent mode. In this mode the PWM input only controls the high-side gate drive. When PWM is high, the high-side gate drive is on. The low side FET in independent mode is directly controlled by the SRE pin. No anti-cross-conduction logic is active in independent mode. The user must insure that the PWM and SRE signals do not overlap.

The PWM input supports a 3-state detection feature. It can detect if the PWM input signal has entered a 3-state mode. When 3-state mode is detected, both the high-side and low-side gate drive signals are held off. To support this mode, the PMW input pin has an internal pull-up resistor of approximately  $50k\Omega$  to 3.3V. It also has a  $50k\Omega$  pull-down resistor to ground. During normal operation, the PWM input signal swings below 0.8V and above 2.5V. If the source driving the PWM pin enters a 3-state or high impedance state, the internal pull-up/pull-down resistors will tend to pull the voltage on the PWM pin to 1.65V. If the voltage on the PWM pin remains within the 0.8V to 2.5V 3-state detection band for longer than the  $t_{HLD_R}$  3-state detection hold-off time, then the device enters 3-state mode and turns both gate drives off. This behavior occurs regardless of the state of the SRE Mode and SRE pins. When exiting 3-state mode, PWM should first be asserted low. This will insure that the bootstrap capacitor is recharged before attempting to turn on the high-side FET.

The logic threshold of this pin typically exhibits 900mV of hysteresis to provide noise immunity and insure glitch-free operation of the gate drivers.

#### **SRE INPUT**

The SRE (Synchronous Rectifier Enable) pin is a digital input with an internal  $10k\Omega$  pull-up resistor to 3.3V. It is designed to accept 3.3V logic levels, but is also tolerant of 5V levels. The SRE Mode pin sets the behavior of the SRE pin. When the SRE Mode pin is asserted high, the device is placed in synchronous mode. In this mode, the input, when asserted high, enables the operation of the low-side synchronous rectifier FET. The state of the low-side gate drive signal is governed by the PWM input. When SRE is asserted low while in synchronous mode, the low-side FET gate drive is continuously held low, keeping the FET off. While held off, current flow in the low-side FET is restricted to its intrinsic body diode. When the SRE Mode pin is asserted low, the device is placed in independent mode. In this mode, the state of the low-side gate drive signal follows the state of the SRE signal. It is completely independent of the state of the PWM signal. No anti-cross-conduction logic is active in independent mode. The user must insure that the PWM and SRE signals do not overlap.

The logic threshold of this pin typically exhibits 450mV of hysteresis to provide noise immunity and insure alitch-free operation of the low-side gate driver.

#### **SRE MODE**

The SRE Mode pin is a digital input designed to accept 3.3V logic levels, but is also tolerant of levels up to 5V. This pin sets the operational mode on the device. When asserted high, the device will be placed in synchronous mode. In this mode the behavior of both the high-side and low-side gate drive signals are under the control of the PWM input. When asserted low, this pin configures the device for independent mode. In this mode the high-side FET is under the control of the SRE pin. The SRE Mode pin is designed to be permanently tied high or low depending on the power architecture being implemented. It is not intended to be switched dynamically while the device is in operation. This pin can be tied to the BP3 pin to always select synchronous mode.

# $V_{IN}$

$V_{IN}$  supplies power to the internal circuits of the device. The input power is conditioned by an internal linear regulator that provides the  $V_{GG}$  gate drive voltage. A second regulator that operates off of the  $V_{GG}$  rail produces an internal 3.3V supply that powers the internal analog and digital functional blocks. The BP3 pin provides access for a high frequency bypass capacitor on this internal rail. The  $V_{GG}$  regulator produces a nominal output of 6.2V. The output of the  $V_{GG}$  regulator is monitored by the Under-Voltage Lock-Out (UVLO) circuitry. The device will not attempt to produce gate drive pulses until the  $V_{GG}$  voltage is above the UVLO threshold. This insures that there is sufficient voltage available to drive the power FETs into saturation when switching activity begins. To use the internal  $V_{GG}$  regulator, the voltage on Vin should be at least 4.7V.

When performing power conversion with less than 4.7V on the  $V_{IN}$  pin, the gate drive voltage must be supplied externally. (See  $V_{GG}$  and  $V_{GG}$  DIS sections for details.)

#### $V_{GG}$

The  $V_{GG}$  pin is the gate drive voltage for the high current gate drivers stages. The voltage on this pin can be supplied internally by the on-chip regulator, or it can be externally supplied by the user. When using the internal regulator, the  $V_{GG}$  DIS pin should be tied low. When an external source of  $V_{GG}$  is to be used, the  $V_{GG}$  DIS pin must be tied high. Current is drawn from the  $V_{GG}$  supply in fast, high-current pulses. A 4.7 $\mu$ F ceramic capacitor should be connected from the  $V_{GG}$  pin to the PGND pin as close as possible to the package.

Whether internally or externally supplied, the voltage on the  $V_{GG}$  pin is monitored by the UVLO circuitry. The voltage must be higher than the UVLO threshold before power conversion can occur. Note that the FLT pin is asserted high when  $V_{GG}$  is below the UVLO threshold.

The average current drawn from the  $V_{GG}$  supply is dependant on the switching frequency and the total gate charge of the power FETs connected to the driver. This current can be significant and is a major contributor to the overall power dissipation of the driver. The total gate charge (Qg) is a function of the value of  $V_{GG}$  and the power FET construction. A value for Qg can be obtained from the FET manufacturer's data sheet. A graph of Qg vs  $V_{GS}$  is usually supplied. Use the value of  $V_{GG}$  as the  $V_{GS}$  value and read the corresponding value of Qg. A value of Qg should be obtained for both the high-side and low-side FETs.

To keep the current draw from the  $V_{GG}$  supply within its capability, the switching frequency of the power stage should be limited to the following:

$$\mathsf{F}_{\mathsf{sw}(\mathsf{max})} = \frac{92000}{\mathsf{Qg}_{\mathsf{HS}} + \mathsf{Qg}_{\mathsf{LS}}} \tag{1}$$

Where  $F_{sw(max)}$  is the maximum switching frequency in kHz,  $Qg_{HS}$  is the gate charge of the high-side FET measured at  $V_{GS} = 6.2V$ , and  $Qg_{LS}$  is the total gate charge of the low-side FET(s) measured at  $V_{GS} = 6.2V$ , both specified in nanocoulombs (nC). Selecting FETs with lower gate charge will permit higher operating frequencies. The formula above allows for a maximum of 92mA of total gate drive current. An additional 8mA is consumed by the remaining circuitry within the device.

The average gate drive current, in mA, can be calculated from the following equation (with switching frequency in kHz and charge in nC):

$$I_{GATE\ AVE} = (Qg_{HS} + Qg_{LS}) \times Fsw \times 1000 \tag{2}$$

Assuming  $V_{GG} = 6.2V$  and Fsw = 500kHz, a typical Qg for a low-side FET is 50nC. A typical high-side FET Qg is 13nC. This combination creates an  $I_{GATE\_AVE}$  of 31.5mA. If the switching frequency was doubled, the current draw would double to 63mA. If  $V_{IN} = 12V$  and the internal  $V_{GG}$  linear regulator is being used, the power dissipation in the  $V_{GG}$  regulator, for this case, at 500kHz operation, is 183mW. At 1MHz, it increases to 365mW. Keep in mind that this is not the total power dissipation of the driver, only the portion dissipated in the  $V_{GG}$  regulator. Good thermal layout techniques are required for this device.

# $V_{GG}$ DIS

This pin, when asserted high, disables the on-chip  $V_{GG}$  linear regulator. When tied low, the  $V_{GG}$  linear regulator is used to derive  $V_{GG}$  from  $V_{IN}$ . This pin is designed to be permanently tied high or low depending on the power architecture being implemented. It is not intended to be switched dynamically while the device is in operation.

#### **SW**

The SW pin connects to the switching node of the power conversion stage. It acts as the return path for the high-side gate driver. When configured as a synchronous buck stage, the voltage swing on SW normally traverses from below ground to well above  $V_{\text{IN}}$ . A power Schottky diode should be connected from this pin to PGND to clamp the negative voltage swing on this pin to less than 1V. A series  $1\Omega$  resistor connects this pin to the actual switching node. It acts as a current limiting resistor when the Schottky diode is clamping negative voltage swings. The diode should be rated for at least 0.5A of current and exhibit a breakdown voltage of at least 30V. Small-signal Schottky diodes should not be used.

Parasitic inductance in the high-side FET and the output capacitance (Coss) of both power FETs form a resonant circuit that can produce high frequency (>100MHz) ringing on this node. The voltage peak of this ringing, if not controlled, can exceed twice  $V_{IN}$ . Care must be taken to not allow the peak ringing amplitude to exceed twice the value of the input voltage, even if that voltage amplitude is within the Absolute Maximum rating limit for the pin. In many cases, a series resistor and capacitor snubber network connected from the switching node to PGND can be helpful in damping the ringing and decreasing the peak amplitude. It is recommended that provisions for snubber network components be provided during the layout of the printed circuit board. If testing reveals that the ringing amplitude at the SW pin exceeds twice  $V_{IN}$ , then the snubber components need to be populated.

#### **BST**

The BST pin provides the drive voltage for the high-side FET. A bootstrap capacitor is connected from this pin to the SW node. Internally, a diode connects the BST pin to the  $V_{GG}$  supply. In normal operation, when the high-side FET is off and the low-side FET is on, the SW node is pulled to ground and, thus, holds one side of the bootstrap capacitor at ground potential. The other side of the bootstrap capacitor is clamped by the internal diode to  $V_{GG}$ . The voltage across the bootstrap capacitor at this point is the magnitude of the gate drive voltage available to switch-on the high-side FET. The bootstrap capacitor should be a low ESR ceramic type, with a recommended minimum value of  $0.22\mu F$ . A minimum voltage rating of 16V or higher is recommended.

### **HS GATE**

The HS Gate signal directly drives the gate of the high-side power FET. It provides high current drive to charge the gate capacitance of the FET rapidly to insure that it makes the transition from off to on as quickly as possible to minimize switching losses. When commanded on, the HS Gate is driven to the BST pin potential. As the FET begins to turn on, the SW will quickly rise to the  $V_{IN}$  potential. This voltage swing is coupled by the bootstrap capacitor to the BST pin. The net result is that the BST pin voltage, and thus the HS Gate voltage, is always equal to  $V_{SW} + V_{GG}$ . As the FET gate charges, the current return path for the driver is provided by the SW pin. When the HS Gate is commanded off, the driver pulls the pin to the SW potential. As the FET turns off, the SW pin will swing quickly to slightly below ground. Once again, this voltage swing is coupled to the BST pin by the bootstrap cap. The HS Gate circuitry is referenced to the SW pin and floats with the SW signal swing. The circuitry loop from the HS Gate pin to the gate of the FET and from the source of the high-side FET to the SW pin should kept as small and tight as possible to limit stray inductance. Likewise, the loop from the BST pin to the bootstrap capacitor and back to the SW pin should be kept small and tight.

#### **LS GATE**

The LS Gate signal directly drives the gate of the low-side power FET. It provides high current drive to quickly charge the gate capacitance of the FET, which is often considerably larger than the high-side FET. When commanded on, the LS Gate is driven to the  $V_{GG}$  pin potential. The current return path for the driver is provided by the PGND pin. When commanded off, the LS Gate pin is driven to the PGND potential. The traces from the LS Gate and the PGND pins to the low-side FET gate and source pins should be short and wide to minimize parasitic inductance and resistance.

# CSP, CSN

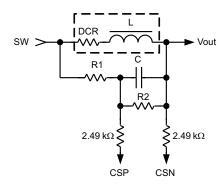

These pins are the input to the differential current sense amplifier. The Current Sense Positive (CSP) pin connects to the non-inverting input, the Current Sense Negative (CSN) connects to the inverting input. This amplifier provides the means to monitor and measure the output current of the power stage. The circuitry can be used with a discrete, low value, series current sense resistor, or can make use of the popular inductor DCR sense method.

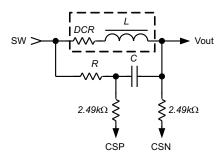

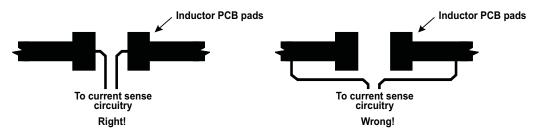

The DCR method is illustrated in Figure 3. A series resistor and capacitor network is added across the buck stage power inductor. It can be shown that when the value of L/DCR is equal to RC, then the *voltage* developed across the capacitor, C, is a replica of the voltage waveform the *ideal current* would induce in the dc resistance (DCR) of the inductor. This method does *not* detect changes in current due to changes in inductance value caused by saturation effects. The value used for C should be in the 0.1µF to 2.2µF range. This keeps the impedance of the sense network low, which reduces its susceptibility to noise pickup from the switching node. The trace lengths of the CSP and CSN signals should be kept short and parallel. To aid in rejection of high frequency common-mode noise, a series 2.49k resistor should be added to both the CSP and CSN signal paths, with the resistors being placed close to the pins at the package. This small amount of additional resistance slightly lowers the current sense gain.

Power inductors are selected for the lowest possible DCR to minimize losses. Typical DCR values range from  $0.5m\Omega$  to  $5m\Omega$ . With a load current of 20A, the voltage presented across the CSP and CSN pins is only in the range of 10mV to 100mV. Keep in mind that this small differential signal is riding on a large common mode signal that is the dc output voltage. This makes the current sense signal challenging to process.

Figure 3. DCR Current Sense

The UCD7232 uses switched capacitor technology to perform the differential to single-ended conversion of the sensed current signal. This technique offers excellent common mode rejection. The differential CSP-CSN signal is amplified by a factor of 97.8 and then a fixed 500mV pedestal voltage is added to the result. This signal is presented to the  $I_{MON}$  pin.

When using inductors with DCR values of  $2m\Omega$  or higher, it may be necessary to attenuate the input signal to prevent saturation of the current sense amplifier. This is easily accomplished through the addition of resistor R2 as shown in Figure 4.

Figure 4. Attenuating the DCR Sense Signal

The amount of attenuation is equal to R2/(R1 + R2). The equivalent resistance value to use in the L/DCR = RC formula is the parallel combination of R1 and R2. Thus, when using the circuit of Figure 4,

$$L/DCR = C \times R1 \times R2/(R1 + R2) \tag{3}$$

# I<sub>MON</sub>

The  $I_{MON}$  signal is a voltage proportional to the output current delivered by the power stage. The voltage magnitude obeys the following equation when using the circuit of Figure 3. This equation takes into account the gain reduction caused by the series 2.49k resistors.

$$V(I_{OLIT}) = 0.5 + 47.8 \times DCR \times I_{LOAD} \tag{4}$$

If the calculated value of  $V(I_{MON})$  exceeds the range of the analog-to-digital converter (ADC) or, if used, the maximum fault comparator threshold limit of a controller monitoring this voltage, then the circuit of Figure 4 should be used. When using the circuit of Figure 4, the voltage on  $I_{MON}$  obeys this modified equation:

$$V(I_{OUT}) = 0.5 + 47.8 \times DCR \times I_{LOAD} \times \left(\frac{R2}{R1 + R2}\right)$$

(5)

In either case, the output voltage is 500mV at no load. Current that is sourced to the load causes the  $I_{MON}$  voltage to rise above 500mV. Current that is forced into the power stage (sinking current) is considered "negative" current and will cause the  $I_{MON}$  voltage to fall below 500mV. The usable dynamic range of the  $I_{MON}$  signal is approximately 100mV to 3.1V. Keep in mind that this signal swing could exceed not just the maximum range of an analog to digital converter (ADC) that may be used to read or monitor the  $I_{MON}$  signal, but also the maximum programmable limit for the fault OC threshold. For example, the UCD92xx family of digital controllers has maximum limit of 2.5V for the ADC converter and 2.0V for the fault OC threshold, even though the input pin can tolerate voltages up to 3.3V.

The  $I_{MON}$  voltage is internally fed to the non-inverting input of the output over-current fault comparator. Good practice dictates that the over-current threshold should be set at approximately 150% of the rated power stage output current plus one half of the peak-to-peak inductor ripple current. This mandates that the  $I_{MON}$  signal should remain within its linear dynamic range at this threshold load current level. This requirement may force the use of the attenuation circuit of Figure 4. Note that the  $I_{MON}$  voltage (that goes to the output over-current fault comparator) is held during the blanking interval set by the resistor on the RDLY pin. This means that the  $I_{MON}$  pin will not reflect output current changes during the blanking interval, and that a fault will not be flagged until the blanking interval terminates.

### **ILIM**

The ILIM pin feeds the inverting input of the output over-current fault comparator. The voltage applied to this pin sets the over-current fault threshold. When the voltage on the  $I_{MON}$  pin exceeds the voltage on this pin, a fault is flagged. The voltage on this pin can be set by a voltage divider, a DAC, or by a filtered PWM output. The usable voltage range of the ILIM pin is approximately 0.6V to 3.1V. This represents the linear range of the  $I_{MON}$  signal for sourced output current. When using a voltage divider to set the threshold, a  $(0.01\mu\text{F})$  capacitor to BP3 can be added to improve noise immunity.

#### **RDLY**

The RDLY pin sets the blanking time of the high-side fault detection comparator. A resistor to AGND sets the blanking time according to the following formula, where  $t_{BLANK}$  is in nanoseconds and RDLY is in k $\Omega$ . Values of RDLY of greater than 25k $\Omega$  should not be used.

$$RDLY = \frac{t_{BLANK} - 33}{11.413} \tag{6}$$

To calculate the nominal blanking time for a given value of resistance, use the formula below.

$$t_{BLANK} = 11.413 \times RDLY + 33$$

(7)

The blanking interval begins on the rising edge of SW. During the blanking time the high-side fault comparator is held off. A high-side fault is flagged when the voltage drop across the high-side FET exceeds the threshold set by the HS Sense pin. Blanking is required because the high amplitude ringing that occurs on the rising edge of SW would otherwise cause false triggering of the fault comparator. The required amount of blanking time is a function of the high-side FET, the PCB layout, and whether or not a snubber network is being used. A value of 125ns is a typical starting point. An RDLY of  $8.06k\Omega$  will provide 125ns of blanking. The blanking interval should be kept as short as possible, consistent with reliable fault detection. The blanking interval sets the minimum duty cycle pulse width where high-side fault detection is possible. When the duty cycle of the PWM pulses are narrower than the blanking time, the high-side fault detection comparator is held off for the entire on-time and is, therefore, blind to any high-side faults.

Internally, the RDLY pin is fed by a  $90\mu A$  current source. When using the default value of  $8.06k\Omega$ , the voltage observed on the RDLY pin will be approximately 725mV.

#### **HS SENSE**

A resistor from the HS Sense pin to the drain of the high-side FET sets the high-side fault detection threshold. When the high-side FET is on, the current flow in the FET produces a voltage drop across the device. The magnitude of this voltage is equal to the  $R_{DS(ON)}$  times the current through the FET. An absolute maximum current level can be set during the design stage and the resultant voltage drop across the FET can be calculated. This maximum voltage drop,  $\Delta V_{MAX}$ , sets the high-side fault threshold.

Internally, a high speed comparator monitors the voltage between the SW pin and the HS Sense pin when the high-side FET is on. Whenever the voltage on the SW pin is lower than the voltage on the HS Sense pin, a fault is flagged. To prevent false tripping during the ringing that accompanies the rising edge of SW, the output of the comparator is held off (blanked) for a time interval set by the RDLY pin. The voltage on the HS Sense pin is set by a resistor connected from the pin to the high-side FET drain. The HS Sense resistor value is calculated from the following formula, where  $\Delta V_{MAX}$  is in mV, and  $R_{HS \ Sense}$  is in kilohms.

$$R_{HS Sense} = \Delta V_{MAX} / 100$$

(8)

For example, if  $\Delta V_{MAX}$  is 100mV, then  $R_{HS \ Sense}$  is 1k $\Omega$ .

The equation can be restated as follows, with  $R_{HS\ Sense}$  in kilohms,  $R_{DS(ON)}$  in milliohms, and  $I_{MAX}$  in amps:

$$R_{HS Sense} = R_{DS(ON)HOT} \times I_{MAX} / 100$$

(9)

The value of  $I_{MAX}$  should be set to approximately 150% of the expected maximum steady-state current. This allows some headroom to avoid nuisance fault events due to transient load currents and the inductor ripple current. Also, keep in mind that the  $R_{DS(ON)}$  of a FET has a large positive temperature coefficient of approximately 4000ppm/°C. The junction temperature of the FET will be elevated when operating at currents near the  $I_{MAX}$  threshold. In the equation above, use a value of  $R_{DS(ON)HOT}$  that is approximately 140% of its typical room temperature value. When using the internal  $V_{GG}$  gate drive supply, the FET, when turned on, is driven to a  $V_{GS}$  enhancement voltage of approximately 6V. Most FET data sheets provide  $R_{DS(ON)}$  values for  $V_{GS}$  values of 4.5V and 10V. Do not use the  $V_{GS}$  = 10V value for the room temperature  $R_{DS(ON)}$  value. Some manufacturers provide a graph of  $R_{DS(ON)}$  vs  $V_{GS}$ . If provided, use the  $V_{GS}$  = 6V value for the room temperature  $R_{DS(ON)}$  value.

A 100 $\mu$ A current sink pulls current through R<sub>HS Sense</sub>. This sets up a reference voltage drop equal to  $\Delta V_{MAX}$ . It is important to connect the far end of the R<sub>HS Sense</sub> resistor directly to the drain of the high-side FET. This should be made with a separate, non-current-carrying trace. This insures that only the R<sub>DS(ON)</sub> of the FET influences the fault threshold and not the resistance of the pc board traces.

#### **FLT**

The Fault Flag (FLT) is a digital output pin that is asserted when a significant fault is detected. It is meant to alert the host controller to an event that has interrupted power conversion. The FLT pin is held low in normal operation. When a fault is detected it is asserted high (3.3V). There are four events that can trigger the FLT signal: output over-current, high-side over-current, UVLO and thermal shutdown. The operation of the device during fault conditions is described in the Fault Behavior section. When asserted in response to an over-current fault, the FLT signal is reset low upon the falling edge of a subsequent PWM pulse, provided no faults are detected during the on-time of the pulse. If the fault is still present, the flag will remain asserted. When asserted in response to an UVLO or thermal shutdown event, the FLT pin will automatically de-assert itself when the UVLO or thermal event has passed. If the on-time of the PWM pulse is less than 100ns, then more than one pulse may be required to reset the flag.

#### BP3

The BP3 pin provides a connection point for a bypass capacitor that quiets the internal 3.3V voltage rail. Connect a 1µF (or greater) ceramic capacitor from this pin to analog ground. Do not draw current from this pin. It is not intended to be a significant source of 3.3V. It can, however, be used to as a source of 3.3V for an ILIM voltage divider and a tie point for the SRE Mode pin. Current draw should be limited to 100µA or less.

# **FAULT BEHAVIOR**

When faults are detected, the device reacts immediately to minimize power dissipation in the FETs and protect the system. The type of fault influences the behavior of the gate drive signals.

When a thermal shutdown fault occurs, both HS Gate and LS Gate are immediately forced low. They will stay low, regardless of the state of PWM and SRE, for the duration of the thermal shutdown.

A UVLO fault occurs when the voltage on the  $V_{GG}$  pin is less than the UVLO threshold. During this time both the HS Gate and LS Gate are driven low, regardless of the state of PWM and SRE. The fault is automatically cleared when the  $V_{GG}$  voltage rises above the UVLO threshold.

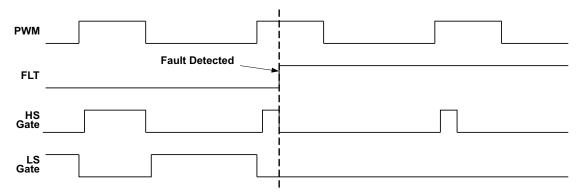

When either a high-side fault or an output over-current fault is detected, the FLT pin is asserted high, and both gate signals are immediately pulled low. During a high-side fault, a high-side gate pulse will be issued with each incoming PWM pulse. If the fault is still present, the HS Gate signal will again be truncated. This behavior repeats on a cycle-by-cycle basis until the fault is gone or the PWM input is held low. This behavior is illustrated in Figure 5.

Figure 5. High-Side Over-Current Fault Response

When a high-side fault and output over-current fault are detected concurrently, then both FET drives are immediately turned off and held off. If the output over-current fault is still present at the next PWM rising edge, then no HS Gate pulse will be issued and both gates will continue to be held off. Unlike the high-side fault detection circuitry, the output over-current fault circuitry is not reset on a cycle-by-cycle basis. The output current must fall below the over-current threshold before switching will resume.

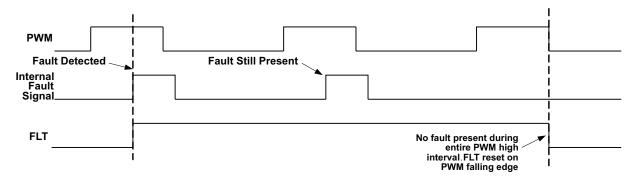

#### **FLT RESET**

With the exception of a UVLO fault or a thermal shutdown fault, the FLT flag, once asserted, is cleared by subsequent PWM pulses. The FLT flag will be cleared on the falling edge of the next PWM pulse, provided a fault condition is not asserted during the entire on-time of the PWM pulse. If a fault is present or detected during the on-time interval, the FLT pin will remain asserted. This behavior is illustrated in Figure 6.

Figure 6. FLT Reset Sequence

Whenever the voltage on the  $V_{GG}$  pin is below the UVLO falling threshold, as at the time of initial power-up, for example, the FLT pin will be asserted. When the voltage on the  $V_{GG}$  pin rises above the UVLO rising threshold, the FLT pin will be cleared automatically. This permits the FLT pin to be used as a "Power Not Good" signal at initial power-up to signify that there is insufficient gate drive voltage available to permit proper power conversion. When FLT goes low, it is an indication of "Gate Drive Power Good" and power conversion can commence. After initial power-up, the assertion of the FLT flag should be interpreted that power conversion has stopped or has been limited by a fault condition.

#### THERMAL SHUTDOWN

If the junction temperature exceeds approximately 165°C, the device will enter thermal shutdown. This will assert the FLT pin and both gate drivers will be turned off. When the junction temperature cools by approximately 20°C, the device will exit thermal shutdown. The FLT flag is reset upon exiting thermal shutdown.

Gate driver temperature will be strongly influenced by the switching frequency being used, the value of  $V_{IN}$  and  $V_{GG}$ , and the total capacitive load on the HS Gate and LS Gate pins. The driver junction temperature is not normally strongly affected by load current. However, a rise in the PCB substrate temperature due to load current induced power dissipation in nearby components will raise the junction temperature and contribute to a possible thermal shutdown event.

#### **APPLICATION INFORMATION**

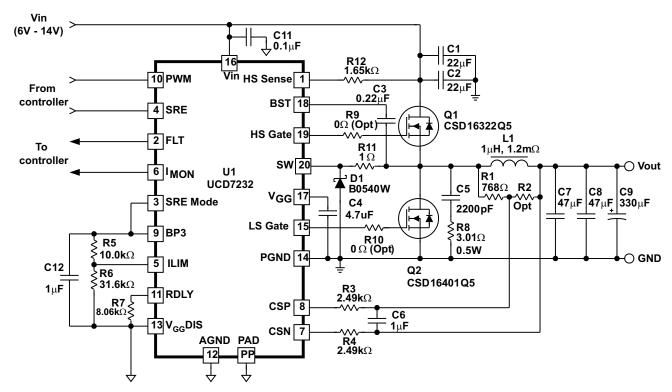

#### **EXAMPLE 20A POWER STAGE**

A partial schematic of a 20A power conversion stage designed for 500kHz operation is shown in Figure 7.

Figure 7. Example 20A Power Stage