## OMAP5912 Multimedia Processor Power Management Reference Guide

Literature Number: SPRU753A March 2004

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated

### **Read This First**

#### About This Manual

This document describes power management in the OMAP5912 multimedia processor.

#### **Notational Conventions**

This document uses the following conventions.

Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

#### Related Documentation From Texas Instruments

The following documents describe the OMAP5910 device and related peripherals. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

- OMAP5912 Multimedia Processor Device Overview and Architecture Reference Guide (literature number SPRU748) introduces the setup, components, and features of the OMAP5912 multimedia processor and provides a high-level view of the device architecture.

- OMAP5912 Multimedia Processor OMAP 3.2 Subsystem Reference Guide (literature number SPRU749) introduces and briefly defines the main features of the OMAP3.2 subsystem of the OMAP5912 multimedia processor.

- OMAP5912 Multimedia Processor DSP Sybsystem Reference Guide (literature number SPRU750) describes the OMAP5912 multimedia processor DSP subsystem. The digital signal processor (DSP) subsystem is built around a core processor and peripherals that interface with: 1) The ARM926EJS via the microprocessor unit interface (MPUI); 2) Various standard memories via the external memory interface (EMIF); 3) Various system peripherals via the TI peripheral bus (TIPB) bridge.

SPRU753A OMAP5912 3

- OMAP5912 Multimedia Processor Clocks Reference Guide (literature number SPRU751) describes the clocking mechanisms of the OMAP5912 multimedia processor. In OMAP5912, various clocks are created from special components such as the digital phase locked loop (DPLL) and the analog phase-locked loop (APLL).

- OMAP5912 Multimedia Processor Initialization Reference Guide (literature number SPRU752) describes the reset architecture, the configuration, the initialization, and the boot ROM of the OMAP5912 multimedia processor.

- OMAP5912 Multimedia Processor Power Management Reference Guide (literature number SPRU753) describes power management in the OMAP5912 multimedia processor. The ultralow-power device (ULPD) generates and manages clocks and reset signals to OMAP3.2 and to some peripherals. It controls chip-level power-down modes and handles chip-level wake-up events. In deep sleep mode, this module is still active to monitor wake-up events. This book describes the ULPD module and outline architecture.

- OMAP5912 Multimedia Processor Security Features Reference Guide (literature number SPRU754) describes the security features of teh OMAP5912 multimedia processor. The OMAP5912 security scheme relies on the OMAP3.2 secure mode. The distributed security on the OMAP3.2 platform is a Texas Instruments solution to address m-commerce and security issues within a mobile phone environment. The OMAP3.2 secure mode was developed to bring hardware robustness to the overall OMAP5912 security scheme.

- OMAP5912 Multimedia Processor Direct Memory Access (DMA) Support Reference Guide (literature number SPRU755) describes the direct memory access support of the OMAP5912 multimedia processor. The OMAP5912 processor has three DMAs:

- The system DMA is embedded in OMAP3.2. It handles DMA transfers associated with MPU and shared peripherals.

- The DSP DMA is embedded in OMAP3.2. It handles DMA transfers associated with DSP peripherals.

- The generic distributed DMA (GDD) is an OMAP5912 resource attached to the SSI peripheral. It handles only DMA transfers associated with the SSI peripheral.

4 OMAP5912 SPRU753A

# OMAP5912 Multimedia Processor Memory Interfaces Reference Guide (literature number SPRU756) describes the memory interfaces of the OMAP5912 multimedia processor.

- SDRAM (external memory interface fast, or EMIFF)

- Asynchronous and synchronous burst memory (external memory interface slow, or EMIFS)

- NAND flash (hardware controller or software controller)

- CompactFlash on EMIFS interface

- Internal static RAM

# OMAP5912 Multimedia Processor Interrupts Reference Guide (literature number SPRU757) describes the interrupts of the OMAP5912 multimedia processor. Three level 2 interrupt controllers are used in OMAP5912:

- One MPU level 2 interrupt handler (also referred to as MPU interrupt level 2) is implemented outside of OMAP3.2 and can handle 128 interrupts.

- One DSP level 2 interrupt handler (also referred to as DSP interrupt level 2.1) is instantiated outside of OMAP3.2 and can handle 64 interrupts.

- One OMAP3.2 DSP level 2 interrupt handler (referenced as DSP interrupt level 2.0) can handle 16 interrupts.

- OMAP5912 Multimedia Processor Peripheral Interconnects Reference Guide (literature number SPRU758) describes various periperal interconnects of the OMAP5912 multimedia processor.

- OMAP5912 Multimedia Processor Timers Reference Guide (literature number SPRU759) describes various timers of the OMAP5912 multimedia processor.

- OMAP5912 Multimedia Processor Serial Interfaces Reference Guide (literature number SPRU760) describes the serial interfaces of the OMAP5912 multimedia processor.

# OMAP5912 Multimedia Processor Universal Serial Bus (USB) Reference Guide (literature number SPRU761) describes the universal serial bus (USB) host on the OMAP5912 multimedia processor. The OMAP5912 processor provides several varieties of USB functionality. Flexible multiplexing of signals from the OMAP5912 USB host controller, the OMAP5912 USB function controller, and other OMAP5912 peripherals allow a wide variety of system-level USB capabilities. Many of the OMAP5912 pins can be used for USB-related signals or for signals from other OMAP5912 peripherals. The OMAP5912 top-level pin multiplexing

SPRU753A OMAP5912 5

controls each pin individually to select one of several possible internal pin signal interconnections. When these shared pins are programmed for use as USB signals, the OMAP5912 USB signal multiplexing selects how the signals associated with the three OMAP5912 USB host ports and the OMAP5912 USB function controller can be brought out to OMAP5912 pins.

- OMAP5912 Multimedia Processor Multi-channel Buffered Serial Ports (McBSPs) Reference Guide (literature number SPRU762) describes the three multi-channel buffered serial ports (McBSPs) available on the OMAP5912 device. The OMAP5912 device provides multiple high-speed multichannel buffered serial ports (McBSPs) that allow direct interface to codecs and other devices in a system.

- **OMAP5912 Multimedia Processor Camera Interface Reference Guide** (literature number SPRU763) describes two camera inerfaces implemented in the OMAP5912 multimedia processor: compact serial camera port and camera parallel interface.

- OMAP5912 Multimedia Processor Display Interface Reference Guide (literature number SPRU764) describes the display interface of the OMAP5912 multimedia processor.

- LCD module

- LCD data conversion module

- LED pulse generator

- Display interface

- OMAP5912 Multimedia Processor Multimedia Card (MMC/SD/SDIO) (literature number SPRU765) describes the multimedia card (MMC) interface of the OMAP5912 multimedia processor. The multimedia card/secure data/secure digital IO (MMC/SD/SDIO) host controller provides an interface between a local host, such as a microprocessor unit (MPU) or digital signal processor (DSP), and either an MMC or SD memory card, plus up to four serial flash cards. The host controller handles MMC/SD/SDIO or serial port interface (SPI) transactions with minimal local host intervention.

- OMAP5912 Multimedia Processor Keyboard Interface Reference Guide (literature number SPRU766) describes the keyboard interface of the OMAP5912 multimedia processor. The MPUIO module enables direct I/O communication between the MPU (through the public TIPB) and external devices. Two types of I/O can be used: specific I/Os dedicated for 8 x 8 keyboard connection, and general-purpose I/Os.

- OMAP5912 Multimedia Processor General-Purpose Interface Reference Guide (literature number SPRU767) describes the general-purpose in-

6 OMAP5912 SPRU753A

terface of the OMAP5912 multimedia processor. There are four GPIO modules in the OMAP5912. Each GPIO peripheral controls 16 dedicated pins configurable either as input or output for general purposes. Each pin has an independent control direction set by a programmable register. The two–edge control registers configure events (rising edge, falling edge, or both edges) on an input pin to trigger interrupts or wake–up requests (depending on the system mode). In addition, an interrupt mask register masks out specified pins. Finally, the GPIO peripherals provide the set and clear capabilities on the data output registers and the interrupt mask registers. After detection, all event sources are merged and a single synchronous interrupt (per module) is generated in active mode, whereas a unique wake–up line is issued in idle mode. Eight data output lines of the GPIO3 are ORed together to generate a global output line at the OMAP5912 boundary. This global output line can be used in conjunction with the SSI to provide a CMT–APE interface to the OMAP5912.

OMAP5912 Multimedia Processor VLYNQ Serial Communications Interface Reference Guide (literature number SPRU768) describes the VLYNQ of the OMAP5912 multimedia processor.

VLYNQ is a serial communications interface that enables the extension of an internal bus segment to one or more external physical devices. The external devices are mapped into local, physical address space and appear as if they are on the internal bus of the OMAP 5912. The external devices must also have a VLYNQ interface. The VLYNQ module serializes bus transactions in one device, transfers the serialized data between devices via a VLYNQ port, and de-serializes the transaction in the external device.

OMAP5912 includes one VLYNQ module connected on OCPT2 target port and OCPI initiator port. These connections are configured via a static switch, which selects either SSI or VLYNQ module. This switch, forbids the simultaneous use of GDD/SSI and VLYNQ. The switch is controlled by the VLYNQ\_EN bit in the OMAP5912 configuration control register (CONF\_5912\_CTRL).

OMAP5912 Multimedia Processor Pinout Reference Guide (literature number SPRU769) provides the pinout of the OMAP5912 multimedia processor. After power-up reset, the user can change the configuration of the default interfaces. If another interface is available on top of the default, it is possible to enable a new interface for each ball by setting the corresponding 3-bit field of the associated FUNC\_MUX\_CTRL register. It is also possible to configure on-chip pullup/pulldown. This document

SPRU753A OMAP5912 7

also describes the various power domains so that the user can apply the different interfaces seamlessly with external components.

OMAP5912 Multimedia Processor Window Tracer (WT) Reference Guide (literature number SPRU770) describes the window tracer module used to capture the memory transactions from four interfaces: EMIFF, EMIFS, OCP-T1, and OCP-T2. This module is located in the OMAP3.2 traffic controller (TC).

OMAP5912 Multimedia Processor Real-Time Clock Reference Guide (literature number SPRUxxx) describes the real-time clock of the OMAP5912 multimedia processor. The real-time clock (RTC) block is an embedded real-time clock module directly accessible from the TIPB bus interface.

#### **Trademarks**

OMAP and the OMAP symbol are trademarks of Texas Instruments.

8 *OMAP5912 SPRU753A*

# **Contents**

| 1 | Ultra | low-Power Device                                         |

|---|-------|----------------------------------------------------------|

|   | 1.1   | ULPD Features                                            |

|   | 1.2   | Overview                                                 |

|   | 1.3   | ULPD Input Clock Sources                                 |

|   | 1.4   | ULPD Setup Counters                                      |

|   | 1.5   | Power Modes                                              |

|   |       | 1.5.1 Deep Sleep Mode                                    |

|   |       | 1.5.2 Big Sleep Mode                                     |

|   |       | 1.5.3 Awake Mode                                         |

|   | 1.6   | External Clock and Voltage Supply Control                |

|   |       | 1.6.1 Behavior of LOW_PWR                                |

|   |       | 1.6.2 Behavior of LOW_PWR                                |

|   | 1.7   | Leakage Current Management                               |

|   | 1.8   | Low-Voltage Operation at Reduced Clock Frequency         |

|   | 1.9   | Transitions Between Power Modes                          |

|   | 1.10  | Power-on Transition to Deep Sleep Mode                   |

|   | 1.11  | Transitions From Deep Sleep Mode                         |

|   |       | 1.11.1 Transition from Deep Sleep to Big Sleep Mode      |

|   |       | 1.11.2 Transition from Deep Sleep to Awake Mode          |

|   | 1.12  | Transitions From Big Sleep Mode                          |

|   |       | 1.12.1 Transition From Big Sleep Mode to Deep Sleep Mode |

|   |       | 1.12.2 Transition From Big Sleep Mode to Awake Mode      |

|   | 1.13  | Transitions From Awake Mode                              |

|   |       | 1.13.1 Transition From Awake Mode to Deep Sleep Mode     |

|   |       | 1.13.2 Transition From Awake Mode to Big Sleep Mode      |

|   | 1.14  | ULPD Output Clocks                                       |

|   | 1.15  | Power-up and Reset Management                            |

|   |       | 1.15.1 Device Power up 4                                 |

|   |       | 1.15.2 Generic Power-up Sequence in Oscillator Mode      |

|   |       | 1.15.3 Power-up Sequence in External Clock Mode          |

|   | 1.16  | ULPD Reset Inputs                                        |

|   | 1.17  | OMAP3.2 Reset Generation                                 |

|   | 1.18  | OMAP3.2 Embedded LDO for DPLL[3] Control                 |

|   | 1.19  | Analog Phase-Locked Loop Control                         |

|   | 1.20  | Battery Failed Interrupt                                 |

SPRU753A OMPA5912 9

|   | 1.21 |          | z Oscillator Calibration                              |     |

|---|------|----------|-------------------------------------------------------|-----|

|   | 1.22 |          | evices                                                |     |

|   | 1.23 |          | Interrupt Generation                                  |     |

|   | 1.24 | ULPD     | Registers                                             | 50  |

| 2 |      | -        | m Overview                                            |     |

|   | 2.1  |          | Domains                                               |     |

|   | 2.2  | Clock I  | Domain                                                | 70  |

| 3 | Powe |          | gement User Services                                  |     |

|   | 3.1  |          | Services                                              |     |

|   | 3.2  | Static ( | Clock Management                                      |     |

|   |      | 3.2.1    | DPLL1 Clock                                           |     |

|   |      | 3.2.2    | DSP/MPU/TRAFFIC Clocks                                |     |

|   |      | 3.2.3    | DSP (MGS3) Clocks Management                          |     |

|   |      |          | Global Power Management                               |     |

|   |      |          | Local Power Management                                |     |

|   |      | 3.2.4    | RNG CLOCKS                                            |     |

|   |      |          | Total RNG Shutdown                                    |     |

|   |      |          | Partial RNG Shutdown: Input Clock Cut Off             |     |

|   |      |          | Total RNG Shutdown: Reset RNG Module                  |     |

|   |      | 3.2.5    | Externals Clocks                                      |     |

|   | 3.3  | Dynam    | nic Management                                        | 83  |

|   |      | 3.3.1    | Autogating Mechanisms                                 |     |

|   |      |          | OMAP3.2 Autogating                                    | 83  |

|   |      |          | OMAP5912 Peripherals Autogating                       | 83  |

|   |      |          | MGS3/DSP Autogating                                   |     |

|   | 3.4  | ULPD     | Power Modes Management                                | 85  |

|   |      | 3.4.1    | Introduction                                          | 85  |

|   |      | 3.4.2    | ULPD Mode Descriptions                                |     |

|   |      | 3.4.3    | ULPD Mechanisms Description                           |     |

|   |      | 3.4.4    | Control of External Clock and Voltage Supplies        |     |

|   |      | 3.4.5    | Transitions Between ULPD Modes                        |     |

|   | 3.5  | Power    | Domain Management                                     |     |

|   |      | 3.5.1    | RTC Domain Management                                 |     |

|   |      | 3.5.2    | DSP Domain Management                                 | 92  |

| 4 | Dyna |          | tage Scaling                                          |     |

|   | 4.1  |          | oltage With Chip Totally Shut Down                    |     |

|   |      | 4.1.1    | Oscillator Clock Mode                                 |     |

|   |      | 4.1.2    | External Clock Mode                                   |     |

|   | 4.2  | Low Vo   | oltage With Chip Running at Reduced Clock Frequencies | 95  |

| 5 | OMAI |          | Power Modes                                           |     |

|   | 5.1  | OMAP     | 5912 Power Mode Transitions                           | 97  |

| 6 | OMAI | P5912 P  | Power Management Software User Guide                  | 103 |

10 OMPA5912 SPRU753A

# **Figures**

| 1  | ULPD and Clock Domains in OMAP5912                          | 17 |

|----|-------------------------------------------------------------|----|

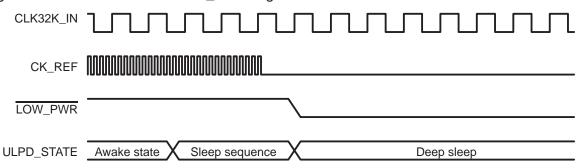

| 2  | Assertion of LOW_PWR                                        | 20 |

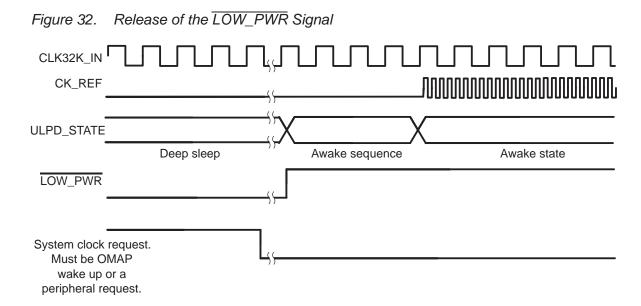

| 3  | Release of LOW_PWR                                          | 21 |

| 4  | Behavior of LOW_PWR in RESET_MODE 0                         | 22 |

| 5  | Control of OMAP5912 Low-Power Output by ULPD POWER_CTRL_REG | 23 |

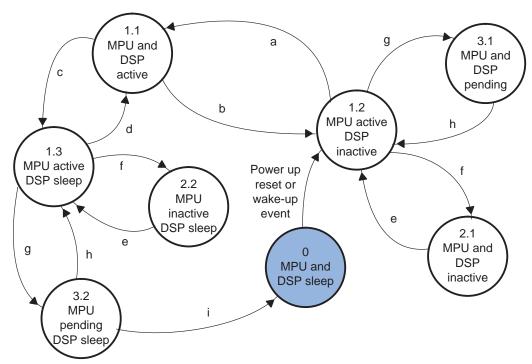

| 6  | Simplified State Diagram of the ULPD FSM1                   | 24 |

| 7  | 20MAP3.2-Initiated Wake-up Sequence                         | 30 |

| 8  | Wake-up Sequence in Case of Warm Reset                      | 31 |

| 9  | Sleep Sequence                                              | 33 |

| 10 | Basic Diagram of the ULPD Output and Input Clocks           | 35 |

| 11 | Timing Diagram for Clock Request to Clock Available Latency | 39 |

| 12 | Power-up Sequence in Oscillator Mode                        | 44 |

| 13 | Power-up Sequence in External Clock Mode                    | 45 |

| 14 | OMAP3.2 Input Reset Generation                              | 46 |

| 15 | ULPD_PLL Clock Management                                   | 47 |

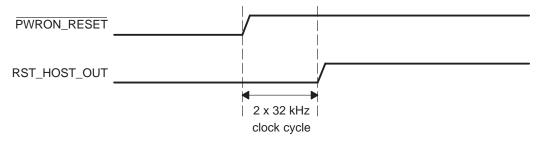

| 16 | RST_HOST_OUT Activation on PWRON_RESET                      | 48 |

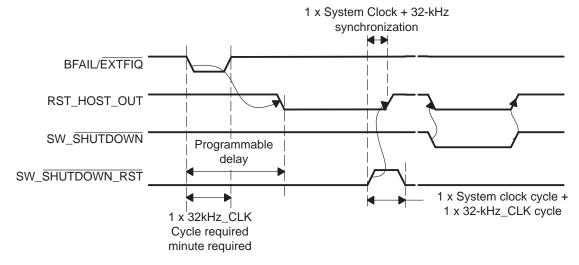

| 17 | RST_HOST_OUT Activation on BFAIL/EXTFIQ and SW_SHUTDOWN     | 48 |

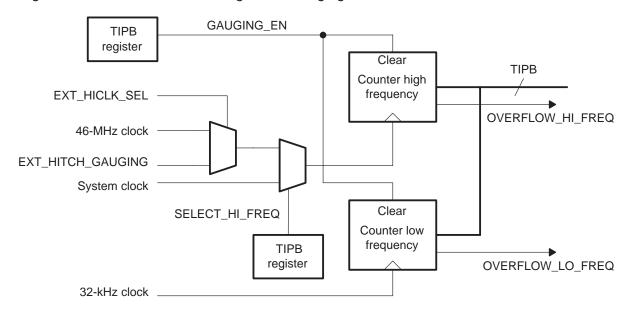

| 18 | Functional Block Diagram of Gauging                         | 49 |

| 19 | OMAP5912 Power Domains                                      | 69 |

| 20 | OMAP5912 Clock Domains                                      | 71 |

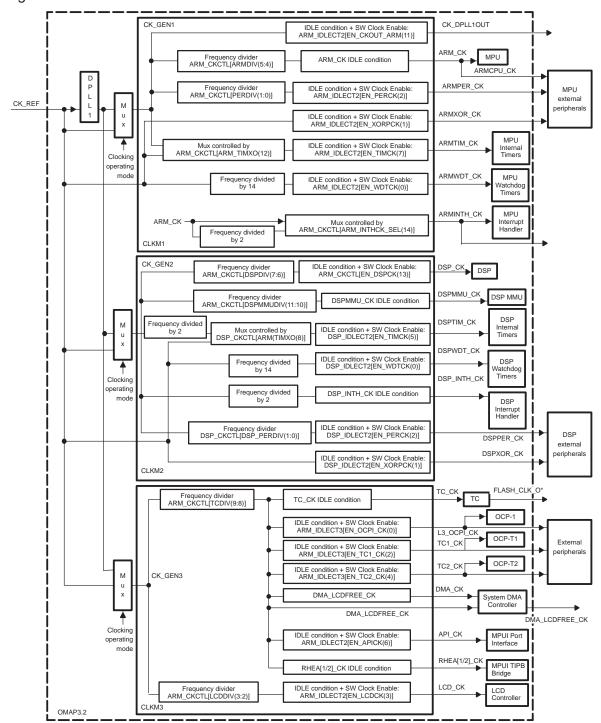

| 21 | OMAP3.2 Clock Generation                                    | 74 |

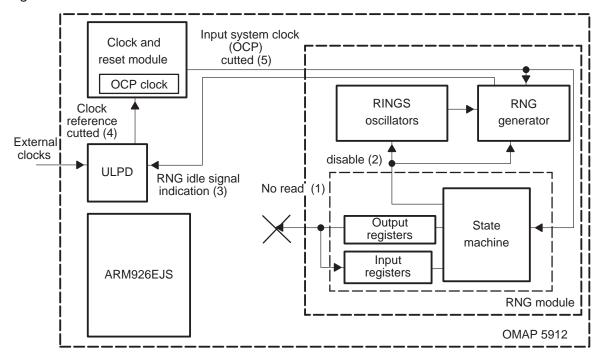

| 22 | Total Automatic RNG Shutdown                                | 81 |

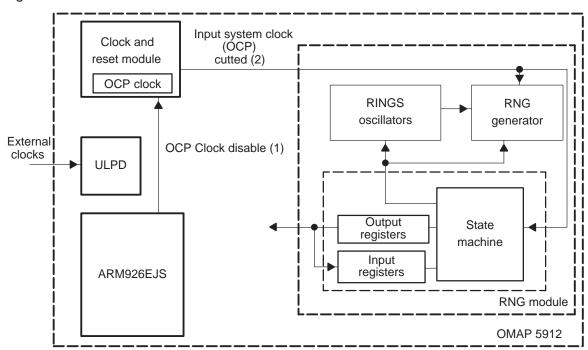

| 23 | Partial RNG Shut Down                                       | 82 |

| 24 | OMAP5912 Shutdown Request Management                        | 87 |

| 25 | OMAP5912 Wake-Up Management                                 | 88 |

| 26 | Software Control of the LOW_PWR Signal                      | 89 |

| 27 | Transition Flow                                             | 89 |

| 28 | OMAP 5912 State OFF                                         | 91 |

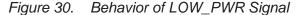

| 29 | OMAP 5912 State ON                                          |    |

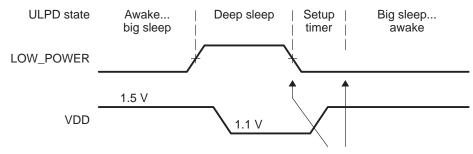

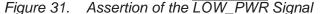

| 30 | Behavior of LOW_PWR Signal                                  | 94 |

| 31 | Assertion of the LOW_PWR Signal                             | 94 |

| 32 | Release of the LOW_PWR Signal                               | 95 |

| 33 | Power Mode Transitions                                      | 98 |

SPRU753A OMPA5912 11

# **Tables**

| 1  | Sleep Modes versus Active Mode (Summary)                         |    |

|----|------------------------------------------------------------------|----|

| 2  | Initiators to Deep Sleep -> Big Sleep Transition                 |    |

| 3  | Initiators of Deep Sleep -> Awake Transition                     |    |

| 4  | ULPD Output Clocks Description                                   |    |

| 5  | Clock Request to Clock Available Latencies                       |    |

| 6  | Latencies for Each Peripheral Clock                              |    |

| 7  | ULPD Registers                                                   |    |

| 8  | Counter 32 LSB Register (COUNTER_32_LSB_REG)                     |    |

| 9  | Counter 32 MSB Register (COUNTER_32_MSB_REG)                     |    |

| 10 | Counter High-Frequency LSB Register (COUNTER_HIGH_FREQ_LSB_REG)  |    |

| 11 | Counter High-Frequency MSB Register (COUNTER_HIGH_FREQ_MSB_REG)  |    |

| 12 | Gauging Control Register (GAUGING_CTRL_REG)                      |    |

| 13 | Interrupt Status Register (IT_STATUS_REG)                        |    |

| 14 | Reserved Register (RESERVED)                                     |    |

| 15 | Reserved Register (RESERVED)                                     |    |

| 16 | Setup Analog Cell3 ULPD1 Register (SETUP_ANALOG_CELL3_REG)       |    |

| 17 | Setup Analog Cell2 ULPD1 Register (SETUP_ANALOG_CELL2_REG)       |    |

| 18 | Setup Analog Cell1 ULPD1 Register (SETUP_ANALOG_CELL1_REG)       |    |

| 19 | Clock Control Register (CLOCK_CTRL_REG)                          |    |

| 20 | Software Request Register (SOFT_REQ_REG)                         |    |

| 21 | Counter 32 FIQ Register (COUNTER_32_FIQ_REG)                     |    |

| 22 | Reserved Register (RESERVED)                                     |    |

| 23 | Status Request Register (STATUS_REQ_REG)                         |    |

| 24 | PLL Division Register (PLL_DIV_REG)                              |    |

| 25 | Reserved Register (RESERVED_48)                                  |    |

| 26 | ULPD PLL Control Status Register (ULPD_PLL_CTRL_STATUS)          |    |

| 27 | Power Control Register (POWER_CTRL_REG)                          |    |

| 28 | Status Request Register 2 (STATUS_REQ_REG2)                      |    |

| 29 | Sleep Status Register (SLEEP_STATUS)                             |    |

| 30 | Setup Analog Cell4 ULPD1 Register (SETUP_ANALOG_CELL4_REG)       |    |

| 31 | Setup Analog Cell5 ULPD1 Register (SETUP_ANALOG_CELL5_REG)       |    |

| 32 | Setup Analog Cell6 ULPD1 Register (SETUP_ANALOG_CELL6_REG)       |    |

| 33 | Software Disable Request Register (SOFT_DISABLE_REQ_REG)         |    |

| 34 | Reset Status Register (RESET_STATUS)                             |    |

| 35 | Revision Number Register (REVISION_NUMBER)                       |    |

| 36 | SDW Clock Divider Control Select Register (SDW_CLK_DIV_CTRL_SEL) | 65 |

12 OMPA5912 SPRU753A

| 37 | COM Clock Divider Control Select Register (COM_CLK_DIV_CTRL_SEL) . | ( | 65 |

|----|--------------------------------------------------------------------|---|----|

| 38 | CAM Clock Control Register (CAM_CLK_CTRL)                          |   | 66 |

| 39 | Software Request Register2 (SOFT_REQ_REG2)                         |   | 66 |

| 40 | Power Domains With Associated Power Supply and Planes              |   | 68 |

| 41 | Powering OMAP5912 Domains                                          |   | 69 |

| 42 | OMAP3.2 Subsystem Clocks                                           |   | 73 |

| 43 | Idle Configuration Register (ICR)                                  |   | 75 |

| 44 | Idle Status Register (ISTR)                                        |   | 76 |

| 45 | EMIF Global Control Register (GCR)                                 |   | 78 |

| 46 | TIPB Control Mode Register (CMR)                                   |   | 79 |

| 47 | Wait State Strobe Frequency NIL                                    |   | 79 |

| 48 | OMAP3.2 Modules With Clock Autogating Enable Feature               |   | 83 |

| 49 | OMAP5912 Peripherals With Clock Autogating Enable Feature          |   | 84 |

| 50 | Power Management Control Register                                  |   | 85 |

| 51 | DSP Isolation Control                                              |   | 93 |

| 52 | Global OMAP5912 System Power Modes                                 |   | 96 |

| 53 | MPU Domain States                                                  |   |    |

| 54 | DSP Domain States                                                  |   | 97 |

SPRU753A OMPA5912 13

14 OMPA5912 SPRU753A

# **Power Management**

This document describes power management in the OMAP5912 multimedia processor.

#### 1 Ultralow-Power Device

The ultralow-power device (ULPD) generates and manages clocks and reset signals to OMAP3.2 and to some peripherals. It controls chip-level power-down modes and handles chip-level wake-up events. In deep sleep mode, this module is still active to monitor wake-up events.

This chapter describes the ULPD module and outline architecture. For further information on clock sources and clock and reset architecture, see Chapter 4 and Chapter 5.

#### 1.1 ULPD Features

| The | e ULPD has the following features:                                                                                                   |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|

|     | Performs transitions among power modes (awake, big sleep, and deep sleep)                                                            |

|     | Handles idle/wake-up handshake with OMAP3.2                                                                                          |

|     | Monitors wake-up events                                                                                                              |

|     | Controls system clock input sources for several possible configurations (oscillator/external clocks)                                 |

|     | Performs calibration of the 32-kHz oscillator                                                                                        |

|     | Manages the clocks and resets distributed to OMAP3.2 and to some peripherals                                                         |

|     | Handles the power-up sequence                                                                                                        |

|     | Controls an on-chip PLL that generates a 96-MHz clock (for 48-MHz peripheral clocks)                                                 |

|     | Is controlled by the MPU for set up and configuration                                                                                |

|     | Manages the sleep signal of an embedded LDO used to regulate the supply voltage for OMAP3.2 digital phase locked loop (DPLL) and the |

SPRU753A Power Management 15

system clock oscillator

#### 1.2 Overview

The ULPD is a power management module running at 32 kHz (CLK32K).

The ULPD employs three global-system power modes: awake mode, big sleep mode, and deep sleep mode. See Section 1.5, *Power Modes*, for a description of these modes and the transitions between them.

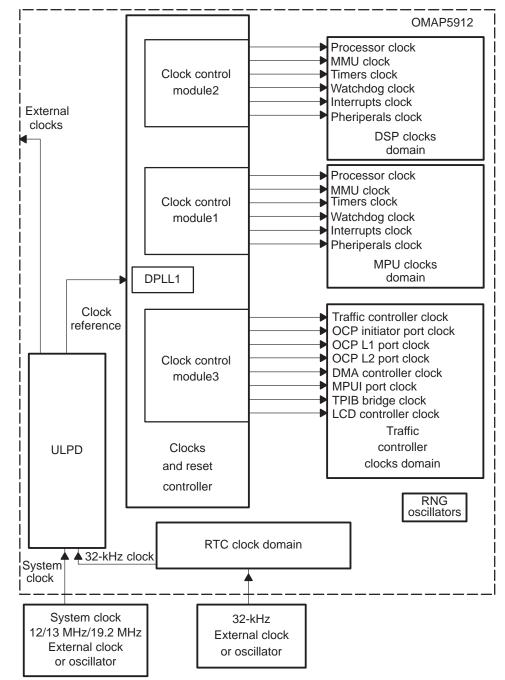

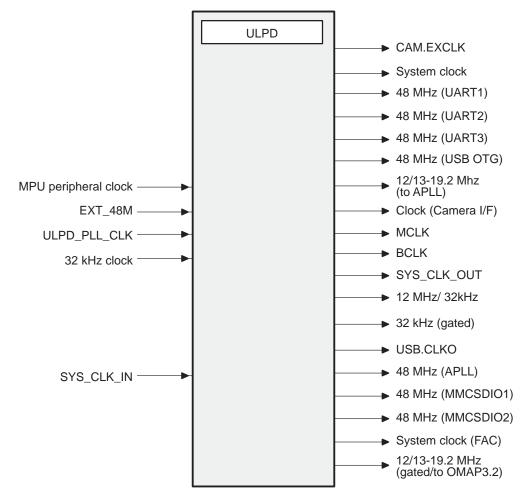

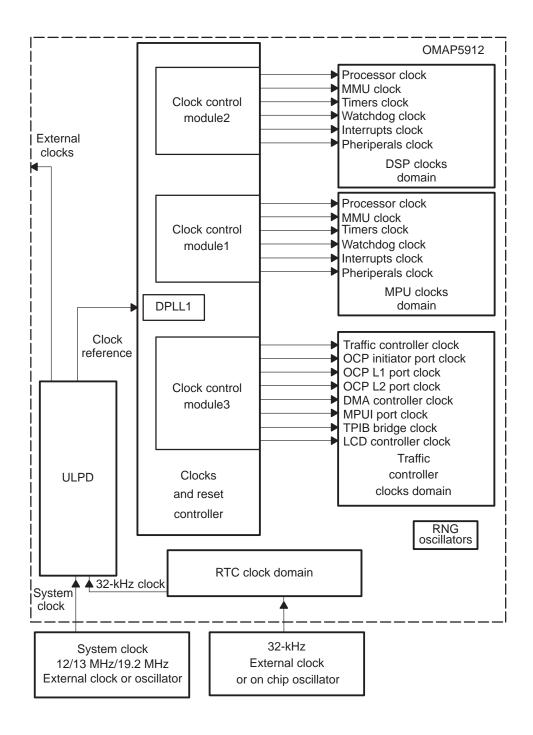

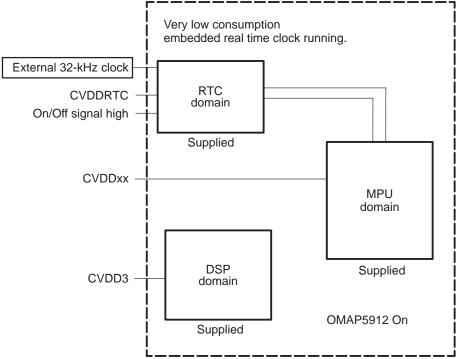

The ULPD controls the various module clocks with several input clock sources provided by the oscillator and by the OMAP3.2 DPLL and the 96-MHz analog phase-locked loop (APLL). It also can sequence the wake-up of the system properly by enabling various analog cells successively. Analog cells are on-chip or external modules that are involved in the generation of the device input clock or supply voltage. Typical analog cells are on-chip oscillators or external supply voltage regulators. ULPD can manage up to six analog cells Figure 1.

Figure 1. ULPD and Clock Domains in OMAP5912

The ULPD is composed of one state machine, a clock management module, and a control register file.

☐ The state machine (FSM1) manages the global power modes transitions. It handles the idle/wake-up handshake with OMAP3.2 and monitors the wake-up events.

The state machine controls the input system clock (internal oscillator or external clock source) and generates resets to OMAP3.2 and to some peripherals. It also manages the power-up sequence. The FSM1 uses a setup timer to manage the sequencing of the wake-up procedure. Each setup timer is associated with a specific analog cell.

- □ The clock management module is composed of clock-gating logic, multiplexers, and clock dividers. It generates and manages clocks to OMAP3.2 and to some peripherals. It also manages the 48-MHz clocks. Those clocks are generated from an on-chip analog phase locked loop (APLL) operating at 96 MHz. The output of the APLL is divided by two to create a 48-MHz reference clock. From the reference clock are derived the various 48-MHz clocks.

- The control register file is an MPU peripheral connected to the MPU private peripheral bus; it is used to set/configure the features of ULPD.

See Section 1.24 for a detailed description of the registers.

#### 1.3 ULPD Input Clock Sources

The ULPD has two main clock sources: a 32-kHz clock and a system clock of medium frequency (12 MHz, 13 MHz, and 19.2 MHz). These frequencies are also the ULPD\_PLL input clock frequency. See Chapter 5 for additional information on the clock source for ULPD.

#### 1.4 ULPD Setup Counters

The ULPD can sequence the wake-up of the system from deep sleep properly by enabling up to six analog cells successively (for example, oscillator and regulator).

The ULPD FSM1 is instantiated in OMAP5912 with two setup counters, each associated with an analog cell. Setup counters are cascaded and must be programmed with the stabilization time of the associated analog cell.

Whenever a counter underflows, it enables the next analog cell and triggers the associated counter.

The cascaded flow of the SETUP\_ANALOG\_CELL starts with SETUP\_ANALOG\_CELL2 and ends with SETUP\_ANALOG\_CELL3.

When SETUP\_ANALOG\_CELL3 underflows, all the analog cells must be stable and the input system clock is released internally in ULPD.

The ULPD FSM1 can then move in big sleep or awake mode.

#### 1.5 Power Modes

The ULPD handles three global power modes: deep sleep, big sleep, and awake. The ULPD state machine, which is in charge of the wake-up/idle handshake with OMAP3.2, manages the states of the system in each mode and performs transitions between the modes.

#### 1.5.1 Deep Sleep Mode

In deep sleep mode, all internal clocks are inactive except the 32-kHz clock, which is the ULPD state machine clock. In this mode ULPD\_PLL is always inactive.

In oscillator mode, the oscillator is disabled; therefore, the system input clock is off, except when POWER CTRL REG [9] =0.

In external mode, the input system clock can be on or off; it is not controlled by ULPD.

#### Note:

OSC12M\_STOP output of ULPD is active high every time the state machine is in a deep-sleep state. EXT\_CLK\_REQ is the same signal but with inverted polarity.

OMAP5912 cannot go into deep-sleep while an emulator (JTAG) is connected

#### 1.5.2 Big Sleep Mode

In big sleep mode, the OMAP input clock is inactive, the 32-kHz clock is active, and the system input clock is active in both oscillator and external modes.

This state is characterized by an external clock request to go active or POWER\_CTRL\_REG [4] =0.

This mode has a shorter wake-up latency. It also provides clocks (system frequency clocks and/or ULPD\_PLL clock) to peripherals whenever requested and while the OMAP3.2 input clock is stopped.

#### 1.5.3 Awake Mode

In awake mode, the OMAP input clock and any requested peripheral clocks are active. In awake mode, the 32-kHz, system clock, OMAP input clock, and any requested peripheral clocks are active.

#### 1.6 External Clock and Voltage Supply Control

The ULPD provides two signals to control the activation or the shut down of the external clock and core voltage supplies.

These two signals,  $\overline{\text{LOW\_PWR}}$  and  $\overline{\text{LOW\_PWR}}$ , behave similarly except that they do not have the same polarity.

LOW\_PWR can be controlled by software, whereas LOW\_PWR cannot.

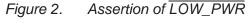

#### 1.6.1 Behavior of LOW PWR

The LOW\_PWR signal is used in external clock mode.

When low,  $\overline{\text{LOW\_PWR}}$  indicates to external devices that the input system clock (SYS\_CLK\_IN) can be shut down. It can also indicate to an external power management device that the core voltage supply can be lowered to 1.1 V.

The LOW\_PWR signal is asserted low when the ULPD enters the deep sleep state (except at power-up reset) and released upon deep sleep exit (except at power-up reset).

At power-up reset, LOW\_PWR is reset to its inactive value (high).

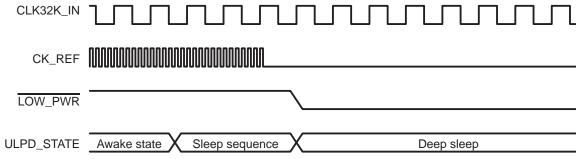

#### 1.6.2 Behavior of LOW PWR

The LOW\_PWR signal is used in oscillator clock mode to control an external power management device.

When high, the signal LOW\_PWR drives the external core voltage supply in low voltage (1.1 V) operations.

LOW\_PWR can be set by software so that two types of operations are allowed:

- ☐ Reduction of leakage current

- Low-voltage operation at reduced clock frequency, also known as dynamic voltage scaling (DVS)

#### 1.7 Leakage Current Management

The conditions below cause the listed events:

- □ POWER\_CTRL\_REG[0] set to 1: Enable LOW\_PWR feature

- □ POWER\_CTRL\_REG[4] set to 1: Enable transition to deep sleep mode or

POWER\_CTRL\_REG[10] set to 0: DVS disabled

LOW\_PWR switches to active high whenever the ULPD enters deep sleep state. In this way, the external core voltage supply can be driven in low-voltage operation by the external power management device.

When the ULPD exits deep sleep mode, LOW\_PWR switches back to inactive low and the external core voltage supply ramps up to a nominal 1.5 V.

At reset, the low-power feature is disabled (POWER\_CTRL\_REG[0] is set to 0). The LOW\_PWR signal is inactive low, which indicates a nominal voltage requirement.

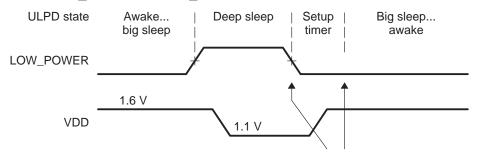

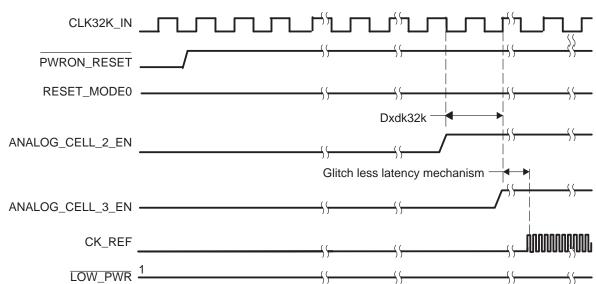

Figure 4. Behavior of LOW\_PWR in RESET\_MODE 0

ULPD setup analog cell timer2 delays deep sleep to big sleep/awake transition while the regulator ramps from 1.1 V to 1.6 V.

#### 1.8 Low-Voltage Operation at Reduced Clock Frequency

In this mode of operation, also known as dynamic voltage scaling (DVS), the following conditions must be met:

- □ POWER\_CTRL\_REG[4] set to 0: Disables transition to deep sleep mode

- POWER\_CTRL\_REG[10] set to 1: Enables DVS

Whenever OMAP3.2 indicates to ULPD that it is prepared to go into idle, the transition to deep sleep is prevented, and the ULPD moves into big sleep mode. In this mode, the OMAP3.2 input clock is shut down, but the oscillator is still active.

In this case, LOW\_PWR follows the value programmed in POWER\_CTRL\_REG [11].

If POWER\_CTRL\_REG [11] =1 (min), LOW\_PWR switches to active high, driving the external regulator in low-voltage operation.

If POWER\_CTRL\_REG [11] =0 (max), LOW\_PWR switches to inactive low, driving the external regulator in nominal voltage operation.

Whenever OMAP3.2 initiates a wake-up procedure, the ULPD moves back to awake mode but LOW\_PWR keeps the value programmed in POWER\_CTRL\_REG [11].

In this way, when POWER\_CTRL\_REG [11] =1, OMAP3.2 restarts operations at low voltage. To ramp up the operating voltage back to nominal value, a new

OMAP3.2 idle/wake-up procedure must be performed with POWER\_CTRL\_REG[11]=0.

This feature allows dynamic control of the operating voltage of OMAP5912. It provides two operating points (voltage, frequency) to adapt the operating voltage to the performance requirement.

The OMAP3.2 DPLL frequency must be set accordingly before initiating the procedure.

The DVS procedure described here goes through the OMAP3.2 idle and wake-up sequences. To overcome limitations of this procedure, a more direct way to control the OMAP5912 operating voltage is provided.

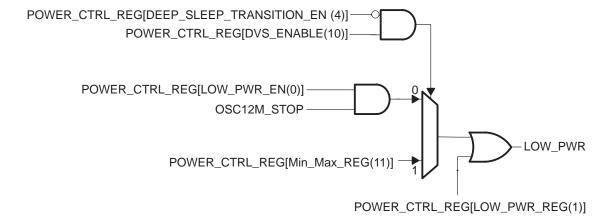

The user can directly force the LOW\_PWR signal to 1 and thereby force the operating voltage to 1.1 V by setting the bit POWER\_CTRL\_REG[1]. POWER\_CTRL\_REG [1] cannot force the LOW\_PWR signal to 0 (see Figure 5).

Figure 5. Control of OMAP5912 Low-Power Output by ULPD POWER\_CTRL\_REG

#### 1.9 Transitions Between Power Modes

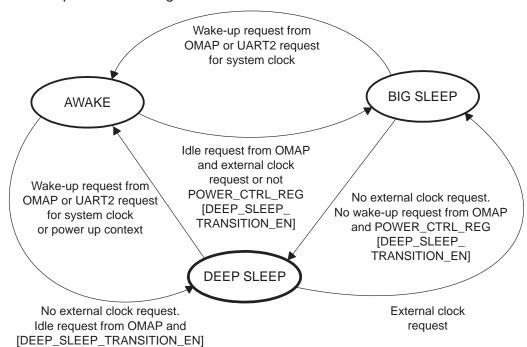

Figure 6 shows the basic functional scheme of the FSM1:

Figure 6. Simplified State Diagram of the ULPD FSM1

The ULPD handles the state transitions among deep sleep, big sleep, and awake. The transitions are triggered by the following:

- ☐ External events: Hardware resets or clock requests

- ☐ Internal events: Software resets, watchdog time-out, software clock request, or MPU idle request

Table 1. Sleep Modes versus Active Mode (Summary)

| Mode       | Power Dissipation                                               | Active Clocks                                                                    | Comments                                                                                                                                                           |

|------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deep sleep | Lowest                                                          | 32 kHz for wake-up detection                                                     | Only the UART2 functional clock using 32 kHz is active.                                                                                                            |

| Big sleep  | From modules<br>clocked by active<br>32-kHz or 48-MHz<br>clocks | System and 32-kHz<br>clock. ULDP output<br>clocks to peripherals if<br>requested | For BCLK and MCLK, the 48-MHz frequency can be divided further by setting respectively SDW_CLK_DIV_CTRL_SEL[7:2] and COM_RATIO_SEL[7:2] in ULPD control registers. |

| Awake      | Nominal                                                         | All 32-kHz, 48-MHz, and clocks derived from system clock can be active.          | OMAP3.2 input clock is active.                                                                                                                                     |

#### 1.10 Power-on Transition to Deep Sleep Mode

At power-up, namely when the power-up input signal PWRON\_RESET is asserted low, the ULPD FSM1 enters deep sleep mode.

In this case, the LOW\_PWR signal is reset to inactive state 1.

When PWRON\_RESET is released, the FSM automatically switches from deep sleep to awake.

The transition follows this procedure:

- 1) PWRON\_RESET is asserted low, and LOW\_PWR is reset to 1 (inactive).

- 2) FSM enters the deep sleep mode and stays in this mode until the PWRON\_RESET signal is released.

#### 1.11 Transitions From Deep Sleep Mode

In deep sleep mode, the FSM monitors the OMAP3.2 wake-up request and external clock requests. OMAP3.2 propagates asynchronously unmasked peripheral interrupts to generate a wake-up request.

External clock requests and the OMAP3.2 wake-up request are respectively initiators of deep sleep to big sleep and deep sleep to awake transitions. The power-up reset initiates a transition from deep sleep to awake.

#### 1.11.1 Transition from Deep Sleep to Big Sleep Mode

Transition to big sleep state occurs when there is at least one specific external clock request (see Table 2).

Table 2. Initiators to Deep Sleep -> Big Sleep Transition

| Transition from Deep Sleep                  | to Big Sleep |  |

|---------------------------------------------|--------------|--|

| External Clock Request                      |              |  |

| CONF_CAM_CLKMUX_R (register)                | CAMERA I/F   |  |

| External Clock Request (C                   | continued)   |  |

| CONF_MOD_UART1_CLK_MODE_R (register)        | UART1        |  |

| CONF_MOD_UART2_CLK_MODE_R (register)        | UART2        |  |

| CONF_MOD_UART3_CLK_MODE_R (register)        | UART3        |  |

| CONF_MOD_USB_HOST_HHC_UHOST_EN_R (register) | USB OTG      |  |

| CONF_MOD_MMC_SD_CLK_REQ_R (register)        | MMC/SDIO1    |  |

Table 2. Initiators to Deep Sleep -> Big Sleep Transition (Continued)

| Transition from Deep Sleep to Big Sleep |                                |  |

|-----------------------------------------|--------------------------------|--|

| CONF_MOD_MMC_SD2_CLK_REQ_R (register)   | MMC/SDIO2                      |  |

| Clock request by USB                    | USB OTG. See Note 4.           |  |

| MCLKREQ                                 | OMAP5912 input pin             |  |

| BCLKREQ                                 | OMAP5912 I/O input pin         |  |

| SOFT_REQ_REG (active)                   | Software requests. See Note 5. |  |

| Other                                   |                                |  |

| DEEP_TRANSITION_ENABLE                  | ULPD                           |  |

Notes: 1) Software requests

- Software requests prevent the transition to deep sleep when leaving awake state but are not initiators of deep sleep to big sleep transition.

- 2) DEEP\_SLEEP\_TRANSITION\_EN is not an initiator of deep sleep to big sleep transition. It keeps FSM1 in big sleep mode and prevents transition to deep sleep mode when leaving the awake state.

- When in external 48-MHz clock mode (CONF\_DPLL\_EXT\_SEL = 0), clock requests related to 48-MHz clock have no effect on the FSM.

- 4) The USB can request clock when an external host or device is detected or when the USB enters the resume state.

- 5) Software requests for clock can be programmed in the ULPD SOFT\_REQ\_REG (see Table 20).

The transition sequence is as follows:

- 1) External clock request occurs.

- 2) LOW\_PWR is asserted high.

- 3) Depending on the system input clock source mode:

- a) External mode: In this case, the setup counter, SETUP\_ANALOG\_CELL3, is loaded with the related setup value from the ULPD register that corresponds to the ramp-up time of the external voltage supply. When the counter underflow is generated, it globally enables the system input clock to peripherals.

At this point it is possible that the external system input clock is not present yet. The clocks for the peripherals are effectively restarted whenever the system input clock arrives, if the corresponding clock request is active.

This setup stage allows the supply voltage to be stable before enabling the input clocks to peripherals.

b) Oscillator mode: In this case, the setup counter, SETUP\_ANALOG\_CELL2, is loaded with the related setup value from the ULPD register that corresponds to the maximum time between ramp-up time of the external voltage supply and LDO stabilization time.

When the counter underflow is generated, it enables the oscillator. Then the setup counter, SETUP\_ANALOG\_CELL3, is loaded with the related setup value from the ULPD register that corresponds to the stabilization delay of the oscillator.

When the counter underflow is generated, it globally enables the system input clock to peripherals.

The clocks for the peripherals are restarted if the corresponding clock request is active. These two setup stages allow the supply voltage and the input system clock to be stable before enabling the input clock to peripherals

4) FSM1 enters big sleep mode.

#### 1.11.2 Transition from Deep Sleep to Awake Mode

| Transition to awake mode occurs whenever a wake-up event occurs. Wake-up |

|--------------------------------------------------------------------------|

| events are:                                                              |

| MPU_RST                                                                                                |

|--------------------------------------------------------------------------------------------------------|

| OMAP3.2 asserts the wake-up request. A wake-up request is initiated by peripheral unmasked interrupts. |

| UART2 requests system clock.                                                                           |

| PWRON_RESET                                                                                            |

| RTC_ON_NOFF                                                                                            |

| 32-kHz watchdog reset                                                                                  |

Table 3. Initiators of Deep Sleep -> Awake Transition

| Transition from Deep Sleep to Awake |                                 |  |  |  |

|-------------------------------------|---------------------------------|--|--|--|

| Wake-up Event                       |                                 |  |  |  |

| PWRON_RESET                         | Power-on reset pin              |  |  |  |

| RTC_ON_NOFF                         | Power-on reset pin              |  |  |  |

| MPU_RST                             | System reset pin                |  |  |  |

| 32-kHz watchdog reset               | 32-kHz watchdog time-out        |  |  |  |

| Wake-up request                     | Peripheral unmasked interrupts  |  |  |  |

| PERIPH_REQ                          |                                 |  |  |  |

| PERIPH_REQ                          | System clock request from UART2 |  |  |  |

The transition follows one of two sequences:

- ☐ Sequence 1

- 1) The following wake-up event occurs:

- a) OMAP3.2 asserts a wake-up request. The wake-up request is initiated by a peripheral unmasked interrupt.

- b) UART2 requests system clock.

- Power-up reset, system reset (low on MPU\_RST), secure watchdog reset, or 32-kHz watchdog reset

- 2) LOW\_PWR is asserted high.

- 3) Depending on the system input clock source mode:

- a) External mode: In this case, the setup down counter, SETUP\_ANALOG\_CELL3, is loaded with the related setup value from the ULPD register that corresponds to the ramp-up time of the external voltage supply.

When the counter underflow is generated, it globally enables the system input clock to peripherals.

At this point, it is possible that the external system input clock is not present yet.

The peripheral clocks are effectively restarted whenever the system input clock arrives, if the corresponding clock request is active.

This setup stage is intended to allow the supply voltage to be stable before enabling the input clocks to peripherals.

At power up, the supply voltage and the input system clock must be stable when the PWRON\_RESET signal is released. In this case, this setup stage is skipped.

b) Oscillator mode: In this case, the setup counter, SETUP\_ANALOG\_CELL2, is loaded with the related setup value from the ULPD register that corresponds to the maximum time between ramp-up time of the external voltage supply and LDO stabilization time.

When the counter underflow is generated, it enables the oscillator. Then the setup counter, SETUP\_ANALOG\_CELL3, is loaded with the related setup value from the ULPD register that corresponds to the stabilization delay of the oscillator.

When the counter underflow is generated, it globally enables the system input clock to peripherals.

The clocks for the peripherals are restarted if the corresponding clock request is active. These two setup stages are intended to allow the supply voltage and the input system clock to be stable before enabling the input clock to peripherals.

- 4) FSM1 enters the awake mode.

- 5) OMAP3.2 input clock is enabled. In external mode, the clock is effectively restarted whenever the system input clock arrives.

- 6) OMAP3.2 deasserts the CHIP\_IDLE signal.

- 7) ULPD releases the CHIP\_WAKEUP signal high.

request (internal)

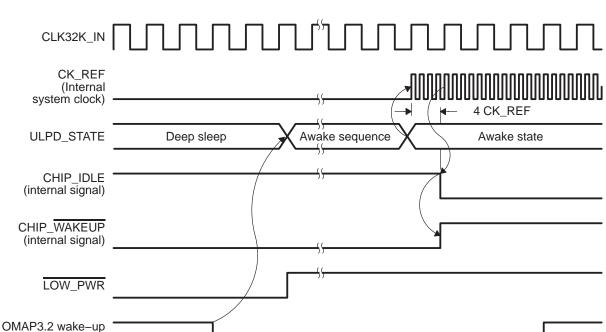

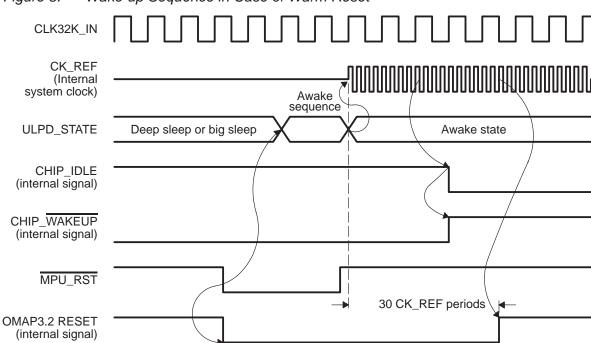

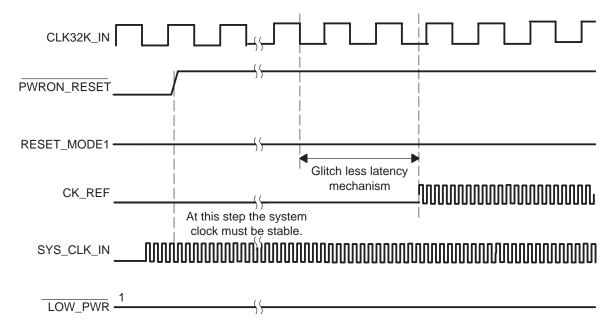

Figure 7. 20MAP3.2-Initiated Wake-up Sequence

The wake-up sequence requires five CLK32K clock cycles from assertion of OMAP3.2 wake-up request to release of CK\_REF.

- ☐ Sequence 2

- 1) The following wake-up events occur:

- a) MPU\_RST low event

- b) 32-kHz watchdog time-out

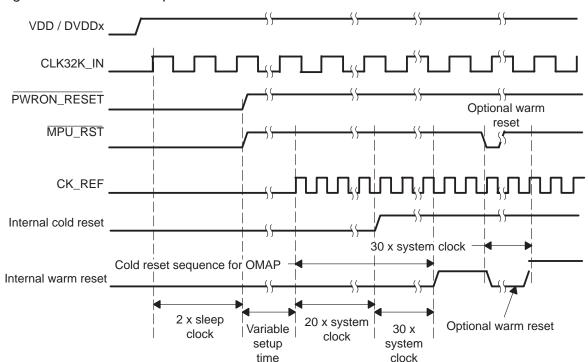

- 2) ULPD performs the transition to awake as described previously and releases the system clock to OMAP3.2.

- 3) As soon as the system clock is back on, the ULPD asserts low the OMAP3.2 reset for at least 30 system clock cycles.

- 4) On detection of OMAP3.2 reset low, OMAP3.2 deasserts the CHIP\_IDLE signal.

- 5) ULPD asserts the CHIP\_WAKEUP signal high.

Figure 8. Wake-up Sequence in Case of Warm Reset

#### 1.12 Transitions From Big Sleep Mode

#### 1.12.1 Transition From Big Sleep Mode to Deep Sleep Mode

Three necessary conditions lead to deep sleep mode:

- ☐ Wake-up request from OMAP is not active.

- Peripherals clock request and software clock request are inactive. Namely, every clock request that is in is not active.

- □ POWER\_CTRL\_REG[4]=1

The transition follows this sequence:

- All clock requests are inactive; there is no wake-up request from OMAP and POWER\_CTRL\_REG[4]=1.

- 2) Input clocks to peripherals are globally disabled.

- 3) LOW\_PWR is activate low and in oscillator mode the oscillator is also disabled, unless POWER\_CTRL\_REG[9]=0.

- 4) FSM1 enters deep sleep mode.

#### 1.12.2 Transition From Big Sleep Mode to Awake Mode

The transition to awake mode occurs when OMAP3.2 requests wake-up or UART2 requests system clock. An OMAP3.2 wake-up request is initiated by the unmasked interrupts of the peripherals.

The transition follows this sequence:

- Wake-up event occurs (OMAP3.2 wake-up request or UART2 requests system clock)

- 2) FSM1 enters the awake mode.

- 3) OMAP3.2 input clock in enabled. In external mode, the clock is effectively restarted whenever the external system input clock arrives.

#### 1.13 Transitions From Awake Mode

#### 1.13.1 Transition From Awake Mode to Deep Sleep Mode

Three necessary conditions lead to deep sleep mode:

- OMAP3.2 asserts the CHIP\_IDLE signal when no clocks are needed in OMAP3.2 or by any peripheral using OMAP3.2 output clocks. For example, DMA\_LCD\_CTRL.lcd\_destination\_port = 1 is a condition that prevents the OMAP3.2 chip\_idle to be asserted because the clock request corresponding to the external LCD controller clock is kept active.

- No clock request or software request by peripherals

- □ POWER CTRL REG [4] =1

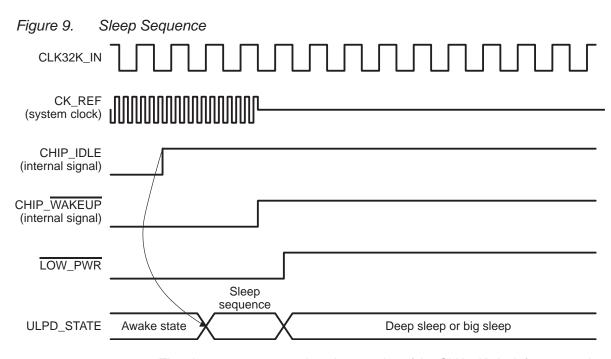

The transition follows this sequence:

- 1) All clock requests are inactive, CHIP\_IDLE is asserted high and POWER\_CTRL\_REG[4]=1. Any incoming interrupt is ignored.

- The ULPD asserts CHIP\_WAKEUP to 0. This is a sleep acknowledge, and OMAP3.2 expects its input clock to be cut off. Interrupts can then be taken again.

- 3) Input clock to peripherals is globally disabled.

- 4) LOW\_PWR is asserted low and in oscillator mode the oscillator is also disabled, unless POWER\_CTRL\_REG[9]=0.

- 5) FSM1 enters the deep sleep mode.

The sleep sequence requires three cycles of the CLK32K clock from assertion of the CHIP\_IDLE signal to assertion of the LOW\_PWR signal.

#### Note:

The name of the signal CHIP\_WAKEUP may confuse users. This signal is not a wake-up signal but is an idle acknowledge.

#### 1.13.2 Transition From Awake Mode to Big Sleep Mode

Two necessary conditions lead to big sleep mode:

- OMAP asserts the CHIP\_IDLE (active high) when no clocks are needed in OMAP3.2 or by any peripherals using OMAP3.2 output clocks.

- ☐ At least one specific peripheral clock request is active or POWER\_CTRL\_REG[4]=0

#### Sequence:

- CHIP\_IDLE is asserted high. There are active external clock requests or POWER\_CTRL\_REG[4]=0.

- 2) OMAP3.2 input clock is disabled.

- 3) FSM1 enters the big sleep mode.

#### 1.14 ULPD Output Clocks

The ULPD controls the system clock (12 MHz or 19.2 MHz) and the various 48-MHz clocks used by OMAP5912 peripherals.

These clocks supply the OMAP3.2 subsystem and some of the OMAP5912 peripherals.

Figure 10 shows a simplified diagram of the ULPD clock generation scheme. Most of the clocks generated by ULPD can be controlled independently by hardware and by software. In fact, a hardware clock request signal and a software clock request (programmable) bit in the SOFT\_REQ\_REG register are associated with most of the ULPD-generated clocks.

These clock requests are used in the ULPD to enable/disable the associated clocks.

In addition, the hardware request serves as a wake-up event for the ULPD state machine and the clock generation module it controls (the oscillator and ULPD\_PLL).

The software requests are involved in the conditions of the awake to big sleep transition.

Figure 10. Basic Diagram of the ULPD Output and Input Clocks

Table 4 describes how clocks are gated by the ULPD. It shows:

- ☐ The source of each clock output with its associated selection signal

- The specific enable signal and clock request whenever the clock can be gated

See Section 1.24 for more details on registers.

Table 4. ULPD Output Clocks Description

| OMAP5912 I/O<br>Destination | Clock Selected             | Clock Source<br>Selection                     | Wake-up<br>Request                                                 | Soft Request<br>Disable     |

|-----------------------------|----------------------------|-----------------------------------------------|--------------------------------------------------------------------|-----------------------------|

| BCLK                        | Derived from APLL<br>CLK/2 | SDW_SYSCLK_<br>PLLCLK_SEL                     | BCLKREQ                                                            | SOFT_DISABLE_<br>REQ_REG[1] |

|                             |                            | CLOCK_CTRL_<br>REG[2]                         |                                                                    |                             |

|                             |                            | SDW_CLK_DIV_<br>CTRL_SEL[7:2]<br>(see Note 1) |                                                                    |                             |

| MCLK                        | Derived from APLL<br>CLK/2 | COM_SYSCLK_<br>PLLCLK_SEL                     | MCLKREQ SOFT_REQ_ REG[6] COM_CLK_DIV_ CTRL_SEL[1] SOFT_REQ_ REG[1] | SOFT_DISABLE_<br>REQ_REG[0] |

|                             |                            | CONF_MOD_COM_<br>MCLK_12_48_<br>SEL_R         |                                                                    |                             |

|                             |                            | CONF_DPLL_EXT_<br>SEL<br>(see Note 2)         |                                                                    |                             |

|                             |                            | CLOCK_CTRL_<br>REQ[1]                         |                                                                    |                             |

|                             |                            | COM_RATIO_<br>SEL[7:2]<br>(see Note 3)        |                                                                    |                             |

| UART2                       | System clock               | CLOCK_CTRL_<br>REG[0]                         | OMAP3.2<br>wake-up request                                         | SOFT_DISABLE_<br>REQ_REG[3] |

|                             |                            |                                               | UART2 request for system clock                                     |                             |

|                             |                            |                                               | SOFT_REQ_<br>REG[5]                                                |                             |

| USB.CLKO                    | EXT.48M divided by 8       | CONF_DPLL_EXT_<br>SEL                         | Clock request to<br>APLL                                           |                             |

|                             | APLL CLK/2                 | CLOCK_CTRL_<br>REG[4]                         | SOFT_REQ_<br>REG[0]                                                |                             |

| SYS_CLK_OUT                 | System clock               | CLOCK_CTRL_<br>REG[3]                         | MCLKREQ                                                            | SOFT_DISABLE_<br>REQ_REG[0] |

|                             |                            |                                               | SOFT_REQ_<br>REG[1]                                                |                             |

Table 4. ULPD Output Clocks Description (Continued)

| OMAP5912 I/O<br>Destination | Clock Selected        | Clock Source<br>Selection | Wake-up<br>Request                | Soft Request<br>Disable     |

|-----------------------------|-----------------------|---------------------------|-----------------------------------|-----------------------------|

| CAM.D[7]<br>(See Note 4.)   | EXT.48M<br>APLL CLK/2 | CONF_DPLL_EXT_<br>SEL     | SOFT_REQ_<br>REG[0]               |                             |

|                             | 711 22 32142          |                           | Clock request to APLL             |                             |

| UART1                       | EXT.48M               | CONF_DPLL_EXT_<br>SEL     | MOD_CONF_<br>CTRL0[29]            | SOFT_DISABLE_<br>REQ_REG[7] |

|                             | APLL CLK/2            | OLL                       | SOFT_REQ_<br>REG[9]               | NEQ_NEO[/]                  |

| UART2                       | EXT.48M               | CONF_DPLL_EXT_<br>SEL     | MOD_CONF_<br>CTRL0[30]            | SOFT_DISABLE_<br>REQ_REG[8] |

|                             | APLL CLK/2            | OLL                       | SOFT_REQ_<br>REG[10]              | NEQ_NEG[0]                  |

| UART3                       | EXT.48M               | CONF_DPLL_<br>EXT_SEL     | MOD_CONF_                         | SOFT_DISABLE_               |

|                             | APLL CLK/2            | EXI_SEL                   | CTRL0[31]<br>SOFT_REQ_<br>REG[11] | REQ_REG[9]                  |

| CAMERA I/F                  | EXT.48M               | CONF_DPLL_                | CONF_ CAM_                        | SOFT_DISABLE_               |

|                             | APLL CLK/2            | EXT_SEL                   | CLKMUX_R<br>SOFT_REQ_<br>REG[11]  | REQ_REG[5]                  |

| FAC                         | MPU peripheral clock  | CLOCK_CTRL_<br>REG[5]     | Clock request by the USB          |                             |

|                             |                       |                           | SOFT_REQ_<br>REG[3]               |                             |

Table 4. ULPD Output Clocks Description (Continued)

| OMAP5912 I/O<br>Destination | Clock Selected            | Clock Source<br>Selection | Wake-up<br>Request                           | Soft Request<br>Disable |

|-----------------------------|---------------------------|---------------------------|----------------------------------------------|-------------------------|

| USB OTG                     | EXT.48M                   | CONF_DPLL_<br>EXT_SEL     | USB request for 48 MHz                       | SOFT_REQ_<br>REG[4]     |

|                             | APLL CLK/2                | LXI_SLL                   | (see Note 5)                                 | SOFT_DISABLE_           |

|                             |                           |                           | CONF_MOD_<br>USB_HOST_<br>HHC_UHOST_<br>EN_R | REQ_REG[6]              |

|                             |                           |                           | SOFT_REQ_<br>REG[8]                          |                         |

| MMC/SDIO1                   | EXT.48M                   | CONF_DPLL_<br>EXT_SEL     | MOD_CONF_                                    | SOFT_DISABLE_           |

|                             | APLL CLK/2                |                           | CTRL_0[23]                                   | REQ_REG[10]             |

|                             |                           |                           | SOFT_REQ_<br>REG[12]                         |                         |

| MMC/SDIO2                   | EXT.48M                   | CONF_DPLL_                | MOD_CONF_                                    | SOFT_DISABLE_           |

|                             | APLL CLK/2                | EXT_SEL                   | CTRL_0[20]                                   | REQ_REG[11]             |

|                             |                           |                           | SOFT_REQ_<br>REG[13]                         |                         |

| CAM.EXCLK                   | System clock              | CAM_CLK_CTRL[0]           | M_CLK_CTRL[0] OMAP3.2                        |                         |

|                             | System clock divided by 2 | CAM_CLK_CTRL[1]           | wake-up request                              |                         |

| GPIO                        | System clock              | CAM_CLK_CTRL[2]           | OMAP3.2<br>wake-up request                   |                         |

Notes: 1) The frequency on the BCLK can be set accordingly: SDW\_CLK\_DIV\_CTRL\_SEL[7:2]. The resulting frequency is given in the following table:

```

SDW_CLK_DIV_CTRL_SEL[7:2] = 0X00000, BCLK = 48 MHz SDW_CLK_DIV_CTRL_SEL[7:2] = 0X00001, BCLK = 32 MHz SDW_CLK_DIV_CTRL_SEL[7:2] = 0X00002, BCLK = 24 MHz SDW_CLK_DIV_CTRL_SEL[7:2] = 0X00003, BCLK = 19.2 MHz SDW_CLK_DIV_CTRL_SEL[7:2] = 0X00004, BCLK = 16 MHz SDW_CLK_DIV_CTRL_SEL[7:2] = 0X00005, BCLK = 13.7 MHz SDW_CLK_DIV_CTRL_SEL[7:2] = 0X00005, BCLK = 13.7 MHz SDW_CLK_DIV_CTRL_SEL[7:2] = 0X00006, BCLK = 12 MHz SDW_CLK_DIV_CTRL_SEL[7:2] = 0X00007, BCLK = 9.6 MHz SDW_CLK_DIV_CTRL_SEL[7:2] = 0X00008, BCLK = 8 MHz SDW_CLK_DIV_CTRL_SEL[7:2] = 0X00009, BCLK = 6.9 MHz SDW_CLK_DIV_CTRL_SEL[7:2] = 0X000012, BCLK = 3 MHz SDW_CLK_DIV_CTRL_SEL[7:2] = 0X000012, BCLK = 3 MHz SDW_CLK_DIV_CTRL_SEL[7:2] = 0X000032, BCLK = 1 MHz

```

Other programmed values in SDW\_CLK\_DIV\_CTRL\_SEL[7:2] result in BCLK = 48 MHz.

2) If CONF\_DPLL\_EXT\_SEL is set to 1, external 48 MHz clock source is selected instead of the APLL clock source. The external 48 MHz clock is provided through GPIO[14].

3) The frequency on the MCLK can be set accordingly: COM\_RATIO\_SEL[7:2]. The resulting frequency is given in the following table:

```

COM_RATIO_SEL[7:2] = 0X00000, MCLK = 48 MHz COM_RATIO_SEL[7:2] = 0X00001, MCLK = 32 MHz COM_RATIO_SEL[7:2] = 0X00002, MCLK = 24 MHz COM_RATIO_SEL[7:2] = 0X00003, MCLK = 19.2 MHz COM_RATIO_SEL[7:2] = 0X00004, MCLK = 16 MHz COM_RATIO_SEL[7:2] = 0X00005, MCLK = 13.7 MHz COM_RATIO_SEL[7:2] = 0X00006, MCLK = 12 MHz COM_RATIO_SEL[7:2] = 0X00006, MCLK = 9.6 MHz COM_RATIO_SEL[7:2] = 0X00007, MCLK = 9.6 MHz COM_RATIO_SEL[7:2] = 0X00008, MCLK = 8 MHz COM_RATIO_SEL[7:2] = 0X00009, MCLK = 6.9 MHz COM_RATIO_SEL[7:2] = 0X000012, MCLK = 3 MHz COM_RATIO_SEL[7:2] = 0X000012, MCLK = 3 MHz COM_RATIO_SEL[7:2] = 0X000032, MCLK = 1 MHz

```

Other programmed values in COM\_RATIO\_SEL[7:2] result in MCLK = 48 MHz.

- 4) The 48 MHz from the APLL, which can be observed on CAM.D[7], is the observability mode as configured.

- 5) The USB will request 48 MHz clock in case of the following event:

- The USB has detected that either an external host or an external device is attached to one of the configured OMAP5912 USB ports, or

- The USB exits the suspend mode and enters the resume mode.

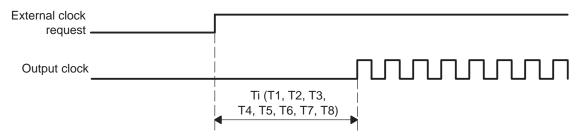

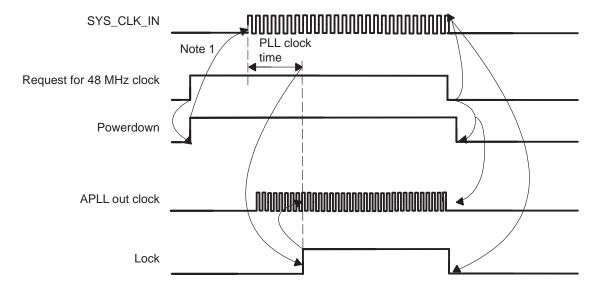

Figure 11 shows the latency between the clock request and the clock activation.

Figure 11. Timing Diagram for Clock Request to Clock Available Latency

The parameters (T1 to T8) are the latencies between peripheral clock requests and clock available (see Table 5 and Table 6). These latencies depend on ULPD setup counters and on the FSM1 state when the request is received.

Table 5. Clock Request to Clock Available Latencies

| Latency Name | Description                                            |

|--------------|--------------------------------------------------------|

| T1           | 4 x 32-kHz clock cycles + setup analog cell            |

| T2           | 3 x 32-kHz clock cycles                                |

| Т3           | 2 x 32-kHz clock cycles + setup analog cell            |

| T4           | 1 x 32-kHz clock cycles                                |

| T5           | 1 x 32-kHz clock cycles + APLL lock time               |

| Т6           | 2 x 32-kHz cycles + setup analog cell + APLL lock time |

| T7           | 2 x 32-kHz clock cycles                                |

| Т8           | 3 x 32-kHz clock cycles + setup analog cell            |

Table 6. Latencies for Each Peripheral Clock

| Name   | Wake-Up Request                                 |               | Time to Get the Clock Active<br>Depending on Initial FSM State |       |  |

|--------|-------------------------------------------------|---------------|----------------------------------------------------------------|-------|--|

|        |                                                 | Deep<br>Sleep | Big<br>Sleep                                                   | Awake |  |

| CK_REF | • PWRON_RESET                                   | T1            | T2                                                             |       |  |

|        | • MPU_RST                                       |               |                                                                |       |  |

|        | • RTC_ON_NOFF                                   |               |                                                                |       |  |

|        | 32-kHz watchdog time-out                        |               |                                                                |       |  |

|        | Wake-up request                                 |               |                                                                |       |  |

|        | <ul> <li>UART2 requests system clock</li> </ul> |               |                                                                |       |  |

| BCLK   | • BCLKREQ                                       | System clo    | ck                                                             |       |  |

|        | • SOFT_REQ_REG[2]                               | Т3            | T4                                                             | T5    |  |

|        | • SDW_CLK_DIV_CTRL_SEL[1]                       | PLL clock     |                                                                |       |  |

|        |                                                 | T6            | T5                                                             | T5    |  |

| MCLK   | • MCLKREQ                                       | System clo    | ck                                                             |       |  |

|        | • SOFT_REQ_REG[6]                               | Т3            | T4                                                             | T4    |  |

|        | • COM_CLK_DIV_CTRL_SEL[1]                       | PLL clock     |                                                                |       |  |

|        | • CONF_MOD_COM_MCLK_12_48_SEL_R                 | Т6            | T5                                                             | T5    |  |

Table 6. Latencies for Each Peripheral (Continued)Clock (Continued)

| Name                      |                                                                                                                            |               | Get the Clock Active ing on Initial FSM State |       |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------|-------|

|                           |                                                                                                                            | Deep<br>Sleep | Big<br>Sleep                                  | Awake |

| Functional<br>Clock UART2 | PWRON_RESET  MPU_RST  RTC_ON_NOFF  32-kHz watchdog time-out  Wake-up request  UART2 requests system clock  SOFT_REQ_REG[5] | T8            | T7                                            | 0     |

| 48-MHz USB<br>OTG         | <ul><li>Any hard or soft request related to APLL</li><li>SOFT_REQ_REG[0]</li></ul>                                         | Т6            | T5                                            | T5    |

| SYS_CLK_OUT               | • MCLKREQ • SOFT_REQ_REG[1]                                                                                                | Т3            | T4                                            | T4    |

| 48 MHz from<br>APLL       | <ul><li>SOFT_REQ_REG[0]</li><li>Any hard or soft request related to APLL</li></ul>                                         | Т6            | T5                                            | T5    |

| 48-MHz UART1              | • CONF_MOD_UART1_CLK_MODE_R • SOFT_REQ_REG[9]                                                                              | Т6            | T5                                            | T5    |

| 48-MHz UART2              | • CONF_MOD_UART2_CLK_MODE_R • SOFT_REQ_REG[10]                                                                             |               |                                               |       |

| 48-MHz UART3              | • CONF_MOD_UART3_CLK_MODE_R • SOFT_REQ_REG[11]                                                                             |               |                                               |       |

| Clock for<br>CAMERA IF    | • CONF_CAM_CLKMUX_R • SOFT_REQ_REG[7]                                                                                      | Т6            | T5                                            | T5    |

| System clock for FAC      | <ul><li>Request for 48 MHz from the USB</li><li>SOFT_REQ_REG[3]</li></ul>                                                  | Т6            | T2                                            | T2    |

| 48 MHz for USB<br>OTG     | <ul><li>Request for 48 MHz from the USB</li><li>CONF_MOD_USB_HOST_HHC_UHOST_EN_R</li><li>SOFT_REQ_REG[8]</li></ul>         | Т6            | T5                                            | T5    |

Table 6. Latencies for Each Peripheral (Continued)Clock (Continued)

| Name                     | Wake-Up Request                                                                                                                                                       |               | Time to Get the Clock Active<br>Depending on Initial FSM State |       |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------|-------|--|

|                          |                                                                                                                                                                       | Deep<br>Sleep | Big<br>Sleep                                                   | Awake |  |

| 48 MHz for<br>MMCSDIO1   | • CONF_MOD_MMC_SD_CLK_REQ_R • SOFT_REQ_REG[12]                                                                                                                        | Т6            | T5                                                             | T5    |  |

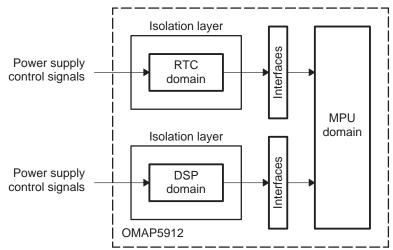

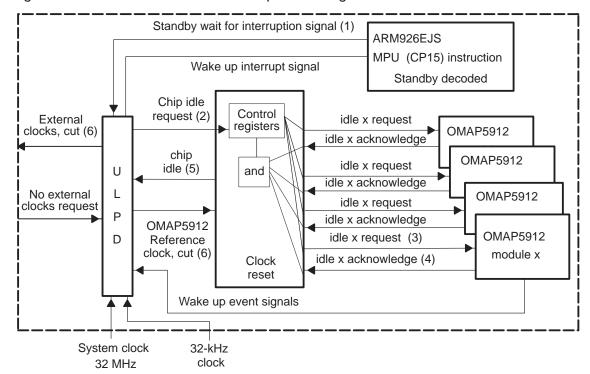

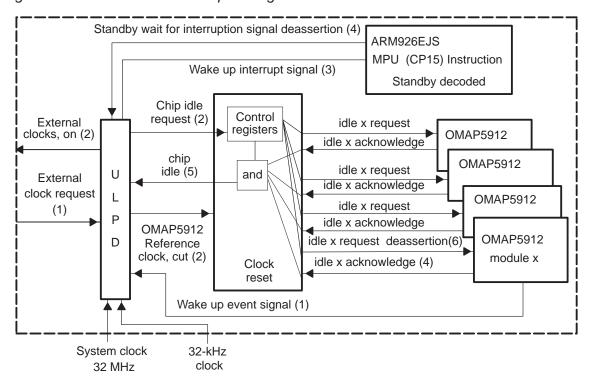

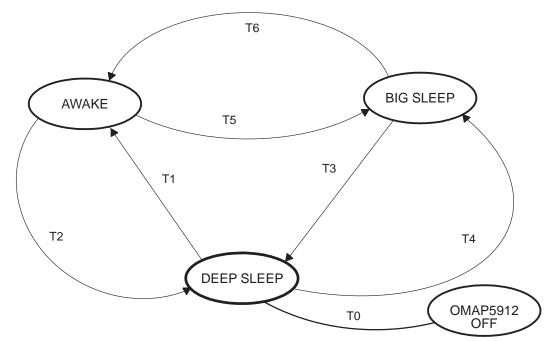

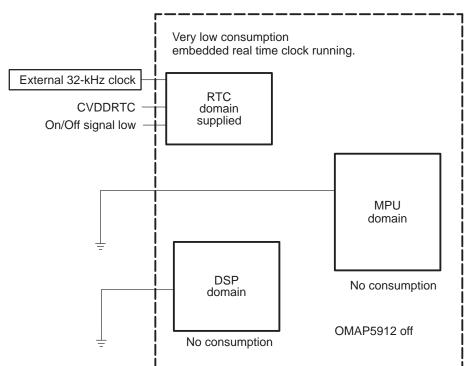

| 48 MHz for<br>MMCSDIO2   | • CONF_MOD_MMC_SD2_CLK_REQ_R • SOFT_REQ_REG[13]                                                                                                                       | Т6            | T5                                                             | T5    |  |