# OMAP5912 Multimedia Processor Peripheral Interconnects Reference Guide

Literature Number: SPRU758A March 2004

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated

# **Read This First**

#### About This Manual

This document describes various peripheral interconnects of the OMAP5912 multimedia processor.

#### **Notational Conventions**

This document uses the following conventions.

Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

#### Related Documentation From Texas Instruments

The following documents describe the OMAP5910 device and related peripherals. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

- OMAP5912 Multimedia Processor Device Overview and Architecture Reference Guide (literature number SPRU748) introduces the setup, components, and features of the OMAP5912 multimedia processor and provides a high-level view of the device architecture.

- OMAP5912 Multimedia Processor OMAP 3.2 Subsystem Reference Guide (literature number SPRU749) introduces and briefly defines the main features of the OMAP3.2 subsystem of the OMAP5912 multimedia processor.

- OMAP5912 Multimedia Processor DSP Sybsystem Reference Guide (literature number SPRU750) describes the OMAP5912 multimedia processor DSP subsystem. The digital signal processor (DSP) subsystem is built around a core processor and peripherals that interface with: 1) The ARM926EJS via the microprocessor unit interface (MPUI); 2) Various standard memories via the external memory interface (EMIF); 3) Various system peripherals via the TI peripheral bus (TIPB) bridge.

SPRU758A OMAP5912 3

- OMAP5912 Multimedia Processor Clocks Reference Guide (literature number SPRU751) describes the clocking mechanisms of the OMAP5912 multimedia processor. In OMAP5912, various clocks are created from special components such as the digital phase locked loop (DPLL) and the analog phase-locked loop (APLL).

- OMAP5912 Multimedia Processor Initialization Reference Guide (literature number SPRU752) describes the reset architecture, the configuration, the initialization, and the boot ROM of the OMAP5912 multimedia processor.

- OMAP5912 Multimedia Processor Power Management Reference Guide (literature number SPRU753) describes power management in the OMAP5912 multimedia processor. The ultralow-power device (ULPD) generates and manages clocks and reset signals to OMAP3.2 and to some peripherals. It controls chip-level power-down modes and handles chip-level wake-up events. In deep sleep mode, this module is still active to monitor wake-up events. This book describes the ULPD module and outline architecture.

- OMAP5912 Multimedia Processor Security Features Reference Guide (literature number SPRU754) describes the security features of teh OMAP5912 multimedia processor. The OMAP5912 security scheme relies on the OMAP3.2 secure mode. The distributed security on the OMAP3.2 platform is a Texas Instruments solution to address m-commerce and security issues within a mobile phone environment. The OMAP3.2 secure mode was developed to bring hardware robustness to the overall OMAP5912 security scheme.

- OMAP5912 Multimedia Processor Direct Memory Access (DMA) Support Reference Guide (literature number SPRU755) describes the direct memory access support of the OMAP5912 multimedia processor. The OMAP5912 processor has three DMAs:

- The system DMA is embedded in OMAP3.2. It handles DMA transfers associated with MPU and shared peripherals.

- The DSP DMA is embedded in OMAP3.2. It handles DMA transfers associated with DSP peripherals.

- The generic distributed DMA (GDD) is an OMAP5912 resource attached to the SSI peripheral. It handles only DMA transfers associated with the SSI peripheral.

4 OMAP5912 SPRU758A

OMAP5912 Multimedia Processor Memory Interfaces Reference Guide (literature number SPRU756) describes the memory interfaces of the OMAP5912 multimedia processor.

- SDRAM (external memory interface fast, or EMIFF)

- Asynchronous and synchronous burst memory (external memory interface slow, or EMIFS)

- NAND flash (hardware controller or software controller)

- CompactFlash on EMIFS interface

- Internal static RAM

OMAP5912 Multimedia Processor Interrupts Reference Guide (literature number SPRU757) describes the interrupts of the OMAP5912 multimedia processor. Three level 2 interrupt controllers are used in OMAP5912:

- One MPU level 2 interrupt handler (also referred to as MPU interrupt level 2) is implemented outside of OMAP3.2 and can handle 128 interrupts.

- One DSP level 2 interrupt handler (also referred to as DSP interrupt level 2.1) is instantiated outside of OMAP3.2 and can handle 64 interrupts.

- One OMAP3.2 DSP level 2 interrupt handler (referenced as DSP interrupt level 2.0) can handle 16 interrupts.

- OMAP5912 Multimedia Processor Peripheral Interconnects Reference Guide (literature number SPRU758) describes various periperal interconnects of the OMAP5912 multimedia processor.

- OMAP5912 Multimedia Processor Timers Reference Guide (literature number SPRU759) describes various timers of the OMAP5912 multimedia processor.

- OMAP5912 Multimedia Processor Serial Interfaces Reference Guide (literature number SPRU760) describes the serial interfaces of the OMAP5912 multimedia processor.

OMAP5912 Multimedia Processor Universal Serial Bus (USB) Reference Guide (literature number SPRU761) describes the universal serial bus (USB) host on the OMAP5912 multimedia processor. The OMAP5912 processor provides several varieties of USB functionality. Flexible multiplexing of signals from the OMAP5912 USB host controller, the OMAP5912 USB function controller, and other OMAP5912 peripherals allow a wide variety of system-level USB capabilities. Many of the OMAP5912 pins can be used for USB-related signals or for signals from other OMAP5912 peripherals. The OMAP5912 top-level pin multiplexing

SPRU758A OMAP5912 5

controls each pin individually to select one of several possible internal pin signal interconnections. When these shared pins are programmed for use as USB signals, the OMAP5912 USB signal multiplexing selects how the signals associated with the three OMAP5912 USB host ports and the OMAP5912 USB function controller can be brought out to OMAP5912 pins.

- OMAP5912 Multimedia Processor Multi-channel Buffered Serial Ports (McBSPs) Reference Guide (literature number SPRU762) describes the three multi-channel buffered serial ports (McBSPs) available on the OMAP5912 device. The OMAP5912 device provides multiple highspeed multichannel buffered serial ports (McBSPs) that allow direct interface to codecs and other devices in a system.

- OMAP5912 Multimedia Processor Camera Interface Reference Guide (literature number SPRU763) describes two camera inerfaces implemented in the OMAP5912 multimedia processor: compact serial camera port and camera parallel interface.

- OMAP5912 Multimedia Processor Display Interface Reference Guide (literature number SPRU764) describes the display interface of the OMAP5912 multimedia processor.

- LCD module

- LCD data conversion module

- LED pulse generator

- Display interface

- OMAP5912 Multimedia Processor Multimedia Card (MMC/SD/SDIO) (literature number SPRU765) describes the multimedia card (MMC) interface of the OMAP5912 multimedia processor. The multimedia card/secure data/secure digital IO (MMC/SD/SDIO) host controller provides an interface between a local host, such as a microprocessor unit (MPU) or digital signal processor (DSP), and either an MMC or SD memory card, plus up to four serial flash cards. The host controller handles MMC/SD/SDIO or serial port interface (SPI) transactions with minimal local host intervention.

- OMAP5912 Multimedia Processor Keyboard Interface Reference Guide (literature number SPRU766) describes the keyboard interface of the OMAP5912 multimedia processor. The MPUIO module enables direct I/O communication between the MPU (through the public TIPB) and external devices. Two types of I/O can be used: specific I/Os dedicated for 8 x 8 keyboard connection, and general-purpose I/Os.

- OMAP5912 Multimedia Processor General-Purpose Interface Reference Guide (literature number SPRU767) describes the general-purpose in-

6 OMAP5912 SPRU758A

terface of the OMAP5912 multimedia processor. There are four GPIO modules in the OMAP5912. Each GPIO peripheral controls 16 dedicated pins configurable either as input or output for general purposes. Each pin has an independent control direction set by a programmable register. The two–edge control registers configure events (rising edge, falling edge, or both edges) on an input pin to trigger interrupts or wake–up requests (depending on the system mode). In addition, an interrupt mask register masks out specified pins. Finally, the GPIO peripherals provide the set and clear capabilities on the data output registers and the interrupt mask registers. After detection, all event sources are merged and a single synchronous interrupt (per module) is generated in active mode, whereas a unique wake–up line is issued in idle mode. Eight data output lines of the GPIO3 are ORed together to generate a global output line at the OMAP5912 boundary. This global output line can be used in conjunction with the SSI to provide a CMT–APE interface to the OMAP5912.

OMAP5912 Multimedia Processor VLYNQ Serial Communications Interface Reference Guide (literature number SPRU768) describes the VLYNQ of the OMAP5912 multimedia processor.

VLYNQ is a serial communications interface that enables the extension of an internal bus segment to one or more external physical devices. The external devices are mapped into local, physical address space and appear as if they are on the internal bus of the OMAP 5912. The external devices must also have a VLYNQ interface. The VLYNQ module serializes bus transactions in one device, transfers the serialized data between devices via a VLYNQ port, and de-serializes the transaction in the external device.

OMAP5912 includes one VLYNQ module connected on OCPT2 target port and OCPI initiator port. These connections are configured via a static switch, which selects either SSI or VLYNQ module. This switch, forbids the simultaneous use of GDD/SSI and VLYNQ. The switch is controlled by the VLYNQ\_EN bit in the OMAP5912 configuration control register (CONF\_5912\_CTRL).

OMAP5912 Multimedia Processor Pinout Reference Guide (literature number SPRU769) provides the pinout of the OMAP5912 multimedia processor. After power-up reset, the user can change the configuration of the default interfaces. If another interface is available on top of the default, it is possible to enable a new interface for each ball by setting the corresponding 3-bit field of the associated FUNC\_MUX\_CTRL register. It is also possible to configure on-chip pullup/pulldown. This document

SPRU758A OMAP5912 7

also describes the various power domains so that the user can apply the different interfaces seamlessly with external components.

OMAP5912 Multimedia Processor Window Tracer (WT) Reference Guide (literature number SPRU770) describes the window tracer module used to capture the memory transactions from four interfaces: EMIFF, EMIFS, OCP-T1, and OCP-T2. This module is located in the OMAP3.2 traffic controller (TC).

OMAP5912 Multimedia Processor Real-Time Clock Reference Guide (literature number SPRUxxx) describes the real-time clock of the OMAP5912 multimedia processor. The real-time clock (RTC) block is an embedded real-time clock module directly accessible from the TIPB bus interface.

#### **Trademarks**

OMAP and the OMAP symbol are trademarks of Texas Instruments.

8 OMAP5912 SPRU758A

# **Contents**

| 1 | Share | ed Perip | herals                                     | . 13 |

|---|-------|----------|--------------------------------------------|------|

| 2 | Lavei | 4 Inter  | connect                                    | . 20 |

|   | 2.1   |          | outer Connections                          |      |

|   | 2.2   |          | ols                                        |      |

|   | 2.3   |          | ic Switch                                  |      |

|   | 2.4   | -        | onal Description                           |      |

|   |       | 2.4.1    | Bus Allocation                             |      |

|   |       |          | MPU/DSP TIPB Bridge to Peripherals         |      |

|   |       |          | Peripherals to MPU/DSP TIPB Bridge         |      |

|   |       | 2.4.2    | 16-bit Accesses on 32-Bit Atomic Registers |      |

|   |       | 2.4.3    | Conflicting Transaction                    |      |

|   |       | 2.4.4    | Abort Transaction                          |      |

|   |       | 2.4.5    | Reset Methodology                          |      |

|   | 2.5   | Static S | Switch                                     |      |

|   |       | 2.5.1    | Simultaneous Access                        |      |

|   |       | 2.5.2    | TIPB to OCP Interface                      |      |

|   | 2.6   | Abort T  | ransaction                                 |      |

|   | 2.7   |          | eral Static Switch Configuration Registers |      |

|   |       | 2.7.1    | Reset Methodology                          |      |

|   | 2.8   | TIPB1-   | VIA/VIA-TIPB Wrapper                       |      |

|   |       | 2.8.1    | Reset Methodology                          |      |

|   | 2.9   | _        | OCP/OCP-TIPB Wrapper                       |      |

|   |       | 2.9.1    | Reset Methodology                          |      |

|   |       | 2.9.2    | DSP TIPB to OCP                            |      |

|   |       | 2.9.3    | MPU TIPB to OCP                            |      |

|   | 2.10  | TIPB-C   | OCP/OCP-TIPB Wrapper for USBOTG            |      |

|   |       |          | Reset Methodology                          |      |

|   | 2.11  |          | couter                                     |      |

|   | 2.12  |          | eral Instantiation                         |      |

| 3 | ОСР   | Intercor | nnect                                      | . 37 |

|   | 3.1   | OCP Ir   | ntroduction                                | . 38 |

|   | 3.2   | Module   | Features                                   | . 40 |

|   | 3.3   | 1x OCF   | P Slave Port                               | . 40 |

|   | 3.4   | 1/2x O   | CP Slave Port                              | . 40 |

#### Contents

|   | 3.5    | 1x OC   | P Master Port                                | <br> | . 41 |

|---|--------|---------|----------------------------------------------|------|------|

|   | 3.6    | Addre   | ss Space                                     | <br> | . 41 |

|   | 3.7    |         | r Block                                      |      |      |

|   | 3.8    | Buffer  | Block                                        | <br> | . 41 |

| 4 | SSI Ir | ntercon | nect                                         | <br> | . 42 |

|   | 4.1    | Introdu | uction                                       | <br> | . 42 |

|   | 4.2    | OCP t   | o VIA Asynchronous Bridge                    | <br> | . 43 |

|   | 4.3    |         | o VIA Synchronous Bridge                     |      |      |

|   | 4.4    | Decod   | le                                           | <br> | . 44 |

|   | 4.5    |         | and Interrupt Formatter                      |      |      |

|   | 4.6    | Clock   | and Reset Module                             | <br> | . 45 |

|   | 4.7    | Progra  | amming Model                                 | <br> | . 45 |

|   |        | 4.7.1   | OCPI REGISTERS (MPU Address: FFFE:C320)      | <br> | . 45 |

|   |        | 4.7.2   | OCPT REGISTERS (MPU Address: FFFE:CC00)      | <br> | . 45 |

|   |        | 4.7.3   | Power Saving Modes                           |      |      |

| 5 | On-C   | hip/Off | -Chip Memory and Peripheral Access Latencies | <br> | . 45 |

10 OMAP5912 SPRU758A

# **Figures**

| 1  | Peripherals Access                | . 14 |

|----|-----------------------------------|------|

| 2  | Layer 4 Interface                 | . 21 |

| 3  | Dynamic Switch for OCP Peripheral |      |

| 4  | Transfer from Host to Peripheral  | . 25 |

| 5  | Transfer from Peripheral to Host  | . 25 |

| 6  | Static Switch for OCP Peripheral  | . 27 |

| 7  | TIPB Router Block Diagram         | . 34 |

| 8  | OCP and SSI Interconnects         | . 38 |

| 9  | OCP Interconnect                  | . 39 |

| 10 | SSI Interconnect                  | . 43 |

SPRU758A OMAP5912 11

# **Tables**

| 1  | MPU/DSP Peripheral Access                                                | 4          |

|----|--------------------------------------------------------------------------|------------|

| 2  | Private Peripherals                                                      | 22         |

| 3  | MPU Peripherals Connected to MPU Shared TIPB Bridge                      | 22         |

| 4  | DSP Peripherals Connected to DSP Shared TIPB Bridge                      |            |

| 5  | DSP and MPU Shared Peripherals                                           | 23         |

| 6  | Static Switch Configuration Registers Offset Addresses                   | 29         |

| 7  | Peripheral MPU Static Switch Configuration Register (xxx_SSW_MPU_CONF) 3 | 31         |

| 8  | Peripheral DSP Static Switch Configuration Register (xxx_SSW_DSP_CONF) 3 | 31         |

| 9  | Private Peripherals Instantiation                                        | 35         |

| 10 | MPU Peripherals Connected to the MPU Shared TIPB Bridge Instantiation    | 36         |

| 11 | DSP Peripherals Connected to the DSP Shared TIPB Bridge Instantiation    | 37         |

| 12 | DSP and MPU Shared Peripherals Instantiation                             | 37         |

| 13 | GDD/SSI Address Space                                                    | ŀ1         |

| 14 | SSI Address Spaces                                                       |            |

| 15 | OMAP3.2 Timing Parameters                                                |            |

| 16 | Peripheral Access Time Calculations                                      | <b>ļ</b> 7 |

12 OMAP5912 SPRU758A

# **Peripheral Interconnects**

This document describes various peripheral interconnects of the OMAP5912 multimedia processor.

# 1 Shared Peripherals

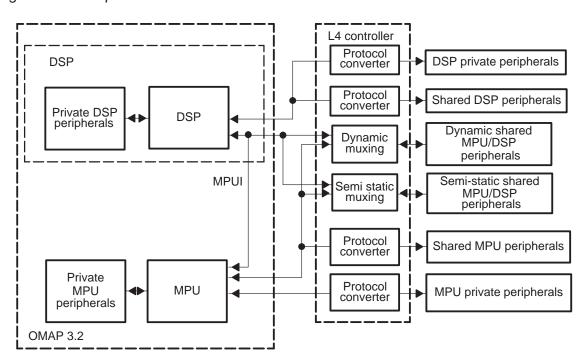

Outside OMAP 3.2, the OMAP5912 includes several peripherals. They can be considered shared by the MPU and the DSP, or can be DSP or MPU private.

Privacy is mainly driven by the performance requested by the peripheral. OMAP provides four peripheral buses:

|        | 16-bit data bus DSP private |

|--------|-----------------------------|

|        | 16-bit data bus DSP shared  |

|        | 32-bit data bus MPU private |

| $\Box$ | 32-bit data bus MPU shared  |

OMAP supports one bus protocol: the TIPB protocol.

The TIPB protocol enables unidirectional asynchronous transfer from or to peripherals to or from CPUs/DMAs.

Both shared buses ((MPU + system DMA) and (DSP + DSPDMA)) are multiplexed in the L4 interface either dynamically or semistatically to communicate with all the shared peripherals.

The L4 interface groups a set of wrappers (or protocol converter), a dynamic switch, and a static switch. They enable interface with all the peripherals, regardless of their interface protocol with the MPU and DSP peripheral buses.

The DSP peripherals are also accessible from the MPU via the DSP MPUI port (see Figure 1).

Figure 1. Peripherals Access

Table 1 lists the following for each module:

- On which bus the module resides

- ☐ Whether a DMA can initiate a transaction to the peripheral

- ☐ Whether the module can be accessed dynamically by each processor or the corresponding static switch must be configured

Table 1. MPU/DSP Peripheral Access

|                | MPU I        | Domain       |                      | DSP Domain             |           |         |                      |

|----------------|--------------|--------------|----------------------|------------------------|-----------|---------|----------------------|

| Module<br>Name | MPU Start    | MPU End      | MPU TIPB<br>Bus Type | L4 Controler<br>Switch | DSP Start | DSP End | DSP TIPB<br>Bus Type |

| DPLL1          | FFFE<br>CF00 | FFFE<br>CFFF | Private              |                        |           |         |                      |

| CLKM           | FFFE<br>CE00 | FFFE<br>CEFF | Private              |                        |           |         |                      |

| ULPD           | FFFE 0800    | FFFE 0FFF    | Private              |                        |           |         |                      |

Note: The SSI and the GDD modules are on the L3-OCP2 port and thus are seen as part of memory port interface.

Table 1. MPU/DSP Peripheral Access (Continued)

|                                          | MPU [        | Domain    |                      | DSP Domain             |           |              |                      |  |

|------------------------------------------|--------------|-----------|----------------------|------------------------|-----------|--------------|----------------------|--|

| Module<br>Name                           | MPU Start    | MPU End   | MPU TIPB<br>Bus Type | L4 Controler<br>Switch | DSP Start | DSP End      | DSP TIPB<br>Bus Type |  |

| OMAP<br>5912<br>configuratio<br>n        | FFFE 1000    | FFFE 17FF | Private              |                        |           |              |                      |  |

| 32-kHz<br>synchroniz<br>ation<br>counter | FFFB<br>C400 | FFFB C7FF | Shared               | Dynamic                | E101 C400 | E101<br>C7FF | Shared               |  |

| Secure<br>watchdog                       | FFFE A800    | FFFE AFFF | Private              |                        |           |              |                      |  |

| 32-kHz<br>watchdog                       | FFFE B000    | FFFE B7FF | Private              |                        |           |              |                      |  |

| RTC                                      | FFFB 4800    | FFFB 4FFF | Shared               |                        |           |              |                      |  |

| RNG                                      | FFFE 5000    | FFFE 57FF | Private              |                        |           |              |                      |  |

| DES/3DES                                 | FFFE 4000    | FFFE 47FF | Private              |                        |           |              |                      |  |

| SHA-<br>1/MD5                            | FFFE 4800    | FFFE 4FFF | Private              |                        |           |              |                      |  |

| OMAP<br>MPU timer1                       | FFFE<br>C500 | FFFE C5FF | Private              |                        |           |              |                      |  |

| OMAP<br>MPU timer2                       | FFFE<br>C600 | FFFE C6FF | Private              |                        |           |              |                      |  |

| OMAP<br>MPU timer3                       | FFFE<br>C700 | FFFE C7FF | Private              |                        |           |              |                      |  |

| OMAP<br>watchdog<br>timer                | FFFE<br>C800 | FFFE C8FF | Private              |                        |           |              |                      |  |

| OS timer                                 | FFFB 9000    | FFFB 93FF | Shared               |                        |           |              |                      |  |

| L3 OCP initiator                         | FFFE<br>C300 | FFFE C3FF | Private              |                        |           |              |                      |  |

Table 1. MPU/DSP Peripheral Access (Continued)

|                                     | MPU [        | Domain       |                      |                        | DSP Do    | main         |                      |

|-------------------------------------|--------------|--------------|----------------------|------------------------|-----------|--------------|----------------------|

| Module<br>Name                      | MPU Start    | MPU End      | MPU TIPB<br>Bus Type | L4 Controler<br>Switch | DSP Start | DSP End      | DSP TIPB<br>Bus Type |

| L3 OCP T1 interface                 | FFFE<br>C100 | FFFE C1FF    | Private              |                        |           |              |                      |

| OMAP5912<br>TIPB switch             | FFFB<br>C800 | FFFB<br>CBFF | Shared               | Semi-static            | E101 C800 | E101<br>CBFF | Shared               |

| TIPB bridge (internal)              | FFFE<br>CA00 | FFFE<br>CAFF | Private              |                        |           |              |                      |

| TIPB<br>bridge2<br>(external)       | FFFE<br>D300 | FFFE D3FF    | Private              |                        |           |              |                      |

| MPUI<br>interface                   | FFFE<br>C900 | FFFE C9FF    | Private              |                        |           |              |                      |

| DSP MMU                             | FFFE<br>D200 | FFFE D2FF    | Private              |                        |           |              |                      |

| Traffic controller                  | FFFE<br>CC00 | FFFE<br>CCFF | Private              |                        |           |              |                      |

| Gigacell<br>mailbox                 | FFFB F000    | FFFB F7FF    | Shared               | Semi-static            | E101 F000 | E101<br>F7FF | Shared               |

| Mailbox                             | FFFC F000    | FFFC F7FF    | Shared               |                        |           |              |                      |

| DSP TIPB                            |              |              |                      |                        | E100 0000 | E100<br>07FF | Shared               |

| MGS3<br>MPUI<br>control<br>register |              |              |                      |                        | E102 0000 | E102<br>0003 | Shared               |

| System<br>DMA                       | FFFE<br>D800 | FFFE<br>DFFF | Private              |                        |           |              |                      |

| System<br>DMA                       | FFFE E000    | FFFE E7FF    | Private              |                        |           |              |                      |

| MPU level<br>1 interrupt<br>handler | FFFE<br>CB00 | FFFE<br>CBFF | Private              |                        |           |              |                      |

Table 1. MPU/DSP Peripheral Access (Continued)

|                                     | MPU I        | Domain    |                      | DSP Domain             |           |              |                      |  |

|-------------------------------------|--------------|-----------|----------------------|------------------------|-----------|--------------|----------------------|--|

| Module<br>Name                      | MPU Start    | MPU End   | MPU TIPB<br>Bus Type | L4 Controler<br>Switch | DSP Start | DSP End      | DSP TIPB<br>Bus Type |  |

| MPU level<br>2 interrupt<br>handler | FFFE 0000    | FFFE 07FF | Private              |                        |           |              |                      |  |

| MPUIO                               | FFFB 5000    | FFFB 57FF | Shared               |                        |           |              |                      |  |

| GPIO1                               | FFFB E400    | FFFB E7FF | Shared               | Dynamic                | E101 E400 | E101<br>E7FF | Shared               |  |

| GPIO2                               | FFFB<br>EC00 | FFFB EFFF | Shared               | Dynamic                | E101 EC00 | E101<br>EFFF | Shared               |  |

| GPIO3                               | FFFB B400    | FFFB B7FF | Shared               | Dynamic                | E101 B400 | E101<br>B7FF | Shared               |  |

| GPIO4                               | FFFB<br>BC00 | FFFB BFFF | Shared               | Dynamic                | E101 BC00 | E101<br>BFFF | Shared               |  |

| PWL                                 | FFFB 5800    | FFFB 5FFF | Shared               |                        |           |              |                      |  |

| PWT                                 | FFFB 6000    | FFFB 67FF | Shared               |                        |           |              |                      |  |

| GP<br>timer 1                       | FFFB 1400    | FFFB 17FF | Shared               | Semi-static            | E101 1400 | E101<br>17FF | Shared               |  |

| GP<br>timer 2                       | FFFB<br>1C00 | FFFB 1FFF | Shared               | Semi-static            | E101 1C00 | E101<br>1FFF | Shared               |  |

| GP<br>timer 3                       | FFFB 2400    | FFFB 27FF | Shared               | Semi-static            | E101 2400 | E101<br>27FF | Shared               |  |

| GP<br>timer 4                       | FFFB<br>2C00 | FFFB 2FFF | Shared               | Semi-static            | E101 2C00 | E101<br>2FFF | Shared               |  |

| GP<br>timer 5                       | FFFB 3400    | FFFB 37FF | Shared               | Semi-static            | E101 3400 | E101<br>37FF | Shared               |  |

| GP<br>timer 6                       | FFFB<br>3C00 | FFFB 3FFF | Shared               | Semi-static            | E101 3C00 | E101<br>3FFF | Shared               |  |

| GP<br>timer 7                       | FFFB 7400    | FFFB 77FF | Shared               | Semi-static            | E101 7400 | E101<br>77FF | Shared               |  |

Table 1. MPU/DSP Peripheral Access (Continued)

|                          | MPU I        | Domain       |                      | DSP Domain             |           |              |                      |  |

|--------------------------|--------------|--------------|----------------------|------------------------|-----------|--------------|----------------------|--|

| Module<br>Name           | MPU Start    | MPU End      | MPU TIPB<br>Bus Type | L4 Controler<br>Switch | DSP Start | DSP End      | DSP TIPB<br>Bus Type |  |

| GP<br>timer 8            | FFFB<br>D400 | FFFB D7FF    | Shared               | Semi-static            | E101 D400 | E101<br>D7FF | Shared               |  |

| LCDCONV                  | FFFE 3000    | FFFE 37FF    | Private              |                        |           |              |                      |  |

| LCD<br>controller        | FFFE<br>C000 | FFFE C0FF    | Private              |                        |           |              |                      |  |

| LPG1                     | FFFB<br>D000 | FFFB D3FF    | Shared               |                        |           |              |                      |  |

| LPG2                     | FFFB<br>D800 | FFFB BFFF    | Shared               |                        |           |              |                      |  |

| McBSP1                   |              |              |                      |                        | E101 1800 | E101<br>1BFF | Shared               |  |

| McBSP2                   | FFFB 1000    | FFFB 13FF    | Shared               | Semi-static            | E101 1000 | E101<br>13FF | Shared               |  |

| McBSP3                   |              |              |                      |                        | E101 7000 | E101<br>73FF | Shared               |  |

| MCSI1                    |              |              |                      |                        | E101 2800 | E101<br>2BFF | Shared               |  |

| MCSI2                    |              |              |                      |                        | E101 2000 | E101<br>23FF | Shared               |  |

| Memory<br>Stick          | FFFB 8000    | FFFB 83FF    | Shared               |                        |           |              |                      |  |

| MMC/SDIO<br>1            | FFFB 7800    | FFFB 7BFF    | Shared               |                        |           |              |                      |  |

| MMC/SDIO<br>2            | FFFB<br>7C00 | FFFB 7FFF    | Shared               | Semi-static            | E101 7C00 | E101<br>7FFF | Shared               |  |

| Compact flash controller | FFFE 2800    | FFFE 2FFF    | Private              |                        |           |              |                      |  |

| NAND flash controller    | FFFB<br>CC00 | FFFB<br>CFFF | Shared               |                        |           |              |                      |  |

Table 1. MPU/DSP Peripheral Access (Continued)

|                                      | MPU I        | Domain       |                      | DSP Domain             |           |              |                      |  |

|--------------------------------------|--------------|--------------|----------------------|------------------------|-----------|--------------|----------------------|--|

| Module<br>Name                       | MPU Start    | MPU End      | MPU TIPB<br>Bus Type | L4 Controler<br>Switch | DSP Start | DSP End      | DSP TIPB<br>Bus Type |  |

| SoSSI                                | FFFB<br>AC00 | FFFB AFFF    | Shared               |                        |           |              |                      |  |

| SPI                                  | FFFB<br>0C00 | FFFB 0FFF    | Shared               | Semi-static            | E101 0C00 | E101<br>0FFF | Shared               |  |

| UART1                                | FFFB 0000    | FFFB 03FF    | Shared               | Semi-static            | E101 0000 | E101<br>07FF | Shared               |  |

| UART2                                | FFFB 0800    | FFFB 0BFF    | Shared               | Semi-static            | E101 0800 | E101<br>0BFF | Shared               |  |

| UART3                                | FFFB 9800    | FFFB 9BFF    | Shared               | Semi-static            | E101 9800 | E101<br>9BFF | Shared               |  |

| FAC                                  | FFFB A800    | FFFB<br>ABFF | Shared               |                        |           |              |                      |  |

| USB<br>client                        | FFFB 4000    | FFFB 43FF    | Shared               |                        |           |              |                      |  |

| USB host                             | FFFB A000    | FFFB A3FF    | Shared               |                        |           |              |                      |  |

| USB OTG                              | FFFB 0400    | FFFB 07FF    | Shared               |                        |           |              |                      |  |

| I <sup>2</sup> C<br>multi-<br>master | FFFB 3800    | FFFB 3BFF    | Shared               | Semi-static            | E101 3800 | E101<br>3BFF | Shared               |  |

| $\mu \text{Wire}$                    | FFFB 3000    | FFFB 33FF    | Shared               |                        |           |              |                      |  |

| HDQ<br>1-Wire                        | FFFB<br>C000 | FFFB C3FF    | Shared               |                        |           |              |                      |  |

| STI<br>(reserved)                    | FFFE A000    | FFFE A7FF    | Private              | Dynamic                | E101 A400 | E101<br>A7FF | Shared               |  |

| OMAP5912<br>JTAG (test)              | FFFE 5800    | FFFE 5FFF    | Private              |                        |           |              |                      |  |

| BCM (test)                           | FFFE 3800    | FFFE 3FFF    | Private              |                        |           |              |                      |  |

| Production<br>ID (test)              | FFFE 2000    | FFFE 27FF    | Private              |                        |           |              |                      |  |

Table 1. MPU/DSP Peripheral Access (Continued)

| MPU Domain               |              |           |                      | DSP Domain             |           |              |                      |

|--------------------------|--------------|-----------|----------------------|------------------------|-----------|--------------|----------------------|

| Module<br>Name           | MPU Start    | MPU End   | MPU TIPB<br>Bus Type | L4 Controler<br>Switch | DSP Start | DSP End      | DSP TIPB<br>Bus Type |

| Die ID<br>(test)         | FFFE 1800    | FFFE 1FFF | Private              |                        |           |              |                      |

| Test block<br>(PSA test) | FFFE<br>D400 | FFFE D4FF | Private              |                        |           |              |                      |

| DSP trace                |              |           |                      |                        | E100 4000 | E100<br>47FF | Private              |

# 2 Layer 4 Interconnect

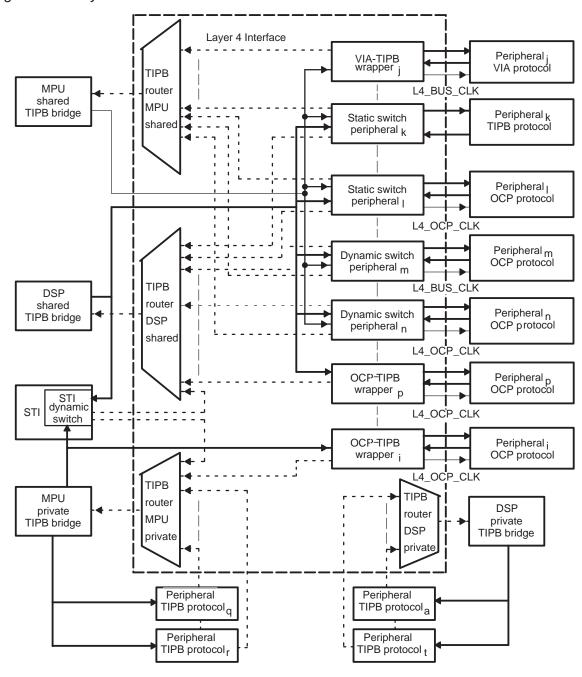

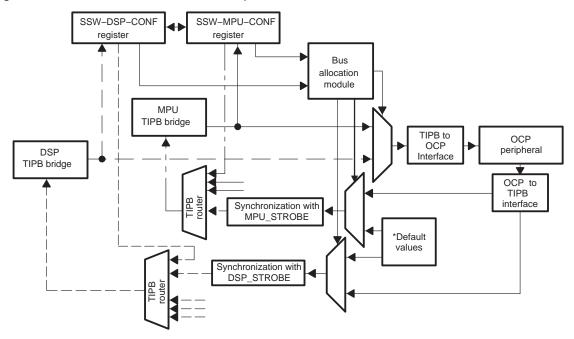

The layer 4 interface manages accesses to OMAP5912 peripherals through the MPU shared TIPB bridge, DSP shared TIPB bridge, MPU private TIPB bridge, and DSP private TIPB bridge. DSP TIPB bridges are inside the C55x DSP. It is composed of a set of dynamic and static switches and wrappers dedicated to the access protocol of each peripheral. The MPU TIPB bridge is already a merge of MPU and system DMA signals for peripheral accesses. The DSP TIPB bridge is already a merge of DSP and system DMA signals for peripheral accesses (see Figure 2).

Two different switches are implemented:

|     | Static TIPB/OCP: OCP/TIPB switch (configuration register included)                                                                                                                        |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Dynamic TIPB/OCP: OCP/TIPB switch with resynchronization on MPU and DSP accesses                                                                                                          |

| Tw  | o different wrappers are provided:                                                                                                                                                        |

|     | TIPB/VIA: VIA/TIPB wrapper with resynchronization                                                                                                                                         |

|     | MPU (or DSP) TIPB/OCP: OCP/TIPB wrapper                                                                                                                                                   |

| TIP | e common protocol on the MPU/DSP side is the TIPB bus protocol. For each PB bridge, a dedicated router is implemented to allow the multiplexing of all return paths from the peripherals. |

|     | MPU shared TIPB router to MPU shared TIPB bridge                                                                                                                                          |

|     | DSP shared TIPB router to DSP shared TIPB bridge                                                                                                                                          |

- ☐ MPU private TIPB router to MPU private TIPB bridge

- □ DSP private TIPB router to DSP private TIPB bridge

Figure 2. Layer 4 Interface

# 2.1 TIPB Router Connections

Table 2. Private Peripherals

| OMAP 5912 Peripheral          | Interface   | TIPB Router |

|-------------------------------|-------------|-------------|

| DSP level 2 interrupt handler | Wrapper OCP | Private DSP |

| ULPD (clock and reset)        | TIPB        | Private MPU |

| OMAP5912 configuration        | TIPB        | Private MPU |

| Secure watchdog               | Wrapper OCP | Private MPU |

| 32-kHz watchdog               | Wrapper OCP | Private MPU |

| MPU level 2 interrupt handler | Wrapper OCP | Private MPU |

| SHA_1 accelerator             | Wrapper OCP | Private MPU |

| RNG random generator          | Wrapper OCP | Private MPU |

| DES/3DES                      | Wrapper OCP | Private MPU |

| System DMA handler            | Wrapper OCP | Private MPU |

Table 3. MPU Peripherals Connected to MPU Shared TIPB Bridge

| OMAP 5912 Peripheral | Interface   | TIPB Router |

|----------------------|-------------|-------------|

| HDQ/1-Wire           | TIPB        | Shared MPU  |

| μWIRE                | TIPB        | Shared MPU  |

| MMCSD/IO1            | Wrapper OCP | Shared MPU  |

| MPUIO                | TIPB        | Shared MPU  |

| 2 x LPG              | TIPB        | Shared MPU  |

| SoSSI                | Wrapper VIA | Shared MPU  |

| RTC                  | TIPB        | Shared MPU  |

| Memory Stick         | TIPB        | Shared MPU  |

| PWL                  | TIPB        | Shared MPU  |

| PWT                  | TIPB        | Shared MPU  |

| FAC                  | TIPB        | Shared MPU  |

| OS timer             | TIPB        | Shared MPU  |

| USBOTG               | Wrapper OCP | Shared MPU  |

Table 4. DSP Peripherals Connected to DSP Shared TIPB Bridge

| OMAP 5912 Peripheral | Interface   | TIPB Router |  |

|----------------------|-------------|-------------|--|

| 2 x MCSI             | TIPB        | Shared DSP  |  |

| 2 x McBSP            | Wrapper OCP | Shared DSP  |  |

Table 5. DSP and MPU Shared Peripherals

| OMAP 5912 Peripheral         | Interface   | TIPB Rou | ıter   |

|------------------------------|-------------|----------|--------|

|                              |             | MPU      | DSP    |

| MMCSD/IO2                    | Static OCP  | Shared   | Shared |

| STI (reserved)               | Dynamic OCP | Private  | Shared |

| 32-kHz synchronization timer | Dynamic OCP | Shared   | Shared |

| 4 x GPIO                     | Dynamic OCP | Shared   | Shared |

| GPIO                         | Dynamic OCP | Shared   | Shared |

| 3 x UART                     | Static OCP  | Shared   | Shared |

| McBSP                        | Static OCP  | Shared   | Shared |

| I <sup>2</sup> C             | Static OCP  | Shared   | Shared |

| SPI                          | Static OCP  | Shared   | Shared |

| 8 x GP timers                | Static OCP  | Shared   | Shared |

| NAND flash control           | Static OCP  | Shared   | Shared |

| Static switch configuration  | TIPB        | Shared   | Shared |

# 2.2 Protocols

The layer 4 interface is connected to several peripherals, which use different protocols:

☐ TI peripheral bus or TIPB bus

Versatile interconnection architecture designated also as VIA bus or VIA protocol

Open core protocol designated as OCP

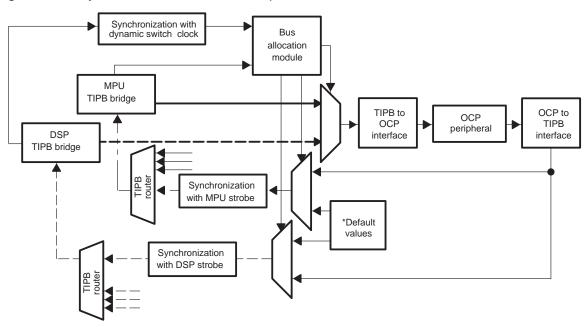

# 2.3 Dynamic Switch

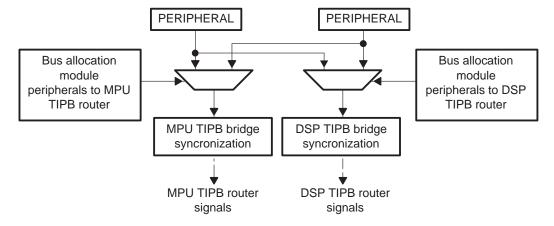

Figure 3. Dynamic Switch for OCP Peripheral

**Note:** Default value: To simplify the TIPB router implementation and reduce the toggling on buses, a default value is returned to the host, which does not access the peripheral.

# 2.4 Functional Description

#### 2.4.1 Bus Allocation

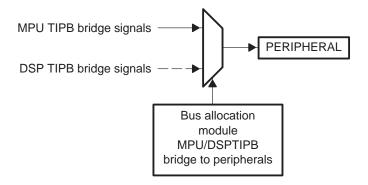

## MPU/DSP TIPB Bridge to Peripherals

The peripheral TIPB buses are shared between the MPU TIPB bridge and the DSP TIPB bridge. Both bridges can access the same peripheral. Therefore, a bus allocation module is required to decide which one can access to the peripheral bus in case of conflict. This arbitration occurs after a synchronization of the DSP enable signal with the dynamic switch clock (ARMPER\_CLK).

If no more than one of the two masters requests the bus, the bus is allocated to the requesting master. Otherwise, the MPU TIPB bridge takes control of the bus. DSP TIPB bridge accesses the peripheral after the data has been returned to the MPU TIPB bridge. During the transfer, the access size can be either 16-bit for the DSP or 8-, 16-, or 32-bit for the MPU.

Figure 4. Transfer from Host to Peripheral

# Peripherals to MPU/DSP TIPB Bridge

All peripherals can send data back on a dedicated bus (one bus per peripheral—8-, 16-, or 32-bit according to each peripheral requirement), either to the MPU or to the DSP.

Figure 5. Transfer from Peripheral to Host

**Note:** Default value: To simplify the TIPB router implementation and reduce the toggling on buses, a default value is returned to the host that does not access the peripheral.

#### 2.4.2 16-bit Accesses on 32-Bit Atomic Registers

There is no protection inside the dynamic switch to ensure the atomic reading or writing of one 32-bit register with two 16-bit accesses. The nonoverlapping requests from the two hosts must be controlled in the software.

# 2.4.3 Conflicting Transaction

When one host requires an access to the peripheral, an enable host signal is set (synchronously with the host strobe). With the DSP TIPB bridge strobe, a DSP TIPB bridge enable is generated, and with the MPU TIPB bridge strobe an MPU TIPB bridge enable is generated. DSP TIPB bridge enable and MPU TIPB bridge enable are then resynchronized with the dynamic switch clock to perform arbitration. This arbitration takes place during one dynamic switch clock cycle. In case of conflict, the MPU TIPB bridge has the priority and the DSP TIPB bridge waits until the ready has been sent to the MPU TIPB bridge. Then the DSP TIPB bridge performs its access.

#### 2.4.4 Abort Transaction

After a predetermined number of strobe cycles (DSP\_nStrobe or MPU\_nStrobe), if a peripheral does not activate its ready signal, the TIPB bridge generates an abort. The dynamic switch uses this abort to kill the current access. The maximum number of strobe cycles is programmable within the DSP TIPB bridge for DSP\_nStrobe, and within the MPU TIPB bridge for MPU nStrobe.

# 2.4.5 Reset Methodology

An MPU initiator reset is always used in the dynamic switch to reset an eventual MPU ongoing transaction. A DSP initiator reset is also used into the dynamic switch to reset an eventual DSP ongoing transaction.

#### 2.5 Static Switch

Figure 6. Static Switch for OCP Peripheral

**Note:** Default value: To simplify the TIPB router implementation and reduce the toggling on buses, a default value is returned to the host which does not access the peripheral.

The static switch module allows the switching of a given peripheral between two TIPB host buses. This module enables static sharing between the DSP and the MPU processors. The switch between the two TIPB buses is implemented through a basic protocol. The software must control carefully the accessibility of each shared peripheral by the desired host. The programmer must ensure that the ongoing DMA transfers from/to the peripheral are completed before updating the peripheral ownership. There is no protection from the static switch hardware.

If the static switch is not well programmed before an access to a shared peripheral register, the corresponding ready signal is not sent back to the host. The result is a time-out error generated by the host TIPB bridge, depending on the TIPB bridge programming.

Two registers control the accessibility from the host to each statically sharedperipheral:

- ☐ SSW\_MPU\_CONF in the MPU peripheral address space

- ☐ SSW\_DSP\_CONF in the DSP peripheral address space

To perform an MPU access, the MPU software must first set (write 1) the MPU\_SWITCH bit in the SSW\_MPU\_CONF register. Then all the MPU TIPB bus signals are connected either to the TIPB bus peripheral signals (for a TIPB peripheral), or to the dedicated wrapper TIPB bus interface (for OCP peripheral).

To perform a DSP access, the MPU software must first authorize this access by resetting the MPU\_SWITCH bit in the SSW\_MPU\_CONF register (write 0); then the DSP software must set the DSP\_SWITCH in the SSW\_DSP\_CONF register.

If the MPU wants to access the SSW\_MPU\_CONF register when the DSP\_SWITCH bit is set, the access is completed but a write access has no effect on the register.

Symmetrically, if the DSP wants to access the SSW\_DSP\_CONF register when the MPU\_SWITCH bit is set, the access is completed but a write access has no effect on the register.

The following programming sequence enables DSP access to the peripheral:

- 1) Check that the MPU\_SWITCH bit is reset (no MPU access is ongoing on the same peripheral).

- Set the DSP\_SWITCH bit in the SSW\_DSP\_CONF register (DSP software: write 1)

- Check that the DSP\_SWITCH is set (in case of priority conflict with the MPU software).

- 4) Perform the shared peripheral access through the DSP TIPB bus.

- 5) After the completion of this access, reset the DSP\_SWITCH bit in the SSW\_DSP\_CONF register (write 0).

The following programming sequence enables MPU access to the peripheral:

- Check that DSP\_SWITCH bit is reset (no DSP access is on going on the same peripheral).

- Set the MPU\_SWITCH bit in the SSW\_MPU\_CONF register (MPU software: write 1).

- Check that the MPU\_SWITCH is set (in case of priority conflict with the DSP software).

- 9) Perform the shared peripheral access through the MPU TIPB bus.

- After the completion of this access, reset the MPU\_SWITCH bit in the SSW\_MPU\_CONF register (write 0)

Depending on the host interface protocol for the peripheral, a dedicated wrapper is connected between the host and the peripheral bus. Two different peripheral protocols are supported:

□ TIPB

□ OCP

#### 2.5.1 Simultaneous Access

Setting both the DSP\_SWITCH bit and MPU\_SWITCH bits is impossible, by design. An access control and arbitration phase in the ARMPER\_CLK clock domain ensures that this programming conflict never occurs.

#### 2.5.2 TIPB to OCP Interface

A full resynchronization process between the MPU TIPB interface, the DSP TIPB interface, and the peripheral interface OCP clock is implemented. The TIPB bus is stalled until the decoding of the peripheral acknowledge by the wrapper. The decoded acknowledge is then synchronized with the TIPB strobe to generate the ready (end of TIPB transaction).

#### 2.6 Abort Transaction

After a predetermined number of strobe cycles (DSP\_nStrobe or MPU\_nStrobe), if a peripheral did not complete the transaction, the TIPB bridge generates an abort. The static switch uses this abort to kill the current access. The maximum number of strobe cycles is programmable, within the DSP TIPB bridge for DSP\_nStrobe, and within the MPU TIPB bridge for MPU\_nStrobe configuration registers.

# 2.7 Peripheral Static Switch Configuration Registers

The registers listed in Table 6 are accessible through the DSP shared TIPB bridge (16-bit access) or through the MPU shared TIPB bridge (16- or 32-bit accesses).

Table 6. Static Switch Configuration Registers Offset Addresses

| Register Name      | # Bits | Offset | Bus |

|--------------------|--------|--------|-----|

| UART1_SSW_MPU_CONF | 16/32  | 0x000  | MPU |

| UART1_SSW_DSP_CONF | 16     |        | DSP |

| UART2_SSW_MPU_CONF | 16/32  | 0x020  | MPU |

Table 6. Static Switch Configuration Registers Offset Addresses (Continued)

| Register Name       | # Bits | Offset | Bus |

|---------------------|--------|--------|-----|

| UART2_SSW_DSP_CONF  | 16     |        | DSP |

| UART3_SSW_MPU_CONF  | 16/32  | 0x040  | MPU |

| UART3_SSW_DSP_CONF  | 16     |        | DSP |

| McBSP_SSW_MPU_CONF  | 16/32  | 0x090  | MPU |

| McBSP_SSW_DSP_CONF  | 16     |        | DSP |

| I2C_SSW_MPU_CONF    | 16/32  | 0x0A0  | MPU |

| I2C_SSW_DSP_CONF    | 16     |        | DSP |

| SPI_SSW_MPU_CONF    | 16/32  | 0x0B0  | MPU |

| SPI_SSW_DSP_CONF    | 16     |        | DSP |

| TIMER1_SSW_MPU_CONF | 16/32  | 0x0C0  | MPU |

| TIMER1_SSW_DSP_CONF | 16     |        | DSP |

| TIMER2_SSW_MPU_CONF | 16/32  | 0x0D0  | MPU |

| TIMER2_SSW_DSP_CONF | 16     |        | DSP |

| TIMER3_SSW_MPU_CONF | 16/32  | 0x0E0  | MPU |

| TIMER3_SSW_DSP_CONF | 16     |        | DSP |

| TIMER4_SSW_MPU_CONF | 16/32  | 0x0F0  | MPU |

| TIMER4_SSW_DSP_CONF | 16     |        | DSP |

| TIMER5_SSW_MPU_CONF | 16/32  | 0x100  | MPU |

| TIMER5_SSW_DSP_CONF | 16     |        | DSP |

| TIMER6_SSW_MPU_CONF | 16/32  | 0x110  | MPU |

| TIMER6_SSW_DSP_CONF | 16     |        | DSP |

| TIMER7_SSW_MPU_CONF | 16/32  | 0x130  | MPU |

| TIMER7_SSW_DSP_CONF | 16     |        | DSP |

| TIMER8_SSW_MPU_CONF | 16/32  | 0x140  | MPU |

| TIMER8_SSW_DSP_CONF | 16     |        | DSP |

| NFCtrl_SSW_MPU_CONF | 16/32  | 0x150  | MPU |

Table 6. Static Switch Configuration Registers Offset Addresses (Continued)

| Register Name       | # Bits | Offset | Bus |

|---------------------|--------|--------|-----|

| NFCtrl_SSW_DSP_CONF | 16     |        | DSP |

| MMCSD2_SSW_MPU_CONF | 16/32  | 0x160  | MPU |

| MMCSD2_SSW_DSP_CONF | 16     |        | DSP |

For each static-shared peripheral, two registers are defined (Table 7 and Table 8): one is dedicated to MPU accesses, and the other to DSP accesses.

Table 7. Peripheral MPU Static Switch Configuration Register (xxx\_SSW\_MPU\_CONF)

|      | Base Address = FFFB C800, Offset Address = see Table 6 |                                                                        |        |            |  |  |  |

|------|--------------------------------------------------------|------------------------------------------------------------------------|--------|------------|--|--|--|

| Bit  | Name                                                   | Description                                                            | Access | Reset      |  |  |  |

| 31:2 | _                                                      | Reserved                                                               | R      | 0x00000000 |  |  |  |

| 1    | DSP_SWITCH                                             | No DSP TIPB bridge access required     DSP TIPB bridge access required | R      | 0          |  |  |  |

| 0    | MPU_SWITCH                                             | No MPU TIPB bridge access required     MPU TIPB bridge access required | RW     | 1          |  |  |  |

This register is only accessible through the MPU shared TIPB bridge.

It is used to perform MPU access on the peripheral.

Table 8. Peripheral DSP Static Switch Configuration Register (xxx\_SSW\_DSP\_CONF)

|      | Base Address = FFFB C800, Offset Address = see Table 6 |                                       |        |            |  |  |  |

|------|--------------------------------------------------------|---------------------------------------|--------|------------|--|--|--|

| Bit  | Name                                                   | Description                           | Access | Reset      |  |  |  |

| 15:2 | _                                                      | Reserved                              | R      | 0x00000000 |  |  |  |

| 1    | DSP_SWITCH                                             | 0: No DSP TIPB bridge access required | RW     | 0          |  |  |  |

|      |                                                        | 1: DSP TIPB bridge access required    |        |            |  |  |  |

| 0    | MPU_SWITCH                                             | 0: No MPU TIPB bridge access required | R      | 1          |  |  |  |

|      |                                                        | 1: MPU TIPB bridge access required    |        |            |  |  |  |

This register is accessible only through the DSP shared TIPB bridge.

#### 2.7.1 Reset Methodology

An MPU or a DSP initiator reset is always used internally by the static switch.

A reset on the static switch configuration register resets the DSP\_SWITCH bit and sets the MPU\_SWITCH bit, which turns the static switch in the MPU position.

# 2.8 TIPB1-VIA/VIA-TIPB Wrapper

The synchronous VIA protocol requires a free-running clock and synchronous signals relative to this clock.

In addition to the TIPB bus signals, DMA requests need to be adapted.

Two successive DMA requests must be separated by at least two system DMA clock cycles.

#### 2.8.1 Reset Methodology

The internal state machine of the wrapper is reset by the MPU peripheral reset.

For the SoSSI peripheral, two resets must be provided to the peripheral:

☐ L4\_VIA\_Reset: synchronous with the CK\_DPLL1OUT

☐ L4\_DMA\_Reset: synchronous with the DMA\_LCDFREE\_CLK

In both cases, the reset source is the MPU peripheral reset.

For the CCP peripheral, one reset is generated to the peripheral; L4\_VIA\_RESET is synchronous with the ARMPER\_CLK.

# 2.9 TIPB-OCP/OCP-TIPB Wrapper

The synchronous OCP protocol requires a free-running clock and synchronous signals realtive to this clock.

The free-running clock is ARMPER\_CLK.

# 2.9.1 Reset Methodology

The NO\_RESET signal comes from the wrapper to the connected peripheral.

#### 2.9.2 DSP TIPB to OCP

This wrapper is sensitive to either DSP watchdog reset or DSP peripheral reset in order to clear the interface state machine.

#### 2.9.3 MPU TIPB to OCP

This wrapper is sensitive to MPU watchdog reset or MPU peripheral reset in order to clear the internal state machine.

# 2.10 TIPB-OCP/OCP-TIPB Wrapper for USBOTG

The synchronous OCP protocol requires a free-running clock and synchronous signals relative to this clock.

The free-running clock is ARMPER\_CLK.

This wrapper is used for transmissions with USB client, USB host, and OTG.

Depending on the access, an increment is applied to the address:

- ☐ If USB host is accessed, the address remains unchanged.

- ☐ If USB client is accessed, the address is incremented by 0x200h.

- ☐ If OTG is accessed, the address is incremented by 0x300h.

## 2.10.1 Reset Methodology

This wrapper is sensitive to MPU peripheral reset in order to reset the internal state machine.

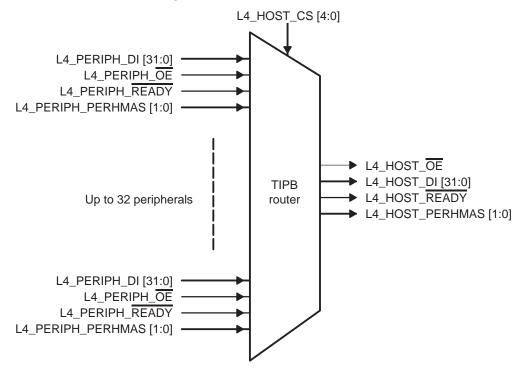

## 2.11 TIPB Router

Figure 7. TIPB Router Block Diagram

The TIPB router is a simple multiplexer that returns information coming from peripherals to the host (DSP or MPU). The information concerns a current READ or WRITE access on a peripheral. This TIPB router supports up to 32 peripheral connections.

# 2.12 Peripheral Instantiation

Table 9. Private Peripherals Instantiation

| OMAP 5912<br>Peripheral          | Interface      | I                      | Instanti | ation |        |     | TIPB Router |

|----------------------------------|----------------|------------------------|----------|-------|--------|-----|-------------|

|                                  |                | Address Bus            |          | Acc   | cess S | ize | _           |

|                                  |                | Alignment <sup>†</sup> | Data     | 8b    | 16b    | 32b |             |

| 3 DSP level 2 interrupt handler  | TIPB           | Byte                   | 16       | -     | R      | -   | Private DSP |

| ULPD (clock and reset)           | TIPB           | Byte                   | 16       | -     | R      | _   | Private MPU |

| OMAP5912 configuration           | TIPB           | Byte                   | 32       | -     | -      | R   | Private MPU |

| Secure watchdog                  | Wrapper<br>OCP | Byte                   | 32       | -     | R      | R   | Private MPU |

| 32-kHz<br>watchdog               | Wrapper<br>OCP | Byte                   | 32       | -     | R      | R   | Private MPU |

| 2 MPU level 2 interrupt handlers | TIPB           | Byte                   | 32       | -     | -      | R   | Private MPU |

| SHA_1 accelerator                | Wrapper<br>OCP | Byte                   | 32       | -     | -      | R   | Private MPU |

| RNG random generator             | Wrapper<br>OCP | Byte                   | 32       | -     | -      | R   | Private MPU |

| DES/3DES                         | Wrapper<br>OCP | Byte                   | 32       | -     | -      | R   | Private MPU |

| System DMA<br>handler            | Wrapper<br>OCP | Byte                   | 32       | -     | -      | R   | Private MPU |

<sup>†</sup> Address bus alignment:

Byte: The least significant bit of the peripheral address bus corresponds to a byte address in the peripheral.

16-bit: The least significant bit of the peripheral address bus corresponds to a 16-bit address in the peripheral.

32-bit: The least significant bit of the peripheral address bus corresponds to a 32-bit address in the peripheral.

Table 10. MPU Peripherals Connected to the MPU Shared TIPB Bridge Instantiation

| OMAP 5912<br>Peripheral | Interface      | Instantiation                         |             |    |     |                | TIPB Router |

|-------------------------|----------------|---------------------------------------|-------------|----|-----|----------------|-------------|

| remplicial              | menace         | Address Bus                           | Access Size |    |     | - III B Routei |             |

|                         |                | Address Bus<br>Alignment <sup>†</sup> | Data        | 8b | 16b | 32b            |             |

| HDQ/1-Wire              | TIPB           | Byte                                  | 8           | R  | -   | _              | Shared MPU  |

| $\mu WIRE$              | TIPB           | Byte                                  | 16          | _  | R   | _              | Shared MPU  |

| MMCSD/IO1               | Wrapper<br>OCP | 16b                                   | 16          | -  | R   | -              | Shared MPU  |

| MPUIO                   | TIPB           | 16b                                   | 16          | _  | R   | _              | Shared MPU  |

| 2 x LPG                 | TIPB           | Byte                                  | 8           | R  | _   | -              | Shared MPU  |

| SoSSI                   | Wrapper<br>VIA | 32b                                   | 32          | _  | -   | R              | Shared MPU  |

| RTC                     | TIPB           | Byte                                  | 8           | R  | _   | -              | Shared MPU  |

| Memory Stick            | TIPB           | 32b                                   | 32          | -  | _   | R              | Shared MPU  |

| PWL                     | TIPB           | Byte                                  | 8           | R  | _   | _              | Shared MPU  |

| PWT                     | TIPB           | Byte                                  | 8           | R  | _   | _              | Shared MPU  |

| FAC                     | TIPB           | Byte                                  | 16          | _  | R   | -              | Shared MPU  |

| OS timer                | TIPB           | Byte                                  | 32          | _  | R   | R              | Shared MPU  |

| USBOTG                  | Wrapper<br>OCP | Byte                                  | 16          | -  | R   | -              | Shared MPU  |

<sup>†</sup> Address bus alignment:

Byte: The least significant bit of the peripheral address bus corresponds to a byte address in the peripheral. 16-bit: The least significant bit of the peripheral address bus corresponds to a 16-bit address in the peripheral. 32-bit: The least significant bit of the peripheral address bus corresponds to a 32-bit address in the peripheral.

Table 11. DSP Peripherals Connected to the DSP Shared TIPB Bridge Instantiation

| OMAP 5912<br>Peripheral | Interface   |             | Insta | TIPB Router |     |     |            |

|-------------------------|-------------|-------------|-------|-------------|-----|-----|------------|

|                         |             | Address Bus |       | Access Size |     |     |            |

|                         |             | alignment   | Data  | 8b          | 16b | 32b |            |

| 2 x MCSI                | TIPB        | Byte        | 16    | _           | R   | -   | Shared DSP |

| 2 x McBSP               | Wrapper OCP | Byte        | 16    | _           | R   | _   | Shared DSP |

Table 12. DSP and MPU Shared Peripherals Instantiation

| OMAP 5912<br>Peripheral             | Interface   |             | TIPB Rou | ter |         |     |         |        |

|-------------------------------------|-------------|-------------|----------|-----|---------|-----|---------|--------|

|                                     |             | Address Bus |          | Acc | ess Siz | е   |         |        |

|                                     |             | Alignment   | Data     | 8b  | 16b     | 32b | MPU     | DSP    |

| MMCSD/IO2                           | Static OCP  | Byte        | 16       | -   | R       | -   | Shared  | Shared |

| STI (reserved)                      | Dynamic OCP | Byte        | 32       | -   | R       | R   | Private | Shared |

| 32-kHz<br>synchronizatio<br>n timer | Dynamic OCP | Byte        | 32       | -   | R       | R   | Shared  | Shared |

| 4 x GPIO                            | Dynamic OCP | Byte        | 16       | _   | R       | R   | Shared  | Shared |

| GPIO pin control                    | Dynamic OCP | Byte        | 16       | -   | R       | R   | Shared  | Shared |

| 3 x UART                            | Static TIPB | Byte        | 8        | R   | _       | _   | Shared  | Shared |

| McBSP                               | Static OCP  | Byte        | 16       | _   | R       | _   | Shared  | Shared |

| I <sup>2</sup> C                    | Static OCP  | Byte        | 16       | R   | R       | -   | Shared  | Shared |

| SPI                                 | Static OCP  | Byte        | 32       | _   | R       | R   | Shared  | Shared |

| 8 x GP timers                       | Static OCP  | Byte        | 32       | _   | R       | R   | Shared  | Shared |

| NAND flash control                  | Static OCP  | Byte        | 32       | R   | R       | R   | Shared  | Shared |

| Static switch configuration         | TIPB        | Byte        | 32       | R   | R       | R   | Shared  | Shared |

# 3 OCP Interconnect

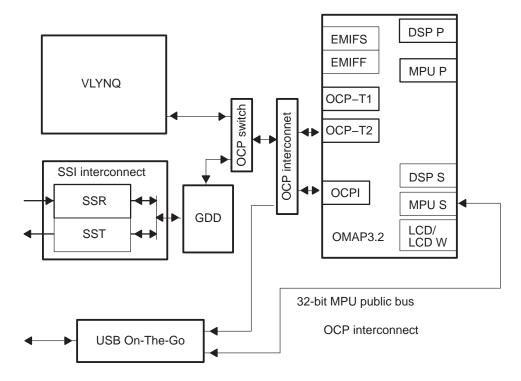

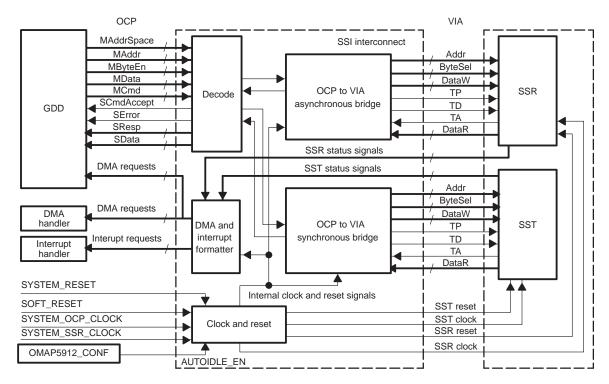

The OCP, SSI interconnects, and static switches manage data transfers between OMAP3.2 and the SSI or VLYNQ and USB peripherals.

The SSI is a full-duplex interface, using a synchronous serial interconnect protocol (SSI). This protocol consists of a transmitter called (SST) in SSI, which is in charge of transmitting information, and a receiver called (SSR), which is in charge of receiving information

SSI DMA transfers are handled by the generic distributed DMA (GDD).

Because the SSI uses a proprietary bus interface (versatile interconnection architecture (VIA)), bridges are implemented in the SSI interconnect to perform data transfers between the SSI VIA bus and the OMAP3.2 OCP bus.

VLYNQ is also a full duplex interface, using a VBUS 1.0 protocol. A wrapper around the VLYNQ core performs the protocol conversion VBUS to OCP and OCP to VBUS.

In addition, data transfer between the USB host and OMAP3.2 are done through the OCP interconnect and the OCPI port.

The GDD has priority over the USB.

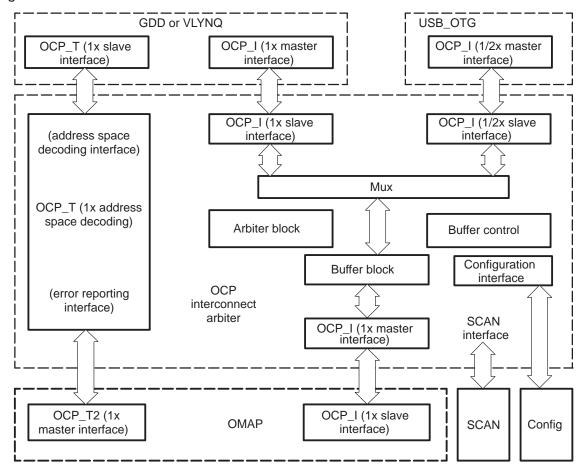

Figure 8. OCP and SSI Interconnects

#### 3.1 OCP Introduction

The OCP arbiter must interconnect two OCP master devices (peripherals), such as GDD or VLYNQ and USB\_OTG peripheral, to a single OMAP OCP\_I slave port. GDD or VLYNQ OCP\_I port has priority over USB\_OTG OCP\_I port.

38 Peripheral Interconnects SPRU758A

All interfaces are 32-bit data width and support burst and nonburst operations.

Because the OMAP OCP\_I port does not support split bursts, the buffer block translates split burst (master can insert wait states between valid commands during burst) into a simple burst action (the master cannot insert wait states between valid commands during burst).

The OCP arbiter interconnect also provides address space decoding and standard OCP error signaling if the address is out of GDD/SSI or VLYNQ address space.

Figure 9. OCP Interconnect

# 3.2 Module Features

|     | Th          | e OCP interconnect arbiter provides the following features:                                                                                                     |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |             | One OCP master port 32-bit width, 1x balanced clock, 4x32 (FOUR-TWO-LAST incremented burst only) nonsplit burst and nonburst accesses (OMAP OCP_I interconnect) |

|     |             | One OCP slave port 32-bit width, 1x balanced clock, 4x32 split burst and nonburst accesses (GDD OCP_I interconnect)                                             |

|     |             | One OCP slave port 32-bit width, 1/2x balanced clock, 4x32 split burst and nonburst accesses (USB_OTG OCP_I interconnect)                                       |

|     |             | Translate split burst to nonsplit burst accesses for OMAP OCP_I slave interface (buffer for burst transaction)                                                  |

|     |             | Offer high priority to OCP_I 1x master (GDD OCP_I has the priority)                                                                                             |

|     |             | Address space decoding for GDD/SSI and standard error report to the OCP_T2 OMAP port when address is out of GDD/SSI address space.                              |

| 3.3 | 1x OCP Slav | re Port                                                                                                                                                         |

|     | Th          | e OCP interconnect arbiter 1x OCP slave port has the following features:                                                                                        |

|     |             | OCP interface (slave)                                                                                                                                           |

|     |             | Synchronous                                                                                                                                                     |

|     |             | Balanced 100-MHz clock                                                                                                                                          |

|     |             | 32-bit data width only                                                                                                                                          |

|     |             | Support 4x32 burst and nonburst accesses                                                                                                                        |

|     | Th          | is port is directly connected to the GDD memory port.                                                                                                           |

| 3.4 | 1/2x OCP SI | ave Port                                                                                                                                                        |

|     | Th          | e OCP interconnect arbiter 1/2x OCP slave port has the following features:                                                                                      |

|     | _           | OCP interface (slave) Synchronous Balanced 100-MHz clock using a 50-MHz phase indication 32-bit data width only Support 4x32 burst and nonburst accesses        |

|     | Th          | is port is directly connected to the USB OTG OCP master interface.                                                                                              |

40 Peripheral Interconnects SPRU758A

#### 3.5 1x OCP Master Port

The OCP interconnect arbiter 1x OCP master port has the following features:

OCP interface (master)

Synchronous

Balanced 100-MHz clock

32-bit data width only

Support 4x32 burst (4–2–2–LAST only) and non-burst accesses

Non-split burst only

This port is directly connected to the OMAP OCP\_I slave interface.

# 3.6 Address Space

The address space for the GDD/SSI and VLYNQ is shown in Table 13 (and is fixed; no configuration registers are needed).

Table 13. GDD/SSI Address Space

| Block Name           | Start Address | End Address | Size      |

|----------------------|---------------|-------------|-----------|

| SSI mapping          | 0x3000 0000   | 0x3000 0FFF | 4K bytes  |

| GDD mapping          | 0x3000 1000   | 0x3000 1FFF | 4K bytes  |

| VLYNQ conf mapping   | 0x3000 2000   | 0x3000 21FF | 512 bytes |

| VLYNQ window mapping | 0x3100 0000   | 0x34FF FFFF | 64 Mbytes |

#### 3.7 Arbiter Block

The arbiter block controls the priority between GDD or VLYNQ and USB conflicting requests to the OMAP OCP-I port. The arbitration scheme is simple. If both 1x OCP and 1/2x OCP ports request at the same time, priority is given to the 1x port. In other words, the GDD or VLYNQ always has the highest priority.

#### 3.8 Buffer Block