## Test Report: PMP22165 Power for Xilinx Versal Adaptive Compute Acceleration Platform (ACAP) Reference Design

## **TEXAS INSTRUMENTS**

### Description

PMP22165 reference design addresses Xilinx Versal Adaptive Compute Acceleration Platform (ACAP) platform requirements and consists of a Power Management Integrated Circuit (PMIC) for system-rails, plus a multiphase controller and power stages to support higher current processor loads. On board dynamic loads on the critical outputs allow testing to Xilinx's demanding power requirements. PMP22165 along with the TPS53681 EVM is a tested solution offering performance with cost-optimized components to meet processor requirements for Versal's most common use cases 1 & 3.

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

#### 1 **Test Prerequisites**

#### Voltage and Current Requirements 1.1

Table 1. **Voltage and Current Requirements**

| PARAMETER                                                 | SPECIFICATIONS                   |

|-----------------------------------------------------------|----------------------------------|

| Input Voltage                                             | 7-14 VDC                         |

| Output Voltage Range                                      | Various outputs 0.8V thru 3.3V   |

| Max Load Current                                          | 165A on main, up to 4.8A on 1.2V |

| Max Output Power (electrical peak / for thermal purposes) | 150W electrical peak             |

#### 1.2 **Required Equipment**

- Lab 12 V 20 A source if testing with main 0.8V 165A, otherwise 12V 3A source OK

- Electronic loads rated to carry maximum static load

- Signal generator to drive on-board dynamic load. Example Tektronix AFG3102

- Thermal camera

- Oscilloscope and voltage / current meters or current shunts

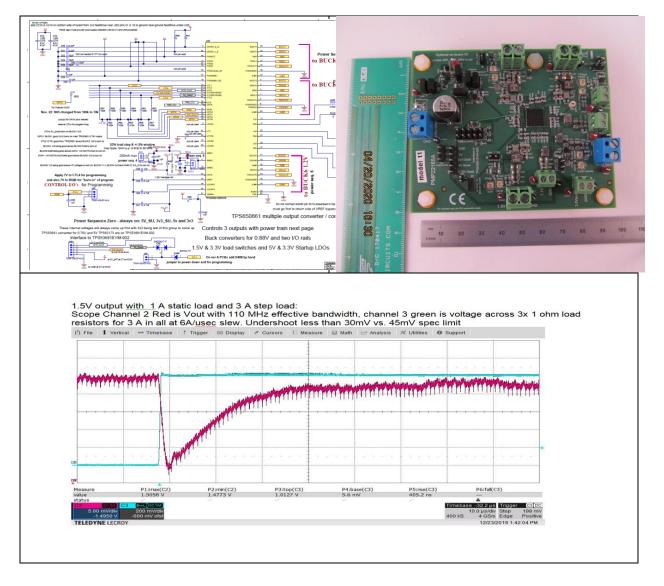

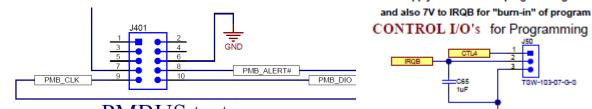

#### 1.3 Programming the TPS650861

The TPS650861 needs to be programmed for this application thru the PMB\_CLK (J401-9) and PMB\_DIO (J401-10) pins with J401-6 as ground. Also, during programming CTL4 (J50-1) needs to be pulled to 7V. Also, when "burning in" the program, IRQB (J50-2) also needs to be pulled to 7V. Apply 7V to CTL4 for programming

## PMBUS test conn

See TPS65086100 Non-Volatile Memory Programming Guide for details. The following script was used on the PMP22165 boards.

var custom program 199 = [

{group: 'PART\_NUMBER', value: 0x199}, {register: 'DEVICEID2', value: 0x01}, {register: 'BUCK1CTRL', value: 0xE8}, {register: 'BUCK2CTRL', value: 0xDC}, {register: 'BUCK3DECAY', value: 0x38}, {register: 'BUCK3VID', value: 0x38}, {register: 'BUCK3SLPCTRL', value: 0x38}, {register: 'BUCK4CTRL', value: 0x0F}, {register: 'BUCK5CTRL', value: 0x0F}, {register: 'BUCK6CTRL', value: 0x0F}, {register: 'LDOA2CTRL', value: 0x0C}, {register: 'LDOA3CTRL', value: 0x0C}, {register: 'DISCHCTRL1', value: 0x55}, {register: 'DISCHCTRL2', value: 0x55}, {register: 'DISCHCTRL3', value: 0x15},

{register: 'PG\_DELAY1', value: 0x06}, {register: 'BUCK1SLPCTRL', value: 0xE8}, {register: 'BUCK2SLPCTRL', value: 0xDC}, {register: 'BUCK4VID', value: 0xA8}, {register: 'BUCK4SLPVID', value: 0xA8}, {register: 'BUCK5VID', value: 0x26}, {register: 'BUCK5SLPVID', value: 0x26}, {register: 'BUCK6VID', value: 0xA0}, {register: 'BUCK6SLPVID', value: 0xA0}, {register: 'LDOA2VID', value: 0xFF}, {register: 'LDOA3VID', value: 0xAA}, {register: 'BUCK123CTRL', value: 0x3F}, {register: 'PG DELAY2', value: 0x00}, {register: 'SWVTT\_DIS', value: 0x60}, {register: 'I2C\_RAIL\_EN1', value: 0x80}, {register: 'I2C RAIL EN2', value: 0x0D}, {register: 'PWR\_FAULT\_MASK1', value: 0x80}, {register: 'PWR FAULT MASK2', value: 0x31}, {register: 'GPO1PG\_CTRL1', value: 0xFE}, {register: 'GPO1PG\_CTRL2', value: 0xFF}, {register: 'GPO4PG\_CTRL1', value: 0xFF}, {register: 'GPO4PG CTRL2', value: 0xFF}, {register: 'GPO2PG\_CTRL1', value: 0xFF}, {register: 'GPO2PG CTRL2', value: 0xFF}, {register: 'GPO3PG\_CTRL1', value: 0x80}, {register: 'GPO3PG\_CTRL2', value: 0x7D}, {register: 'MISCSYSPG', value: 0x7F}, {register: 'VTT DISCH CTRL', value: 0x5F}, {register: 'LDOA1\_SWB2\_CTRL', value: 0x54}, {register: 'BUCK1 CTRL EN1', value: 0xFF}, {register: 'BUCK1\_CTRL\_EN2', value: 0xFB}, {register: 'BUCK1\_CTRL\_EN3', value: 0x10}, {register: 'BUCK2 CTRL EN1', value: 0xFE}, {register: 'BUCK2 CTRL EN2', value: 0xCB}, {register: 'BUCK2\_CTRL\_EN3', value: 0x10}, {register: 'BUCK3 CTRL EN1', value: 0xC4}, {register: 'BUCK3\_CTRL\_EN2', value: 0x6B}, {register: 'BUCK3 CTRL EN3', value: 0x09}, {register: 'BUCK4 CTRL EN1', value: 0xC4}, {register: 'BUCK4\_CTRL\_EN2', value: 0xEB}, {register: 'BUCK4\_CTRL\_EN3', value: 0x10}, {register: 'BUCK5\_CTRL\_EN1', value: 0xFC}, {register: 'BUCK5\_CTRL\_EN2', value: 0x6B}, {register: 'BUCK5\_CTRL\_EN3', value: 0x08}, {register: 'BUCK6 CTRL EN1', value: 0xCC}, {register: 'BUCK6 CTRL EN2', value: 0xCB}, {register: 'BUCK6 CTRL EN3', value: 0x01}, {register: 'SWA1\_CTRL\_EN1', value: 0xEC}, {register: 'SWA1\_CTRL\_EN2', value: 0x0B}, {register: 'SWA1 CTRL EN3', value: 0x01}, {register: 'LDOA2\_CTRL\_EN1', value: 0xFF}, {register: 'LDOA2\_CTRL\_EN2', value: 0x5F}, {register: 'LDOA2\_CTRL\_EN3', value: 0x00}, {register: 'LDOA3\_CTRL\_EN1', value: 0xFF}, {register: 'LDOA3\_CTRL\_EN2', value: 0x1F}, {register: 'LDOA3\_CTRL\_EN3', value: 0x80}, {register: 'SWB1 CTRL EN1', value: 0x8C},

{register: 'SWB1\_CTRL\_EN2', value: 0xEB}, {register: 'SWB1 CTRL EN3', value: 0x08}, {register: 'SWB2 LDOA1 CTRL EN1', value: 0xFF}, {register: 'SWB2\_LDOA1\_CTRL\_EN2', value: 0x7F}, {register: 'SWB2 LDOA1 CTRL EN3', value: 0x00}, {register: 'OTP\_RSVD\_38\_28', value: 0x18}, {register: 'SLP\_PIN', value: 0xFF}, {register: 'OUTPUT\_MODE', value: 0x27}, {register: 'OTP\_RSVD\_38\_2C', value: 0xA1}, {register: 'OTP\_RSVD\_38\_2E', value: 0xAA}, {register: 'OTP\_RSVD\_38\_32', value: 0x61}, {register: 'OTP RSVD 38 34', value: 0xAA}, {register: 'OTP\_RSVD\_38\_38', value: 0x61}, {register: 'OTP\_RSVD\_38\_3A', value: 0xAA}, {register: 'OTP RSVD 38 44', value: 0x05}, {register: 'OTP RSVD 38 48', value: 0x25}, {register: 'OTP\_RSVD\_38\_4C', value: 0x25}, {register: 'OTP RSVD 38 53', value: 0xAE}, {register: 'I2CADDRESS', value: 0x00}];

### 1.4 Considerations

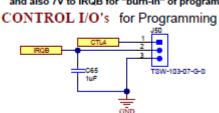

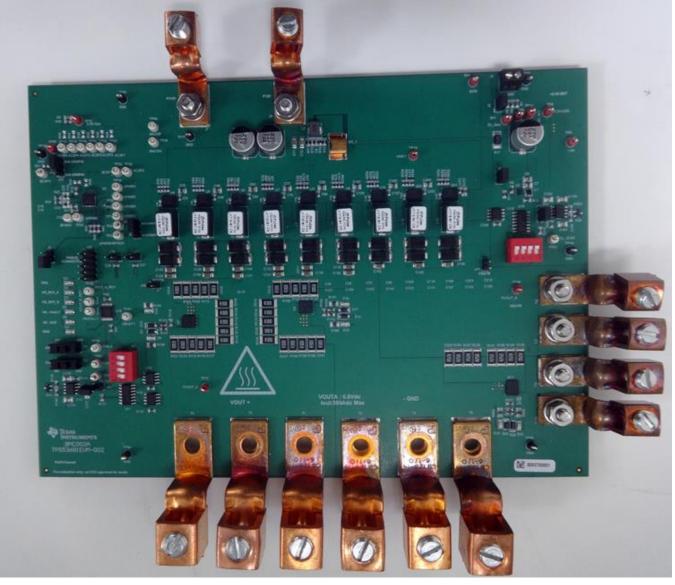

Tests here below focus on the meeting the demanding Xilinx Versal power requirements, especially in terms of output ripple and transient load response, and on the customized PMP22165 board designed specifically for the Xilinx Versal platform to provide all the outputs except for the main high current (165A max) VCCINT rail. For more details of operation of that rail, refer to the <u>TPS53681 EVM user's guide</u>. The main 6 phase rail was used with no hardware changes, only 2 GUI settings as described below for Vout and dynamic response were changed. Switching frequency remains the same at 500 kHz. Hence, the detailed efficiency data taken for 900mV can be extrapolated to 800mV by subtracting 1% from the values shown.

With the conservative assumption that losses at 800mV output are the same as losses at 900mV with switching frequency the same 500 kHz, the 93% peak efficiency at 900mV becomes 92% at 800mV.This is slightly conservative as transformer AC / core losses are slightly less at 800mV than 900mV due to lower peak to peak flux. From the EVM User's guide:

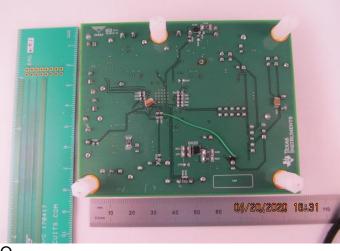

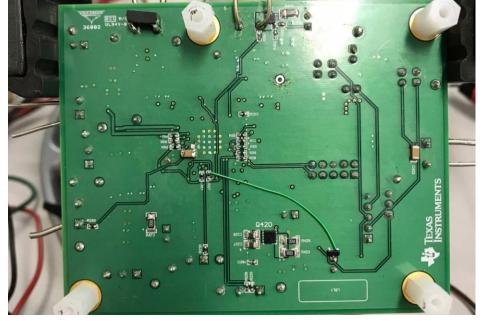

### Section 1.5: PMP22165 Top & Bottom Images 3.75 inches by 3 inches Top image

### Bottom image

Q

### Section 1.5 TPS53681 EVM image

### Testing and Results (Tests done by Josh Mandelcorn & Mitchell Spears) Section 2 overall will be output ripple and dynamics

### Section 2.1 Main 800mV channel on the TPS53681 EVM: ripple & dynamics

Only changes from default GUI settings are Vout from 0.9V to 0.8V and AC\_LL from 0.5mOhm to 0.375mOhm. This AC\_LL setting of 0.375 is the midpoint between 0.5 conservative default setting and 0.25mOhms used in the TPS53681 EVM for dynamic response and Bode plot. Same 500 kHz / phase operation maintained.

| Compensation               | Non-Linear Control                               |

|----------------------------|--------------------------------------------------|

| AC_GAIN: 2.00 🗸 *x [7:6]   | USR2: 300 🗸 mV                                   |

| AC_LL: 0.3750 v mΩ [5:0]   | USR1: 240 🗸 mV                                   |

| INT_Time: 01 v [11:8]      | PH1_USR: Enabling 4-phase operation in USR event |

| INTGAIN: 2.00 v *x [13:12] |                                                  |

| Ramp                       | Timing Control                                   |

| RAMP: 200 v mVp-p          | BLANK_TIME_RISING: 74 🗸 ns                       |

|                            | MINTOFF: 90 V ns                                 |

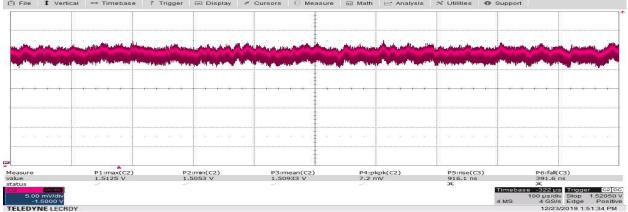

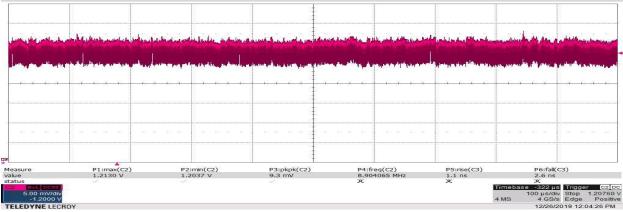

### Output ripple with main channel loaded at 138A static load: 7.7mV peak to peak vs. 10mV max spec

📋 File 🚺 Vertical 😁 Timebase 👔 Trigger 🖃 Display 🥒 Cursors 🗉 Measure 📓 Math 🗠 Analysis 💥 Utilities 🛛 Support

|                      |             |         |          |            | -        |        |     |                                                 |                 |

|----------------------|-------------|---------|----------|------------|----------|--------|-----|-------------------------------------------------|-----------------|

| 16 36 36 36 <b>1</b> |             | 5 5 5 5 |          |            | la sa si |        |     |                                                 |                 |

|                      |             |         |          |            |          |        |     |                                                 |                 |

|                      |             |         |          |            |          |        |     |                                                 |                 |

|                      |             |         |          |            |          |        |     |                                                 |                 |

|                      | x           |         |          |            |          |        | (   |                                                 |                 |

| leasure              | P1:pkpk(C2) |         | mean(C2) | P3:max(C2) |          | in(C2) | P5: | P6:                                             | -               |

| alue<br>tatus<br>2   | 7.7 mV      | 798     | 8.71 mV  | 803.0 mV   | 795.     | 3 mV   |     | Timebase -62.0 µ<br>20.0 µs/d<br>100 kS 500 MS/ | iv Stop 784.8   |

| TELEDYNE LECROY      |             |         |          |            |          |        |     | 4/20/                                           | 2020 12:18:21 P |

### Section 2.1 Main 800mV channel on the TPS53681 EVM continued:

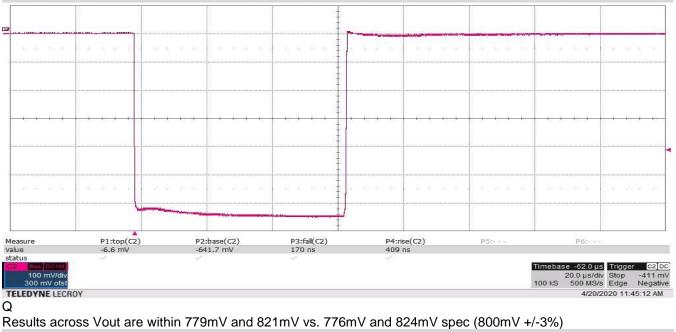

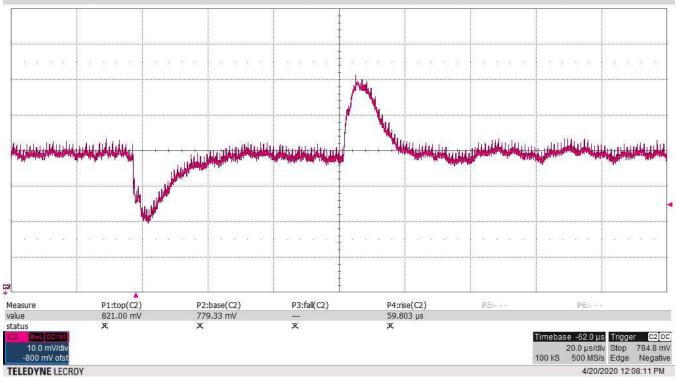

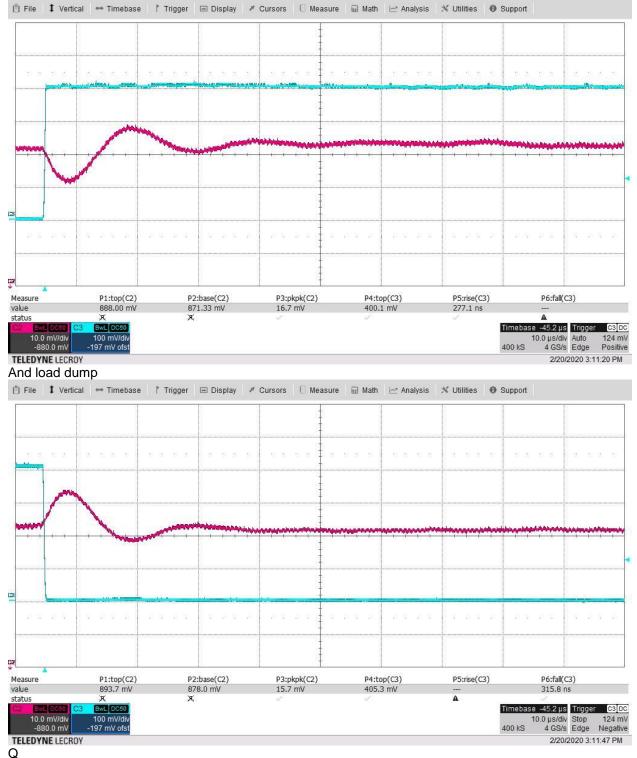

Dynamic load response:

First shown is test pulse across 1 of 45 300mOhm dynamic load resistors

640/300 is 2.13A times 45 is 96A or 60% of 160A

Based upon fall / rise times (10% to 90%) step di/dt is 450A/usec and dump -190A per usec

📋 File 🚺 Vertical 🖶 Timebase | Trigger 🖃 Display | 🖉 Cursors 🗌 Measure 📾 Math 🗠 Analysis 🗡 Utilities 🚳 Support

📋 File 🚺 Vertical 😁 Timebase 🍸 Trigger 🖃 Display 🥒 Cursors 📋 Measure 📓 Math 🗠 Analysis 💥 Utilities 😝 Support

### Now to the channels on the PMP22165 board itself

### Section 2.2 1.5V 4.2A channel ripple & dynamics

1.5V 4.2A full load ripple: Xilinx requires at least 80 MHz bandwidth for this channel's measurements

Scope Channel 2 Red is Vout with 110 MHz effective bandwidth by probe R\*C of 1.4E-9 scope BW full model t2

Spec is 10mV p-p max, measured 7.2mV p-p over 1000usec

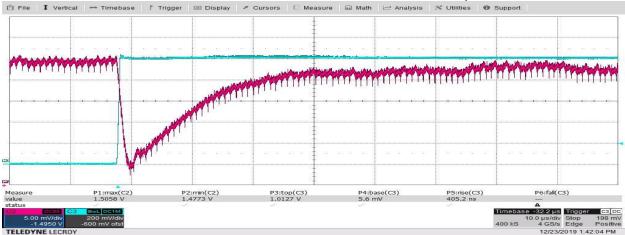

### 1.5V output with 1 A static load and 3 A step load:

Scope Channel 2 Red is Vout with 110 MHz effective bandwidth, channel 3 green is voltage across 3x 1 ohm load resistors for 3 A in all at 6A/usec slew. Undershoot less than 30mV vs. 45mV spec limit

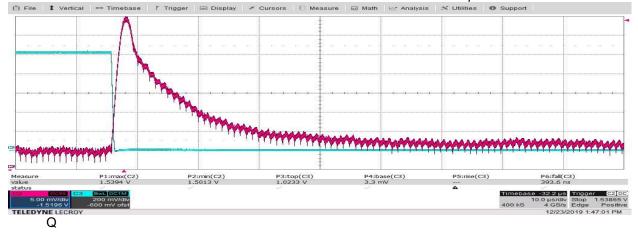

#### & dump.

Scope Channel 2 Red is Vout with 110 MHz effective bandwidth, channel 3 green is voltage across 3x 1 ohm load resistors for 3 A in all at -6A/usec slew. Overshoot less than 40mV vs. 45mV spec limit

|              |                      |                      | 001          | na ma               |                                          | ±3%                        | 80MHz BV                                              | v <del>+</del> /-3/0                | 25%                      | 10mV              | / pk-pk ripple       | at FPGA              |

|--------------|----------------------|----------------------|--------------|---------------------|------------------------------------------|----------------------------|-------------------------------------------------------|-------------------------------------|--------------------------|-------------------|----------------------|----------------------|

| 10           | M                    | GTAVAUX              |              | 1                   | .5∨                                      | 1070                       | 0.1 - 0.2A                                            |                                     | 2070                     | TOTIL             | рк-рк пррк           |                      |

| uFs<br>ppe(  | ize 06<br>Chann      | 03 bypas<br>el 2 Red | s ca<br>is V | ap neai<br>/out wit | test poi<br>h 110 M                      | nt. (C472 o<br>Hz effectiv | o 200mA m<br>on PCB) Fu<br>e bandwidt<br>Measure 🖬 Ma | ill load r<br>h by pro              | ripple less<br>obe R*C ( | s than<br>of 1.4E | 5mV p-p<br>E-9 scope |                      |

|              |                      |                      |              |                     |                                          |                            | Į                                                     |                                     |                          |                   |                      |                      |

| V            | taji Aliya           | New Here Here        |              |                     |                                          | 8 8 8 8                    |                                                       |                                     |                          | 8 8 8             |                      | A <sub>w</sub> wywyw |

|              |                      |                      |              | -                   |                                          |                            |                                                       |                                     |                          |                   |                      |                      |

| - 10-1       | <del>- 1 - 1 -</del> |                      | <b>**</b> *  |                     |                                          |                            |                                                       | 17 (* 1911)<br>17 (* 1911)<br>1 - 1 |                          |                   | <mark>//</mark><br>  |                      |

|              |                      |                      |              |                     |                                          |                            |                                                       |                                     |                          |                   | 1                    |                      |

|              |                      |                      |              |                     | - 10 10 10 10 10 10 10 10 10 10 10 10 10 |                            | ‡<br>                                                 |                                     |                          | 8 82 28           |                      |                      |

| 3            |                      |                      |              |                     |                                          |                            | Ī                                                     |                                     |                          |                   |                      |                      |

| e<br>Measure | 8                    | P1:pkpk(             | ~2)          | 10                  | 2:min(C2)                                | P3:max(                    | (2) 0                                                 | 4:fall(C3)                          | D5·ri                    | se(C3)            | P6:top               |                      |

| alue         |                      | 14.2 mV              |              |                     | .4605 V                                  | 1.4747                     |                                                       | .98 µs                              | 300                      |                   | 502.3                |                      |

| status       |                      | 1                    |              |                     |                                          | 1                          |                                                       | 6 - 20 C                            | 1                        |                   | 1                    |                      |

TELEDYNE LECROY

4/20/2020 2:50:06 PM

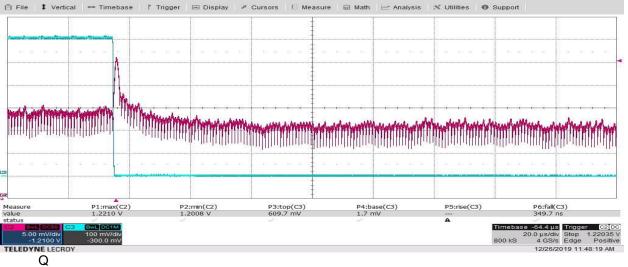

### Section 2.4 1.2V 4.8A channel ripple & dynamics

1.2V 4.8A full load ripple TP460 removed and trace to it cut model t1

Scope Channel 2 Red is Vout with 110 MHz effective bandwidth by probe R\*C of 1.4E-9 scope BW 200MHz

Spec is 10mV p-p max, measured 9.3mV p-p over 1000usec 1.2V output with 3 A static load and 1.2 A step load:

Scope Channel 2 Red is Vout with 110 MHz effective bandwidth, channel 3 green is voltage across 2x 1 ohm load resistors for 1.2 A in all at >2.4A/usec slew. Undershoot max about 5mV

|                               |                                  | <b></b> | متعنية من عدادي مديري |                    |                        |       |               |                         |                                                       | and the second state of the second states |

|-------------------------------|----------------------------------|---------|-----------------------|--------------------|------------------------|-------|---------------|-------------------------|-------------------------------------------------------|-------------------------------------------|

| and and and the second second | Matter and                       |         |                       |                    |                        |       |               |                         |                                                       |                                           |

|                               |                                  | YM      |                       |                    |                        |       |               |                         |                                                       |                                           |

|                               |                                  |         |                       |                    |                        |       | an na an na   |                         |                                                       |                                           |

| asure                         | P1:max<br>1.2097                 |         | 1.1                   | :min(C2)<br>.968 V | P3:top(C3)<br>600.5 mV | 1.7 r | ase(C3)<br>nV | P5:rise(C3)<br>344.9 ns | P6:fall(                                              | 53)                                       |

| 5.00 mV/div<br>-1.2000 V      | BwL[DC1r<br>100 mV/c<br>-300.0 m | liv     |                       |                    |                        |       |               |                         | A<br>Timebase -64.4 µs<br>20.0 µs/dh<br>800 kS 4 GS/s |                                           |

& dump.

Scope Channel 2 Red is Vout with 110 MHz effective bandwidth, channel 3 green is voltage across 2x 1 ohm load resistors for 1.2 A in all at -2.4A/usec slew.

Overshoot less than 15mV vs. +/-36mV allowed band

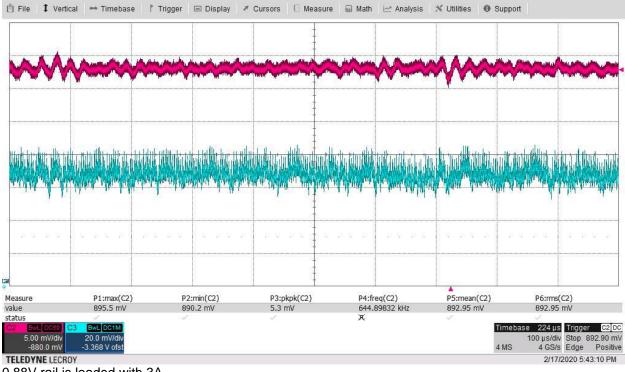

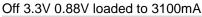

### Section 2.5 0.88V 3.1A channel ripple & dynamics

0.88V testing for ripple / dynamics Model T3:

Made the following modifications to the board:

Added <u>47uF capacitor under U50 near PVIN5 Pin 21 with 3x 47uF at the output of the 3V3.</u>

Output ripple on the 0.88V ~100MHz measurement spec 10mV p-p max @ 80 MHz BW Scope Channel 2 Red is Vout with 110 MHz effective bandwidth by probe R\*C of 1.4E-9 scope BW 200MHz

0.88V rail is loaded with 3A.

TEXAS INSTRUMENTS

www.ti.com

### Section 2.5 0.88V 3.1A channel ripple & dynamics (continued)

0.88V transient response 1.5 static load 0.8A dynamic load (400mV across 2x 1.0 ohm for 800mA) Step load response: +/-3% band allowed 856mV to 904mV range

Scope Channel 2 Red is Vout with 110 MHz effective bandwidth by probe R\*C of 1.4E-9 scope BW 200MHz

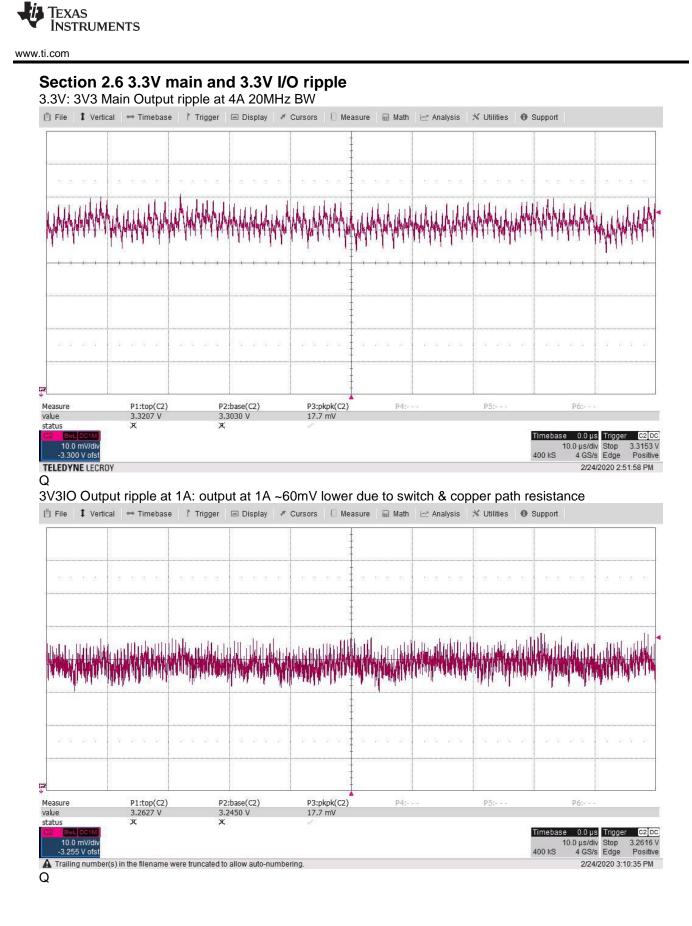

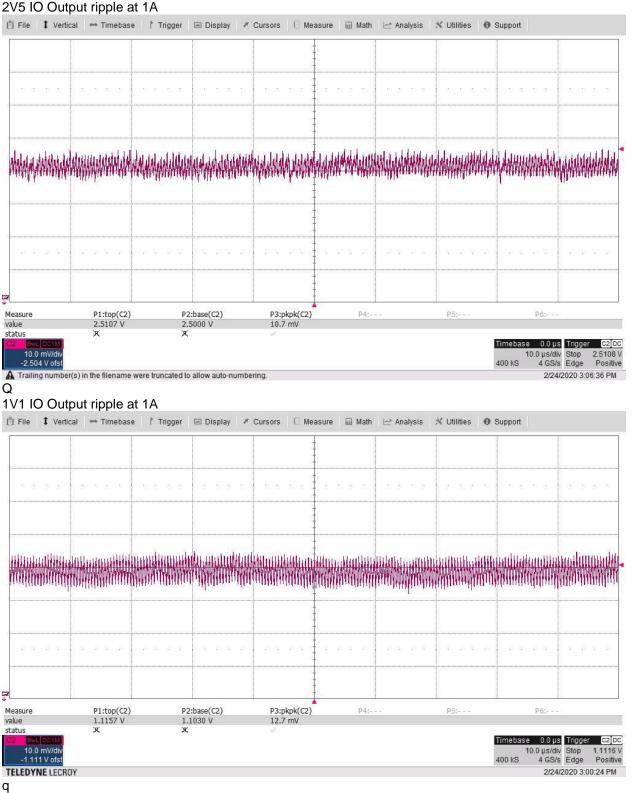

### Section 2.7 2.5V I/O and 1.1V I/O ripple:

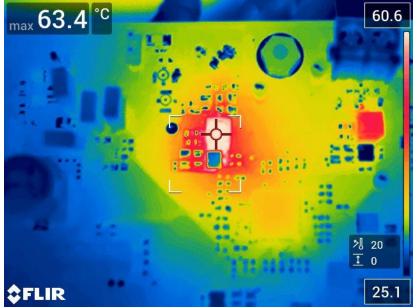

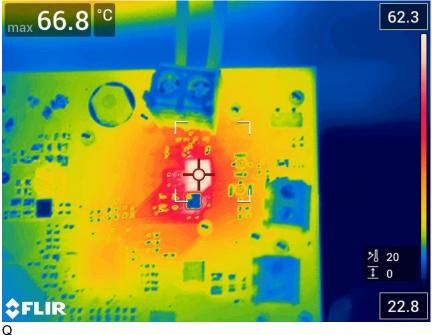

### Section 3: thermal images page 1 of 3

1.2V at 4.8V converter off 12Vin: No fan

3.3V at 4A off 12Vin No fan

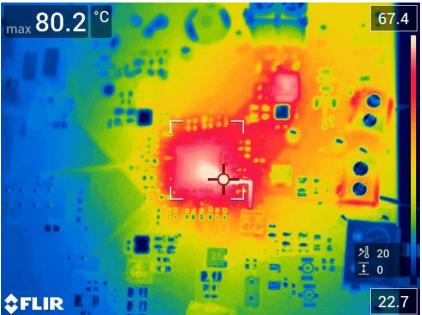

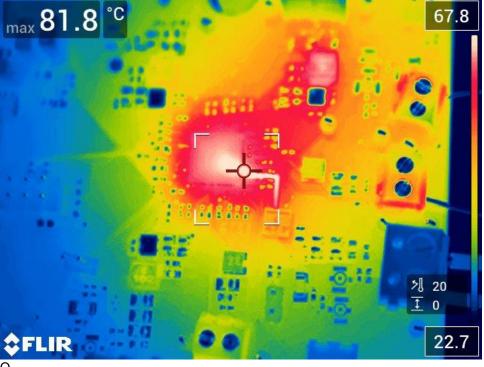

### Section 3: thermal images continued page 2 of 3 0.88V off 3.3V TPS650861

Same, but also 550mA off 1.1V and 446mA off 2.5V

Q

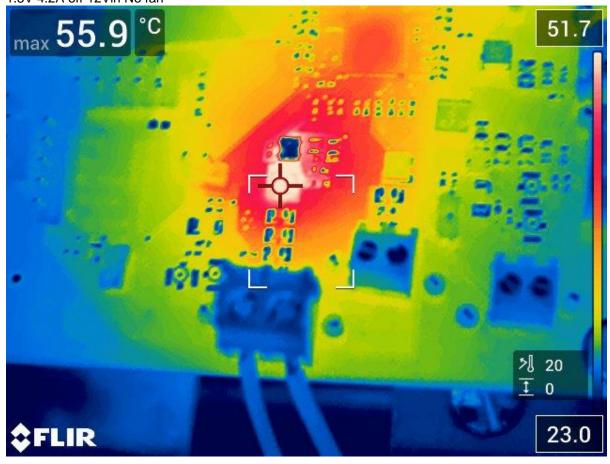

# Section 3: thermal images continued page 3 of 3 1.5V 4.2A off 12Vin No fan

### Section 4: major switching waveforms

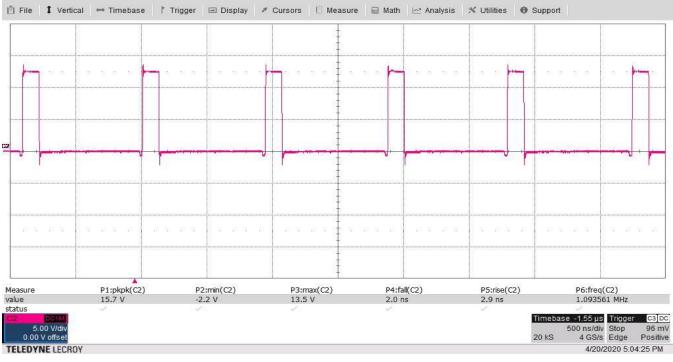

### Off 12V: 1.5V loaded to 4.8A

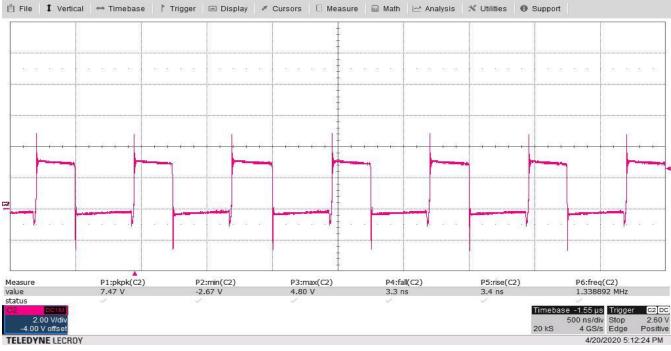

### Section 5: Start up and sequencing page 1 of 2

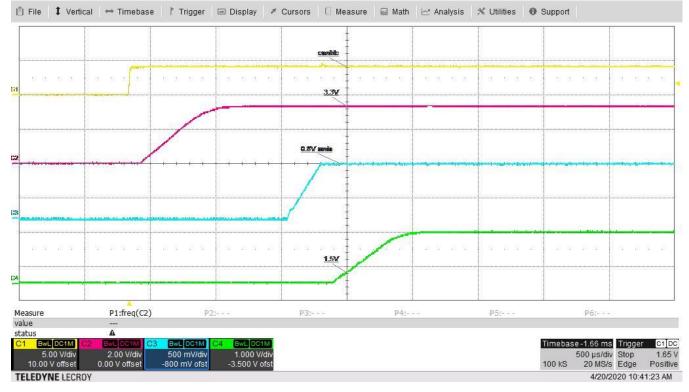

Power up sequencing: This uses the on board 5V bias supply and fake main 0.8V. 5V for bias first and then main 3.3V and then "main 0.8V" and then main 1.5V

### Power up sequencing with PMP22165 mated with TPS53681EVM: Similar to above, but enable shown instead of 5V for channel 1: then 3.3V, then 0.8V main and then 1.5V

TEXAS INSTRUMENTS

www.ti.com

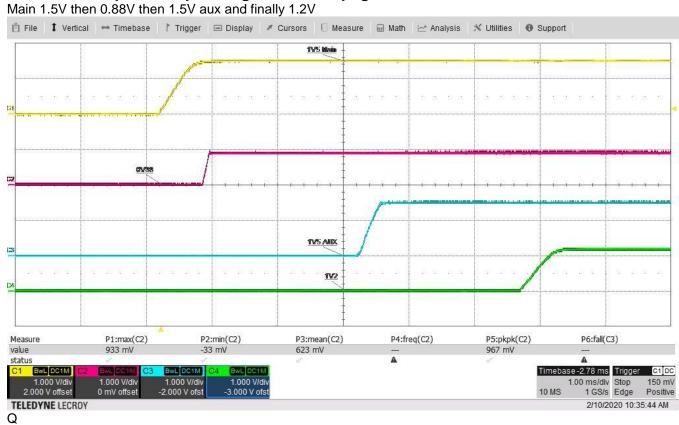

### Section 5: Start up and sequencing continued: page 2 of 2

### I/O voltages coming up after 1.2V is up (2.5V, 3.3V\_IO & 1.1V)

```

TIDT182 - May 2020

```

Power for Xilinx Versal Adaptive Compute Acceleration Platform (ACAP) Reference Design 21 Copyright © 2020, Texas Instruments Incorporated

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated