[Power loss and thermal consideration in gate drivers] [Ritesh Oza]

#### What will I get out of this session?

#### • Purpose:

This presentation will discuss power losses, distribution of power losses, thermal impedance, and impact of various parameters on thermal performance of the gate drivers. Presentation will also show methodology and examples of thermal measurements in gate drivers.

- Part numbers mentioned:

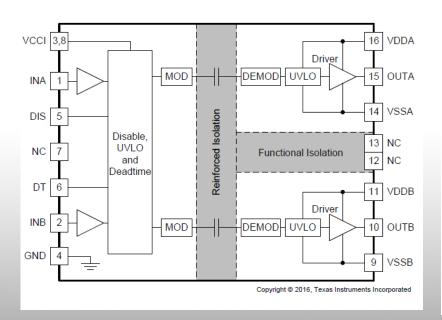

- UCC21520

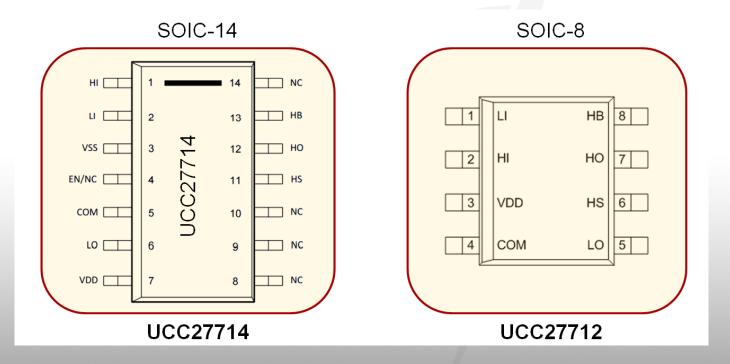

- UCC27714, UCC27712

- Reference designs mentioned:

- TIDM-1000

- PMP20873

- Relevant End Equipments:

- Telecom Power Supplies

- Automotive On Board Charger

- Motor Drives, and more

#### General Classification of Gate Driver ICs

- A) Low Side Gate Driver UCC27524, UCC27531

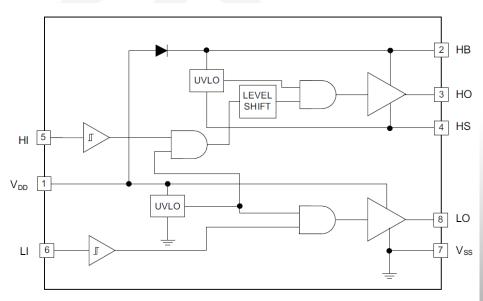

- B) High-Side Low-side Gate Driver or Half-Bridge Gate Driver UCC27712, LM510x

- C) High Side Only Gate Driver

- D) Isolated Gate Driver UCC21520

#### Where does power dissipate?

### Estimating Power Loss in a Gate Driver IC

$$P_{QC} = V_{DD} \times I_{DD} + (V_{DD} - V_{DH}) \times I_{HB}$$

$$P_{IHBS} = V_{HB} \times I_{HBS} \times D$$

• Dynamic Level Shifter Loss

$$P_{LS} = V_{HB} \times Q_P \times f_{SW}$$

$$P_{LS} = V_{HB} \times Q_P \times f_{SW}$$

$$P_{QG1\&2} = 2 \times V_{DD} \times Q_{G} \times f_{SW} \times \frac{R_{GD\_R}}{R_{GD\_R} + R_{Gate} + R_{GFET\_Int}}$$

$$P_{Diode} = Vf \times I_f$$

) + Reverse Recovery Losses

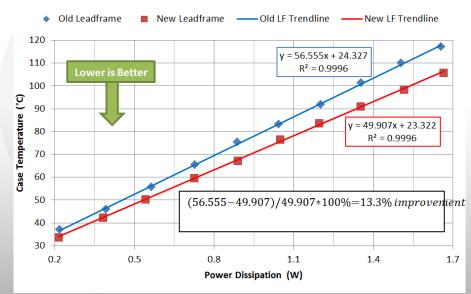

#### Influence of Lead-Frame/Substrate on Thermal Performance

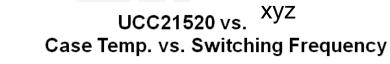

- Identical Layout

- Purely Capacitive Load

- Supply Voltage and current monitored

- Switching frequency varied

- Case temperature measured using type K thermocouple at package top/center

### Megatron LGA Leadframe Comparison Case Temperature vs. Power Dissipation

### Does Package Size Influence Thermal Performance

#### Does Package Size Influence Thermal Performance

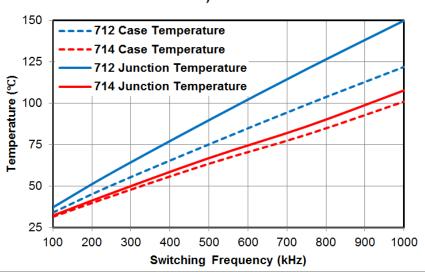

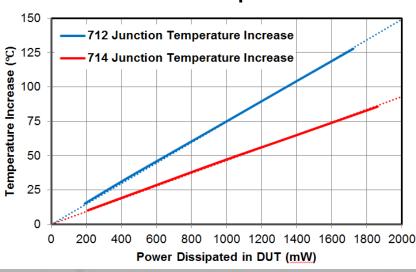

# Thermal Performance of UCC27712, UCC27714

# Est. Junction <u>Temp. Increase</u> vs. Power Dissipation

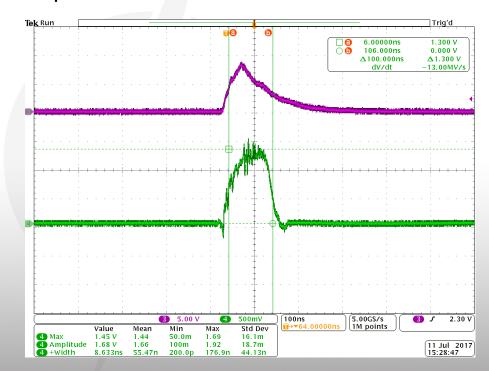

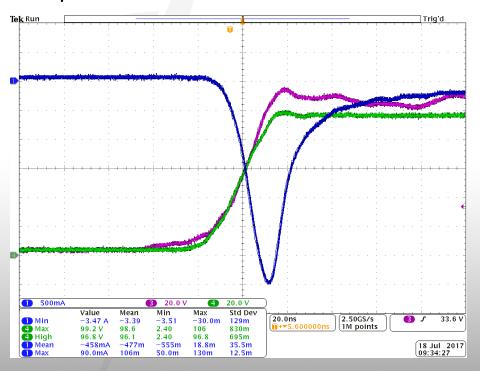

#### Bootstrap Diode Peak Power Dissipation

- During start up, first few cycles high peak current flow through bootstrap diode

- Need to make sure that bond wire, die, and other metal layers can handle this peak current

#### Bootstrap Diode Peak Power Dissipation

If bootstrap diode is reverse biased when high forward current is flowing, then the power dissipation in the bootstrap diode could be very high and could damage the diode.

What information one would need for IC Thermal Analysis?

- A) Maximum Allowed Junction Temperature

- B) IC Thermal Model

- C) IC Power Dissipation

- D) Operating Conditions

#### Thermal Model of a Gate Driver IC

- Based on JEDEC standards

- Many vendors do not provide all the thermal parameters

- Thermal performance comparison must be done on the same board and under the exact same operating conditions

|                      | THERMAL METRIC <sup>(1)</sup>                |              | UNIT |

|----------------------|----------------------------------------------|--------------|------|

| THERMAL METRIC**     |                                              | DW-16 (SOIC) |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 78.1         | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 11.1         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 48.4         | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 12.5         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 48.4         | °C/W |

#### Comparing Thermal Performance of Two Parts

- Case temperature can be compared under the same operating conditions

- But junction temperature cannot be estimated accurately or compared reliably without full thermal model

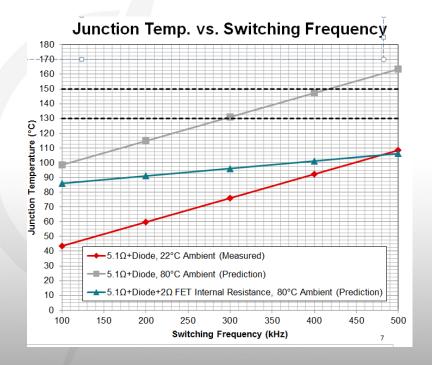

### Thermal Performance Analysis

• TI's Simplified Circuit

- Conservative estimate

- Capacitive load can be estimated based on Q=CV

- Q can be lower for soft switching topologies

- Diode losses are ignored

#### Thermal Performance Analysis

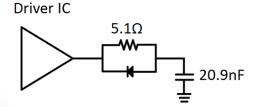

- Estimating junction temperature is always possible when:

- $\triangleright \Psi_{JT}$  is provided on the datasheet  $(T_J = \Psi_{JT} \times P_D + T_C)$

- > Application layout is available for testing

- > Case temperature can be measured

- > IC power dissipation is known

- Predicting thermal performance in three steps:

- 1. Measure T<sub>C</sub> with known voltages/currents and purely capacitive load

- 2. Calculate  $T_J$  for the test cases with  $\Psi_{JT}$

- 3. Characterize  $\Theta_{JA(Effective)}$  for application layout

- 4. Use  $\Theta_{JA(Effective)}$  to estimate junction temperature for any system configuration

### Thermal Performance Analysis

Compare this  $\Theta_{JA}$  with 78°C/W shown in thermal model. Why?

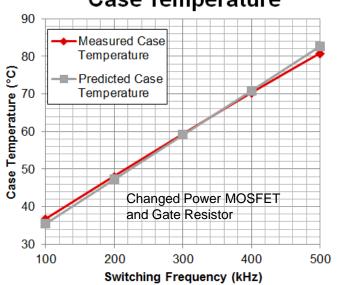

#### Thermal Performance Analysis

- Accuracy

- When system parameters such as power MOSFET and gate resistor changes, one cannot directly compare junction temperature.

- Need to estimate case temperature based on previously calculated Θ<sub>JA(Effective)</sub>

- $\Theta_{JA(Effective)}$  more dependent on board layout and airflow through the board than absolute ambient temperature

- Temperature coefficient of various resistances such as power MOSFET internal gate resistor, driver IC driver stage pull-up/pull-down resistor, and gate resistor is imporatant for very accurate prediction/estimation

- Equal thermal settling time should be allowed before taking thermal measurement

- Proper thermocouple and it's connection is necessary to achieve accurate results

### Thermal Performance Analysis

#### Predicted vs. Measured Case Temperature

#### Prominent Influencers and Best Practices

- Board Layout

- More copper, cooler junction

- Large pour on V<sub>DDA</sub>, V<sub>SSB</sub> minimizes switch node size, maximizes thermal performance

- Soft switching reduces Q<sub>G</sub>, power consumption

- Temperature coefficients

- Driver on/off resistance can vary >10% over temperature

- MOSFET internal gate resistance varies with MOSFET temperature

- Radiation (proportional to T<sup>4</sup>, performance improves with temperature)

- MOSFET internal gate resistance, diode loss, and frequency-related capacitance changes tend to reduce driver IC internal power dissipation

- Can use  $T_{C,Predicted} = (\Theta_{JA} \Psi_{JT})(P_{SW} + P_{STATIC}) + T_A$  to verify vs. measured  $T_C$

### Key Take Aways

- Lot of parameters influence thermal performance of the gate driver IC

- Complete thermal model is essential to do detailed thermal analysis and comparison

- Detailed functional block diagram and power dissipation distribution within IC need to be understood to evaluate thermal reliability of the part

- Estimating thermal performance based on thermal model could save lot of development time

Thank You

Ritesh Oza

**Systems Engineer**

r-oza@ti.com

© Copyright 2017 Texas Instruments Incorporated. All rights reserved.

This material is provided strictly "as-is," for informational purposes only, and without any warranty.

Use of this material is subject to TI's **Terms of Use**, viewable at TI.com