TIPL 4601 TI Precision Labs – ADCs

Created by Reed Kaczmarek and Peggy Liska

**Presented by Peggy Liska**

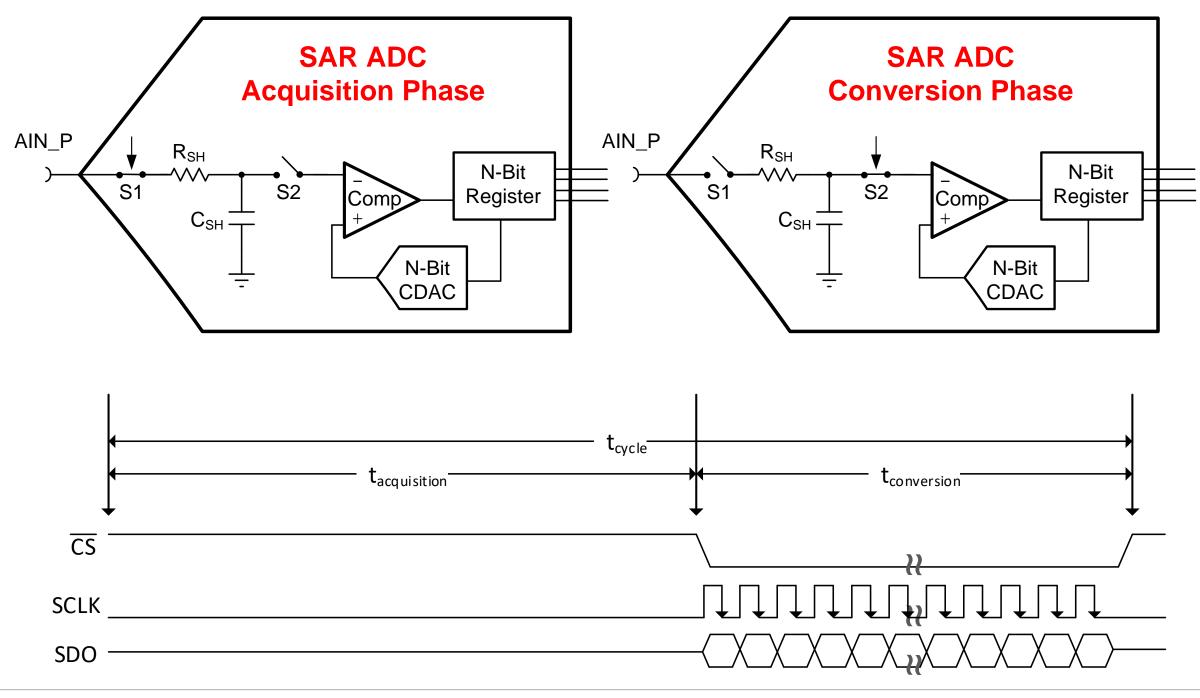

### **Acquisition Phase vs. Conversion Phase**

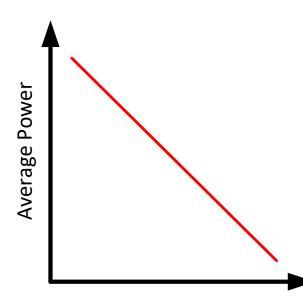

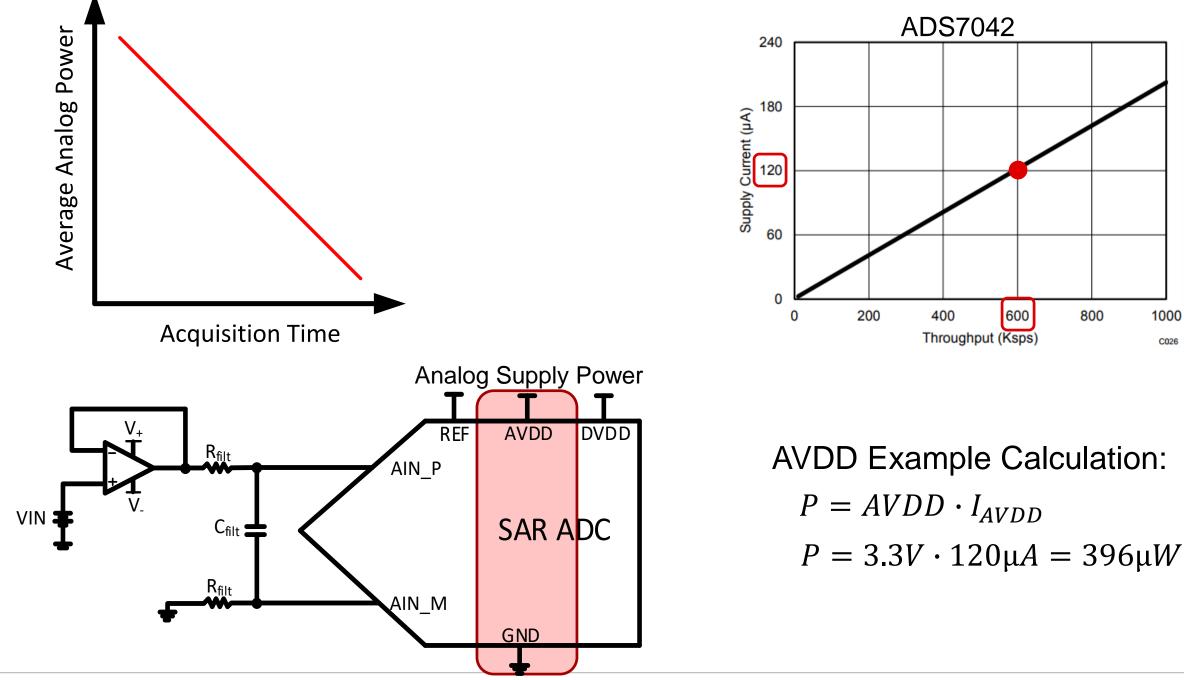

### **Power: Acquisition Phase vs. Conversion Phase**

- The majority of the power is consumed ulletduring the conversion phase

- Note that not all SAR ADCs will lacksquaresupport power scaling

**Acquisition Time**

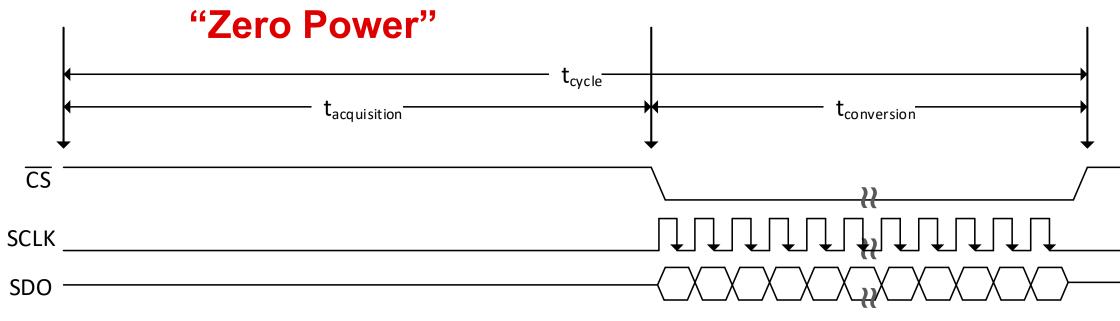

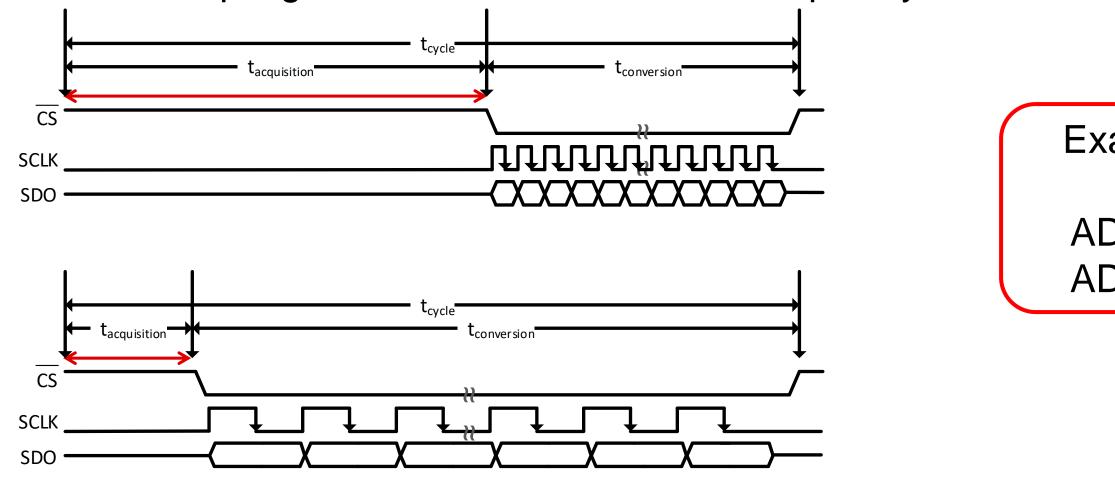

### **Acquisition Time: Internal Conversion Clock**

- Conversion time is fixed due to internal conversion clock

- SCLK sets data output speed only, doesn't effect conversion / acquisition time

- Slower sampling rate directly adds more time for acquisition

4

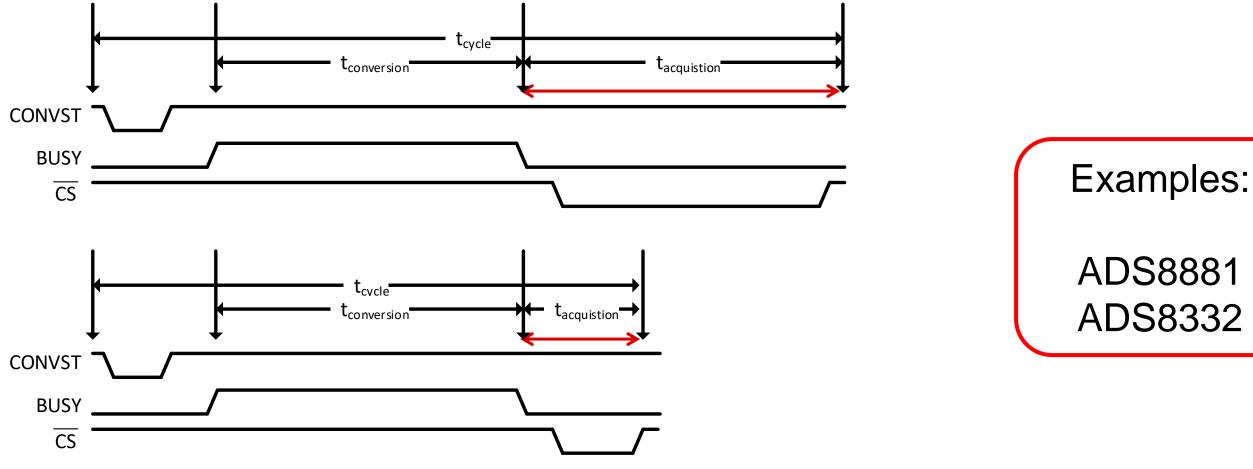

### **Acquisition Time: External Conversion Clock**

- SCLK sets data output speed and conversion time

- Increasing SCLK frequency increases acquisition time for same sampling rate

- Slower sampling rate with the same SCLK frequency increases acquisition time

**Examples**: ADS7042 ADS7056

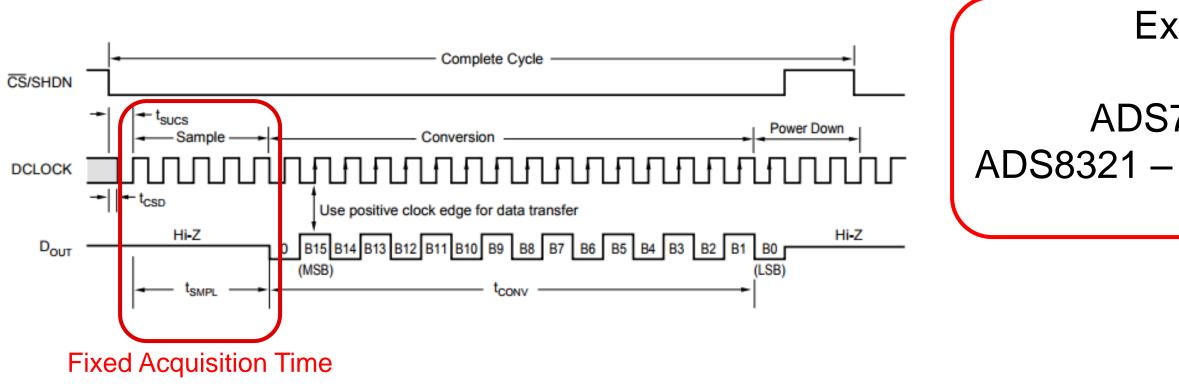

### **Acquisition Time: Other**

- I2C

- Fixed Acquisition

- Always check the datasheet for timing diagram

### ADS7924 – I2C ADS8321 – Fixed Acquisition

### Examples:

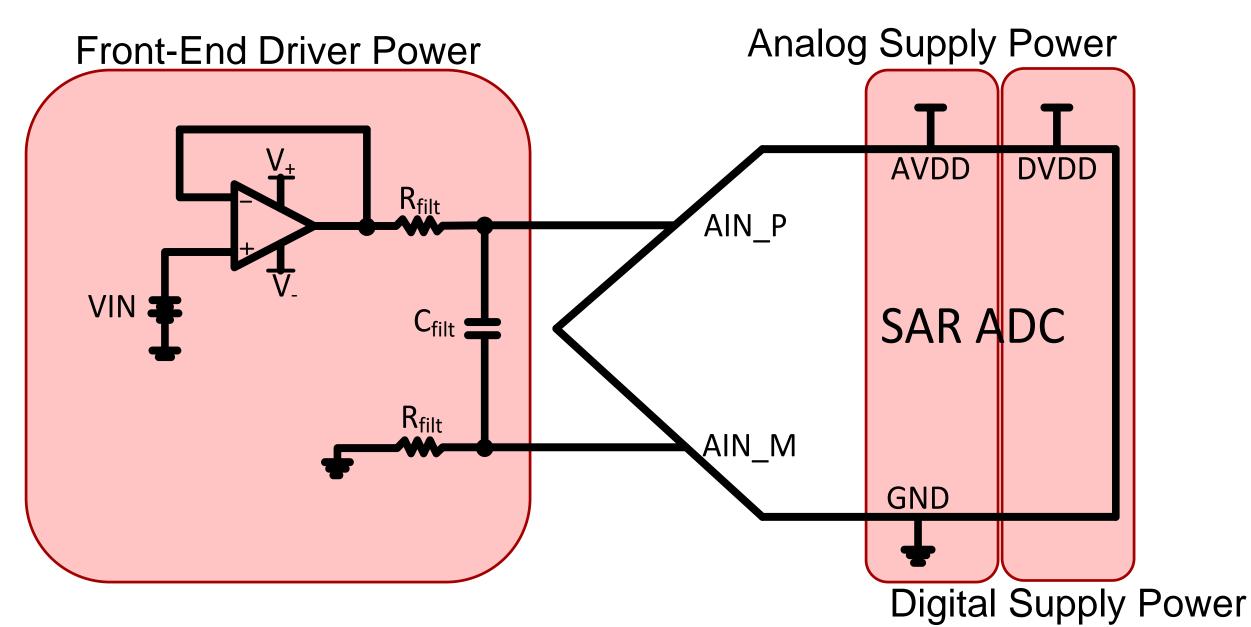

### **Power of a SAR ADC**

### **Analog Supply (AVDD) Power Consumption**

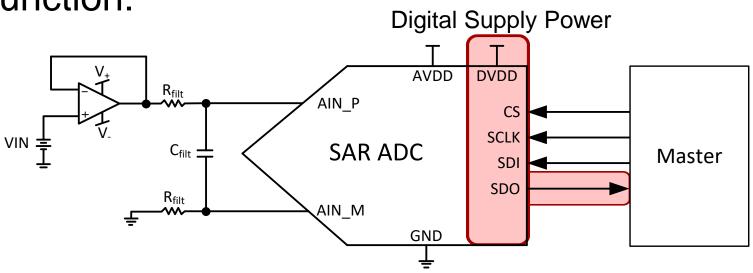

# **Digital Supply (DVDD) Power Consumption**

- Digital supply power consumption is a function: ullet

- DVDD Voltage

- Sampling rate

- Digital output code

- Capacitance

- Trace + Pin + External

$I_{DVDD} = C_{SDO} \cdot DVDD \cdot f$

Where *I*<sub>DVDD</sub> *is the DVDD supply current*  $C_{SDO}$  is the load capacitance on SDO

DVDD is the digital supply voltage f is the frequency of transitions on the SDO output

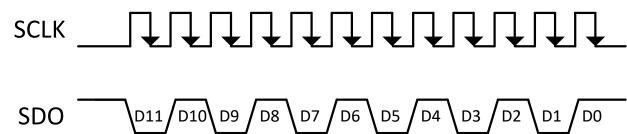

### Maximum SDO Transitions for 12-bit SAR

9

## **Minimizing Digital Supply Power Consumption**

- Use a lower digital voltage (ex. use 1.8V logic instead of 3.3V logic) •

- Run the device at lowest applicable throughput

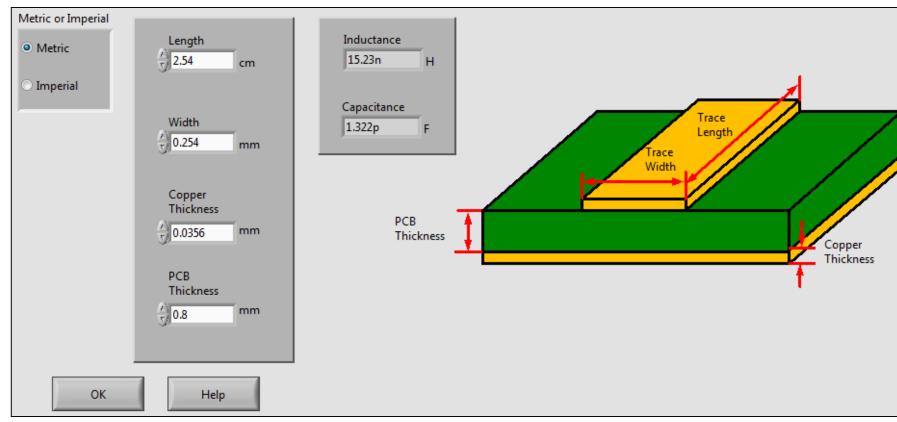

- Reduce the trace capacitance of SDO line ullet

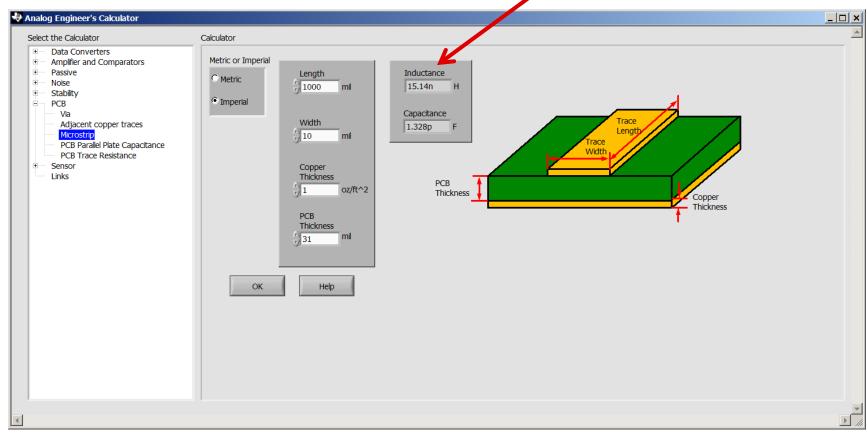

- Analog Engineer's Calculator can be used to determine PCB capacitance

### ti.com/tool/analog-engineer-calc

### **DVDD Supply Power: Example Calculation**

- DVDD Voltage = 3.3V

- Pin Capacitance = 3 pF for both ADC and Master

- SDO Trace Capacitance (2.54 cm long, 0.254 mm wide) = 1.322 pF

- Sampling rate = 1 MSPS

- Frequency of SDO Transitions (12 bit transitions, 1µs cycle time)

$$P_{DVDD} = DVDD \cdot I_{DVDD} = DVDD \cdot (C_{SDO} \cdot DVDD \cdot f)$$

= 3.3V \cdot \left( (1.322pF + 3pF + 3pF \right) \cdot 3.3V \cdot \frac{12 bit}{1\mu s} \right) = 956.8\mu W

Where

$P_{DVDD}$  is the total DVDD supply power *I*<sub>DVDD</sub> *is the DVDD supply current*  $C_{SDO}$  is the load capacitance on SDO DVDD is the digital supply voltage f is the frequency of transitions on the SDO output

**TEXAS INSTRUMENTS**

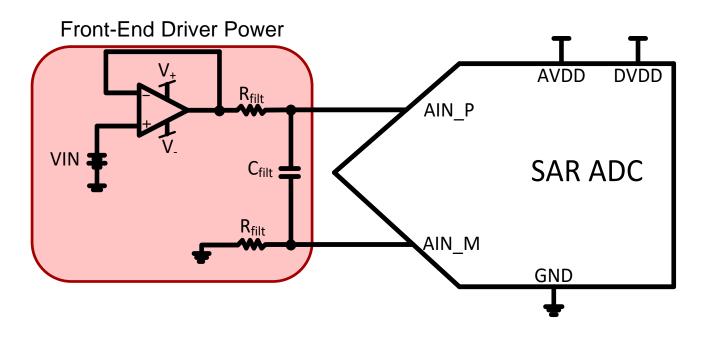

### **Front-End Driver Power Consumption**

| Amplifier | Bandwidth | l <sub>Q</sub> |  |

|-----------|-----------|----------------|--|

| OPA365    | 50 MHz    | 5 mA           |  |

| OPA211    | 45 MHz    | 3.6 mA         |  |

| OPA320    | 20 MHz    | 1.45 mA        |  |

| TLV313    | 1 MHz     | 65 µA          |  |

| LPV811    | 8 kHz     | 450 nA         |  |

| $P = I_Q \cdot$ | $((V_{+}) -$ | $(V_{-}))$ |

|-----------------|--------------|------------|

|-----------------|--------------|------------|

Where *P* is the amplifier power consumption *I*<sub>0</sub> is opamp quiescent current *V*<sub>+</sub> *is positive opamp power supply V*\_ is negative opamp power supply

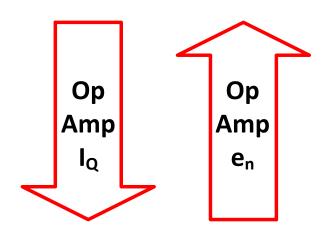

### **Front-End Driver Tradeoffs**

$e_n \propto 1/\sqrt{I_0}$ Where  $e_n$  is opamp noise density *I*<sub>0</sub> is opamp quiescent current

- Large feedback resistors will act as a small load and result in less power consumption but add more noise

- A good rule of thumb is to keep the Op Amp noise dominant lacksquare

$$e_{n_{opa}} \ge 3 \cdot e_{n_{res}}$$

Where

$e_{n_{opa}}$  is opamp noise density

$e_{n_{res}}$  is resistor noise density

TI Precision Labs - Op Amps: Noise

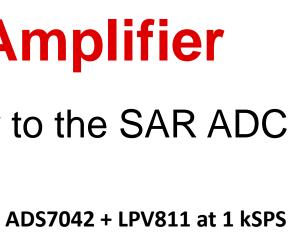

### **Driving a SAR ADC without a Driver Amplifier**

- Low frequency voltage inputs can be connected directly to the SAR ADC ullet

- Applicable for low sampling rates (<20 kSPS)  ${\color{black}\bullet}$

3.5

### ti.com/lit/pdf/sboa206

**TEXAS INSTRUMENTS**

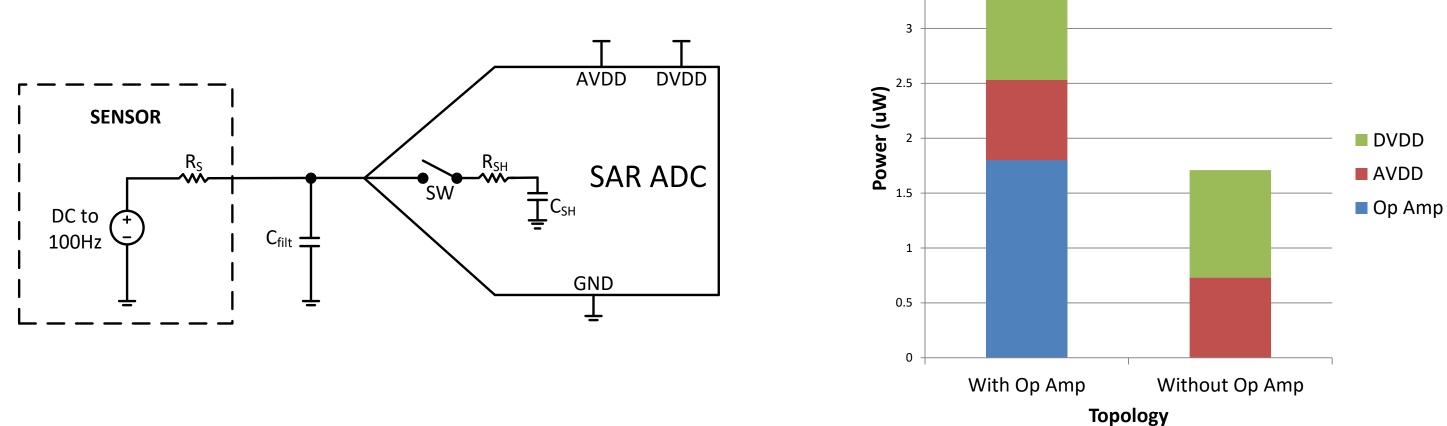

### **Power Scaling Example**

ADS7042 AVDD = 3.3V, DVDD = 3.3V, Op Amp Supply = 4.5V

| Power<br>Level | Amplifier | Sampling<br>Rate | Measured<br>Amplifier Power | Measured<br>Analog Power | Measured<br>Digital Power | Total System<br>Power |

|----------------|-----------|------------------|-----------------------------|--------------------------|---------------------------|-----------------------|

| Low            | LPV811    | 1 kSPS           | 1.8 µW                      | 0.737 µW                 | 0.988 µW                  | 3.5 µW                |

| Medium         | TLV313    | 100 kSPS         | 192.7 µW                    | 73.1 µW                  | 135.8 µW                  | 401.7 µW              |

| High           | OPA320    | 1 MSPS           | 6386 µW                     | 708.3 µW                 | 655.2 μW                  | 7750 μW               |

# Thanks for your time! Please try the quiz.

TIPL 4601 TI Precision Labs – ADCs

**Created by Peggy Liska**

- (T/F) Most of the power is consumed by the SAR ADC during the acquisition phase. 1.

- True a.

- b. False

- You can always reduce the overall power consumption of a SAR ADC by \_\_\_\_\_. 2.

- Decreasing the acquisition time a.

- Increasing the acquisition time b.

- Decreasing the SCLK speed C.

- d. Increasing the SCLK speed

- 3. Which of the following is NOT a way to reduce digital supply (DVDD) power consumption?

- Decrease the digital logic voltage level a.

- Increase the throughput of the ADC b.

- Reduce the trace capacitance of the SDI line C.

- Both a & c d.

- e. Both b & c

- (T/F) Large feedback resistors on the front-end driver reduce power consumption but add noise. 4.

- True a.

- False b.

- Calculate the digital supply power consumption using the following values: HINT: Use the <u>Analog Engineer's Calculator</u>.

- DVDD Voltage = 1.8 V

- SDO Trace Dimensions = 1000 mils long, 10 mils wide

- Copper Thickness = 1 oz

- PCB Thickness = 31 mils

- Sampling rate = 1 MSPS

- ADC Resolution = 12-bit

# **Solutions**

- (T/F) Most of the power is consumed by the SAR ADC during the acquisition phase. 1.

- True a.

- b. False

- You can always reduce the overall power consumption of a SAR ADC by \_\_\_\_\_. 2.

- Decreasing the acquisition time a.

- Increasing the acquisition time b.

- Decreasing the SCLK speed C.

- Increasing the SCLK speed d.

- 3. Which of the following is NOT a way to reduce digital supply (DVDD) power consumption?

- Decrease the digital logic voltage level a.

- Increase the throughput of the ADC b.

- Reduce the trace capacitance of the SDI line C.

- Both a & c d.

- Both b & c е.

- (T/F) Large feedback resistors on the front-end driver reduce power consumption but add noise. 4. True а.

- False b.

- Calculate the digital supply power consumption using the following values: HINT: Use the <u>Analog Engineer's Calculator</u>.

- DVDD Voltage = 1.8 V

- SDO Trace Dimensions = 1000 mils long, 10 mils wide

- Copper Thickness = 1 oz

- PCB Thickness = 31 mils

- Sampling rate = 1 MSPS

- ADC Resolution = 12-bit

$$P = DVDD \cdot (C \cdot DVDD \cdot f)$$

$$P = 1.8V \cdot \left(1.33pF \cdot 1.8V \cdot \frac{12}{1\mu s}\right)$$

$$P = 51.7\mu W$$

### L = 15.14nH C = 1.328pF