# Hercules<sup>™</sup> ARM<sup>®</sup> Cortex<sup>®</sup>-R4 System Architecture

**Memory Protection Unit (MPU)**

# **Memory Protection Unit (MPU): Regions**

- 8, 12, or 16 regions

- ARM Cortex-R5 has 16 regions

- ARM RM42 (Corona) has 8 regions

- All other Hercules ARM processors have 12 regions

- The region with highest region number has the highest priority.

- Overlay of regions is possible.

- Regions are defined based on the following:

- Base address

- Region size

- Sub-regions

- Region attributes

- Region access permissions

NOTE: Before enabling the MPU, at least one region has to be defined. Otherwise the CPU can get into a state which can only be recovered by reset!

#### **Memory Protection Unit: Memory map by region**

TMS570 Default Memory Map

Region 12

| Address Range            |                         | Instruction Memory Type          |                                           | Data Memory Type                           |                                   |                        |

|--------------------------|-------------------------|----------------------------------|-------------------------------------------|--------------------------------------------|-----------------------------------|------------------------|

|                          |                         | Cache enabled                    | Cache disabled                            | Cache enabled                              | Cache disabled                    | Execute Never          |

| 0xFFFFFFFF<br>0xFFF80000 | System<br>Registers     | Normal                           | Normal                                    | Strongly Ordered                           | Strongly Ordered                  | Execute Never          |

| 0xFFF7FFFF               | Peripheral<br>Registers | Normal                           | Normal                                    | Strongly Ordered                           | Strongly Ordered                  | Execute Never          |

| 0xFFF78000               |                         |                                  |                                           |                                            |                                   |                        |

| 0xFFA0FFFF               | Coresight<br>Debug      | Normal                           | Normal                                    | Strongly Ordered                           | Strongly Ordered                  | Execute Never          |

| 0xFFA00000               |                         |                                  |                                           |                                            |                                   |                        |

| 0xFF7FFFFF               | Peripheral<br>Memory    | Normal                           | Normal                                    | Strongly Ordered                           | Strongly Ordered                  | Execute Never          |

| 0xFF000000               |                         |                                  |                                           |                                            |                                   |                        |

| 0xFEFFFFFF               | - CRC                   | Normal                           | Normal                                    | Strongly Ordered                           | Strongly Ordered                  | Execute Never          |

| 0xFE000000               |                         |                                  |                                           |                                            |                                   |                        |

| 0xFDFFFFFF               | - HPI                   | Normal                           | Normal                                    | Strongly Ordered                           | Strongly Ordered                  | Execute Never          |

| 0xFD000000               |                         |                                  |                                           |                                            |                                   |                        |

| 0x64FFFFFF               | External<br>Memory      | Normal, Cacheable,<br>Non-Shared | Normal, Non-<br>Cacheable, Non-<br>Shared | Normal, WBWA-<br>Cacheable, Non-<br>Shared | Normal, Non-<br>Cacheable, Shared | Execution<br>Permitted |

| 0x6000000                |                         |                                  |                                           |                                            |                                   |                        |

| 0x1FFFFFFF               | - Flash Swap            | Normal, Cacheable,<br>Non-Shared | Normal, Non-<br>Cacheable, Non-           | Normal, WBWA-                              | Normal, Non-<br>Cacheable, Shared | Execution<br>Permitted |

| 0x18000000               |                         |                                  | Shared                                    | Cacheable, Non-<br>Shared                  |                                   |                        |

| 0x17FFFFFF               | eSRAM                   | Normal, Cacheable,<br>Non-Shared | Normal, Non-<br>Cacheable, Non-<br>Shared | Normal, WBWA-                              | Normal, Non-<br>Cacheable, Shared | Execution<br>Permitted |

| 0x08000000               |                         |                                  |                                           | Cacheable, Non-<br>Shared                  |                                   |                        |

| 0x00FFFFFF               | Program<br>Memory       | Normal, Cacheable,<br>Non-Shared | Normal, Non-                              | Normal, WBWA-                              | Normal, Non-                      | Execution<br>Permitted |

| 0x00000000               |                         |                                  | Cacheable, Non-<br>Shared                 | Cacheable, Non-<br>Shared                  | Cacheable, Shared                 |                        |

Region1

# **Memory Protection Unit: Memory Attributes**

- Strongly-ordered (so) and Device (dev):

- Explicit load/stores to strongly-ordered and device regions always produce the exact size and number of transactions.

- Accesses to strongly-ordered and device regions always appear in the order they are listed in the program.

- Strongly-ordered versus Device:

- Strongly-ordered access are ordered with respect to \*all\* other explicit load/stores.

- Device accesses are only ordered with respect to other device accesses.

- Normal (norm):

- Load/stores to normal memory regions may result in any size and number of transactions.

For example: Two neighboring half-word stores might be merged into a single-word write.

- With respect to ordering, accesses to normal memory may be reordered.

- Examples:

- load-norm-A, load-dev-B, load-dev-C, load-norm-D could be performed as ADBC, or even DBCA;

- load-norm-A, load-so-B, load-so-C, load-norm-D must be performed as ABCD.

# **Memory Protection Unit: Memory Regions**

#### Base Address

- Defines start of memory address range

- Has to be multiple of region size (e.g. 256 byte region aligned on 256 byte boundary)

- Non-size aligned regions might result in unpredictable behavior

- Region size: From 32B up to 4GB

- Region attributes:

- Define access permissions for a region

- Memory type (strongly ordered, normal, device)

- Shared, non-shared

- Non-cachable

- Write-through cachable

- Write-back cachable

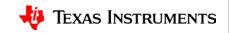

#### Memory Protection Unit: Overlapping Memory Regions & Sub-regions

- Overlapping regions:

- Higher-numbered region defines access permission.

- Provides more flexibility to protect memory which is not region-size aligned.

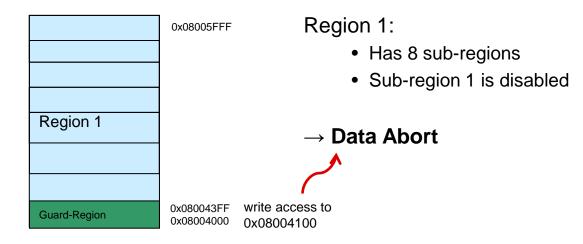

- Sub-regions:

- Each region can be split into 8 equal size, nonoverlapping sub-regions.

- Sub-regions can be enabled/disabled in the CP15 (MPU Region Size and Enable Register).

- Region sizes below 256 bytes do not support sub-regions.

# For more information

- SafeTI Web Page: <u>www.ti.com/safeti</u>

- Hercules Web Page: <u>www.ti.com/hercules</u>

- Data sheets

- Technical Reference Manual

- Application notes

- Software & tools downloads and updates

- Order evaluation and development kits

- Hercules Safety Microcontrollers Training Series

<u>training.ti.com/hercules</u>

- Cortex-R Processor Architecture

- Peripherals

- Software

- Functional Safety

- For questions about this training, refer to the Engineer-2-Engineer Support Forum <u>www.ti.com/hercules-support</u>

- News and announcements

- Ask technical questions

- Search for technical content

©Copyright 2017 Texas Instruments Incorporated. All rights reserved.

This material is provided strictly "as-is," for informational purposes only, and without any warranty. Use of this material is subject to TI's **Terms of Use**, viewable at TI.com