# PCIe Signal Integrity

Prepared by Lee Sledjeski Presented by Nicholaus Malone

## **Five generations of PCI Express**

| PCle                           | Bandwidth | Line rate   | Coding    | UI       | Media                 | Stressed eye                   | Eye pattern |

|--------------------------------|-----------|-------------|-----------|----------|-----------------------|--------------------------------|-------------|

| Gen 1.0 (2003)                 | 250 MB/s  | 2.5<br>Gbps | 8b/10b    | 400 ps   | FR-4                  | Open – N/A                     |             |

| Gen 2.0 (2005)                 | 500 MB/s  | 5<br>Gbps   | 8b/10b    | 200 ps   | FR-4                  | Open – N/A                     |             |

| Gen 3.0 (2010)                 | 1 GB/s    | 8<br>Gbps   | 128b/130b | 125 ps   | FR-4                  | HEO: ≤ 0.30 UI<br>VEO: ≤ 25 mV |             |

| Gen 4.0 <i>(</i> 2017 <i>)</i> | 2 GB/s    | 16<br>Gbps  | 128b/130b | 62.5 ps  | Low-loss PCB          | HEO: ≤ 0.30 UI<br>VEO: ≤ 15 mV |             |

| Gen 5.0 <i>(</i> 2019 <i>)</i> | 4 GB/s    | 32<br>Gbps  | 128b/130b | 31.25 ps | Ultra-low-loss<br>PCB | HEO: ≤ 0.30 UI<br>VEO: ≤ 15 mV |             |

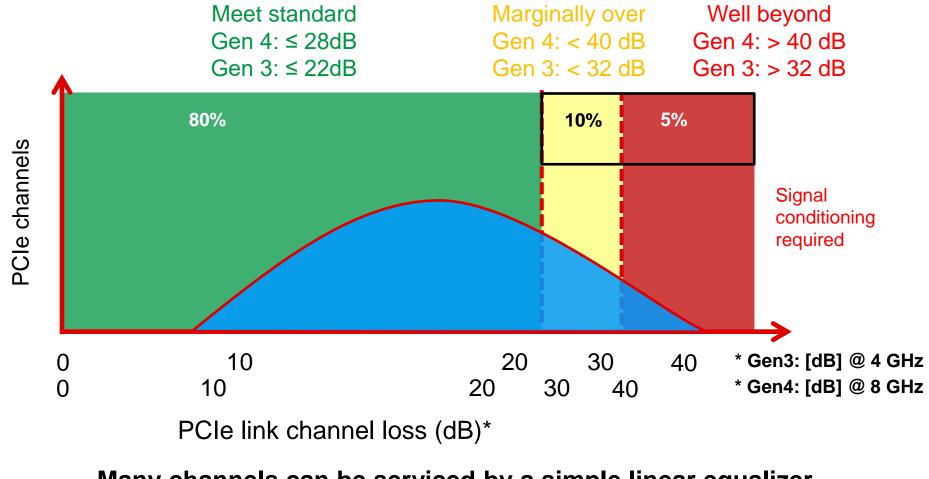

### PCIe Gen3/4 insertion loss landscape model

Many channels can be serviced by a simple linear equalizer

3

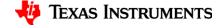

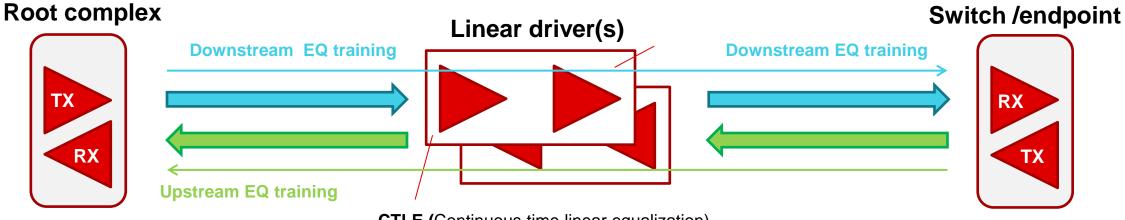

# Signal conditioners to remedy impairments

**CTLE (**Continuous time linear equalization)

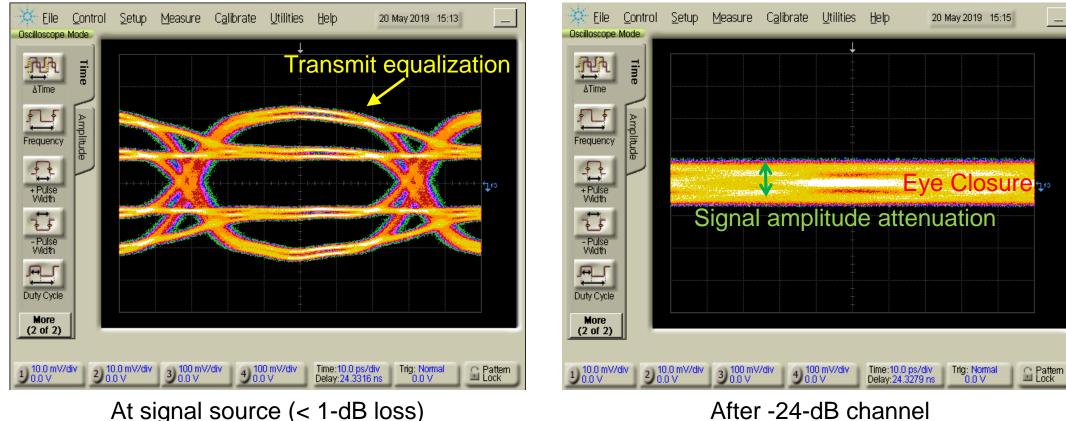

# **PCIe Gen4 without in-channel linear equalization**

After -24-dB channel

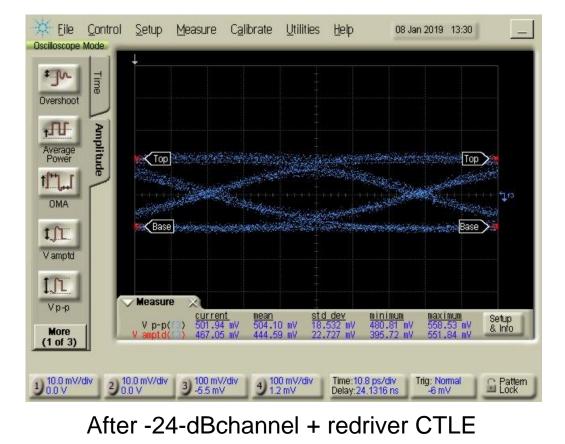

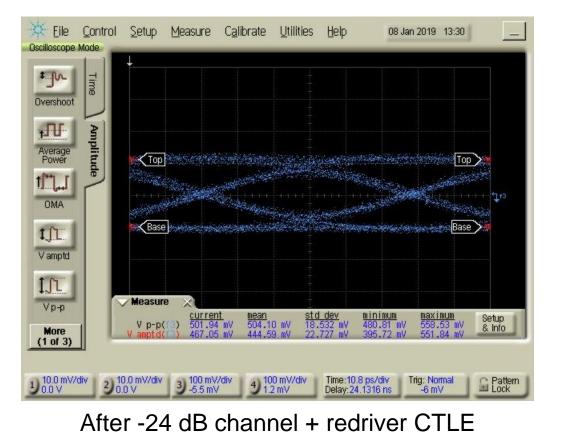

## **PCIe Gen4 with in-channel linear equalization**

#### The redriver restores horizontal and vertical eye opening

🜵 Texas Instruments

6

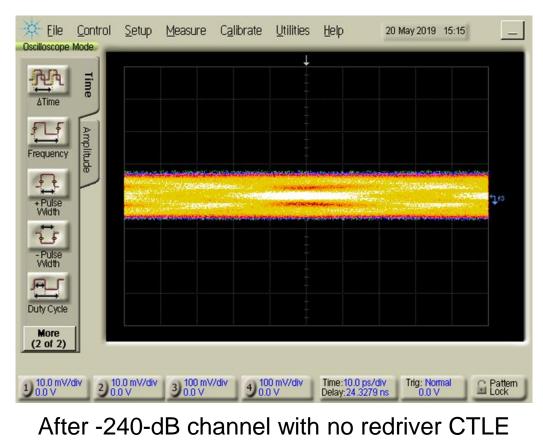

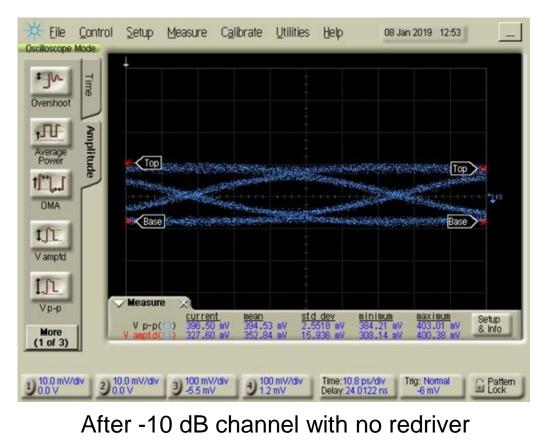

## **PCIe Gen4 with in channel linear equalization**

#### Longer channel with redriver looks exactly like shorter channel without redriver

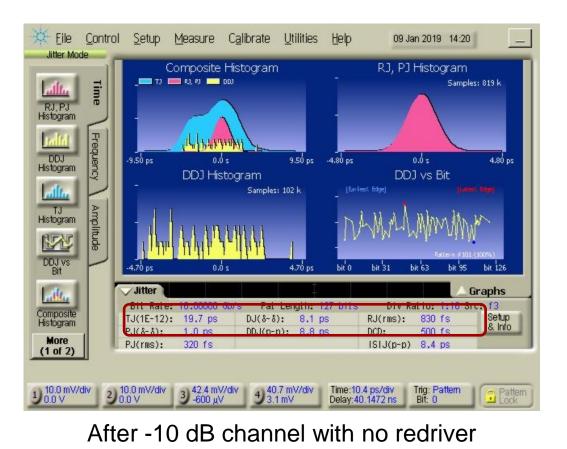

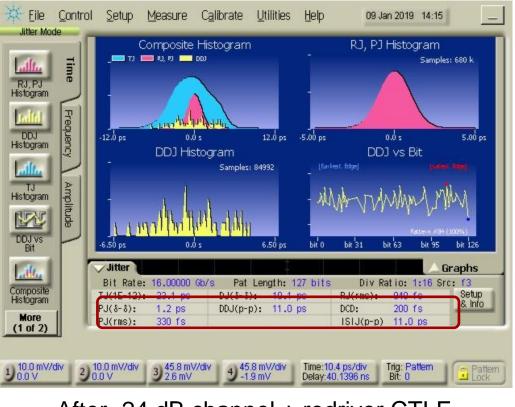

# PCIe Gen4 linear equalization – jitter comparison

Rj: + 100fs Dj: + 2ps Tj: + 3.4ps

After -24 dB channel + redriver CTLE

8

# **Short quiz**

- 1. Check all correct statements:

- A. PCI Express is a serial bus protocol

- B. PCI Express uses a 100 MHz clock to provide robust setup and hold time on the PCI data

- C. PCI Express currently operates up to 16 Gbps

- D. PCI Express never uses any signal conditioning components

- 2. Check all correct statements:

- A. PCI Express is a widely used standard in computers

- B. Not all PCI Express channels will need signal conditioning

- C. Linear equalization can be very effective extending the reach of a PCIe link

- D. Protocol Aware Retimer operation is defined by the PCIe 4.0 standard.

- 3. PCI Express repeaters using Linear equalization have extremely low latency.

- A. True

- B. False

- C. Unknown

© Copyright 2019 Texas Instruments Incorporated. All rights reserved.

This material is provided strictly "as-is," for informational purposes only, and without any warranty. Use of this material is subject to TI's **Terms of Use**, viewable at TI.com