Jacinto™ 7 processors: virtualization

## Virtualization features

- · Key features and benefits

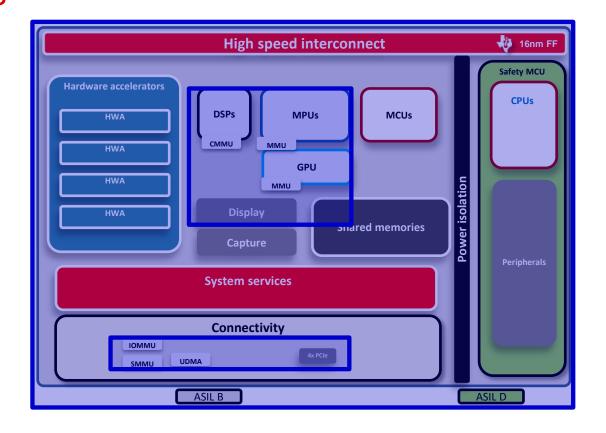

- Heterogeneous processing cores

- Application-specific hardware accelerators

- Device management architecture

- Memory architecture and data movement

- Safety and isolation features

- Virtualization features

- Security features

- Power management features

- Network connectivity

- Flash and storage

- Serial connectivity

## Virtualization features

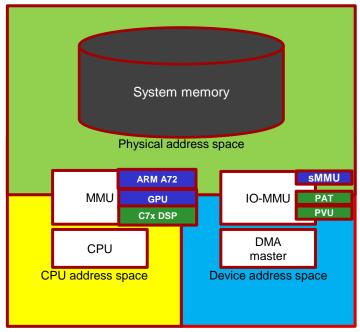

- Memory Management Unit (MMU)

- CPU 2-stage MMUs: A72, C71x, GPU (PVU as 2<sup>nd</sup> stage)

- IO-MMU

- System MMU (sMMU):

- Standard ARMv3 SMMU 2-stage system MMU

- Support for PCle Single-Root I/O Virtualization (SRIOV)

- TI IO-MMU Peripheral Virtualization Unit (PVU):

- Deterministic address translation for real-time data (e.g. DSS)

- Channelized Translation Lookaside Buffer (TLB); SW-triggered Flexible page size

- Page-based Address Translator (PAT):

- Fine-grain, real-time address translation (4/16/64KB or 1MB)

- Supports deterministic scatter-gather /defragmentation (e.g. display)

- Address-mapped translation space

- Peripheral support:

- DSS virtualized ownership of pipe and overlay management

- GPU virtual resource manager

- ARM generic interrupt controller (GIC-500)

TI IP

#### Virtualization features 8 virtual 4 independent Virtualized **GPUs** display pipelines Up to 64 flows endpoints C7x+ MMA Rest of **GPU** DSS Ethernet PCle peripherals MMU MMU MMU Credentials mapping PVU + PAT sMMU Address translation + resource isolation Firewalls – per channel basis Peripheral configuration DMA configuration Memory **TEXAS INSTRUMENTS**

Jacinto™ 7 processors: security management

# Security management features

- · Key features and benefits

- Heterogeneous processing cores

- Application-specific hardware accelerators

- Device management architecture

- Memory architecture and data movement

- Safety and isolation features

- Virtualization features

- Security features

- Power management features

- Network connectivity

- Flash and storage

- Serial connectivity

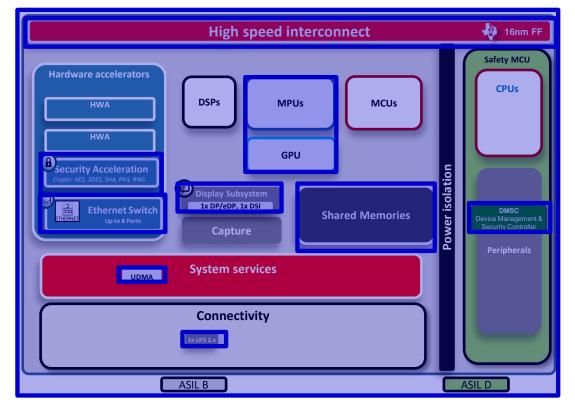

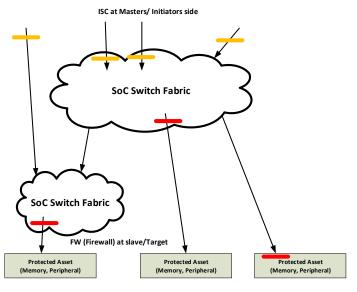

# Security management features

- Secure boot and runtime security support

- Customer-securable device via One-Time-Programmable (OTP) ROM

- DMSC (Arm Cortex-M3) security manager:

- Sandbox concept for base root of trust

- Secure messaging for all requests to DMSC

- Endpoint protection:

- Initiator-Side Security Control (ISC)

- Firewalls: Peripheral, Channelized, Memory

- Central hardware cryptography:

- Multiple algorithms implemented in hardware

- SHA2, AES, etc.

- DMA flows route-able to or from crypto engines

- Permissions controlled by DMSC

- IP/peripheral features

- Cryptography required by standards (EDP, UFS, etc.)

- GPU/decoder/DSS/Ethernet secure features

- Arm TrustZone

Jacinto™ 7 processors: power management

## Power management features

- · Key features and benefits

- Heterogeneous processing cores

- Application-specific hardware accelerators

- Device management architecture

- Memory architecture and data movement

- Safety and isolation features

- Virtualization features

- Security features

- Power management features

- Network connectivity

- Flash and storage

- Serial connectivity

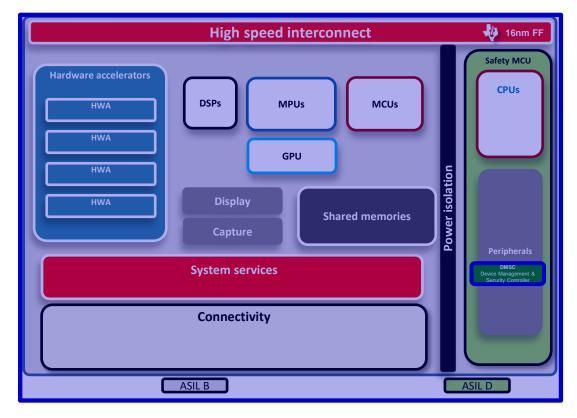

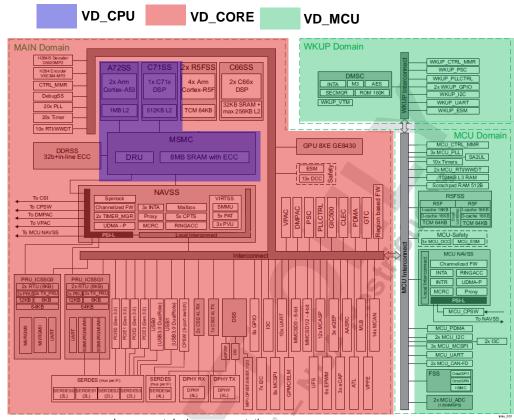

## Power management features

- Voltage domains (AVS, power modes):

- Adaptive voltage scaling for main CPUs

- Shut off Main during MCU-only mode

- Power domains:

- Internally-switched domains on major core/IP

- Clocking control:

- Multiple PLL for fine-grain clock control

- Dynamic Frequency Scaling (DFS)

- Clock gating (SW and automatic)

- Power management IP:

- Wake-up (WKUP) domain

- Power-OK (POK) voltage detectors

- Power glitch detectors (PGD)

- Temperature sensors (per major domain)

- Thermal diode

example superset device representation

# Power management features

#### Power modes:

Total power + high

low

- \*ACTIVE: All rails on, cores/peripherals active

- Standby: Arm CPU WFI (wait for interrupt) mode, system idled

- Core power domain OFF: All main power domains OFF, MCU on

- Deep sleep: All main power domains OFF, MCU Arm Cortex-R5 CPU off

- \*MCU-only: Main voltage domain OFF, MCU on

- Suspend2RAM: All rails off except DDR IO, DDR in self-refresh mode

\* NOTE: Can boot directly into MCU-only or ACTIVE mode

### For more information

- For more training on Jacinto 7 processors: <a href="http://training.ti.com/jacinto7">http://training.ti.com/jacinto7</a>

- Download Processor SDK Automotive for Jacinto 7 processors: <a href="http://www.ti.com/tool/PROCESSOR-SDK-DRA8X-TDA4X">http://www.ti.com/tool/PROCESSOR-SDK-DRA8X-TDA4X</a>

- Order TDA4VM Jacinto Automotive processors for ADAS & autonomous vehicles: http://www.ti.com/product/TDA4VM

- Order the TDA4VMx evaluation module: <a href="http://www.ti.com/tool/TDA4VMXEVM">http://www.ti.com/tool/TDA4VMXEVM</a>

- Order DRA829V Jacinto Automotive processors for gateway & vehicle compute: <a href="http://www.ti.com/product/DRA829V">http://www.ti.com/product/DRA829V</a>

- Order the DRA829Vx evaluation module: <a href="http://www.ti.com/tool/DRA829VXEVM">http://www.ti.com/tool/DRA829VXEVM</a>

- For questions regarding topics covered in this training, visit the processors support forum at the TI E2E Community website: <a href="https://e2e.ti.com">https://e2e.ti.com</a>

### ©2020 Texas Instruments Incorporated. All rights reserved.

The material is provided strictly "as-is" for informational purposes only and without any warranty.

Use of this material is subject to TI's **Terms of Use**, viewable at TI.com