### **FPD-Link III ADAS Hub Aggregation MIPI CSI-2 Aggregation Breakdown**

**Casey McCrea Applications Manager, FPD-Link Products Texas Instruments**

TI Confidential – NDA Restrictions

## **CSI-2 Topics Overview**

- 1. FPD-Link Deserializer Hub Basics

- 2. MIPI CSI-2/D-PHY Protocol Review

- 3. D-PHY Overhead

Ē

- 4. Calculating Input Bandwidth

- 5. CSI-2 Aggregation and Forwarding Engine

- 6. Calculating Output Bandwidth

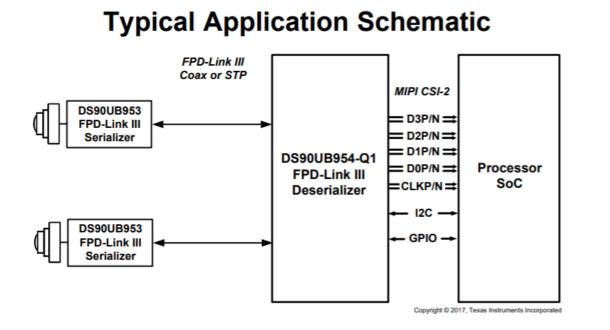

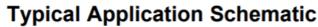

### **FPD-Link Deserializer Hub Basics**

FPD-Link III offers both dual and quad deserializer hubs devices which can aggregate data from multiple remote sensors

Ē

## MIPI CSI-2/D-PHY Protocol

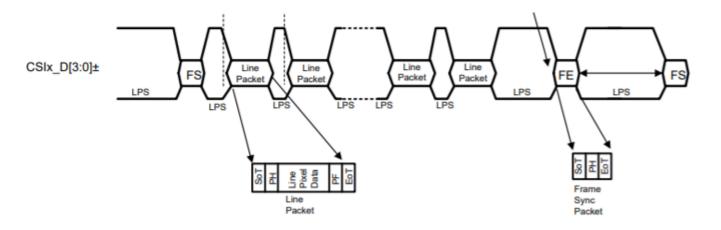

- Breaking down a single frame of CSI-2 video ۲ goes as follows:

- Frame Start Short Packet 32 bits

- LP11 state corresponding to vertical blanking —

- First line of active video data Long Packet

- Includes 32 bit header and 16 bit footer

- Number of bytes per pixel is defined by the data format. For RAW12, there are 3 bytes per 2 pixels

- I P11 state

- Next line

- LP11 state

- . . .

Ę

Frame End – Short Packet 32 bits

### **Overhead in the protocol comes from:** •

- Packet header/footer information

- LP11 states to denote line boundaries

| Dat<br>16<br>Short<br>Data<br>VCX |  | VCX + ECC |

|-----------------------------------|--|-----------|

|-----------------------------------|--|-----------|

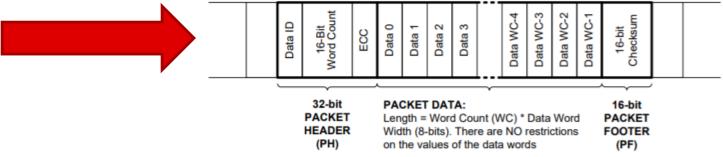

### 32-bit SHORT PACKET (SH) Data Type (DT) = 0x00 - 0x0F

### Figure 20. CSI-2 Short Packet Structure

### Figure 21. CSI-2 Long Packet Structure

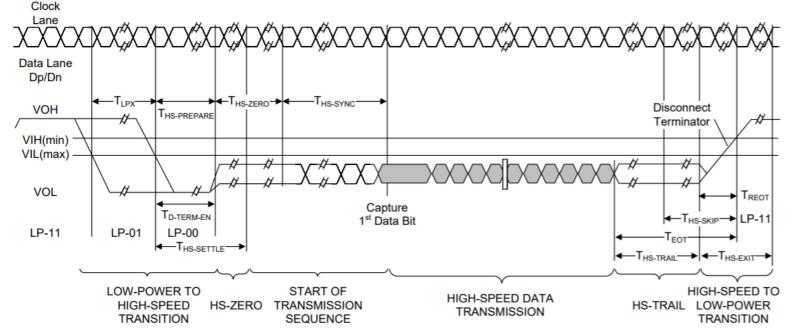

### **D-PHY Overhead**

- CSI-2 requires LP-11 idle states between each long packet to distinguish packet boundaries

- The amount of time it takes for the transmitter to transition between HS mode and LP-11 mode is  $\bullet$ defined by the MIPI D-PHY physical layer

- Transition overhead is broken down into T<sub>LPX</sub>, T<sub>HS-PREPARE</sub>, T<sub>HS-ZERO</sub>, T<sub>HS-SYNC</sub>, T<sub>HS-TRAIL</sub>, and T<sub>HS-EXIT</sub>

- $T_{LPX} + T_{HS-PREPARE} + T_{HS-ZERO} + T_{HS-SYNC} + T_{HS-TRAIL} + T_{HS-EXIT} = T_{OVERHEAD}$

- Additional overhead is also introduced in discontinuous clock mode compared to continuous clock  $\bullet$ mode

### **CSI-2/DPHY Protocol**

Ē

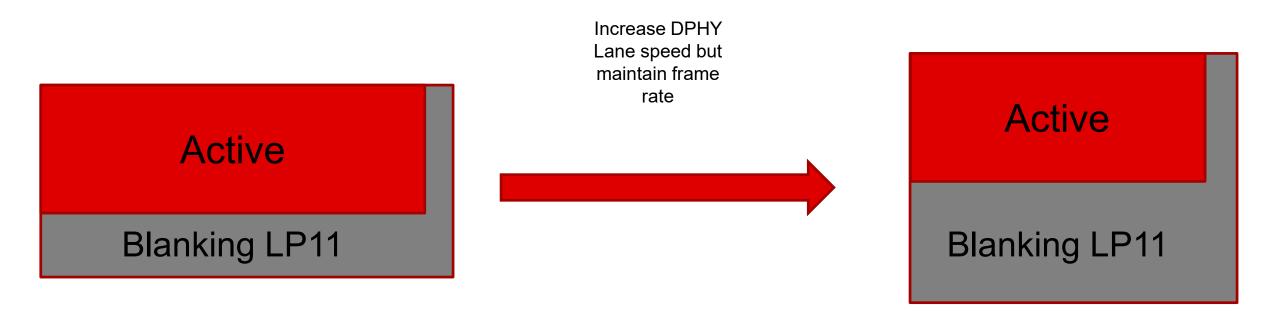

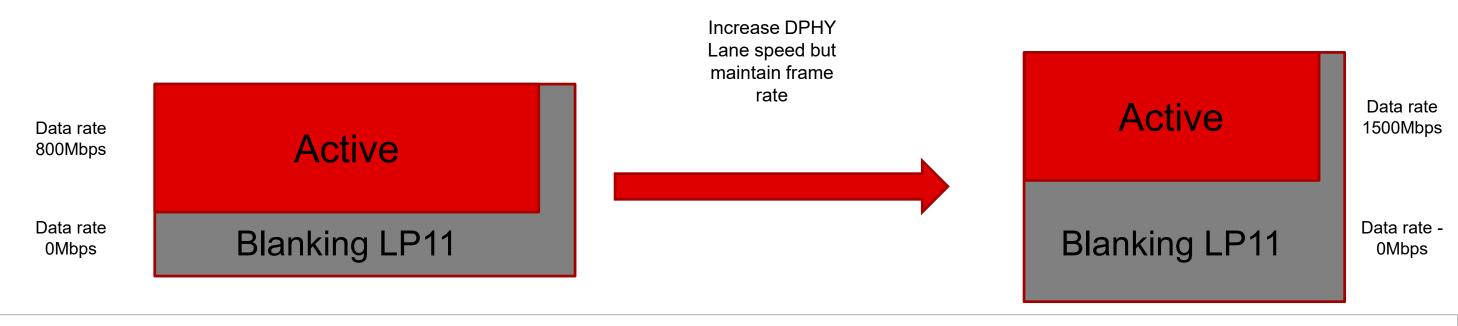

- The CSI-2 source can choose to send each line at arbitrary speed since CSI-2 does not require **specific horizontal timing** like other video protocols

- If each horizontal line is sent at higher speed (higher PCLK), then the vertical blanking must increase to • maintain the same frame rate

- This directly correlates to the DPHY lane speed

- The blanking here is <u>not</u> CSI-2 data it is time spent in LP11 which does not add to the number of bytes ٠ getting forwarded

# **Calculating Input Bandwidth**

- For video protocols such as HDMI, LVDS, RGB, pixels are always scanned out at a constant PCLK rate which makes • video bandwidth easy to define:

- Htotal x Vtotal x FPS x bits per pixel

Ē

- However for CSI-2 since horizontal pixels can be sent at an arbitrary lane speed, bandwidth varies across one frame • high bandwidth during active region and no bandwidth during vertical blanking

- Ex. In both cases below the total number of pixels sent during the frame is the same, but the example on the right uses • higher lane speed. Averaged over one frame, the bandwidth is the same because the same number of pixels was sent and the total frame time is the same, but during the active video region the bandwidths are different

### Texas Instruments

## **Calculating Input Bandwidth**

- We must consider the fact that input bandwidth is variable across one video frame

- This means input bandwidth is the worst case number during the active portion of each sensor's output

- Input Bandwidth =  $\frac{Horizontal active bit per line}{det active}$ Line time

- Example: 1280x964 @ 36Hz, Vtotal = 1250 lines, RAW12

• *Line Time*

$$= \frac{1}{_{36Hz*1250}} = 22.2us$$

• Bits per line = 1280 \* 12bpp = 15360 bits

•

$$Bandwidth = \frac{Bits \ per \ line}{Line \ time} = 691Mbps$$

- Input bandwidth during vertical blanking is 0Mbps

- We must calculate bandwidth at the line level because FPD-Link has line buffers, not frame buffers

# **CSI-2 Aggregation and Forwarding Engine**

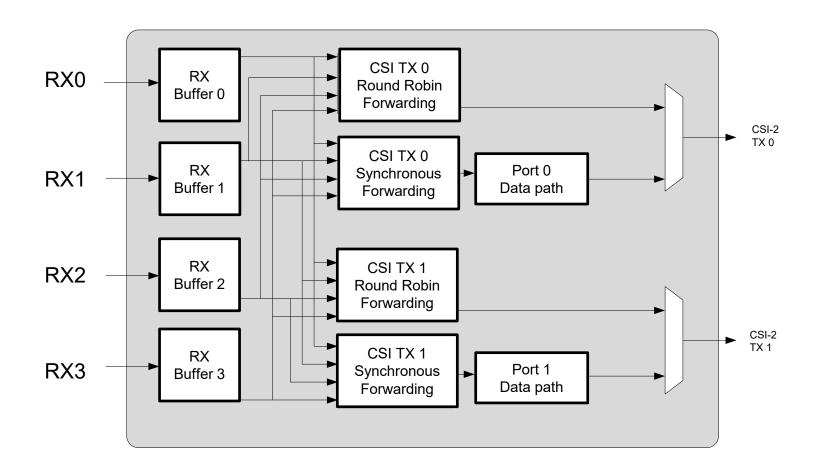

The deserializer hub contains RX channel • buffers for each input to store incoming video streams before they are pulled by the forwarding engine (2 or 4 based on the hub device)

F

- Each RX buffer is designed to store only up to ~1-2 lines of video depending on the line size

- The forwarding engine rotates through RX ports checking if line data is ready to be forwarded to the CSI-2 outputs

- For example during one sensor's inactive video, the engine can forward a port which is receiving active video

- Between each sensor's line data the ۲ DPHY protocol requires an LP-11 state

# **CSI-2 Aggregation and Forwarding Engine**

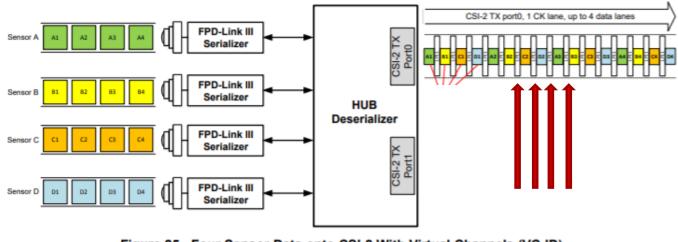

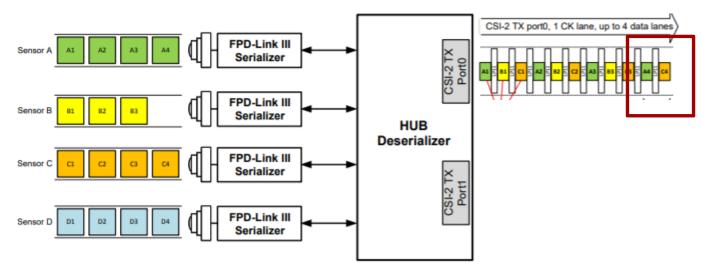

- In the picture to the right, 4 sensors with equal video • parameters are sent out of 1 port in round robin fashion with LP11 states in between each

- With this type of equal spacing, it is straightforward to • determine the number of LP states per unit time

- In this example, sensors are running at different video • rates so which means the number of packets forwarded from each sensor can be unequal over an arbitrary unit time

- Depends on relative relation of active/inactive video times, ٠ line length sizes, and line times

Figure 25. Four Sensor Data onto CSI-2 With Virtual Channels (VC-ID)

# **Calculating Output Bandwidth**

Ē

- Protocol overhead from aggregation must be considered in order to calculate CSI-2 output bandwidth

- Refer to slide 5 for information on overhead from each LP-11 transition

- Refer to slide 10 for information on how aggregating multiple sensors introduces mode LP-11 transitions

- This output bandwidth is compared with the sum of the input bandwidths for the aggregated sensors in order to determine if the system can function robustly

- Output bandwidth is a factor of the lane speed setting, number of lanes, continuous vs. discontinuous clock mode, and also the characteristics of the input videos being aggregated!

Sum of Input Bandwidths to be Forwarded < Output Bandwidth = Aggregation OK

# **Calculating Output Bandwidth**

- Determine time period of repeating pattern for forwarded lines from each sensor •

- *Repeating Time = LCM(Line Time 0, Line Time 1, Line Time 2, Line Time 3)*

- · Round line times to nearest integer number for estimation

- Find the number of lines forwarded by each sensor during this time period:

- Sensor\_N Lines =  $\frac{Repeating Time}{Sensor_N Line Time}$

- For each line there will be associated LP-11 transition overhead

- Total Lines = Sensor0 Lines + Sensor 1 Lines + Sensor 2 Lines + Sensor 3 Lines

- Calculate the total number of bits sent during the repeating time period •

- Total Repeating Bits = (Sensor 0 Lines \* Sensor 0 Bits Per Line) + (Sensor 1 Lines \* Sensor 1 Bits Per Line) + (Sensor 2 Lines \* Sensor 2 Bits Per Line) + (Sensor 3 Lines \* Sensor 3 Bits Per Line)

- Calculate Output Bandwidth •

- *Output Bandwidth* =

Total Repeating Bits Total Repeating Bits +(Total Lines \*ToverHEAD)

# **Calculating Output Bandwidth**

### • Example - Assume the following parameters:

- Number of transmitter lanes = 4

- D-PHY lane speed = 1600Mbps/lane

- Data rate = 1600Mbps\*4 Lanes = 6.4Gbps

- Clock mode = Continuous

- $T_{OVERHEAD} = 0.76 \mu s$

- Sensors:

Ē

| RX Port | Horizontal Active | Vertical Total | Frame Rate | Bits Per Pixel |

|---------|-------------------|----------------|------------|----------------|

| 0       | 1920              | 1200           | 30         | 12             |

| 1       | 640               | 500            | 60         | 20             |

| 2       | 1920              | 860            | 36         | 16             |

| 3       | 2560              | 1620           | 30         | 12             |

- Input Bandwidth Sum = 3.66Gbps

- Calculated Output Bandwidth = 5.36Gbps

- Input Bandwidth < Output Bandwidth so aggregation is viable!

### Calculated Input Bandwidth

829Mbps

384Mbps

951Mbps

1490Mbps

### Quiz

- 1. We are trying to aggregate two identical sensors with exactly 2MP each. There are two options for the sensor dimensions: 2000x1000 or 1000x2000. Which case would require more output bandwidth assuming the pixel clock rate is the same between them?

- 2000x1000 sensors a)

- 1000x2000 sensors b)

- They require the same bandwidth C)

- 2. Which sensor configuration will result in higher input bandwidth contribution for FPD-Link aggregation at the line level? SensorX: 1920x1080@30Hz, RAW12 with 1200 vertical total lines or SensorY: 1920x720@30Hz, RAW12 with 1200 vertical total lines?

- a) SensorX

- SensorY b)

- They are the same C

### Thank you

Ē

- FPD-Link technical resources

- TI FPD-Link products

- ti.com/interface/fpd-link-serdes/products.html

| ų     | Texas Insti                         | RUMENTS               | Search                        |           |                |         |

|-------|-------------------------------------|-----------------------|-------------------------------|-----------|----------------|---------|

| Produ | cts Applications                    | Design resources      | Quality & reliabili           | ity Suppo | ort & training | Order I |

|       | ne > Interface > FPD-Link<br>erface | < SerDes              |                               |           |                |         |

|       | Overview Pro                        | ducts Reference desig | gns Support & train           | ning      |                |         |

| 1enu  | FPD-Link S                          | erDes – Pro           | ducts                         |           |                |         |

|       | Quick searc                         | :h                    |                               |           |                |         |

|       | Function                            | Select 🗸              | Output<br>compatibility       | Select    | ~              |         |

|       | Color depth<br>(bpp)                | 2 8 S S               | - Features                    | Select    | ~              |         |

|       | Input<br>compatibility              | Select 🗸              | Total<br>throughput<br>(Mbps) | ≥ 600     | ≤ 13312        |         |

### Texas Instruments

© Copyright 2019 Texas Instruments Incorporated. All rights reserved.

This material is provided strictly "as-is," for informational purposes only, and without any warranty. Use of this material is subject to TI's Terms of Use, viewable at TI.com