# Retimer vs. Redrivers in PCIe

**TI Precision Labs – PCIe**

Presented by Nicholaus Malone Prepared by Nasser Mohammadi

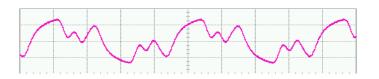

Signal waveform before transmission media

Signal waveform before transmission media

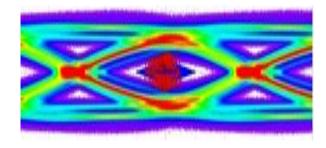

Signal waveform at the end of the transmission media

Signal waveform before transmission media

Signal waveform at the end of the transmission media

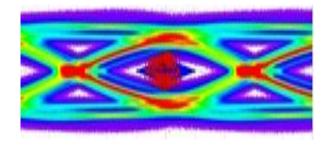

Eye closure at the end of the transmission media

Signal waveform before transmission media

Signal waveform at the end of the transmission media

Eye closure at the end of the transmission media

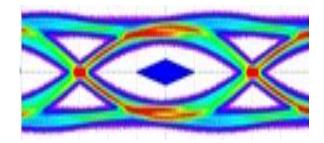

Equalized eye diagram

🔱 Texas Instruments

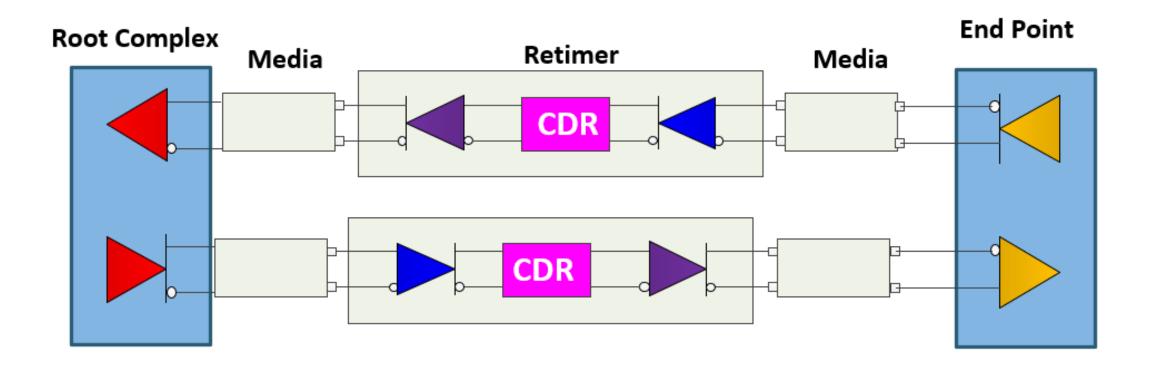

#### How does a retimer work?

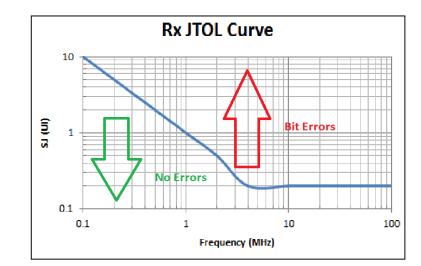

## **Retimer jitter tolerance**

- Retimers compensate for random and deterministic:

- Too much random jitter will result in bit errors

- Retimer periodic and sinusoidal jitter tracking capability: Too much Pj/Sj will also produce errors

- Retimer's output is not jitter free

- There will be some random jitter. If the retimer's own jitter is not superior to the source, it may cause link issues

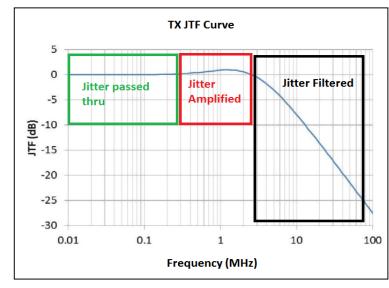

- Jitter Transfer Function

- There will be some deterministic jitter from input passed to output

- It is possible for jitter to be amplified

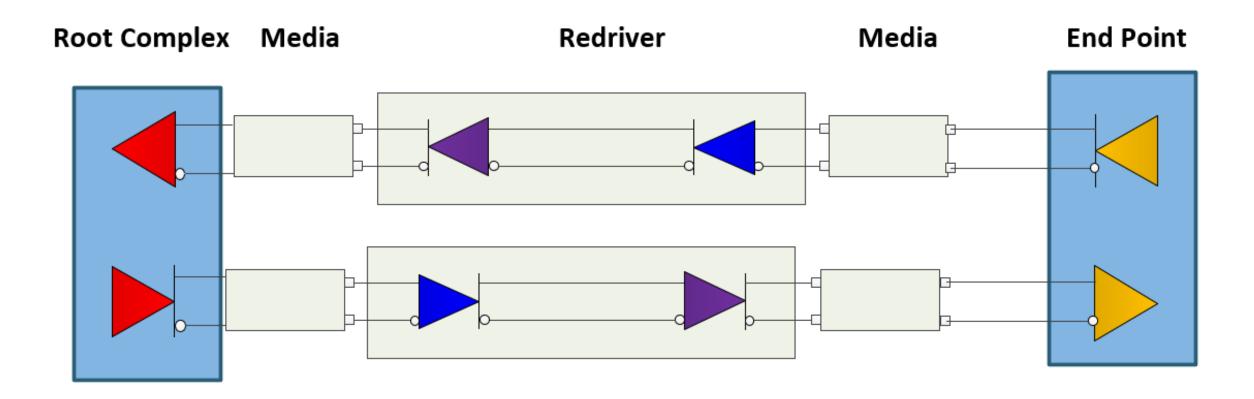

### **Redrivers vs Retimers implementations**

| Feature                               | Redriver  | Retimer | Comments                                                                                                                                                                                                                                                                                     |

|---------------------------------------|-----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Board design/<br>implementation cost  | Low       | High    | <ul> <li>Redriver is a simple component acting like wire in the link</li> <li>Retimer higher cost, requires reference clock, and larger footprint</li> <li>Retimer may require thermal management to meet long term reliability</li> </ul>                                                   |

| Random jitter (RJ)<br>cleaning        | No        | Yes     | <ul> <li>Redrivers can not clean RJ and thus does not reset jitter budget</li> <li>Retimers can clean RJ and should to have superior performance compared to source</li> </ul>                                                                                                               |

| Deterministic jitter (DJ)<br>cleaning | Yes (ISI) | Yes     | <ul> <li>Redrivers typically only clean ISI (optionally cleans DCD &amp; PJ with analog DFE)</li> <li>Retimer cleans ISI, DCD &amp; PJ</li> </ul>                                                                                                                                            |

| Real life functional<br>Inter-op      | Good      | Mixed   | <ul> <li>Linear redriver's simplistic ISI jitter cleaning provides best inter-op</li> <li>Retimer provides very powerful signal integrity tools but often its complexity brings inter-op issues</li> <li>Retimers and linear redrivers work well with end-to-end DP link training</li> </ul> |

| Latency                               | Low       | High    | High latency can cause inter-op issues                                                                                                                                                                                                                                                       |

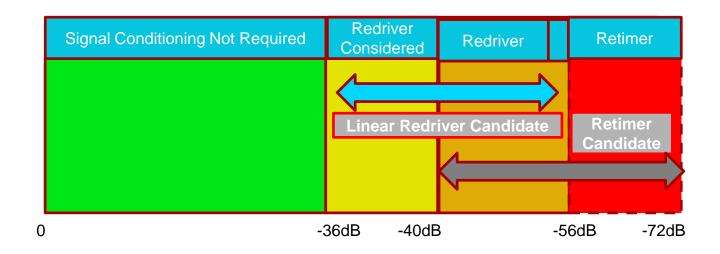

#### **Gen5 Link Budget Feasibility**

- Per PCIe specification, root complex and end point should be able to achieve Gen5 error free operation at up to -36dB total channel loss

- In some cases total channel loss is higher than recommended (-36dB)

- Many applications have a total channel loss between (-40 to -56dB)

- In a case where we have over -56dB loss, a retimer could the only option

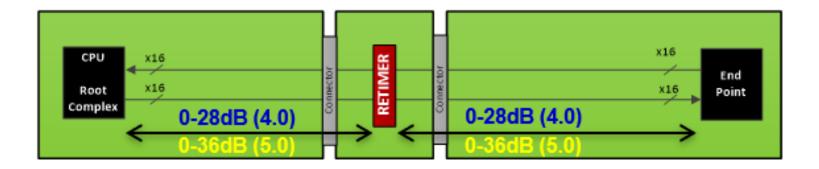

#### **Retimer placement guideline**

- Per PCIe specification:

- At Gen4, retimer should be able to compensate for 28dB Nyquist signal loss

- At Gen5, retimer should be able to compensate for 36dB Nyquist signal loss

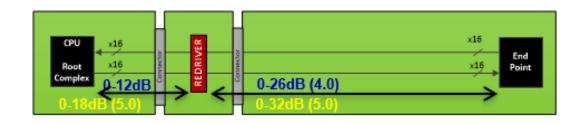

#### **Placement options for redriver placement**

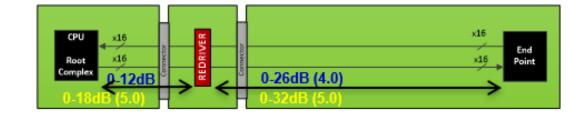

• Near root complex redriver

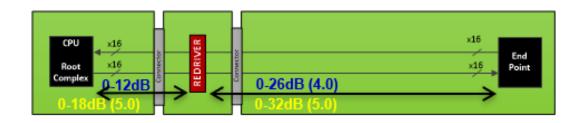

#### **Placement options for redriver placement**

• Near root complex redriver

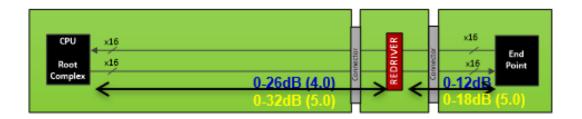

• Near end point redriver

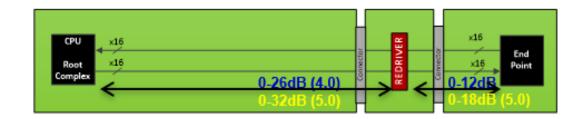

#### **Placement options for redriver placement**

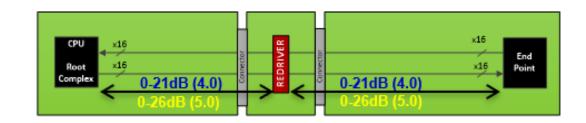

• Near root complex redriver

• Near end point redriver

• Mid-link placement

### Thank you

#### <u>Texas Instruments Precision Labs Website</u>

#### ©2022 Texas Instruments Incorporated. All rights reserved.

The material is provided strictly "as-is" for informational purposes only and without any warranty. Use of this material is subject to TI's **Terms of Use**, viewable at TI.com