# TL1454A, TL1454AY DUAL-CHANNEL PULSE-WIDTH-MODULATION (PWM) CONTROL CIRCUIT

SLVS423 A- MAY 2002 - REVISED SEPTEMBER 2002

- Two Complete PWM Control Circuits

- Outputs Drive MOSFETs Directly

- Oscillator Frequency . . . 50 kHz to 2 MHz

- 3.6-V to 20-V Supply-Voltage Range

- Low Supply Current . . . 3.5 mA Typ

- Adjustable Dead-Time Control, 0% to 100%

- 1.26-V Reference

#### description

The TL1454A is a dual-channel pulse-width-modulation (PWM) control circuit, primarily intended for low-power, dc/dc converters. Applications include LCD displays, backlight inverters, notebook computers, and other products requiring small, high-frequency, dc/dc converters.

D, N OR PW PACKAGE (TOP VIEW) 16 REF CT 15 SCP RT  $\Pi$ DTC1 14 DTC2 13 N2+ IN1+ □ 12 N2-IN1 – ∏ 5 11 \ COMP2 COMP1 [ 10 V<sub>CC</sub> GND 17 OUT1 [ 9 OUT2

Each PWM channel has its own error amplifier, PWM comparator, dead-time control comparator, and MOSFET driver. The voltage reference, oscillator, undervoltage lockout, and short-circuit protection are common to both channels.

Channel 1 is configured to drive n-channel MOSFETs in step-up or flyback converters, and channel 2 is configured to drive p-channel MOSFETs in step-down or inverting converters. The operating frequency is set with an external resistor and an external capacitor, and dead time is continuously adjustable from 0 to 100% duty cycle with a resistive divider network. Soft start can be implemented by adding a capacitor to the dead-time control (DTC) network. The error-amplifier common-mode input range includes ground, which allows the TL1454A to be used in ground-sensing battery chargers as well as voltage converters.

#### **AVAILABLE OPTIONS**

|               | PACKAGED DEVICES <sup>†</sup> |                    |               |              |                  | CUID FORM        |

|---------------|-------------------------------|--------------------|---------------|--------------|------------------|------------------|

| TA            | SMALL OUTLINE (D)             | PLASTIC DIP<br>(N) | TSSOP<br>(PW) | SSOP<br>(DB) | SOP-EIAJ<br>(NS) | CHIP FORM<br>(Y) |

| -20°C to 85°C | TL1454ACD                     | TL1454ACN          | TL1454ACPWR   | TL1454ACDB   | TL1454ACNS       | TL1454AY         |

† The D, DB and NS packages are available taped and reeled. Add the suffix R to the device name (e.g., TL1454ACDR). The PW package is available only left-end taped and reeled (indicated by the R suffix on the device type; e.g., TL1454ACPWR).

### TL1454A, TL1454AY DUAL-CHANNEL PULSE-WIDTH-MODULATION (PWM) CONTROL CIRCUIT

SLVS423 A- MAY 2002 - REVISED SEPTEMBER 2002

#### functional block diagram RT CT | 10 2 16 REF 1.26 V Voltage 1.8 V 2.5 V REF To Internal Circuitry 1.2 V GND VCC osc **PWM** COMP1 Comparator 1 IN1+ 8 OUT1 Amplifier 1 **PWM** COMP2 11 Comparator 2 IN2+ 13 VCC IN2-Error Amplifier 2 UVLO 9 OUT2 and SCP Latch SCP Comparator 2 0.65 V 0.65 V 1 V SCP Comparator 1 1.27 V

14

3

DTC1 DTC2

15

SCP

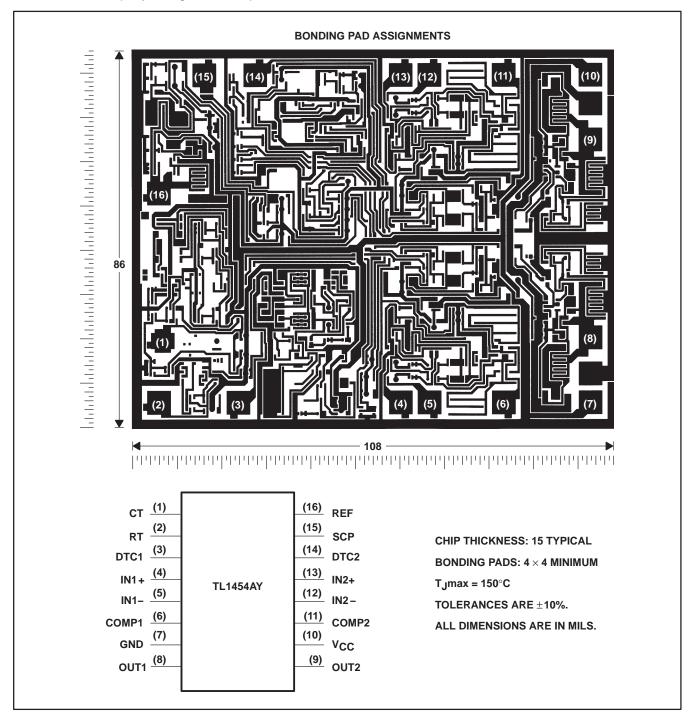

#### **TL1454AY** chip information

This device, when properly assembled, displays characteristics similar to the TL1454AC. Thermal compression or ultrasonic bonding may be used on the doped aluminum bonding pads. The chips may be mounted with conductive epoxy or a gold-silicon preform.

#### theory of operation

#### reference voltage

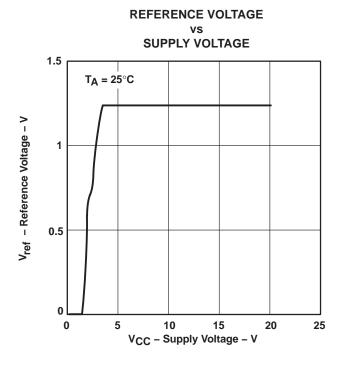

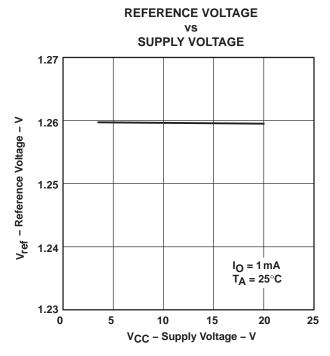

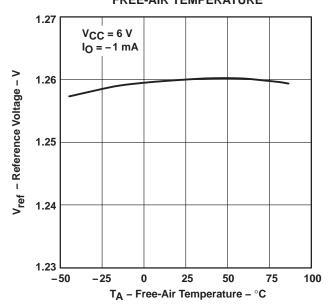

A linear regulator operating from  $V_{CC}$  generates a 2.5-V supply for the internal circuits and the 1.26-V reference, which can source a maximum of 1 mA for external loads. A small ceramic capacitor (0.047  $\mu$ F to 0.1  $\mu$ F) between REF and ground is recommended to minimize noise pickup.

#### error amplifier

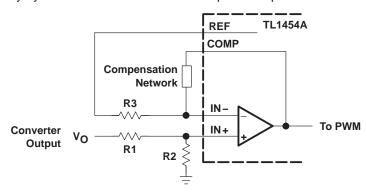

The error amplifier generates the error signal used by the PWM to adjust the power-switch duty cycle for the desired converter output voltage. The signal is generated by comparing a sample of the output voltage to the voltage reference and amplifying the difference. An external resistive divider connected between the converter output and ground, as shown in Figure 1, is generally required to obtain the output voltage sample.

The amplifier output is brought out on COMP to allow the frequency response of the amplifier to be shaped with an external RC network to stabilize the feedback loop of the converter. DC loading on the COMP output is limited to  $45 \, \mu A$  (the maximum amplifier source current capability).

Figure 1 illustrates the sense-divider network and error-amplifier connections for converters with positive output voltages. The divider network is connected to the noninverting amplifier input because the PWM has a phase inversion; the duty cycle decreases as the error-amplifier output increases.

Figure 1. Sense Divider/Error Amplifier Configuration for Converters with Positive Outputs

The output voltage is given by:

$$V_{O} = V_{ref} \left( 1 + \frac{R1}{R2} \right)$$

where  $V_{ref} = 1.26 \text{ V}$ .

The dc source resistance of the error-amplifier inputs should be 10 k $\Omega$  or less and approximately matched to minimize output voltage errors caused by the input-bias current. A simple procedure for determining appropriate values for the resistors is to choose a convenient value for R3 (10 k $\Omega$  or less) and calculate R1 and R2 using:

$$R_1 = \frac{R_3 V_0}{V_0 - V_{ref}}$$

$$R_2 = \frac{R_3 V_0}{V_{ref}}$$

#### error amplifier

R1 and R2 should be tight-tolerance ( $\pm 1\%$  or better) devices with low and/or matched temperature coefficients to minimize output voltage errors. A device with a  $\pm 5\%$  tolerance is suitable for R3.

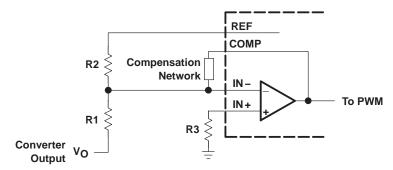

Figure 2. Sense Divider/Error Amplifier Configuration for Converters with Negative Outputs

Figure 2 shows the divider network and error-amplifier configuration for negative output voltages. In general, the comments for positive output voltages also apply for negative outputs. The output voltage is given by:

$$V_O = -\frac{R_1 V_{ref}}{R_2}$$

The design procedure for choosing the resistor value is to select a convenient value for R2 (instead of R3 in the procedure for positive outputs) and calculate R1 and R3 using:

$$R_1 = -\frac{R_2 V_0}{V_{ref}}$$

$$R_3 = \frac{R_1 R_2}{R_1 + R_2}$$

Values in the  $10-k\Omega$  to  $20-k\Omega$  range work well for R2. R3 can be omitted and the noninverting amplifier connected to ground in applications where the output voltage tolerance is not critical.

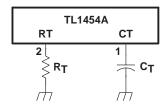

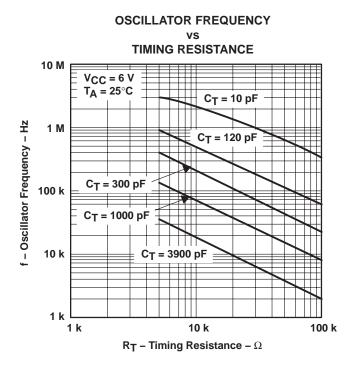

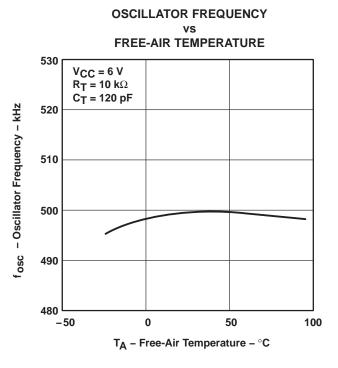

#### oscillator

The oscillator frequency can be set between 50 kHz and 2 MHz with a resistor connected between RT and GND and a capacitor between CT and GND (see Figure 3). Figure 6 is used to determine  $R_T$  and  $C_T$  for the desired operating frequency. Both components should be tight-tolerance, temperature-stable devices to minimize frequency deviation. A 1% metal-film resistor is recommended for  $R_T$ , and a 10%, or better, NPO ceramic capacitor is recommended for  $C_T$ .

Figure 3. Oscillator Timing

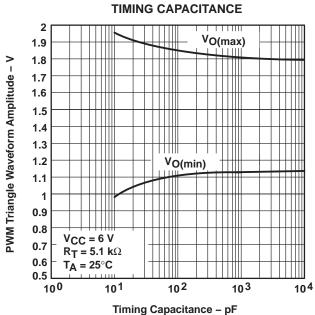

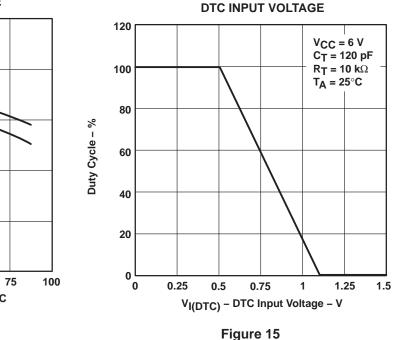

#### dead-time control (DTC) and soft start

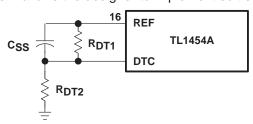

The two PWM channels have independent dead-time control inputs so that the maximum power-switch duty cycles can be limited to less then 100%. The dead-time is set with a voltage applied to DTC; the voltage is typically obtained from a resistive divider connected between the reference and ground as shown in Figure 4. Soft start is implemented by adding a capacitor between REF and DTC.

The voltage, V<sub>DT</sub>, required to limit the duty cycle to a maximum value is given by:

$$V_{DT} = V_{O(max)} - D(V_{O(max)} - V_{O(min)}) - 0.65$$

where V<sub>O(max)</sub> and V<sub>O(min)</sub> are obtained from Figure 9, and D is the maximum duty cycle.

Predicting the regulator startup or rise time is complicated because it depends on many variables, including: input voltage, output voltage, filter values, converter topology, and operating frequency. In general, the output will be in regulation within two time constants of the soft-start circuit. A five-to-ten millisecond time constant usually works well for low-power converters.

The DTC input can be grounded in applications where achieving a 100% duty cycle is desirable, such as a buck converter with a very low input-to-output differential voltage. However, grounding DTC prevents the implementation of soft start, and the output voltage overshoot at power-on is likely to be very large. A better arrangement is to omit  $R_{DT1}$  (see Figure 4) and choose  $R_{DT2}$  = 47 k $\Omega$ . This configuration ensures that the duty cycle can reach 100% and still allows the designer to implement soft start using  $C_{SS}$ .

Figure 4. Dead-Time Control and Soft Start

#### **PWM** comparator

Each of the PWM comparators has dual inverting inputs. One inverting input is connected to the output of the error amplifier; the other inverting input is connected to the DTC terminal. Under normal operating conditions, when either the error-amplifier output or the dead-time control voltage is higher than that for the PWM triangle wave, the output stage is set inactive (OUT1 low and OUT2 high), turning the external power stage off.

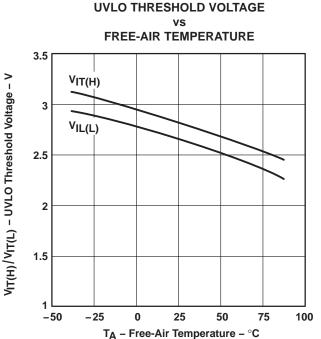

#### undervoltage-lockout (UVLO) protection

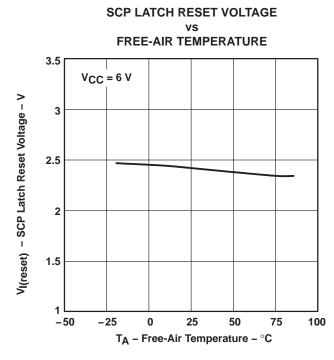

The undervoltage-lockout circuit turns the output circuit off and resets the SCP latch whenever the supply voltage drops too low (to approximately 2.9 V) for proper operation. A hysteresis voltage of 200 mV eliminates false triggering on noise and chattering.

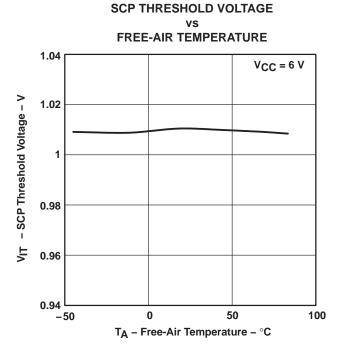

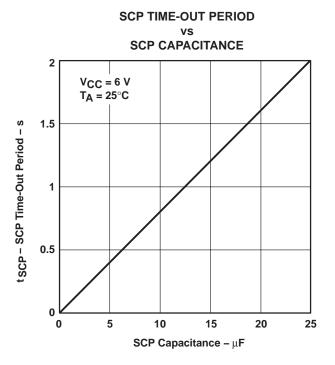

#### short-circuit protection (SCP)

The TL1454A SCP function prevents damage to the power switches when the converter output is shorted to ground. In normal operation, SCP comparator 1 clamps SCP to approximately 185 mV. When one of the converter outputs is shorted, the error amplifier output (COMP) will be driven below 1 V to maximize duty cycle and force the converter output back up. When the error amplifier output drops below 1 V, SCP comparator 1 releases SCP, and capacitor,  $C_{SCP}$ , which is connected between SCP and GND, begins charging. If the error-amplifier output rises above 1 V before  $C_{SCP}$  is charged to 1 V, SCP comparator 1 discharges  $C_{SCP}$  and normal operation resumes. If  $C_{SCP}$  reaches 1 V, SCP comparator 2 turns on and sets the SCP latch, which turns off the output drives and resets the soft-start circuit. The latch remains set until the supply voltage is lowered to 2 V or less, or  $C_{SCP}$  is discharged externally.

#### short-circuit protection (SCP) (continued)

The SCP time-out period must be greater than the converter start-up time or the converter will not start. Because high-value capacitor tolerances tend to be  $\pm 20\%$  or more and IC resistor tolerances are loose as well, it is best to choose an SCP time-out period 10-to-15 times greater than the converter startup time. The value of  $C_{SCP}$  may be determined using Figure 6, or it can be calculated using:

$$C_{SCP} = \frac{T_{SCP}}{80.3}$$

where  $C_{SCP}$  is in  $\mu F$  and  $T_{SCP}$  is the time-out period in ms.

#### output stage

The output stage of the TL1454A is a totem-pole output with a maximum source/sink current rating of 40 mA and a voltage rating of 20 V. The output is controlled by a complementary output AND gate and is turned on (sourcing current for OUT1, sinking current for OUT2) when all the following conditions are met: 1) the oscillator triangle wave voltage is higher than both the DTC voltage and the error-amplifier output voltage, 2) the undervoltage-lockout circuit is inactive, and 3) the short-circuit protection circuit is inactive.

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage, V <sub>CC</sub> (see Note 1)                    | 23 V                         |

|-----------------------------------------------------------------|------------------------------|

| Error amplifier input voltage: IN1+, IN1-, IN2+, IN2            |                              |

| Output voltage: OUT1, OUT2                                      | 20 V                         |

| Continuous output current: OUT1, OUT2                           | ±200 mA                      |

| Peak output current: OUT1, OUT2                                 | 1 A                          |

| Continuous total dissipation                                    | See Dissipation Rating Table |

| Operating free-air temperature range, T <sub>A</sub> : C suffix | –20°C to 85°C                |

| Storage temperature range, T <sub>stq</sub>                     | –65°C to 150°C               |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds    | 260°C                        |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to network GND.

#### DISSIPATION RATING TABLE

| PACKAGE | $T_{\mbox{$A$}} \leq 25^{\circ}\mbox{$C$}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|---------------------------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|

| D       | 950 mW                                                  | 7.6 mW/°C                                      | 608 mW                                | 494 mW                                |

| DB      | 1000 mW                                                 | 8.0 mW/°C                                      | 640 mW                                | 520 mW                                |

| N       | 1250 mW                                                 | 10.0 mW/°C                                     | 800 mW                                | 650 mW                                |

| NS      | 1953 mW                                                 | 15.6 mW/°C                                     | 1250 mW                               | 1015 mW                               |

| PW      | 500 mW                                                  | 4.0 mW/°C                                      | 320 mW                                | 260 mW                                |

### TL1454A, TL1454AY DUAL-CHANNEL PULSE-WIDTH-MODULATION (PWM) CONTROL CIRCUIT

SLVS423 A- MAY 2002 - REVISED SEPTEMBER 2002

#### recommended operating conditions

|                                           |          | MIN  | MAX  | UNIT |

|-------------------------------------------|----------|------|------|------|

| Supply voltage, V <sub>CC</sub>           |          | 3.6  | 20   | V    |

| Error amplifier common-mode input voltage |          | -0.2 | 1.45 | V    |

| Output voltage, VO                        |          |      | 20   | V    |

| Output current, IO                        |          |      | ±40  | mA   |

| COMP source current                       |          |      | -45  | μΑ   |

| COMP sink current                         |          |      | 100  | μΑ   |

| Reference output current                  |          |      | 1    | mA   |

| COMP dc load resistance                   |          | 100  |      | kΩ   |

| Timing capacitor, C <sub>T</sub>          |          | 10   | 4000 | pF   |

| Timing resistor, R <sub>T</sub>           |          | 5.1  | 100  | kΩ   |

| Oscillator frequency                      |          | 50   | 2000 | kHz  |

| Operating free-air temperature, TA        | TL1454AC | -20  | 85   | °C   |

# electrical characteristics over recommended operating free-air temperature range, $V_{CC}$ = 6 V, $f_{osc}$ = 500 kHz (unless otherwise noted)

#### reference

|      | DADAMETED                                 | TEST SONDIT                                  | TONO.                 | 1     | UNIT  |      |      |

|------|-------------------------------------------|----------------------------------------------|-----------------------|-------|-------|------|------|

|      | PARAMETER                                 | TEST CONDIT                                  | IONS                  | MIN   | TYP   | MAX  | UNII |

| V    | Output wells as DEE                       | $I_O = 1 \text{ mA},$                        | T <sub>A</sub> = 25°C | 1.22  | 1.26  | 1.32 | .,   |

| Vref | /ref Output voltage, REF Input regulation | $I_O = 1 \text{ mA}$                         |                       | 1.20  |       | 1.34 | V    |

|      | Input regulation                          | $V_{OC} = 3.6 \text{ V to } 20 \text{ V},$   | $I_O = 1 \text{ mA}$  |       | 2     | 6    | mV   |

|      | Output regulation                         | I <sub>O</sub> = 0.1 mA to 1 mA              |                       |       | 1     | 7.5  | mV   |

|      | Output valtage change with temperature    | $T_A = T_{A(min)}$ to 25°C,                  | $I_O = 1 \text{ mA}$  | -12.5 | -1.25 | 12.5 | \/   |

|      | Output voltage change with temperature    | $T_A = 25^{\circ}C \text{ to } 85^{\circ}C,$ | $I_O = 1 \text{ mA}$  | -12.5 | -2.5  | 12.5 | mV   |

| los  | Short-circuit output current              | V <sub>ref</sub> = 0 V                       |                       |       | 30    |      | mA   |

#### undervoltage lockout (UVLO)

|                  | DADAMETED                                       | TEST COMPITIONS       | TL1454A |     |     | LINUT |

|------------------|-------------------------------------------------|-----------------------|---------|-----|-----|-------|

|                  | PARAMETER                                       | TEST CONDITIONS       | MIN     | TYP | MAX | UNIT  |

| VIT+             | Positive-going threshold voltage                |                       |         | 2.9 |     | V     |

| VIT-             | Negative-going threshold voltage                | T <sub>A</sub> = 25°C |         | 2.7 |     | V     |

| V <sub>hys</sub> | Hysteresis, V <sub>IT+</sub> - V <sub>IT-</sub> |                       | 100     | 200 |     | mV    |

#### short-circuit protection (SCP)

|                          | DADAMETED                    | TEST SOMBITIONS                        | TL1454A |     |      |      |

|--------------------------|------------------------------|----------------------------------------|---------|-----|------|------|

|                          | PARAMETER                    | TEST CONDITIONS                        | MIN     | TYP | MAX  | UNIT |

| VIT                      | Input threshold voltage      | T <sub>A</sub> = 25°C                  | 0.93    | 1   | 1.07 | V    |

| v <sub>stby</sub> †      | Standby voltage              | N. a. a. allana                        | 140     | 185 | 230  | mV   |

| V <sub>I</sub> (latched) | Latched-mode input voltage   | No pullup                              |         | 60  | 120  | mV   |

| VIT(COMP)                | Comparator threshold voltage | COMP1, COMP2                           |         | 1   |      | V    |

|                          | Input source current         | $T_A = 25^{\circ}C$ , $V_{O(SCP)} = 0$ | -5      | -15 | -20  | μΑ   |

<sup>&</sup>lt;sup>†</sup> This symbol is not presently listed within EIA/JEDEC standards for semiconductor symbology.

# TL1454A, TL1454AY DUAL-CHANNEL PULSE-WIDTH-MODULATION (PWM) CONTROL CIRCUIT SLVS423 A- MAY 2002 - REVISED SEPTEMBER 2002

electrical characteristics over recommended operating free-air temperature range,  $V_{CC}$  = 6 V,  $f_{osc}$  = 500 kHz (unless otherwise noted) (continued)

#### oscillator

|      | DARAMETER                            | TEST SOND                                  | TEST CONDITIONS            |     | TL1454A |     |       |

|------|--------------------------------------|--------------------------------------------|----------------------------|-----|---------|-----|-------|

|      | PARAMETER                            | TEST CONDITIONS                            |                            | MIN | TYP     | MAX | UNIT  |

| fosc | Frequency                            | $C_T = 120 \text{ pF},$                    | $R_T = 10 \text{ k}\Omega$ |     | 500     |     | kHz   |

|      | Standard deviation of frequency      |                                            |                            |     | 50      |     | kHz   |

|      | Frequency change with voltage        | $V_{CC} = 3.6 \text{ V to } 20 \text{ V},$ | T <sub>A</sub> = 25°C      |     | 10      |     | kHz   |

|      | Francisco de como cráth tomo quetoro | $T_A = T_{A(min)}$ to 25°C                 |                            |     | -2      | ±30 | 1.11= |

|      | Frequency change with temperature    | T <sub>A</sub> = 25°C to 85°C              |                            |     | -10     | ±30 | kHz   |

|      | Maximum ramp voltage                 |                                            |                            |     | 1.8     |     | V     |

|      | Minimum ramp voltage                 |                                            |                            |     | 1.1     |     | V     |

#### dead-time control (DTC)

|                          | 2424455                                 | T-07 0011710110       | Т    |      |      |      |

|--------------------------|-----------------------------------------|-----------------------|------|------|------|------|

|                          | PARAMETER                               | TEST CONDITIONS       | MIN  | TYP  | MAX  | UNIT |

| .,                       | V <sub>IT</sub> Input threshold voltage | Duty cycle = 0%       | 0.98 | 1.1  | 1.22 | .,   |

| VIT                      |                                         | Duty cycle = 100%     | 0.38 | 0.5  | 0.62 | V    |

| V <sub>I</sub> (latched) | Latched-mode input voltage              |                       |      | 1.2  |      | V    |

| I <sub>IB</sub>          | Common-mode input bias current          | DTC1, IN1+ ≈ 1.2 V    |      |      | 4    | μΑ   |

|                          | Latched-mode (source) current           | T <sub>A</sub> = 25°C |      | -100 |      | μΑ   |

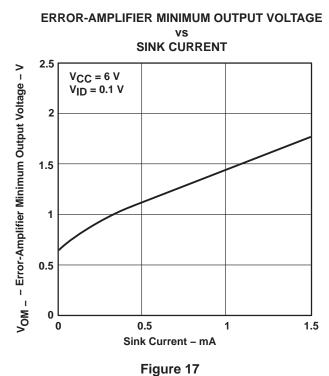

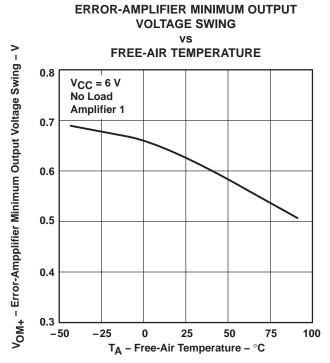

#### error-amplifier

|                  | 24244555                      | TEST SOUDITIONS                                         | TL1454A      |      |      |      |

|------------------|-------------------------------|---------------------------------------------------------|--------------|------|------|------|

|                  | PARAMETER                     | TEST CONDITIONS                                         | MIN          | TYP  | MAX  | UNIT |

| V <sub>IO</sub>  | Input offset voltage          |                                                         |              |      | 6    | mV   |

| I <sub>IO</sub>  | Input offset current          | $V_O = 1.25 \text{ V},  V_{IC} = 1.25 \text{ V}$        |              |      | 100  | nA   |

| I <sub>IB</sub>  | Input bias current            |                                                         |              | -160 | -500 | nA   |

| VICR             | Input voltage range           | V <sub>CC</sub> = 3.6 V to 20 V                         | -0.2 to 1.40 |      |      | V    |

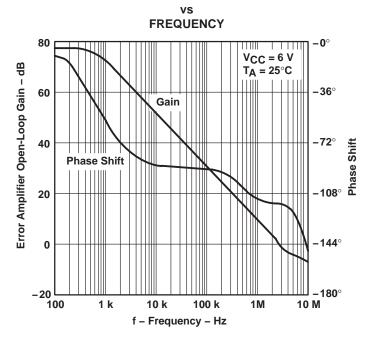

| Ay               | Open-loop voltage gain        | $R_{FB} = 200 \text{ k}\Omega$                          | 70           | 80   |      | dB   |

|                  | Unity-gain bandwidth          |                                                         |              | 3    |      | MHz  |

| CMRR             | Common-mode rejection ratio   |                                                         | 60           | 80   |      | dB   |

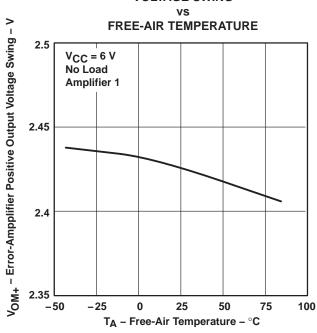

| VOM(max)         | Positive output voltage swing |                                                         | 2.3          | 2.43 |      | .,   |

| VOM(min)         | Negative output voltage swing |                                                         |              | 0.63 | 0.8  | V    |

| I <sub>O+</sub>  | Output sink current           | $V_{ID} = -0.1 \text{ V},  V_{O} = 1.20 \text{ V}$      | 0.1          | 0.5  | ·    | mA   |

| I <sub>O</sub> - | Output source current         | $V_{ID} = 0.1 \text{ V}, \qquad V_{O} = 1.80 \text{ V}$ | -45          | -70  |      | μΑ   |

#### output

|                 | DADAMETER                    | TEST CONDITIONS                                   | TL14                   |     |     |      |

|-----------------|------------------------------|---------------------------------------------------|------------------------|-----|-----|------|

|                 | PARAMETER                    | TEST CONDITIONS                                   | MIN                    | TYP | MAX | UNIT |

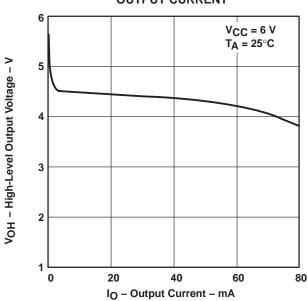

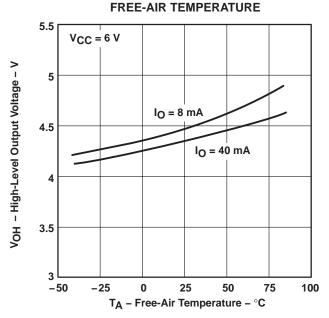

|                 |                              | $I_O = -8 \text{ mA}$                             | V <sub>CC</sub> -2     | 4.5 |     |      |

|                 | OH High-level output voltage | $I_O = -8 \text{ mA } @ V_{CC} = >10 \text{ V}$   | V <sub>CC</sub> -2.3 V |     |     | .,   |

| VOH             |                              | $I_O = -40 \text{ mA}$                            | V <sub>CC</sub> -2     | 4.4 |     | V    |

|                 |                              | $I_O = 40 \text{ mA } @ V_{CC} = >10 \text{ V}$   | V <sub>CC</sub> -2.3 V |     |     |      |

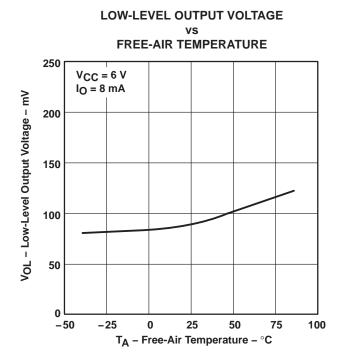

| .,              |                              | IO = 8 mA                                         |                        | 0.1 | 0.4 | .,   |

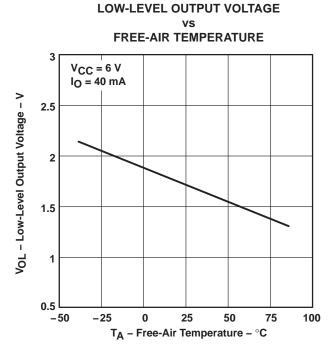

| VOL             | Low-level output voltage     | I <sub>O</sub> = 40 mA                            |                        | 1.8 | 2.5 | V    |

| t <sub>rv</sub> | Output voltage rise time     | C. 2000 T. T. 25°C                                |                        | 220 |     | 20   |

| t <sub>fV</sub> | Output voltage fall time     | $C_L = 2000 \text{ pF}, T_A = 25^{\circ}\text{C}$ |                        | 220 |     | ns   |

# TL1454A, TL1454AY DUAL-CHANNEL PULSE-WIDTH-MODULATION (PWM) CONTROL CIRCUIT

SLVS423 A- MAY 2002 - REVISED SEPTEMBER 2002

electrical characteristics over recommended operating free-air temperature range,  $V_{CC}$  = 6 V,  $f_{osc}$  = 500 kHz (unless otherwise noted) (continued)

#### supply current

|              | DADAMETED              | TEST CONDITIONS                                                                  |     | TL1454A |     |      |

|--------------|------------------------|----------------------------------------------------------------------------------|-----|---------|-----|------|

|              | PARAMETER              | TEST CONDITIONS                                                                  | MIN | TYP     | MAX | UNIT |

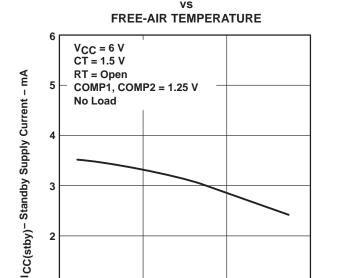

| ICC(stby)    | Standby supply current | RT open, CT = 1.5 V, No load, V <sub>O</sub> (COMP1, COMP2) = 1.25 V,            |     | 3.1     | 6   | mA   |

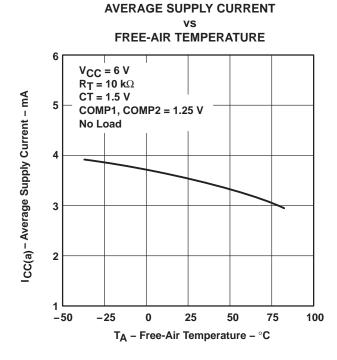

| ICC(average) | Average supply current | $R_T = 10 \text{ k}\Omega,$ $C_T = 120 \text{ pF},$ 50% duty cycle, Outputs open |     | 3.5     | 7   | mA   |

# electrical characteristics, $V_{CC}$ = 6 V, $f_{osc}$ = 500 kHz, $T_A$ = 25°C (unless otherwise noted)

#### reference

|                  | DADAMETED                              | TEST SOMBITIONS                                                        | TL1   |      |     |      |

|------------------|----------------------------------------|------------------------------------------------------------------------|-------|------|-----|------|

|                  | PARAMETER                              | TEST CONDITIONS                                                        | MIN   | TYP  | MAX | UNIT |

| V <sub>ref</sub> | Output voltage, REF                    | $I_O = 1 \text{ mA}$                                                   |       | 1.26 |     | V    |

|                  | Input regulation                       | $V_{OC} = 3.6 \text{ V to } 20 \text{ V}, \qquad I_{O} = 1 \text{ mA}$ |       | 2    |     | mV   |

|                  | Output regulation                      | $I_O = 0.1 \text{ mA to } 1 \text{ mA}$                                |       | 1    |     | mV   |

|                  | Output voltage change with temperature | $I_O = 1 \text{ mA}$                                                   | -1.25 |      |     | mV   |

|                  | Output voltage change with temperature | $I_O = 1 \text{ mA}$                                                   |       | -2.5 |     | IIIV |

| los              | Short-circuit output current           | V <sub>ref</sub> = 0 V                                                 |       | 30   |     | mA   |

#### undervoltage lockout (UVLO)

|                  | 242445752                                      | TEST COMPLETIONS | TI  |     |     |      |

|------------------|------------------------------------------------|------------------|-----|-----|-----|------|

| PARAMETER        |                                                | TEST CONDITIONS  | MIN | TYP | MAX | UNIT |

| V <sub>IT+</sub> | Positive-going threshold voltage               |                  |     | 2.9 |     | V    |

| VIT-             | Negative-going threshold voltage               | 7                |     | 2.7 |     | V    |

| V <sub>hys</sub> | Hysteresis, V <sub>IT+</sub> - V <sub>IT</sub> | 7                |     | 200 |     | mV   |

#### short-circuit protection (SCP)

|                     | DARAMETER                    | TEGT CONDITIONS | TL  |     |     |      |

|---------------------|------------------------------|-----------------|-----|-----|-----|------|

| PARAMETER           |                              | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

| VIT                 | Input threshold voltage      |                 |     | 1   |     | V    |

| v <sub>stby</sub> † | Standby voltage              | No pullup       |     | 185 |     | mV   |

| VI(latched)         | Latched-mode input voltage   | No pullup       |     | 60  |     | mV   |

| VIT(COMP)           | Comparator threshold voltage | COMP1, COMP2    |     | 1   |     | V    |

|                     | Input source current         | $V_O(SCP) = 0$  |     | -15 |     | μΑ   |

<sup>†</sup> This symbol is not presently listed within EIA/JEDEC standards for semiconductor symbology.

#### oscillator

|      | DADAMETER                            | TEGT CONDITIONS                                         | TL1454AY    |       |

|------|--------------------------------------|---------------------------------------------------------|-------------|-------|

|      | PARAMETER                            | TEST CONDITIONS                                         | MIN TYP MAX | UNIT  |

| fosc | Frequency                            | $C_T = 120 \text{ pF}, \qquad R_T = 10 \text{ k}\Omega$ | 500         | kHz   |

|      | Standard deviation of frequency      |                                                         | 50          | kHz   |

|      | Frequency change with voltage        | V <sub>CC</sub> = 3.6 V to 20 V                         | 10          | kHz   |

|      | Francisco de anno vitto tanno antico | $T_A = T_{A(min)}$ to $25^{\circ}C$                     | -2          | 1-11- |

|      | Frequency change with temperature    | $T_A = 25^{\circ}C \text{ to } 85^{\circ}C$             | -10         | kHz   |

|      | Maximum ramp voltage                 |                                                         | 1.8         | V     |

|      | Minimum ramp voltage                 |                                                         | 1.1         | V     |

# TL1454A, TL1454AY DUAL-CHANNEL PULSE-WIDTH-MODULATION (PWM) CONTROL CIRCUIT SLVS423 A- MAY 2002 - REVISED SEPTEMBER 2002

# electrical characteristics, $V_{CC}$ = 6 V, $f_{OSC}$ = 500 kHz, $T_A$ = 25°C (unless otherwise noted) (continued) dead-time control (DTC)

|                         | DADAMETER                     | TEST SOUDITIONS   | TL  |      |     |      |

|-------------------------|-------------------------------|-------------------|-----|------|-----|------|

| PARAMETER               |                               | TEST CONDITIONS   | MIN | TYP  | MAX | UNIT |

| \/                      | Input threshold voltage       | Duty cycle = 0%   |     | 1.1  |     | .,   |

| VIT                     |                               | Duty cycle = 100% |     | 0.5  |     | V    |

| V <sub>I(latched)</sub> | Latched-mode input voltage    |                   |     | 1.2  |     | V    |

|                         | Latched-mode (source) current |                   |     | -100 |     | μΑ   |

#### error-amplifier

|                      | DADAMETED                     | TEOT 04                        | NIDITIONS                | TL  | ,    |     |      |

|----------------------|-------------------------------|--------------------------------|--------------------------|-----|------|-----|------|

|                      | PARAMETER                     | TEST CC                        | ONDITIONS                | MIN | TYP  | MAX | UNIT |

| I <sub>IB</sub>      | Input bias current            | V <sub>O</sub> = 1.25 V,       | V <sub>IC</sub> = 1.25 V |     | -160 |     | nA   |

| Ay                   | Open-loop voltage gain        | $R_{FB} = 200 \text{ k}\Omega$ |                          |     | 80   |     | dB   |

|                      | Unity-gain bandwidth          |                                |                          |     | 3    |     | MHz  |

| CMRR                 | Common-mode rejection ratio   |                                |                          |     | 80   |     | dB   |

| V <sub>OM(max)</sub> | Positive output voltage swing |                                |                          |     | 2.43 |     | V    |

| VOM(min)             | Negative output voltage swing |                                |                          |     | 0.63 |     | V    |

| I <sub>O+</sub>      | Output sink current           | $V_{ID} = -0.1 V$ ,            | V <sub>O</sub> = 1.20 V  |     | 0.5  |     | mA   |

| IO-                  | Output source current         | $V_{ID} = 0.1 V$ ,             | V <sub>O</sub> = 1.80 V  |     | -70  |     | μΑ   |

#### output

|                 | PARAMETER                                                  | TEST SOURITIONS          | Τι  | TL1454AY |     |      |  |  |  |

|-----------------|------------------------------------------------------------|--------------------------|-----|----------|-----|------|--|--|--|

|                 | PARAMETER                                                  | TEST CONDITIONS          | MIN | TYP      | MAX | UNIT |  |  |  |

| V               | High-level output voltage                                  | IO = -8  mA              |     | 4.5      |     |      |  |  |  |

| VOH             |                                                            | $I_O = -40 \text{ mA}$   |     | 4.4      |     |      |  |  |  |

| ,,              | Law law law and a self-self-self-self-self-self-self-self- | I <sub>O</sub> = 8 mA    |     | 0.1      |     |      |  |  |  |

| VOL             | Low-level output voltage                                   | I <sub>O</sub> = 40 mA   |     | V        |     |      |  |  |  |

| t <sub>rv</sub> | Output voltage rise time                                   | C. 2000 pF               |     | 220      |     |      |  |  |  |

| tfV             | Output voltage fall time                                   | C <sub>L</sub> = 2000 pF |     | 220      |     | ns   |  |  |  |

#### supply current

|              | DADAMETED              | TEST COMPLIANC                                                                   | TL  | LINUT |     |      |

|--------------|------------------------|----------------------------------------------------------------------------------|-----|-------|-----|------|

|              | PARAMETER              | TEST CONDITIONS                                                                  | MIN | TYP   | MAX | UNIT |

| ICC(stby)    | Standby supply current | RT open, CT = 1.5 V, No load, V <sub>O</sub> (COMP1, COMP2) = 1.25 V,            |     | 3.1   |     | mA   |

| ICC(average) | Average supply current | $R_T = 10 \text{ k}\Omega,$ $C_T = 120 \text{ pF},$ 50% duty cycle, Outputs open |     | 3.5   |     | mA   |

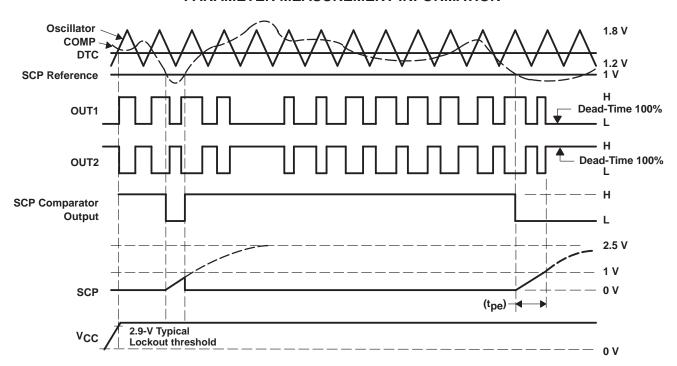

#### PARAMETER MEASUREMENT INFORMATION

Figure 5. Timing Diagram

**OSCILLATOR PERIOD**

#### TYPICAL CHARACTERISTICS

**TIMING CAPACITANCE** 102 V<sub>CC</sub> = 6 V  $R_T = 5.1 \text{ k}\Omega$ T<sub>A</sub> = 25°C t - Oscillation Period -  $\mu$ s 101 10<sup>0</sup> 10 - 1100 101 102 103 104 105 C<sub>T</sub> - Timing Capacitance - pF

Figure 6

PWM TRIANGLE WAVEFORM AMPLITUDE vs

Figure 7

Figure 8 Figure 9

# DTC INPUT THRESHOLD VOLTAGE FREE-AIR TEMPERATURE $V_{CC} = 6 V$ $R_T = 5.1 \text{ k}\Omega$ $C_T = 1000 pF$ 1.2 DTC Input Threshold Voltage - V V<sub>IT</sub> (0% Duty Cycle) 0.8 0.6 VIT (100% Duty Cycle) 0.4 50 100 -50 $T_A$ – Free-Air Temperature – $^{\circ}C$

Figure 10

Figure 12

Figure 11

Figure 13

**DUTY CYCLE**

#### **TYPICAL CHARACTERISTICS**

40 20 0 0.25 0 Figure 14

**ERROR-AMPLIFIER MAXIMUM OUTPUT VOLTAGE** vs **SOURCE CURRENT** V<sub>OM+</sub> - Error-Amplifier Maximum Output Voltage - V 2.5 V<sub>CC</sub> = 6 V V<sub>ID</sub> = 0.1 V  $T_A = 25^{\circ}C$ 2 1.5 1 0.5 0 80 120 0 40 Source Current - µA

Figure 16

## **ERROR AMPLIFIER MAXIMUM** PEAK-TO-PEAK OUTPUT VOLTAGE SWING vs **FREQUENCY** 2.5 $V_{CC} = 6 V$ Vo(PP) - Error Amplifier Maximum Peak-to-Peak Output Voltage Swing - V TA = 25°C 1.5 0.5 10 k 100 k 1M 10 M 100 M 1 k f - Frequency - Hz

Figure 18 Figure 19

#### ERROR AMPLIFIER OPEN-LOOP GAIN AND PHASE SHIFT

Figure 20

# ERROR-AMPLIFIER POSITIVE OUTPUT VOLTAGE SWING

Figure 21

#### HIGH-LEVEL OUTPUT VOLTAGE

#### vs OUTPUT CURRENT

Figure 22

#### HIGH-LEVEL OUTPUT VOLTAGE

#### VS

Figure 23

#

Figure 24

Figure 26

Figure 25

Figure 27

## STANDBY SUPPLY CURRENT **SUPPLY VOLTAGE** VCC = 6 VRT = Open CT = 1.5 V ICC(stby) - Standby Supply Current - mA **COMP1, COMP2 = 1.25 V** No Load T<sub>A</sub> = 25°C 3 2 5 0 15 20 25 10

Figure 28

V<sub>CC</sub> - Supply Voltage - V

Figure 30

STANDBY SUPPLY CURRENT

Figure 29

T<sub>A</sub> - Free-Air Temperature - °C

50

100

0

- 50

Figure 31

# REFERENCE VOLTAGE vs FREE-AIR TEMPERATURE

Figure 32

www.ti.com 11-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/        | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|---------------|--------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | Ball material | Peak reflow        |              | (6)          |

|                       |        |               |                 |                       |      | (4)           | (5)                |              |              |

| TL1454ACD             | Active | Production    | SOIC (D)   16   | 40   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | -20 to 85    | TL1454AC     |

| TL1454ACD.A           | Active | Production    | SOIC (D)   16   | 40   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | -20 to 85    | TL1454AC     |

| TL1454ACDBR           | Active | Production    | SSOP (DB)   16  | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -20 to 85    | T1454A       |

| TL1454ACDBR.A         | Active | Production    | SSOP (DB)   16  | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -20 to 85    | T1454A       |

| TL1454ACN             | Active | Production    | PDIP (N)   16   | 25   TUBE             | Yes  | NIPDAU        | N/A for Pkg Type   | -20 to 85    | TL1454ACN    |

| TL1454ACN.A           | Active | Production    | PDIP (N)   16   | 25   TUBE             | Yes  | NIPDAU        | N/A for Pkg Type   | -20 to 85    | TL1454ACN    |

| TL1454ACNSR           | Active | Production    | SOP (NS)   16   | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -20 to 85    | TL1454A      |

| TL1454ACNSR.A         | Active | Production    | SOP (NS)   16   | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -20 to 85    | TL1454A      |

| TL1454ACPW            | Active | Production    | TSSOP (PW)   16 | 90   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | -20 to 85    | T1454A       |

| TL1454ACPW.A          | Active | Production    | TSSOP (PW)   16 | 90   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM | -20 to 85    | T1454A       |

| TL1454ACPWR           | Active | Production    | TSSOP (PW)   16 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -20 to 85    | T1454A       |

| TL1454ACPWR.A         | Active | Production    | TSSOP (PW)   16 | 2000   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM | -20 to 85    | T1454A       |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

#### PACKAGE OPTION ADDENDUM

www.ti.com 11-Nov-2025

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

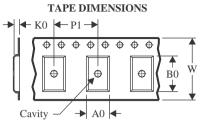

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

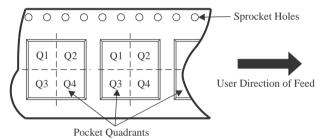

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TL1454ACDBR | SSOP            | DB                 | 16 | 2000 | 330.0                    | 16.4                     | 8.35       | 6.6        | 2.4        | 12.0       | 16.0      | Q1               |

| TL1454ACNSR | SOP             | NS                 | 16 | 2000 | 330.0                    | 16.4                     | 8.1        | 10.4       | 2.5        | 12.0       | 16.0      | Q1               |

| TL1454ACPWR | TSSOP           | PW                 | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

www.ti.com 24-Jul-2025

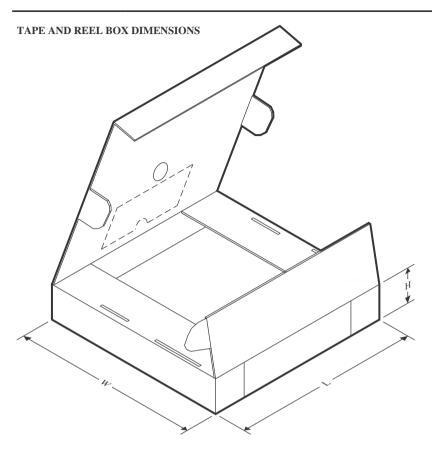

#### \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TL1454ACDBR | SSOP         | DB              | 16   | 2000 | 353.0       | 353.0      | 32.0        |

| TL1454ACNSR | SOP          | NS              | 16   | 2000 | 353.0       | 353.0      | 32.0        |

| TL1454ACPWR | TSSOP        | PW              | 16   | 2000 | 353.0       | 353.0      | 32.0        |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 24-Jul-2025

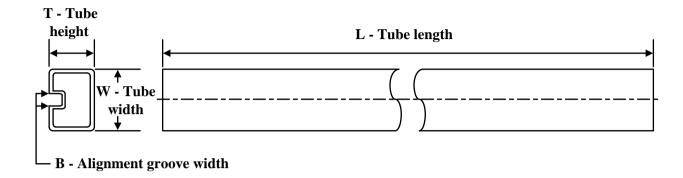

#### **TUBE**

\*All dimensions are nominal

| 7th dimensions are nonlina |              |              |      |     |        |        |        |        |

|----------------------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| Device                     | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

| TL1454ACD                  | D            | SOIC         | 16   | 40  | 507    | 8      | 3940   | 4.32   |

| TL1454ACD                  | D            | SOIC         | 16   | 40  | 505.46 | 6.76   | 3810   | 4      |

| TL1454ACD.A                | D            | SOIC         | 16   | 40  | 507    | 8      | 3940   | 4.32   |

| TL1454ACD.A                | D            | SOIC         | 16   | 40  | 505.46 | 6.76   | 3810   | 4      |

| TL1454ACN                  | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

| TL1454ACN.A                | N            | PDIP         | 16   | 25  | 506    | 13.97  | 11230  | 4.32   |

| TL1454ACPW                 | PW           | TSSOP        | 16   | 90  | 530    | 10.2   | 3600   | 3.5    |

| TL1454ACPW.A               | PW           | TSSOP        | 16   | 90  | 530    | 10.2   | 3600   | 3.5    |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you fully indemnify TI and its representatives against any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale, TI's General Quality Guidelines, or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products. Unless TI explicitly designates a product as custom or customer-specified, TI products are standard, catalog, general purpose devices.

TI objects to and rejects any additional or different terms you may propose.

Copyright © 2025, Texas Instruments Incorporated

Last updated 10/2025