SWAS035C September 2016 – May 2021 CC3220R , CC3220S , CC3220SF

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Functional Block Diagrams

- 5 Revision History

- 6 Device Comparison

- 7 Terminal Configuration and Functions

-

8 Specifications

- 8.1 Absolute Maximum Ratings

- 8.2 ESD Ratings

- 8.3 Power-On Hours (POH)

- 8.4 Recommended Operating Conditions

- 8.5 Current Consumption Summary (CC3220R, CC3220S)

- 8.6 Current Consumption Summary (CC3220SF)

- 8.7 TX Power and IBAT versus TX Power Level Settings

- 8.8 Brownout and Blackout Conditions

- 8.9 Electrical Characteristics (3.3 V, 25°C)

- 8.10 WLAN Receiver Characteristics

- 8.11 WLAN Transmitter Characteristics

- 8.12 WLAN Filter Requirements

- 8.13 Thermal Resistance Characteristics

- 8.14

Timing and Switching Characteristics

- 8.14.1 Power Supply Sequencing

- 8.14.2 Device Reset

- 8.14.3 Reset Timing

- 8.14.4 Wakeup From HIBERNATE Mode

- 8.14.5 Clock Specifications

- 8.14.6

Peripherals Timing

- 8.14.6.1 SPI

- 8.14.6.2 I2S

- 8.14.6.3 GPIOs

- 8.14.6.4 I2C

- 8.14.6.5 IEEE 1149.1 JTAG

- 8.14.6.6 ADC

- 8.14.6.7 Camera Parallel Port

- 8.14.6.8 UART

- 8.14.6.9 SD Host

- 8.14.6.10 Timers

- 9 Detailed Description

- 10Applications, Implementation, and Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RGK|64

Thermal pad, mechanical data (Package|Pins)

- RGK|64

Orderable Information

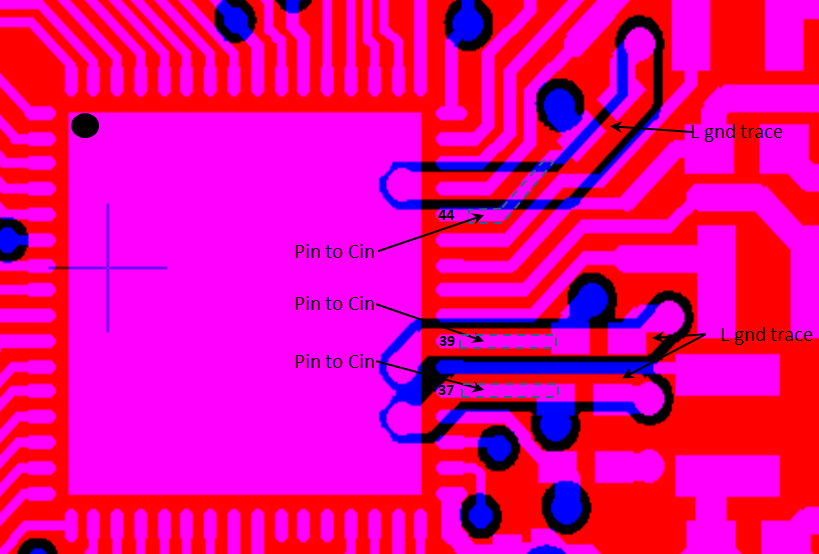

10.2.2.1 Design Considerations

The following design guidelines must be followed when laying out the CC3220x device:

- Route all of the input decoupling capacitors (C11, C13, and C18) on L2 using thick traces, to isolate the RF ground from the noisy supply ground. This step is also required to meet the IEEE spectral mask specifications.

- Maintain the thickness of power traces to be greater than 12 mils. Take special consideration for power amplifier supply lines (pins 33, 40, 41, and 42), and all input supply pins (pins 37, 39, and 44).

- Ensure the shortest grounding loop for the PLL supply decoupling capacitor (pin 24).

- Place all decoupling capacitors as close to the respective pins as possible.

- Power budget: The CC3220x device can consume up to 450 mA for 3.3 V, 670 mA for 2.1 V, and 700 mA for 1.85 V, for 24 ms during the calibration cycle.

- Ensure the power supply is designed to source this current without any issues. The complete calibration (TX and RX) can take up to 17 mJ of energy from the battery over a time of 24 ms.

- The CC3220x device contains many high-current input pins. Ensure the trace feeding these pins is capable of handling the following currents:

- VIN_DCDC_PA input (pin 39) maximum is 1 A

- VIN_DCDC_ANA input (pin 37) maximum is 600 mA

- VIN_DCDC_DIG input (pin 44) maximum is 500 mA

- DCDC_PA_SW_P (pin 40) and DCDC_PA_SW_N (pin 41) switching nodes maximum is 1 A

- DCDC_PA_OUT output node (pin 42) maximum 1 A

- DCDC_ANA_SW switching node (pin 38) maximum is 600 mA

- DCDC_DIG_SW switching node (pin 43) maximum is 500 mA

- VDD_PA_IN supply (pin 33) maximum is 500 mA

Figure 10-3 shows the ground routing for the input decoupling capacitors.

Figure 10-3 Ground Routing for the Input Decoupling Capacitors

Figure 10-3 Ground Routing for the Input Decoupling CapacitorsThe ground return for the input capacitors are routed on L2 to reduce the EMI and improve the spectral mask. This routing must be strictly followed because it is critical for the overall performance of the device.