SBAS649B June 2021 – June 2022 DAC12DL3200

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics - DC Specifications

- 6.6 Electrical Characteristics - Power Consumption

- 6.7 Electrical Characteristics - AC Specifications

- 6.8 Timing Requirements

- 6.9 Switching Characteristics

- 6.10 Typical Characteristics

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 DAC Output Modes

- 7.3.2 DAC Output Interface

- 7.3.3 LVDS Interface

- 7.3.4 Multi-Device Synchronization (SYSREF+/-)

- 7.3.5 Alarms

- 7.4 Device Functional Modes

- 7.5 Programming

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

Orderable Information

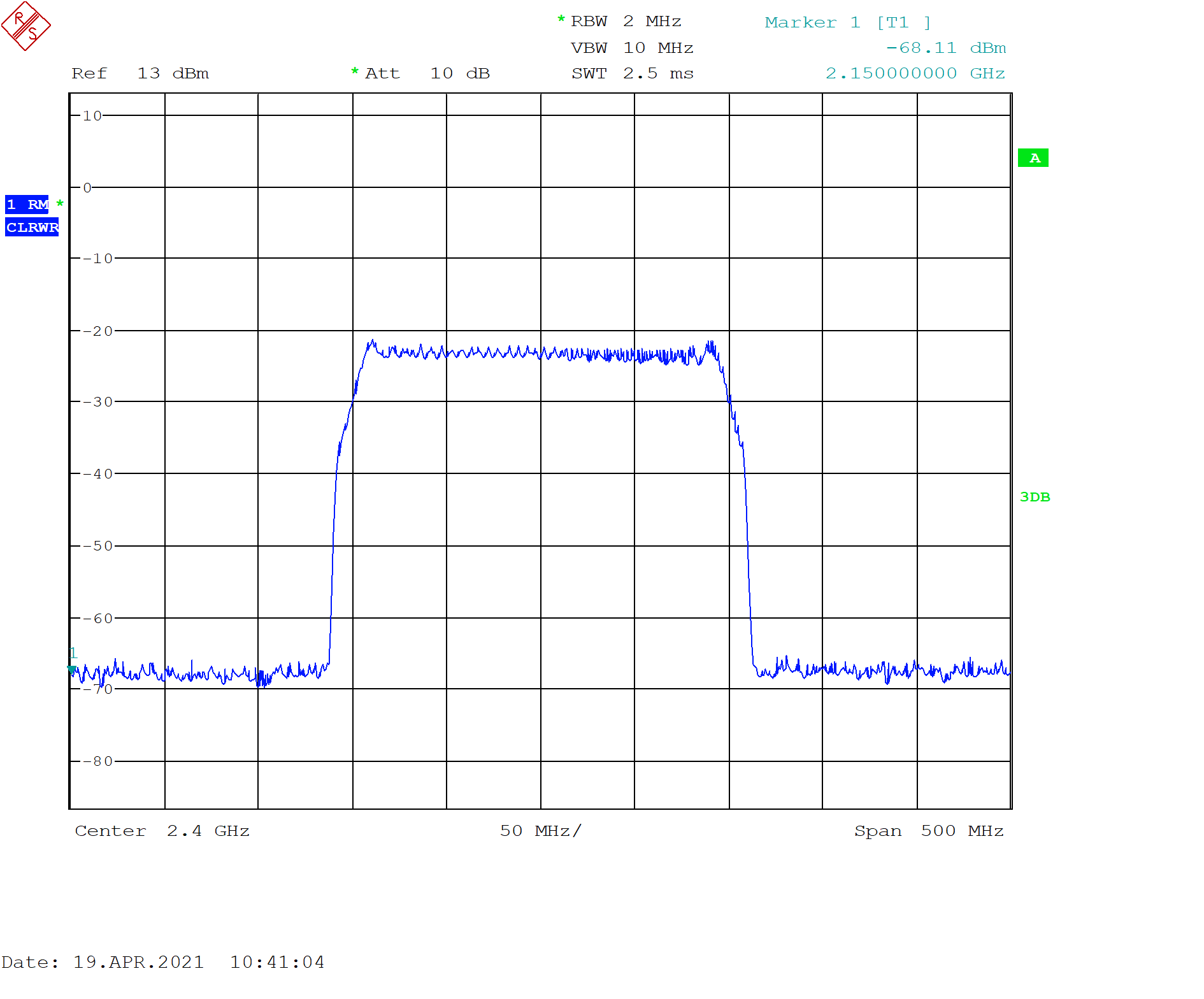

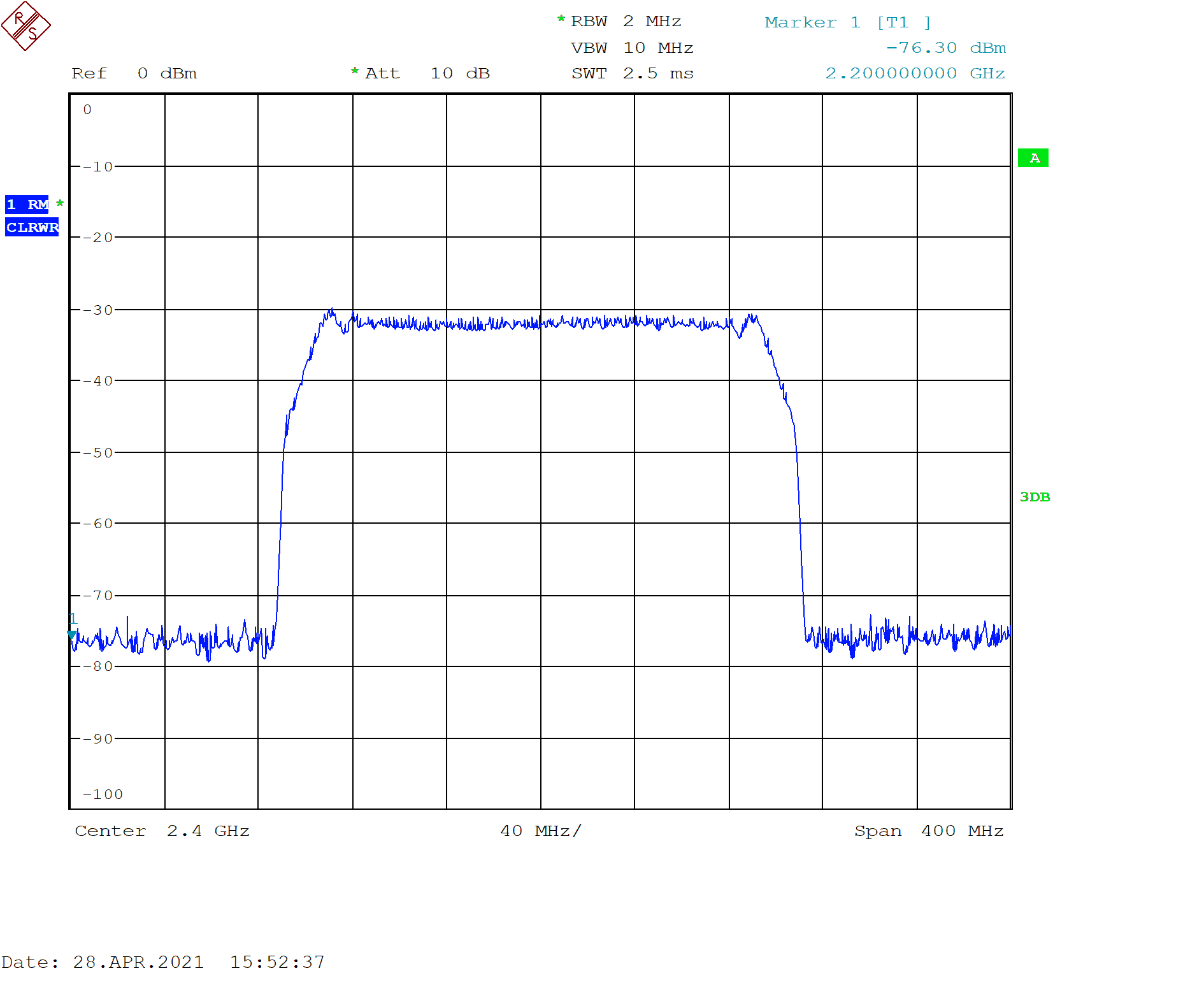

8.2.3 Application Curves

A linear frequency chirp signal with 200 MHz BW, 146.5 MHz/μs and 1.36 μs repetition rate centered at 2.4 GHz was input to the ADC12DL3200. Analog input signal is shown in Figure 8-2. The signal after loopback at the DAC12DL3200 output is shown in Figure 8-3, and matches well the analog input.

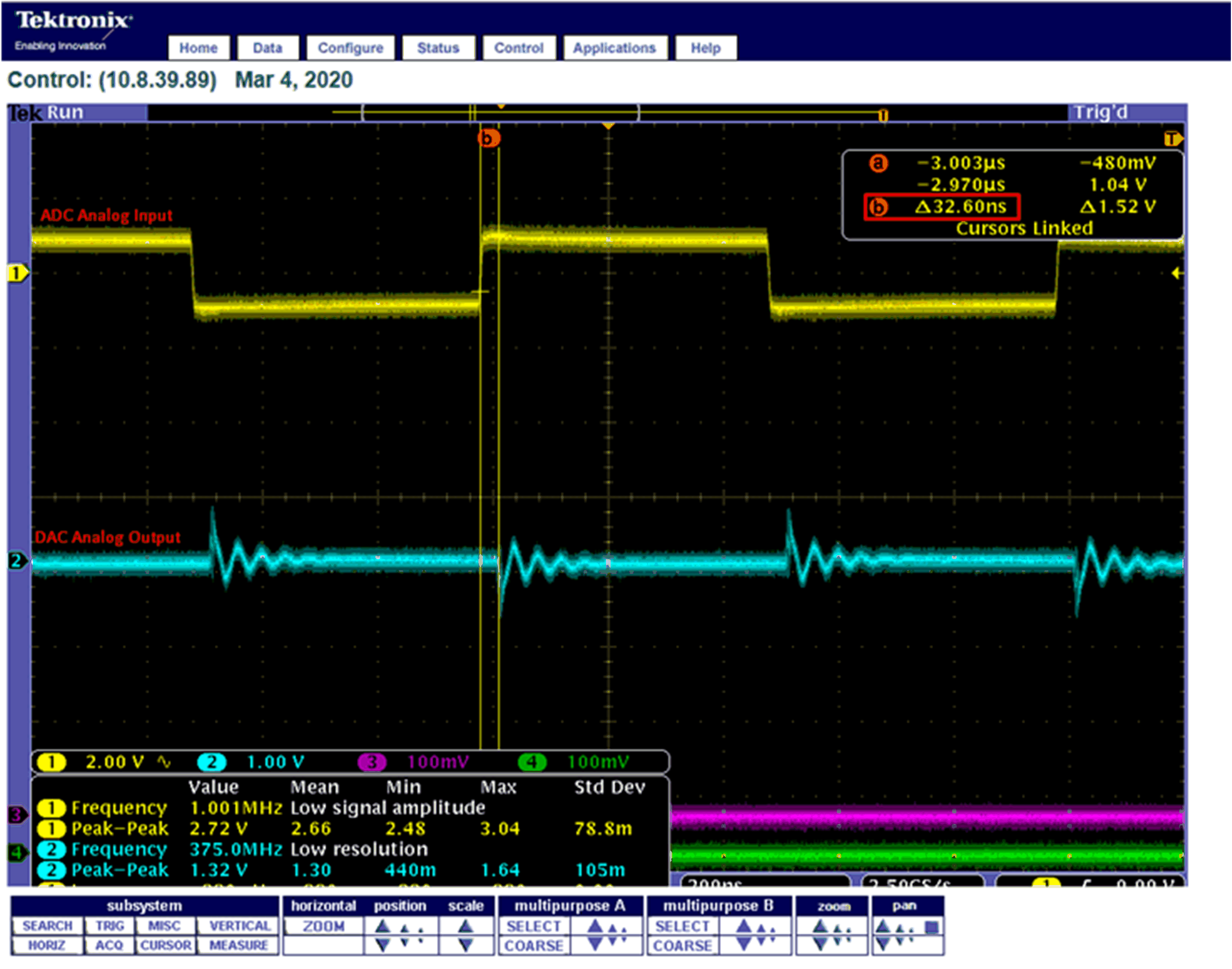

The DAC12DL3200 and ADC12DL3200 latency depend on mode and are 30.5 clock cycles for the DAC and 26 clock cyles for the ADC. At 3.2 GHz, one clock period is 313 ps and therefore the total DAC and ADC latency is 17.7 ns. The latency through the FPGA depends on the FPGA firmware. With significant optimization, a latency of < 20 ns (without signal processing) is possible. To demonstrate an optimized latency, the ADC MSB output was looped back to the DAC MSB input with an latency optimized FPGA firmware. Figure 8-4 shows the ADC input to DAC output, with a latency of 32.6 ns, meeting the system design requirement.