DLPS194A November 2020 – June 2022 DLP670S

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 Storage Conditions

- 6.3 ESD Ratings

- 6.4 Recommended Operating Conditions

- 6.5 Thermal Information

- 6.6 Electrical Characteristics

- 6.7 Capacitance at Recommended Operating Conditions

- 6.8 Timing Requirements

- 6.9 Typical Characteristics

- 6.10 System Mounting Interface Loads

- 6.11 Micromirror Array Physical Characteristics

- 6.12 Micromirror Array Optical Characteristics

- 6.13 Window Characteristics

- 6.14 Chipset Component Usage Specification

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- FYR|350

Thermal pad, mechanical data (Package|Pins)

Orderable Information

10.1.2 Power Connection Guidelines

The following are recommendations for the power connections to the DMD or DMD PCB:

- Solid planes are required for DMD_P3P3V(3.3V), DMD_P1P8V and Ground.

- TI strongly recommends partial power planes are used for VOFFSET, VRESET, and VBIAS.

- VOFFSET, VBIAS, VRESET, VCC, and VCCI power rails must be kept within the specified operating range. This includes effects from ripple and DC error.

- To accommodate power supply transient current requirements, adequate decoupling capacitance must be placed as near the DMD VOFFSET, VBIAS, VRESET, VCC, and VCCI pins as possible.

- Do not swap DMDs while the DMD is still powered on (this is called hot swapping). All DMD power supply rails and signals must be 0 volts (not driven) before connecting or disconnecting the DMD physical interface.

- Do not allow power to be applied to the DMD when one or more signal pins are not being driven.

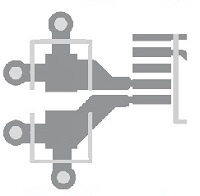

- Decoupling capacitor locations for the DMD must be as close as possible to the DMD. The pads of the capacitors must be connected to at least two or three vias to get a very low impedance to ground as shown in Figure 10-3. Furthermore, the capacitor must be in the flow of the power trace as it goes to the input of the DMD.

- It is extremely important to adhere to the Section 9.1 and Section 9.2 and do not allow the DMD power-supply levels to be outside of the recommended operating conditions specified in the DMD data sheet.

These figures show examples of bypass decoupling capacitor layout.

Figure 10-3 Good Layout

Figure 10-3 Good Layout