SNLS676 May 2022 DP83TC813R-Q1 , DP83TC813S-Q1

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4

Device Functional Modes

- 8.4.1 Power Down

- 8.4.2 Reset

- 8.4.3 Standby

- 8.4.4 Normal

- 8.4.5 Sleep Ack

- 8.4.6 Sleep Request

- 8.4.7 Sleep Fail

- 8.4.8 Sleep

- 8.4.9 Wake-Up

- 8.4.10 TC10 System Example

- 8.4.11 Media Dependent Interface

- 8.4.12 MAC Interfaces

- 8.4.13 Serial Management Interface

- 8.4.14 Direct Register Access

- 8.4.15 Extended Register Space Access

- 8.4.16 Write Address Operation

- 8.4.17 Read Address Operation

- 8.4.18 Write Operation (No Post Increment)

- 8.4.19 Read Operation (No Post Increment)

- 8.4.20 Write Operation (Post Increment)

- 8.4.21 Read Operation (Post Increment)

- 8.5 Programming

- 8.6 Register Maps

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RHF|28

Thermal pad, mechanical data (Package|Pins)

- RHF|28

Orderable Information

11.1.1 Signal Traces

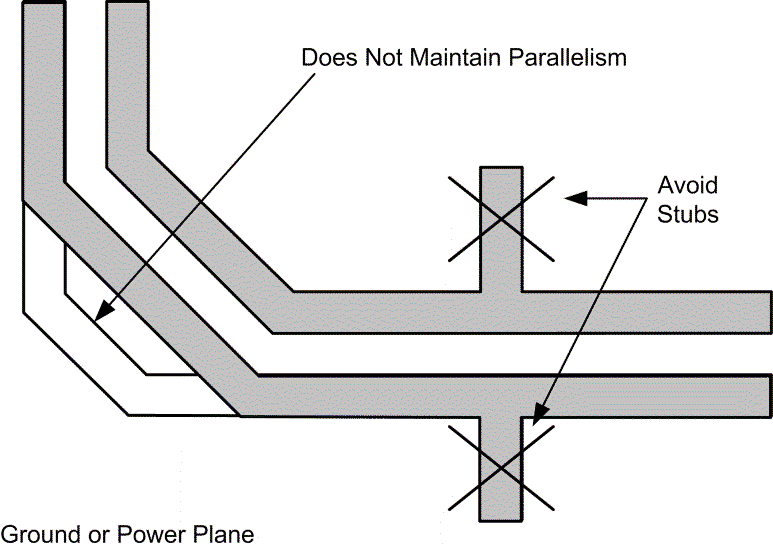

PCB traces are lossy and long traces can degrade signal quality. Traces must be kept short as possible. Unless mentioned otherwise, all signal traces must be 50-Ω, single-ended impedance. Differential traces must be 50-Ω single-ended and 100-Ω differential. Take care to ensure impedance is controlled throughout. Impedance discontinuities will cause reflections leading to emissions and signal integrity issues. Stubs must be avoided on all signal traces, especially differential signal pairs.

Figure 11-1 Differential Signal Trace Routing

Figure 11-1 Differential Signal Trace RoutingWithin the differential pairs, trace lengths must be run parallel to each other and matched in length. Matched lengths minimize delay differences, avoiding an increase in common mode noise and emissions. Length matching is also important for MAC interface connections. All transmit signal traces must be length matched to each other and all receive signal traces must be length matched to each other. For SGMII differential traces, it is recommended to keep the skew mismatch below 20ps.

Ideally, there must be no crossover on signal path traces. High speed signal traces must be routed on internal layers to improved EMC performance. However, vias present impedance discontinuities and must be minimized when possible. Route trace pairs on the same layer. Signals on different layers must not cross each other without at least one return path plane between them. Differential pairs must always have a constant coupling distance between them. For convenience and efficiency, TI recommends routing critical signals first (that is, MDI differential pairs, reference clock, and MAC IF traces).