# LMK3H2104 and LMK3H2108 4- and 8-Output PCle Gen 1-7 Compliant Low Jitter **General Purpose BAW Clock Generator**

#### 1 Features

- Integrated BAW resonator

- No need for external XTAL/XO

- Flexible output frequency

- 2 fraction output dividers (FOD), individual channel dividers

- Up to 400MHz output frequency

- Flexible output format

- 1.2/1.8/2.5/3.3V LVCMOS

- DC- or AC-coupled LVDS

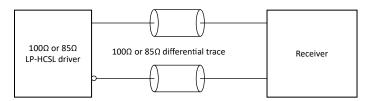

- LP-HCSL with programmable swing. LVPECL, CML and other formats can be derived from LP-HCSL

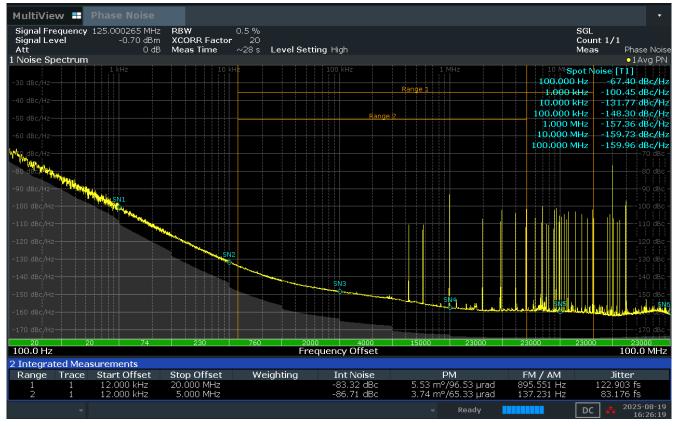

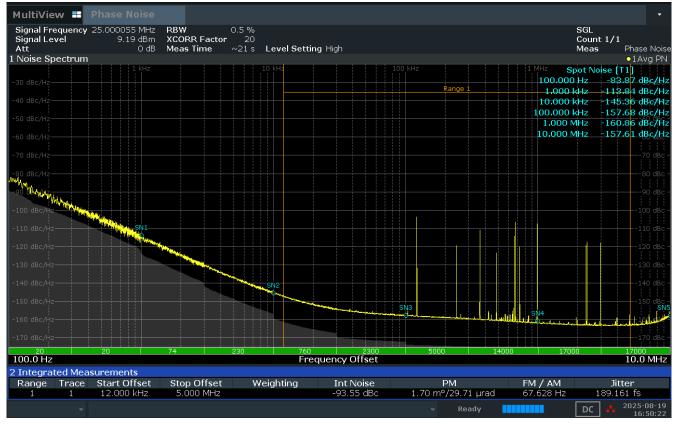

- Very low jitter

- 61fs max PCle Gen 5 CC with SSC jitter

- 36.4fs max PCIe Gen 6 CC with SSC jitter

- 25.5fs max PCle Gen 7 CC with SSC jitter

- PCIe Gen 1 to Gen 7 compliant

- Configurable SSC

- Programmable -0.05% to -3% down spread and ±0.025% to ±1.5% center spread, or preset -0.1%, -0.25%, -0.3% and -0.5% down spread

- 3 inputs (LMK3H2108) or 1 input (LMK3H2104) that can be bypassed to any output

- 5ms max startup time

- Fail-safe input pins can be pulled high when device power is off

- Flexible power supply

- Each VDD pin can be independently connected to = 1.8, 2.5 or 3.3V

- Each VDDO pin can be independently connected set to 1.8, 2.5 or 3.3V

- -40 to 105°C ambient temperature

# 2 Applications

- · High Performance Computing Server Motherboard

- NIC, SmartNIC and Hardware Acceleration

- PCIe Gen 1 to Gen 7 clock generation

- General purpose clock generation and XO/XTAL replacement

## 3 Description

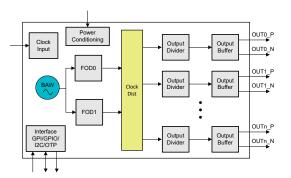

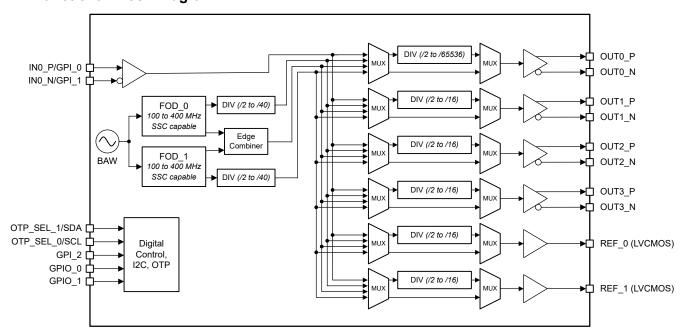

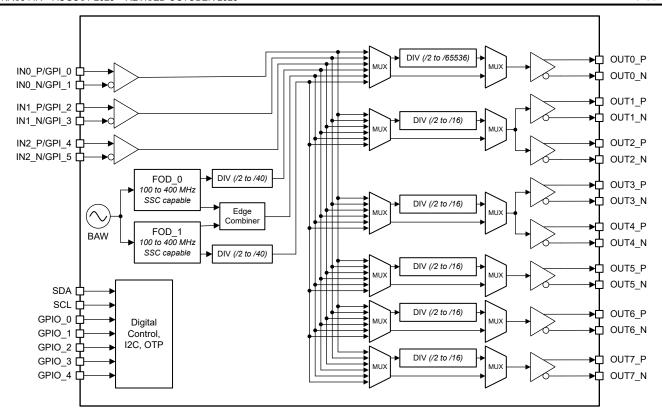

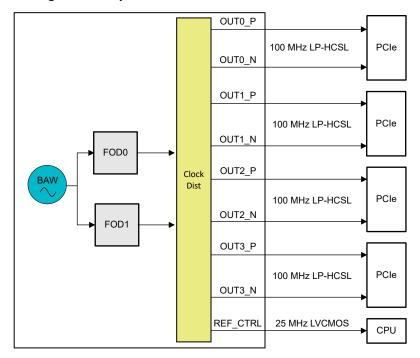

LMK3H2104 and LMK3H2108 are BAW-based clock generators that do not require any external XTAL or XO. The devices can be used as PCIe clock generators or general purpose clock generators. The 2 FODs (Fractional Output Divider) provide frequency flexibility, low power and low jitter at the same time.

LMK3H2104 has up to 4 differential outputs plus 2 LVCMOS outputs or up to 10 LVCMOS outputs. LMK3H2108 has up to 8 differential outputs or 16 LVCMOS outputs.

LMK3H2104 has one clock input and LMK3H2108 has three clock inputs. The clock inputs provide clock multiplexing and buffering ability. Each output bank can independently select any clock source.

The GPI and GPIO pins provide additional control flexibility. These pins can be configured as individual OE, grouped OE, I2C address selection, OTP page selection, PWRGD/PWRDN#, status output and other functions.

The device supports one-time programmable (OTP) non-volatile memory which can be customized and factory preprogrammed.

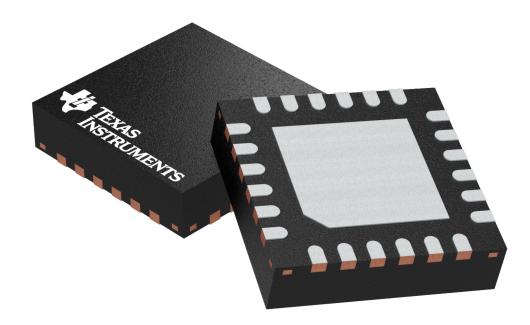

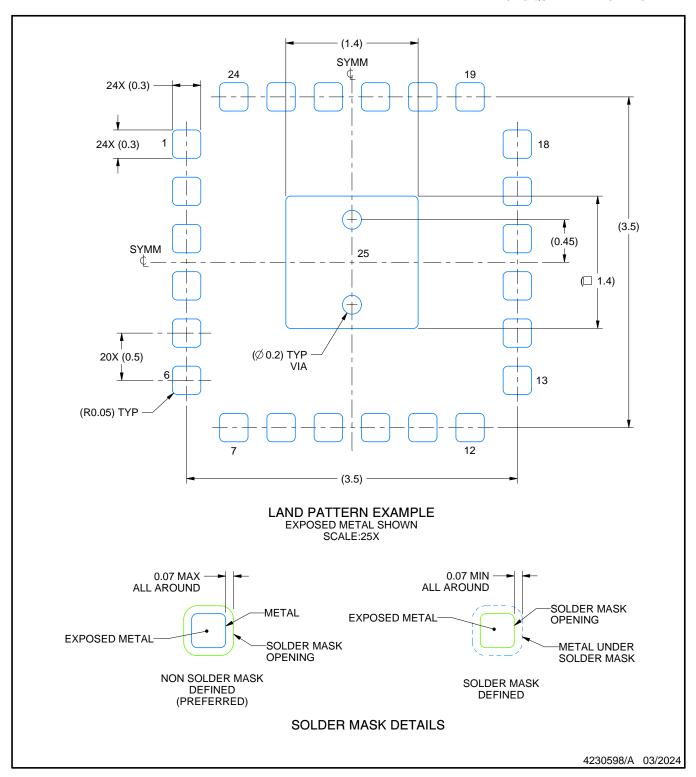

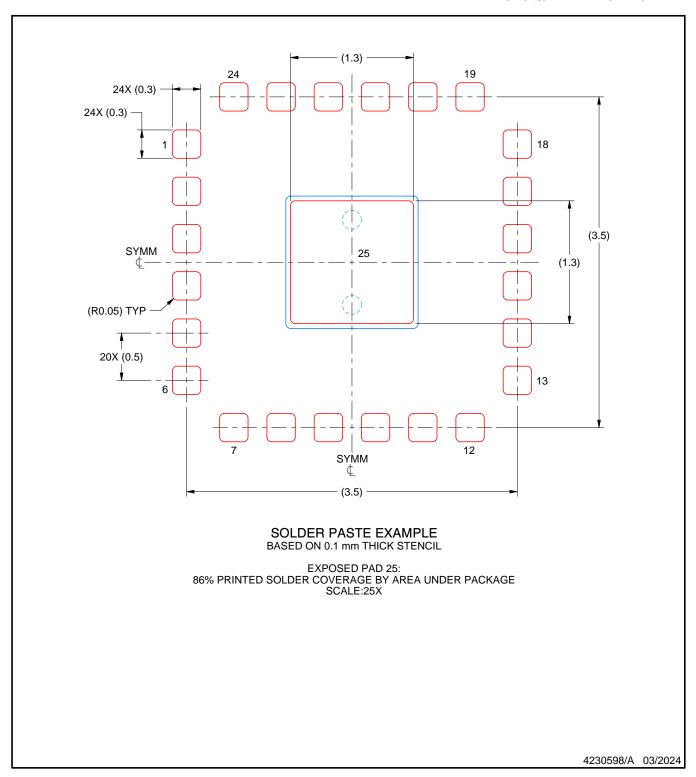

#### **Package Information**

| P  | ART NUMBER |                     | PACKAGE<br>SIZE <sup>(2)</sup> |

|----|------------|---------------------|--------------------------------|

| LN | MK3H2104   | RGE0024AA (QFN, 24) | 4.0mm × 4.0mm                  |

| LN | MK3H2104   | RGE0024AB (QFN, 24) | 4.0mm × 4.0mm                  |

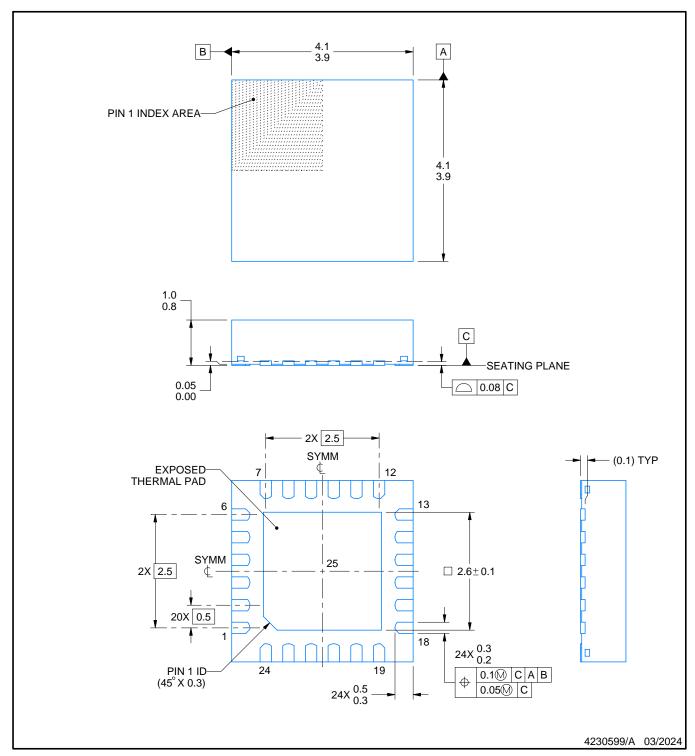

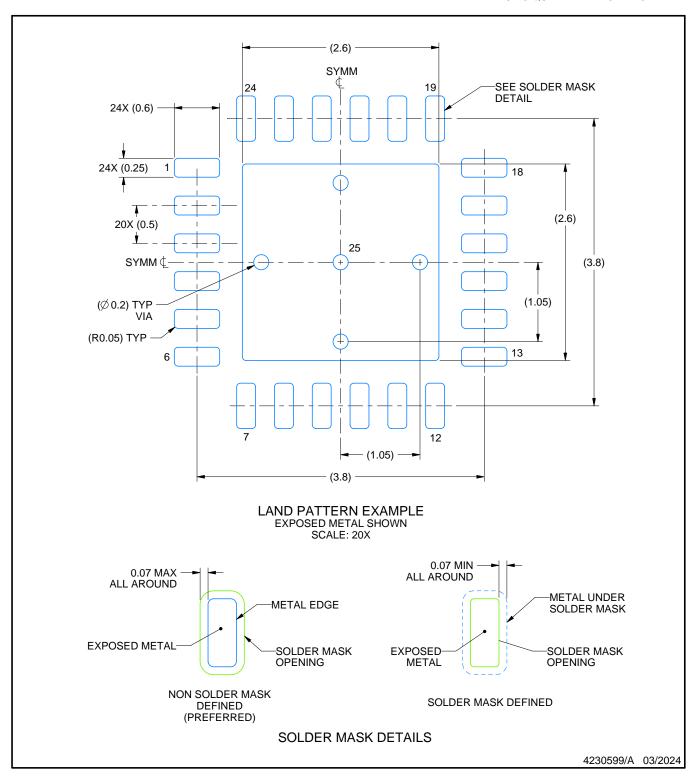

| LN | MK3H2108   | RKP0040A (QFN, 40)  | 5.0mm × 5.0mm                  |

- For more information, see Section 11.

- The package size (length × width) is a nominal value and includes pins, where applicable.

Simplified Block Diagram

# **Table of Contents**

| 1 Features1                            | 7.4 SSC                               | 53 |

|----------------------------------------|---------------------------------------|----|

| 2 Applications1                        | 7.5 Device Functional Modes           |    |

| 3 Description1                         | 7.6 Programming                       |    |

| 4 Pin Configuration and Functions3     |                                       |    |

| 5 Specifications6                      |                                       |    |

| 5.1 Absolute Maximum Ratings6          |                                       |    |

| 5.2 ESD Ratings6                       |                                       |    |

| 5.3 Recommended Operating Conditions6  |                                       |    |

| 5.4 Thermal Information6               |                                       |    |

| 5.5 Electrical Characteristics7        | 9.1 Documentation Support6            | 65 |

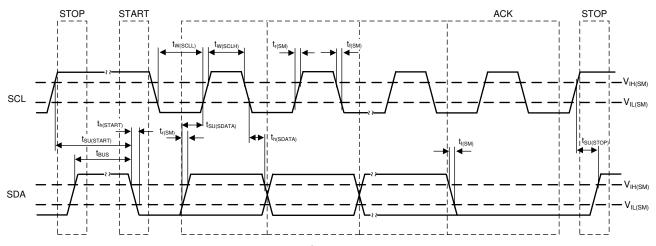

| 5.6 I2C Characteristics23              | ·                                     |    |

| 6 Parameter Measurement Information25  | · · · · · · · · · · · · · · · · · · · |    |

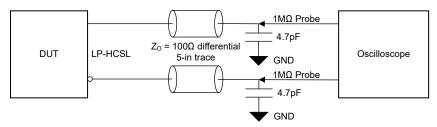

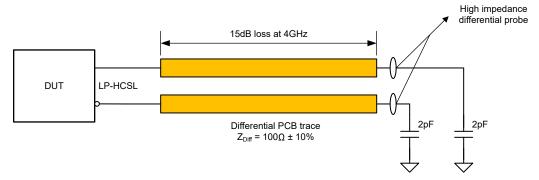

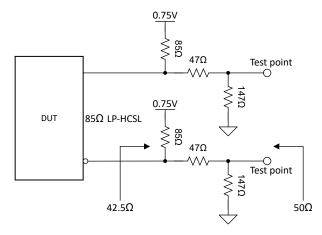

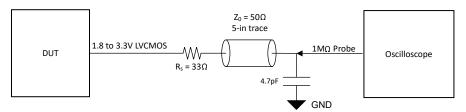

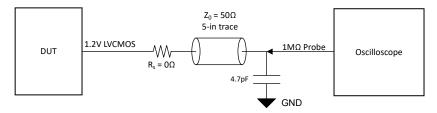

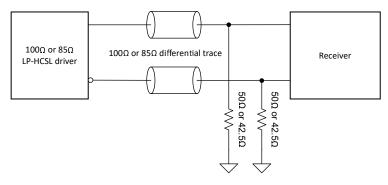

| 6.1 LP-HCSL Test or Simulation Loads25 |                                       |    |

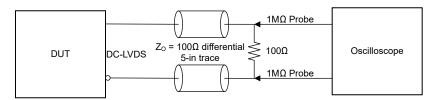

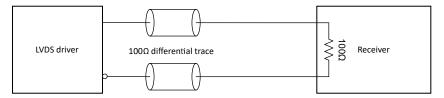

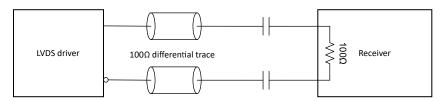

| 6.2 LVDS Test Load                     |                                       |    |

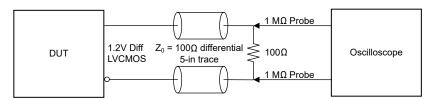

| 6.3 LVCMOS Test Load                   |                                       |    |

| 7 Detailed Description27               |                                       |    |

| 7.1 Overview27                         |                                       |    |

| 7.2 Functional Block Diagram27         |                                       | 65 |

| 7.3 Feature Description28              |                                       |    |

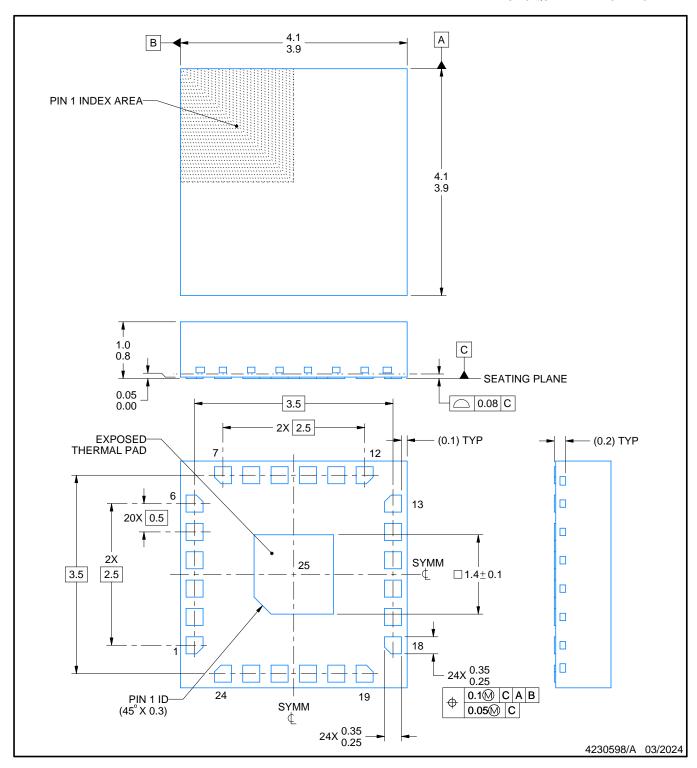

# 4 Pin Configuration and Functions

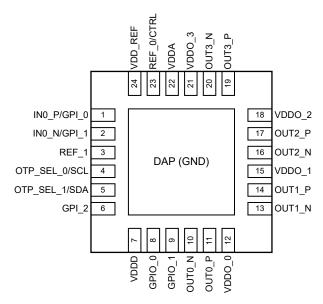

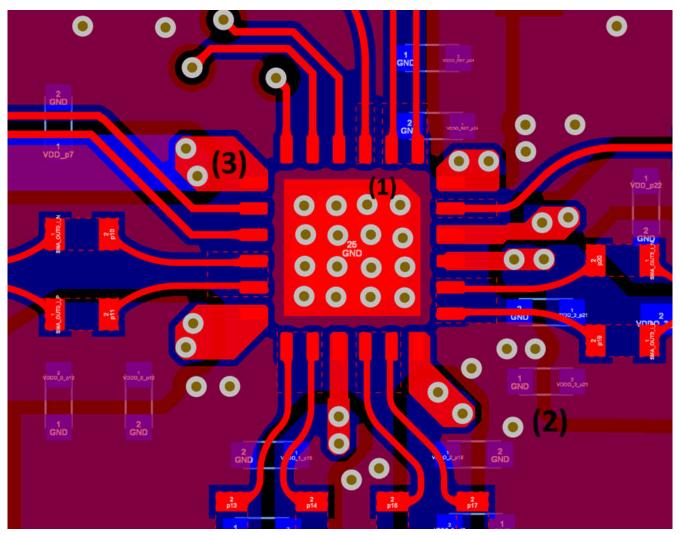

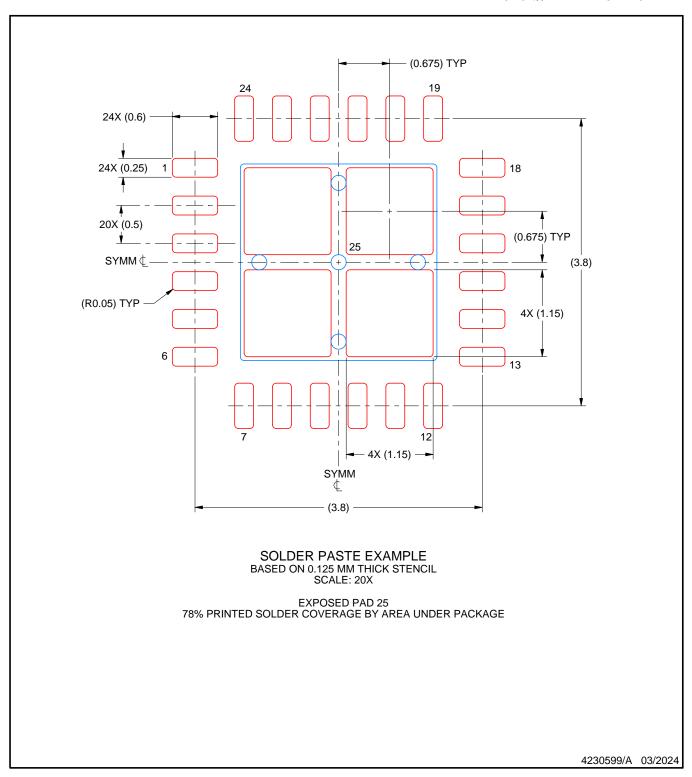

Figure 4-1. LMK3H2104 RGE Package 24-Pin QFN Top View

Table 4-1. Pin Functions

| PIN           |     | TYPE(1) | DECODINE                                                                                                                                        |  |  |

|---------------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME          | NO. | IYPE    | DESCRIPTION                                                                                                                                     |  |  |

| IN0_P/GPI_0   | 1   | ı       | Differential clock input or general purpose inputs. These are fail-safe input pins. Leave                                                       |  |  |

| IN0_N/GPI_1   | 2   | ı       | floating if unused.                                                                                                                             |  |  |

| REF_1         | 3   | 0       | 1.8, 2.5 or 3.3V LVCMOS clock output. This output can be disabled to low or tristate. Leave floating if unused.                                 |  |  |

| OTP_SEL_0/SCL | 4   | I       | Multifunctional pins. Functionality is determined by Pin 23 at power-up. Internal pull-down resistor on both pins by default. SCL is fail-safe. |  |  |

| OTP_SEL_1/SDA | 5   | I/O     | OTP mode: OTP_SEL_[1:0] select 1 out of 4 OTP pages     I2C mode: SCL, SDA                                                                      |  |  |

| GPI_2         | 6   | 1       | General purpose input. Fail-safe pin. Leave floating if unused                                                                                  |  |  |

| VDDD          | 7   | Р       | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping                                                                     |  |  |

| GPIO_0        | 8   | I/O     | General purpose input or output. Leave floating if unused.                                                                                      |  |  |

| GPIO_1        | 9   | I/O     | General purpose input or output. Leave floating or connect to VDD if unused. GPIO_1 must not be configured as an output if connected to VDD.    |  |  |

| OUT0_N        | 10  | 0       | Differential clock output 0. Supports LP-HCSL (85 $\Omega$ or 100 $\Omega$ ), LVDS and 1.2, 1.8, 2.5 or                                         |  |  |

| OUT0_P        | 11  | 0       | 3.3V LVCMOS. Leave floating if unused.                                                                                                          |  |  |

| VDDO_0        | 12  | Р       | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping                                                                     |  |  |

| OUT1_N        | 13  | 0       | Differential clock output 1. Supports LP-HCSL ( $85\Omega$ or $100\Omega$ ), LVDS and 1.2, 1.8, 2.5 or                                          |  |  |

| OUT1_P        | 14  | 0       | 3.3V LVCMOS. Leave floating if unused.                                                                                                          |  |  |

| VDDO_1        | 15  | Р       | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping                                                                     |  |  |

| OUT2_N        | 16  | 0       | Differential clock output 2. Supports LP-HCSL (85 $\Omega$ or 100 $\Omega$ ), LVDS and 1.2, 1.8, 2.5 or                                         |  |  |

| OUT2_P        | 17  | 0       | 3.3V LVCMOS. Leave floating if unused.                                                                                                          |  |  |

| VDDO_2        | 18  | Р       | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping                                                                     |  |  |

| OUT3_P        | 19  | 0       | Differential clock output 3. Supports LP-HCSL ( $85\Omega$ or $100\Omega$ ), LVDS and 1.2, 1.8, 2.5 or                                          |  |  |

| OUT3_N        | 20  | 0       | 3.3V LVCMOS. Leave floating if unused.                                                                                                          |  |  |

| VDDO_3        | 21  | Р       | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping                                                                     |  |  |

| VDDA          | 22  | Р       | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping                                                                     |  |  |

## Table 4-1. Pin Functions (continued)

| PIN        |     | TYPE(1) | DESCRIPTION                                                                                                                                                                                                     |  |  |

|------------|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME       | NO. | ITPE    | DESCRIPTION                                                                                                                                                                                                     |  |  |

|            |     | I/O     | Multifunctional pin. At power-up, the state of this pin is latched to decide Pin 4 and Pin 5 functions. No internal pull-up or pull-down resistor is available. This pin must be pulled high or low externally. |  |  |

| REF 0/CTRL | 23  |         | Low at power-up: I2C mode. Pin 4, 5 = SCL, SDA                                                                                                                                                                  |  |  |

| _          |     |         | High at power-up: OTP mode. Pin 4, 5 = OTP_SEL_0, OTP_SEL_1                                                                                                                                                     |  |  |

|            |     |         | After power-up, this pin can output a 1.8, 2.5, 3.3V LVCMOS clock, or be disabled to low or tristate.                                                                                                           |  |  |

| VDD_REF    | 24  | Р       | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping                                                                                                                                     |  |  |

| DAP        | 25  | G       | Connect to ground                                                                                                                                                                                               |  |  |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

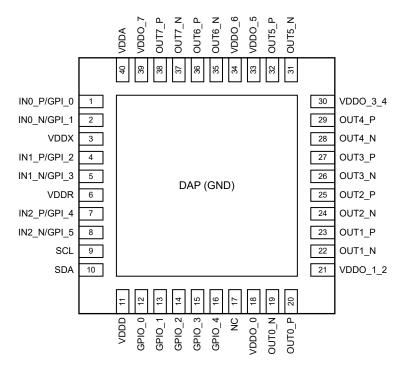

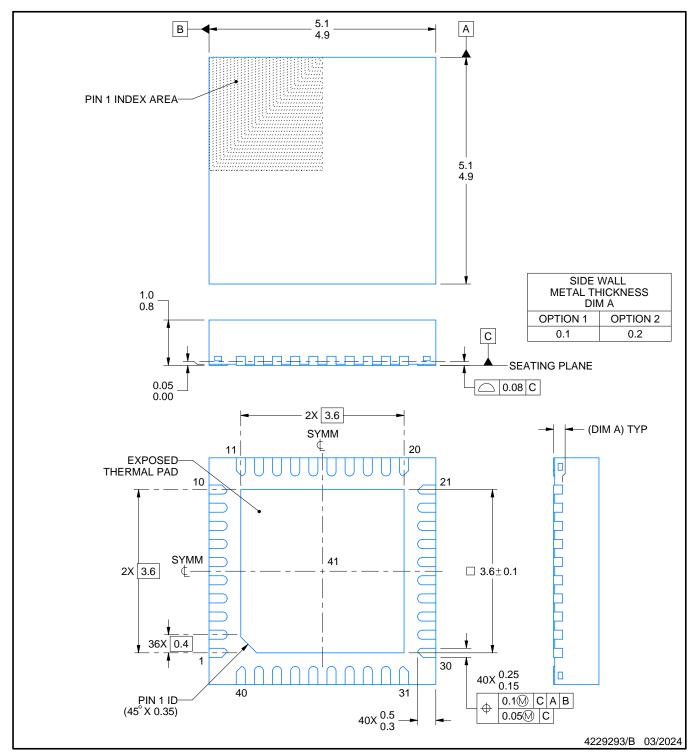

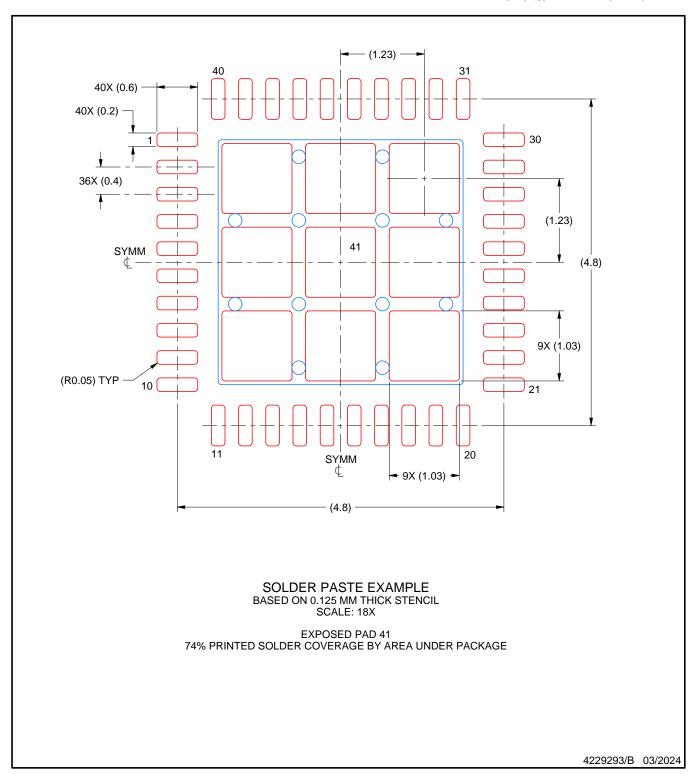

Figure 4-2. LMK3H2108 RKP Package 40-Pin QFN Top View

#### Table 4-2. Pin Functions

| P           | PIN |                     | DESCRIPTION                                                                               |  |  |

|-------------|-----|---------------------|-------------------------------------------------------------------------------------------|--|--|

| NAME        | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                               |  |  |

| IN0_P/GPI_0 | 1   | I                   | Differential clock input or general purpose inputs. These are fail-safe input pins. Leave |  |  |

| IN0_N/GPI_1 | 2   | I                   | floating if unused.                                                                       |  |  |

| VDDX        | 3   | Р                   | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping               |  |  |

| IN1_P/GPI_2 | 4   | I                   | Differential clock input or general purpose inputs. These are fail-safe input pins. Leave |  |  |

| IN1_N/GPI_3 | 5   | I                   | floating if unused.                                                                       |  |  |

| VDDR        | 6   | Р                   | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping               |  |  |

| IN2_P/GPI_4 | 7   | I                   | Differential clock input or general purpose inputs. These are fail-safe input pins. Leave |  |  |

| IN2_N/GPI_5 | 8   | I                   | floating if unused.                                                                       |  |  |

| SCL         | 9   | I                   | I2C clock                                                                                 |  |  |

| SDA         | 10  | I/O                 | I2C data                                                                                  |  |  |

| VDDD        | 11  | Р                   | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping               |  |  |

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

## **Table 4-2. Pin Functions (continued)**

| PII      | N   |                     | able 4-2. Fill Fullctions (continued)                                                                  |  |

|----------|-----|---------------------|--------------------------------------------------------------------------------------------------------|--|

| NAME     | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                            |  |

| GPIO_0   | 12  | I/O                 | General purpose input or output. Leave floating if unused.                                             |  |

| GPIO_1   | 13  | I/O                 | General purpose input or output. Leave floating if unused.                                             |  |

| GPIO_2   | 14  | I/O                 | General purpose input or output. Leave floating if unused.                                             |  |

| GPIO_3   | 15  | I/O                 | General purpose input or output. Leave floating if unused.                                             |  |

| GPIO_4   | 16  | I/O                 | General purpose input or output. Leave floating if unused.                                             |  |

| NC       | 17  | N/A                 | No connect. Leave floating or tie to GND                                                               |  |

| VDDO_0   | 18  | Р                   | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping                            |  |

| OUT0_N   | 19  | 0                   | Differential clock output 0. Supports LP-HCSL ( $85\Omega$ or $100\Omega$ ), LVDS and 1.2, 1.8, 2.5 or |  |

| OUT0_P   | 20  | 0                   | 3.3V LVCMOS. Leave floating if unused.                                                                 |  |

| VDDO_1_2 | 21  | Р                   | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping                            |  |

| OUT1_N   | 22  | 0                   | Differential clock output 1. Supports LP-HCSL ( $85\Omega$ or $100\Omega$ ), LVDS and 1.2, 1.8, 2.5 or |  |

| OUT1_P   | 23  | 0                   | 3.3V LVCMOS. Leave floating if unused.                                                                 |  |

| OUT2_N   | 24  | 0                   | Differential clock output 2. Supports LP-HCSL ( $85\Omega$ or $100\Omega$ ), LVDS and 1.2, 1.8, 2.5 or |  |

| OUT2_P   | 25  | 0                   | 3.3V LVCMOS. Leave floating if unused.                                                                 |  |

| OUT3_N   | 26  | 0                   | Differential clock output 3. Supports LP-HCSL ( $85\Omega$ or $100\Omega$ ), LVDS and 1.2, 1.8, 2.5 or |  |

| OUT3_P   | 27  | 0                   | 3.3V LVCMOS. Leave floating if unused.                                                                 |  |

| OUT4_N   | 28  | 0                   | Differential clock output 4. Supports LP-HCSL (85Ω or 100Ω), LVDS and 1.2, 1.8, 2.5 or                 |  |

| OUT4_P   | 29  | 0                   | 3.3V LVCMOS. Leave floating if unused.                                                                 |  |

| VDDO_3_4 | 30  | Р                   | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping                            |  |

| OUT5_N   | 31  | 0                   | Differential clock output 5. Supports LP-HCSL ( $85\Omega$ or $100\Omega$ ), LVDS and 1.2, 1.8, 2.5 or |  |

| OUT5_P   | 32  | 0                   | 3.3V LVCMOS. Leave floating if unused.                                                                 |  |

| VDDO_5   | 33  | Р                   | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping                            |  |

| VDDO_6   | 34  | Р                   | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping                            |  |

| OUT6_N   | 35  | 0                   | Differential clock output 6. Supports LP-HCSL ( $85\Omega$ or $100\Omega$ ), LVDS and 1.2, 1.8, 2.5 or |  |

| OUT6_P   | 36  | 0                   | 3.3V LVCMOS. Leave floating if unused.                                                                 |  |

| OUT7_N   | 37  | 0                   | Differential clock output 7. Supports LP-HCSL (85Ω or 100Ω), LVDS and 1.2, 1.8, 2.5 or                 |  |

| OUT7_P   | 38  | 0                   | 3.3V LVCMOS. Leave floating if unused.                                                                 |  |

| VDDO_7   | 39  | Р                   | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping                            |  |

| VDDA     | 40  | Р                   | 1.8, 2.5 or 3.3V power supply. See Power Supply Pin Mapping for VDD mapping                            |  |

| DAP      | 41  | G                   | Connect to ground                                                                                      |  |

<sup>(1)</sup> I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

## **5 Specifications**

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                                                                        | MIN  | MAX          | UNIT |

|------------------|----------------------------------------------------------------------------------------|------|--------------|------|

| V <sub>DD</sub>  | Device supply voltage                                                                  | -0.3 | 3.9          | V    |

| $V_{DDO}$        | Output supply voltage                                                                  | -0.3 | 3.9          | V    |

|                  | Voltage applied to OUTx_P and OUTx_N pins (when outputs are high or low)               | -0.3 | VDDO_x + 0.3 | V    |

| V <sub>OUT</sub> | Voltage applied to OUTx_P and OUTx_N pins (when outputs are LVCMOS tri-state)          | -0.3 | 1.89         | V    |

|                  | Voltage applied to OUTx_P and OUTx_N pins (when outputs are LP-HCSL or LVDS tri-state) | -0.3 | 1.5          | V    |

| T <sub>stg</sub> | Storage temperature                                                                    | -65  | 125          | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 5.2 ESD Ratings

|                    |                         |                                                                                     | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

| V                  | Floatractatio discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>     | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JS-002, all pins <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

## **5.3 Recommended Operating Conditions**

$V_{DD} = V_{DDO} = 1.8$ , 2.5 or 3.3V  $\pm$  5%,  $T_A = T_{A,min}$  to  $T_{A,max}$

|                   |                                                | MIN   | NOM | MAX                   | UNIT |

|-------------------|------------------------------------------------|-------|-----|-----------------------|------|

|                   |                                                | 1.71  | 1.8 | 1.89                  | V    |

| $V_{DD}$          | Device supply voltage                          | 2.375 | 2.5 | 2.625                 | V    |

|                   |                                                | 3.135 | 3.3 | 3.465                 | V    |

|                   |                                                | 1.71  | 1.8 | 1.89                  | V    |

| $V_{DDO}$         | Output supply voltage                          | 2.375 | 2.5 | 2.625                 | V    |

|                   |                                                | 3.135 | 3.3 | 3.465                 | V    |

| V                 | IN_x, GPI, OTP_SEL, SCL, SDA pin input voltage | -0.3  |     | 3.6                   | V    |

| V <sub>IN</sub>   | GPIO or CTRL pin input voltage                 | -0.3  |     | V <sub>DD</sub> + 0.3 | V    |

| T <sub>A</sub>    | Ambient temperature                            | -40   |     | 105                   | °C   |

| TJ                | Junction temperature                           | -40   |     | 110                   | °C   |

| +                 | Power supply ramp time. VDD = 1.8V             | 0.05  |     | 5                     | ms   |

| t <sub>ramp</sub> | Power supply ramp time. VDD = 2.5 or 3.3V      | 0.05  |     | 5                     | ms   |

## **5.4 Thermal Information**

|                               | LMK3H210                               |                 | LMK3H2104        | LMK3H2104        |      |

|-------------------------------|----------------------------------------|-----------------|------------------|------------------|------|

| THERMAL METRIC <sup>(1)</sup> |                                        | RKP0040A (VQFN) | RGE0024AA (VQFN) | RGE0024AB (VQFN) | UNIT |

|                               |                                        | 40 PINS         | 24 PINS          | 24 PINS          |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance | 31.8            | 53.0             | 39.6             | °C/W |

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

|                               |                                              | LMK3H2108       | LMK3H2104        | LMK3H2104        |      |

|-------------------------------|----------------------------------------------|-----------------|------------------|------------------|------|

| THERMAL METRIC <sup>(1)</sup> |                                              | RKP0040A (VQFN) | RGE0024AA (VQFN) | RGE0024AB (VQFN) | UNIT |

|                               |                                              | 40 PINS         | 24 PINS          | 24 PINS          |      |

| R <sub>0JC(top)</sub>         | Junction-to-case (top) thermal resistance    | 22.0            | 32.5             | 32.4             | °C/W |

| R <sub>θJB</sub>              | Junction-to-board thermal resistance         | 12.7            | 26.1             | 16.9             | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 0.6             | 0.9              | 0.6              | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 12.7            | 26.0             | 16.8             | °C/W |

| R <sub>0JC(bot)</sub>         | Junction-to-case (bottom) thermal resistance | 0.3             | 5.1              | 3.9              | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

# **5.5 Electrical Characteristics**

|                          | PARAMETER                                                                  | TEST CONDITIONS                      | MIN  | TYP MAX | UNIT |

|--------------------------|----------------------------------------------------------------------------|--------------------------------------|------|---------|------|

| FREQUEN                  | CY STABILITY                                                               |                                      |      |         |      |

| $\Delta f_{total}$       | Total frequency error. This includes all factors and 10-year aging at 25°C | T <sub>A</sub> = -40 to 105°C        | -25  | 25      | ppm  |

|                          |                                                                            | T <sub>A</sub> = 25°C, 1-year aging  | 1.0  | 3.6     | ppm  |

|                          |                                                                            | T <sub>A</sub> = 25°C, 3-year aging  | 1.2  | 5.0     | ppm  |

|                          |                                                                            | T <sub>A</sub> = 25°C, 5-year aging  | 1.3  | 5.7     | ppm  |

| ∆f <sub>aging,25°C</sub> | Frequency error due to aging at 25°C                                       | T <sub>A</sub> = 25°C, 10-year aging | 1.4  | 6.5     | ppm  |

|                          |                                                                            | T <sub>A</sub> = 25°C, 20-year aging | 1.6  | 7.4     | ppm  |

| CLOCK INI                | PUT REQUIREMENTS                                                           |                                      |      |         |      |

|                          | Input fraguency                                                            | LVCMOS input buffer                  | 0    | 200     | MHz  |

| f <sub>IN</sub>          | Input frequency                                                            | Differential input buffer            | 25   | 400     | MHz  |

| DC <sub>IN</sub>         | Clock input duty cycle                                                     |                                      | 40   | 60      | %    |

| \/                       | Differential clock input amplitude (half of                                | f <sub>0</sub> ≤ 300MHz              | 150  | 1200    | mV   |

| $V_{IN}$                 | differential peak-peak voltage)                                            | 300MHz < f <sub>0</sub> ≤ 400MHz     | 150  | 1200    | mV   |

| V <sub>CM</sub>          | Differential input common mode                                             |                                      | 0.2  | 3.3     | V    |

| V <sub>IH</sub>          | Single-ended clock input high voltage                                      |                                      | 1.2  | 3.6     | V    |

| V <sub>IL</sub>          | Single-ended clock input low voltage                                       |                                      | -0.3 | 0.5     | V    |

| dV <sub>IN</sub> /dt     | Clock input slew rate                                                      | 20% to 80%                           | 0.15 |         | V/ns |

Submit Document Feedback

|                                                 | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TEST CONDITIONS                                                                       | MIN | TYP | MAX | UNIT |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----|-----|-----|------|

|                                                 | = 0 terr Coi = 0 diffi is e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Common mode voltage<br>= 0.7V. Internal input<br>termination is disabled              |     | 2.7 |     | pF   |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Common mode voltage = $0.7V$ Internal $100\Omega$ differential termination is enabled |     | 1.4 |     | pF   |

| Clock input capacitance per pin. Capacitance at | Common mode voltage<br>= 1.2V. Internal input<br>termination is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                       | 2.5 |     | pF  |      |

| C <sub>IN</sub>                                 | INx_P pin or INx_N pin, when INx is configured as clock input    Color input capacitance per pin. Capacitance at Invalid as clock input   Color input   Colo | Common mode voltage = $1.2V$ Internal $100\Omega$ differential termination is enabled |     | 1.3 |     | pF   |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Common mode voltage<br>= 3.3V. Internal input<br>termination is disabled              |     | 3.4 |     | pF   |

| =                                               | Common mode voltage = $3.3V$ Internal $100\Omega$ differential termination is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                       | 1.4 |     | pF  |      |

| LP-HCSL (                                       | LOCK OUTPUT CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                       |     |     |     |      |

| f <sub>out</sub>                                | Output frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                       | 2.5 |     | 400 | MHz  |

| V <sub>min</sub>                                | Output voltage low including undershoot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                       | -85 |     | 85  | mV   |

| Vovershoot                                      | Output voltage high overshoot voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $V_{\text{max}} - V_{\text{OH}}$                                                      |     |     | 120 | mV   |

**PARAMETER TEST CONDITIONS** MIN **TYP** MAX UNIT OUTx LPHCSL VOD 612 686 758  $\mathsf{mV}$ SEL = 0OUTx\_LPHCSL\_VOD\_ 638 714 789 mV **SEL = 1** OUTx\_LPHCSL\_VOD\_ 663 741 818 mV SEL = 2OUTx LPHCSL VOD 687 768 849 mV SEL = 3 OUTx LPHCSL VOD 712 793 877 mV SEL = 4 OUTx\_LPHCSL\_VOD\_ 734 817 905 mV SEL = 5 OUTx\_LPHCSL\_VOD\_ 704 794 877 mV **SEL = 6** OUTx\_LPHCSL\_VOD\_ 727 820 906  $\mathsf{mV}$ SEL = 7 Output high voltage(4)  $V_{OH}$ OUTx\_LPHCSL\_VOD\_ 726 823 913 mV SEL = 8 OUTx\_LPHCSL\_VOD\_ 748 847 941 mV **SEL = 9** OUTx\_LPHCSL\_VOD\_ 769 872 967 mV **SEL = 10** OUTx LPHCSL VOD 792 896 996 mV SEL = 11 OUTx\_LPHCSL\_VOD\_ 815 921 1023 mV SEL = 12 OUTx\_LPHCSL\_VOD\_ 836 945 1050 mV SEL = 13 OUTx LPHCSL\_VOD\_ 858 969 1080 mV SEL = 14 OUTx LPHCSL VOD 879 993 1107 mV **SEL = 15** 85Ω LP-HCSL 68 85 102 Ω  $Z_{diff}$ LP-HCSL static differential impedance 100Ω LP-HCSL 80 100 120 Ω OUTx\_SLEW\_RATE = 2.4 3.1 3.7 V/ns 0(1) OUTx\_SLEW\_RATE = Output slew rate (rising and falling 2.2 2.9 3.4 V/ns edge). Measured from -150mV to +150mV on dV/dt the differential waveform, centered on the zero OUTx\_SLEW\_RATE = 2 2.6 3.1 V/ns crossing point. OUTx\_SLEW\_RATE = 1.8 2.3 2.8 V/ns (1) % ∆dV/dt Rising edge rate to falling edge rate matching 20 (1) 45 55 % % f<sub>out</sub> ≤ 325MHz 45 55 ODC Output duty cycle  $325MHz < f_{out} \le 400$ 45 55 %

Output to output skew

Absolute crossing point voltage

Time before V<sub>RB</sub> is allowed

Variation of V<sub>cross</sub> over all clock edges

Absolute value of ring back voltage

$\frac{t_{\text{skew}}}{V_{\text{cross}}}$

$\Delta V_{cross}$

$|V_{RB}|$

t<sub>stable</sub>

250

100

500

100

550

140

ps

mV

mV

mV

ps

Same clock source

(1)

(1)

(1)

(1)

|                                   | PARAMETER                                                                                                                       | TEST CONDITIONS                  | MIN                          | TYP MAX   | UNIT |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------|-----------|------|

| J <sub>cycle-to-cycle</sub>       | Cycle to cycle jitter, Common Clock no SSC                                                                                      | (1)                              |                              | 150       | ps   |

| J <sub>cycle-to-cycle</sub>       | Cycle to cycle jitter, Common Clock, -0.5% SSC                                                                                  | (1)                              |                              | 150       | ps   |

| period_abs                        | Absolute period including jitter and SSC                                                                                        | (1)                              | 9.949                        | 10 10.101 | ns   |

| t <sub>period_avg_C</sub>         | Average clock period accuracy, Common Clock                                                                                     | (1)                              | -100                         | 2600      | ppm  |

| period_avg_S                      | Average clock period accuracy, SRIS                                                                                             | (1)                              | -100                         | 1600      | ppm  |

| V <sub>OH-DC</sub>                | Output voltage high                                                                                                             | DC simulation load,              | 225                          | 270       | mV   |

| V <sub>OL-DC</sub>                | Output voltage low                                                                                                              | 85Ω LP-HCSL,<br>OUTx_LPHCSL_VOD_ | 10                           | 150       | mV   |

| V <sub>cross-DC</sub>             | Absolute crossing point voltage                                                                                                 | SEL = 4                          | 130                          | 200       | mV   |

|                                   | CK OUTPUT CHARACTERISTICS                                                                                                       |                                  |                              |           |      |

| f <sub>out</sub>                  | Output frequency                                                                                                                |                                  | 2.5                          | 400       | MHz  |

| V <sub>OD</sub>                   | Steady-state magnitude of the differential output voltage  V <sub>OUTP</sub> - V <sub>OUTN</sub>                                |                                  | 250                          | 450       | mV   |

| $\Delta V_{pp	ext{-diff}}$        | Change in differential output voltage swing between complementary output states                                                 |                                  |                              | 50        | mV   |

|                                   |                                                                                                                                 | VDDO_x = 3.3V                    | 1.075                        | 1.425     | V    |

| V <sub>OS</sub>                   | Steady-state output offset voltage (common mode voltage)                                                                        | VDDO_x = 2.5V                    | 1.05                         | 1.4       | V    |

|                                   | voltage)                                                                                                                        | VDDO_x = 1.8V                    | 1                            | 1.25      | V    |

| ΔV <sub>OS</sub>                  | Change in V <sub>OS</sub> between complementary output states                                                                   |                                  |                              | 50        | mV   |

| I <sub>SA</sub> , I <sub>SB</sub> | Short-circuit current. Magnitude of current with the generator output terminals short-circuited to the generator circuit common |                                  | -24                          | 24        | mA   |

| I <sub>SAB</sub>                  | Short-circuit current. Magnitude of current with generator output terminals short-circuited to each other                       |                                  | -12                          | 12        | mA   |

|                                   | 20% to 80% differential rise/fall time                                                                                          | OUTx_SLEW_RATE = 0               |                              | 385       | ps   |

| +_ +_                             |                                                                                                                                 | OUTx_SLEW_RATE = 1               |                              | 545       | ps   |

| t <sub>R</sub> , t <sub>F</sub>   | 2070 to 60 76 differential fise/fail time                                                                                       | OUTx_SLEW_RATE = 2               |                              | 710       | ps   |

|                                   |                                                                                                                                 | OUTx_SLEW_RATE = 3               |                              | 850       | ps   |

| t <sub>skew</sub>                 | Output to output skew                                                                                                           | Same clock source                |                              | 100       | ps   |

| ODC                               | Output duty cycle                                                                                                               |                                  | 45                           | 55        | %    |

| LVCMOS C                          | LOCK OUTPUT CHARACTERISTICS                                                                                                     |                                  |                              |           |      |

|                                   | Output frequency. Clock source is FOD or edge                                                                                   | OUT0                             | 38.15 ×<br>10 <sup>-6</sup>  | 200       | MHz  |

| f <sub>out</sub>                  | combiner                                                                                                                        | All other outputs                | 156.25 ×<br>10 <sup>-3</sup> | 200       | MHz  |

|                                   | Output frequency. Clock source is IN0, IN1 or IN2                                                                               |                                  | 0                            | 200       | MHz  |

| -D.77.16                          |                                                                                                                                 | OUTx_CMOS_SLEW_<br>RATE = 0      | 2                            | 5.2       | V/ns |

|                                   | Output slew rate. VDDO = 3.3V ± 5%. Measured                                                                                    | OUTx_CMOS_SLEW_<br>RATE = 1      | 1.7                          | 5         | V/ns |

| dV/dt                             | from 20% to 80%, 4.7pF load                                                                                                     | OUTx_CMOS_SLEW_<br>RATE = 2      | 1.35                         | 4         | V/ns |

|                                   |                                                                                                                                 | OUTx_CMOS_SLEW_<br>RATE = 3      | 1                            | 3.5       | V/ns |

|                      | PARAMETER                                                                             | TEST CONDITIONS                                                                | MIN           | TYP MAX | UNIT |

|----------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------|---------|------|

|                      |                                                                                       | OUTx_CMOS_SLEW_<br>RATE = 0                                                    | 1.5           | 3.9     | V/ns |

| dV/dt                | Output slew rate. VDDO = 2.5V ± 5%. Measured                                          | OUTx_CMOS_SLEW_<br>RATE = 1                                                    | 1.3           | 3.8     | V/ns |

| uv/ut                | from 20% to 80%, 4.7pF load                                                           | OUTx_CMOS_SLEW_<br>RATE = 2                                                    | 1             | 3.1     | V/ns |

|                      |                                                                                       | OUTx_CMOS_SLEW_<br>RATE = 3                                                    | 0.75          | 2.7     | V/ns |

|                      |                                                                                       | OUTx_CMOS_SLEW_<br>RATE = 0                                                    | 1.25          | 2.9     | V/ns |

| dV/dt                | Output slew rate. VDDO = 1.8V ± 5%. Measured                                          | OUTx_CMOS_SLEW_<br>RATE = 1                                                    | 1.1           | 2.8     | V/ns |

| av/at                | from 20% to 80%, 4.7pF load                                                           | OUTx_CMOS_SLEW_<br>RATE = 2                                                    | 0.85          | 2.4     | V/ns |

|                      |                                                                                       | OUTx_CMOS_SLEW_<br>RATE = 3                                                    | 0.65          | 2.1     | V/ns |

|                      |                                                                                       | OUTx_SLEW_RATE = 0                                                             | 1.5           | 2.1     | V/ns |

| dV/dt                | Output slew rate. 1.2V LVCMOS mode. VDDO =                                            | OUTx_SLEW_RATE = 1                                                             | 1.3           | 1.9     | V/ns |

| av/at                | 3.3V or 2.5V. Measured from 20% to 80%, 4.7pF load                                    | OUTx_SLEW_RATE = 2                                                             | 1.1           | 1.6     | V/ns |

|                      |                                                                                       | OUTx_SLEW_RATE = 3                                                             | 1             | 1.5     | V/ns |

|                      | Output slew rate. 1.2V LVCMOS mode. VDDO = 1.8V. Measured from 20% to 80%, 4.7pF load | OUTx_SLEW_RATE = 0                                                             | 1.2           | 2.3     | V/ns |

| -17.77-14            |                                                                                       | OUTx_SLEW_RATE = 1                                                             | 1             | 2       | V/ns |

| dV/dt                |                                                                                       | OUTx_SLEW_RATE = 2                                                             | 0.9           | 1.8     | V/ns |

|                      |                                                                                       | OUTx_SLEW_RATE = 3                                                             | 0.8           | 1.6     | V/ns |

|                      | Output high voltage                                                                   | I <sub>OH</sub> = -15mA at 3.3V                                                | 0.8 ×<br>VDDO | VDDO    | V    |

| $V_{OH}$             |                                                                                       | I <sub>OH</sub> = -12mA at 2.5V                                                | 0.8 ×<br>VDDO | VDDO    | V    |

|                      |                                                                                       | I <sub>OH</sub> = -8mA at 1.8V                                                 | 0.8 ×<br>VDDO | VDDO    | V    |

|                      |                                                                                       | I <sub>OL</sub> = 15mA at 3.3V                                                 | 0             | 0.4     |      |

| $V_{OL}$             | Output low voltage                                                                    | I <sub>OL</sub> = 12mA at 2.5V                                                 | 0             | 0.4     | V    |

|                      |                                                                                       | I <sub>OL</sub> = 8mA at 1.8V                                                  | 0             | 0.4     |      |

| V                    | Output high voltage in 1.2V CMOS made                                                 | Programmed to 1.2V. I <sub>OH</sub> = –3mA                                     | 0.93          | 1.2     | V    |

| V <sub>OH,1.2V</sub> | Output high voltage in 1.2V CMOS mode                                                 | Programmed to 1.1V. I <sub>OH</sub> = –3mA                                     | 0.86          | 1.1     | V    |

| V <sub>OL,1.2V</sub> | Output low voltage in 1.2V CMOS mode                                                  | I <sub>OL</sub> = 3mA                                                          | 0             | 0.24    | V    |

| V <sub>OD,1.2V</sub> | V <sub>OUTP</sub> - V <sub>OUTN</sub>  . Output swing in 1.2V CMOS                    | Programmed to 1.2V. $100\Omega$ differential external termination. $2pF$ load. | 539           | 600 660 | mV   |

| Diff                 | mode with differential output termination                                             | Programmed to 1.1V. $100\Omega$ differential external termination. $2pF$ load. | 495           | 550 617 | mV   |

|                            | PARAMETER                                                                                                                                                     | TEST CONDITIONS                                                                | MIN           | TYP | MAX  | UNIT |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------|-----|------|------|

| Vaaravava                  | Output offset voltage. Output common mode in 1.2V CMOS mode with differential output                                                                          | Programmed to 1.2V. $100\Omega$ differential external termination. $2pF$ load. | 540           | 600 | 660  | mV   |

| V <sub>OS,1.2</sub> V Diff | termination                                                                                                                                                   | Programmed to 1.1V. $100\Omega$ differential external termination. $2pF$ load. | 495           | 550 | 605  | mV   |

|                            |                                                                                                                                                               | OUTx_SLEW_RATE = 0                                                             | 2.8           |     | 3.3  | V/ns |

|                            | Differential output slew rate in 1.2V CMOS mode with $100\Omega$ differential external termination. VDDO                                                      | OUTx_SLEW_RATE = 1                                                             | 2.2           |     | 2.6  | V/ns |

|                            | = 3.3V or 2.5V ± 5%. Measured from 20% to 80%, 2pF load                                                                                                       | OUTx_SLEW_RATE = 2                                                             | 1.8           |     | 2.1  | V/ns |

| dV/dt                      |                                                                                                                                                               | OUTx_SLEW_RATE = 3                                                             | 1.5           |     | 1.7  | V/ns |

| a v/at                     | Differential output slew rate in 1.2V CMOS mode with 100 $\Omega$ differential external termination. VDDO = 1.8V $\pm$ 5%. Measured from 20% to 80%, 2pF load | OUTx_SLEW_RATE = 0                                                             | 2.5           |     | 3.3  | V/ns |

|                            |                                                                                                                                                               | OUTx_SLEW_RATE = 1                                                             | 2             |     | 2.6  | V/ns |

|                            |                                                                                                                                                               | OUTx_SLEW_RATE = 2                                                             | 1.6           |     | 2.1  | V/ns |

|                            |                                                                                                                                                               | OUTx_SLEW_RATE = 3                                                             | 1.3           |     | 1.8  | V/ns |

| I <sub>leak</sub>          | Output leakage current                                                                                                                                        | Output tri-stated. VDD = VDDO = 3.465V                                         | -35           |     | 35   | μΑ   |

|                            |                                                                                                                                                               | 3.3V LVCMOS                                                                    |               | 17  |      | Ω    |

| R <sub>out</sub>           | Output impedance                                                                                                                                              | 2.5V LVCMOS                                                                    |               | 17  |      | Ω    |

| · ·out                     |                                                                                                                                                               | 1.8V LVCMOS                                                                    |               | 17  |      | Ω    |

|                            |                                                                                                                                                               | 1.2V LVCMOS                                                                    | 40            | 50  | 60   | Ω    |

| ODC                        | Output duty cycle                                                                                                                                             | f <sub>out</sub> ≤ 156.25MHz                                                   | 45            |     | 55   | %    |

|                            |                                                                                                                                                               | f <sub>out</sub> > 156.25MHz                                                   | 45            |     | 55   | %    |

| t <sub>skew</sub>          | Output-to-output skew                                                                                                                                         | Same clock source                                                              |               |     | 100  | ps   |

| C <sub>load</sub>          | Maximum load capacitance                                                                                                                                      |                                                                                |               |     | 15   | pF   |

|                            | EFCLK CHARACTERISTICS                                                                                                                                         | T                                                                              |               |     |      |      |

| f <sub>out</sub>           | Output frequency                                                                                                                                              | (0)                                                                            | 0             |     | 200  | MHz  |

|                            |                                                                                                                                                               | $VDDO = 3.3V \pm 5\%^{(2)}$                                                    | 2.2           |     | 6.1  | V/ns |