SLIS113E October 2004 – May 2022 TPIC1021

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- D|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

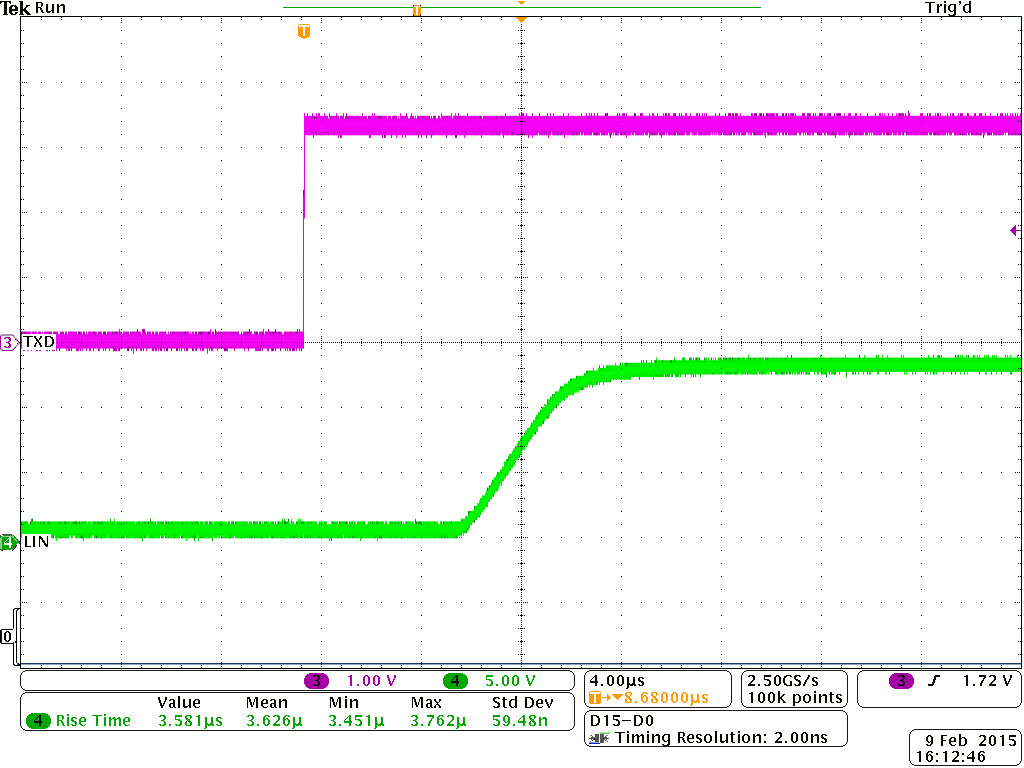

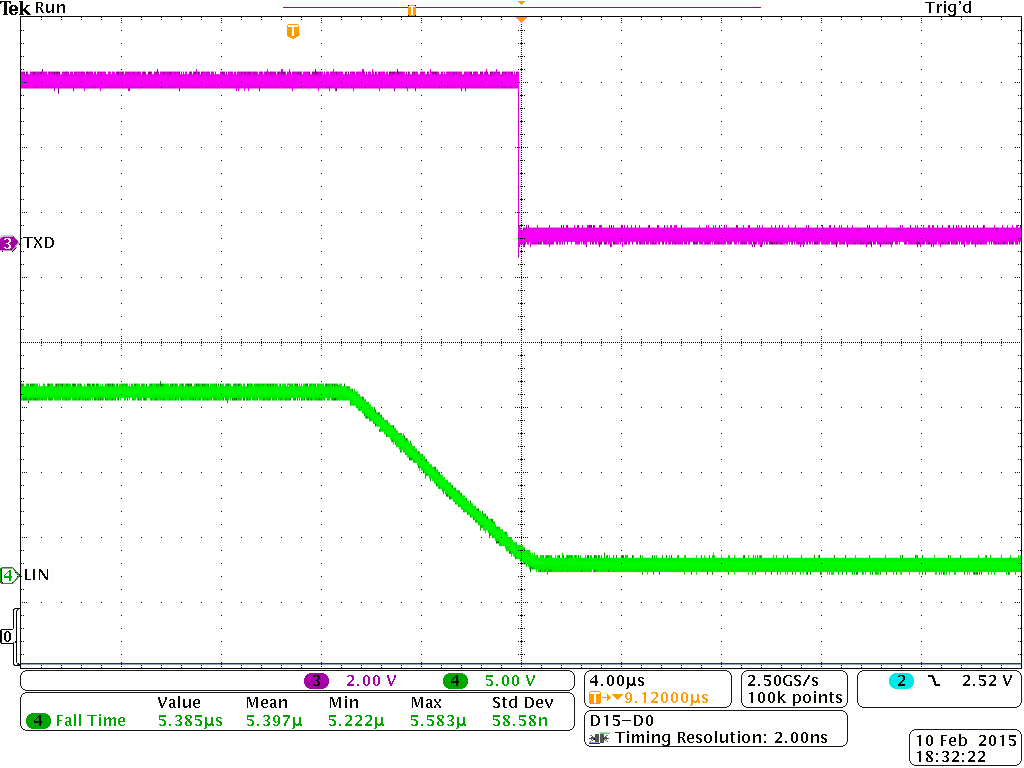

9.2.3 Application Curves

Figure 9-2 and Figure 9-3 show the propagation delay from the TXD pin to the LIN pin for both the recessive to dominant and dominant to recessive states under lightly loaded conditions.

Figure 9-2 Dominant to Recessive Propagation Delay

Figure 9-2 Dominant to Recessive Propagation Delay Figure 9-3 Recessive to Dominant Propagation Delay

Figure 9-3 Recessive to Dominant Propagation Delay