# Connectivity Processor with Cache, DSP, and Bluetooth®, USB, and Dual CAN Interfaces

Check for Samples: CP3SP33

# 1 Introduction

#### 1.1 Features

- CPU Features

- Fully static RISC processor core, capable of operating from 0 to 96 MHz with zero wait/hold state

- Minimum 10.4 ns instruction cycle time with a 96-MHz internal clock frequency, based on a 12-MHz external input

- 4K-byte, 4-way set-associative instruction cache

- 69 independently vectored peripheral interrupts

- DSP Features

- Capable of operating up to 96 MHz

- 16-bit fixed-point arithmetic, dual-MAC architecture

- 32-bit interface to 4K-byte RAM shared with CPU

- 32-bit external bus interface

- Bus master interface to audio peripherals and I/O

- Memory

- 4K bytes CPU instruction cache

- 32K bytes CPU data RAM

- 4K bytes CPU/DSP shared RAM

- 24K bytes DSP program RAM

- 24K bytes DSP data RAM

- 8K bytes Bluetooth<sup>®</sup> sequencer and data RAM

- Addresses up to 96M bytes (FBGA-224 package) or 8M bytes (FBGA-144 package) of external memory

- Broad Range of Hardware Communications

Peripherals

- Bluetooth Lower Link Controller (LLC) including a shared 7K byte Bluetooth data RAM and 1K byte Bluetooth Sequencer RAM

- Universal Serial Bus (USB) 2.0 On-The-Go

- Audio/telematics codec with dual ADC inputs and high quality stereo DAC output

- Two CAN interfaces with 15 message buffers conforming to CAN specification 2.0B active

- Two ACCESS.bus serial bus interfaces (I<sup>2</sup>C compatible)

- Two 8/16-bit SPI, Microwire/Plus serial interfaces

- I<sup>2</sup>S digital audio bus interface

- Four Universal Asynchronous Receiver/Transmitter (UART) channels, one channel has USART capability

- Advanced Audio Interface (AAI) to connect to external 8/ 13-bit PCM Codecs as well as to ISDN-Controllers through the IOM-2 interface (slave only)

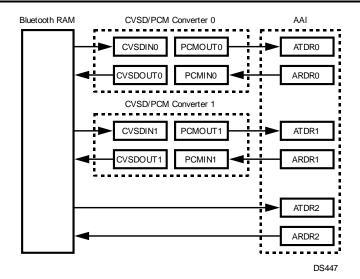

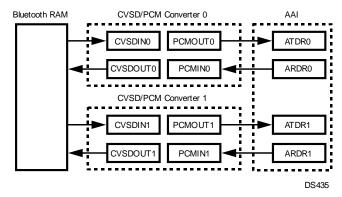

- Two CVSD/PCM converters, for supporting two bidirectional audio connectionsM

- External Bus Interface Shared Between CPU and DSP

- 16/32-bit data busbus interface

- 23-bit address bus

- 3 programmable chip select outputs

- Up to 96M bytes external memory

- 8-level write buffer

- General-Purpose Hardware Peripherals

- 10-channel, 10-bit A/D Converter (ADC)

- 16-channel DMA controller

- Dual 16-bit Multi-Function Timer (MFT)

- Dual Versatile Timer Units (VTU), each with four independent timers

- Timing and Watchdog Unit

- Extensive Power and Clock Management Support

- Two Phase Locked Loops (PLL) for synthesizing independent system and audio peripheral clocks

- Two independent oscillators for Active mode (12 MHz) and Power Save mode (32.768 kHz) clocks

- Low-power modes (Power Save, Idle, and Halt) for slowing or stopping clocks to optimize power consumption while meeting application needs

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. Bluetooth is a registered trademark of Bluethooth SIG, Inc. Teak is a registered trademark of ParthusCeva, Inc.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

# CP3SP33

SNOSCW5-MAY 2013

- Flexible I/O

- Up to 64 general-purpose I/O pins (shared with on-chip peripheral I/O)

- Programmable I/O pin characteristics: TRI-STATE output, push-pull output, weak pullup/pulldown input, high impedance input, high-speed drive capability

- Schmitt triggers on general-purpose inputs

- Multi-Input Wake-Up (MIWU) capability...

- Power Supply

- I/O port operation at 3.0-3.3V

- Core logic operation at 1.8V

- On-chip power-on reset

- Temperature Range

- –40°C to +85°C (Industrial)

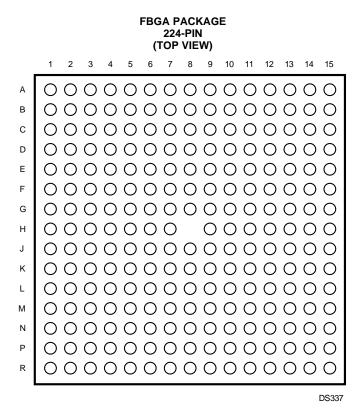

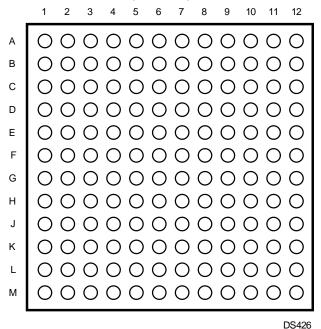

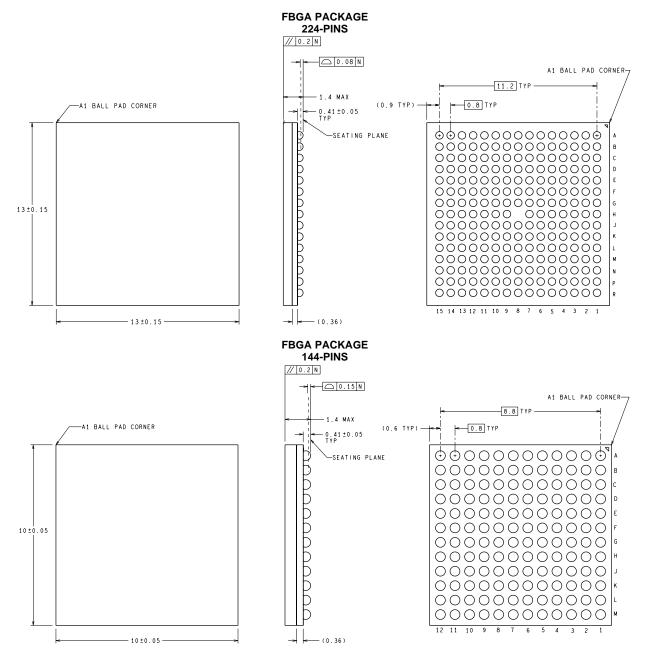

- Packages

- FBGA-224, FBGA-144

- Complete Development Environment

- Pre-integrated hardware and software support for rapid prototyping and production

- Multi-file C source editor, source debugger, and project manager

- Comprehensive, integrated, one-stop technical support

- Bluetooth Protocol Stack

- Applications can interface to the high-level protocols or directly to the low-level Host Controller Interface (HCI)

- Transport layer support allows HCI command-based interface over UART port

- Baseband (Link Controller) hardware minimizes the bandwidth demand on the CPU

- Link Manager (LM)

- Logical Link Control and Adaptation Protocol (L2CAP)

- Service Discovery Protocol (SDP)

- RFCOMM Serial Port Emulation Protocol

- All packet types, piconet, and scatternet functionality

### 1.2 CP3SP33 Connectivity Processor Selection Guide

| NSID       | Speed<br>(MHz) | Temp. Range    | On-Chip<br>RAM | Maximum<br>External Memory | External Data<br>Bus Width | General<br>Purpose I/O | Package<br>Type |

|------------|----------------|----------------|----------------|----------------------------|----------------------------|------------------------|-----------------|

| CP3SP33SMS | 96             | –40°C to +85°C | 32K            | 96M                        | 32                         | 64                     | FBGA-224        |

| CP3SP33SMR | 96             | –40°C to +85°C | 32K            | 8M                         | 16                         | 36                     | FBGA-144        |

### TEXAS INSTRUMENTS

#### www.ti.com

| 1  | Intro | duction                                        | . <u>1</u>   |

|----|-------|------------------------------------------------|--------------|

|    | 1.1   | Features                                       | <u>    1</u> |

|    | 1.2   | CP3SP33 Connectivity Processor Selection Guide | . <u>2</u>   |

| 2  | Desc  | ription                                        | . <u>6</u>   |

|    | 2.1   | Block Diagram                                  | . <u>6</u>   |

| 3  | Devi  | ce Overview                                    | . 7          |

|    | 3.1   | CR16CPlus CPU Core                             | . 7          |

|    | 3.2   | Teak DSP Core                                  | . 7          |

|    | 3.3   | AMBA Bus Architecture                          |              |

|    | 3.4   | External Bus Interface Unit                    | . 7          |

|    | 3.5   | Memory                                         |              |

|    | 3.6   | Bluetooth LLC                                  | . <u>8</u>   |

|    | 3.7   | USB                                            | . <u>8</u>   |

|    | 3.8   | CAN Interface                                  | . 8          |

|    | 3.9   | Audio/Telematics Codec                         | . <u>9</u>   |

|    | 3.10  | CVSD/PCM Conversion Modules                    |              |

|    | 3.11  | I <sup>2</sup> S Digital Audio Bus             | . <u>9</u>   |

|    | 3.12  | Advanced Audio Interface                       |              |

|    | 3.13  | Analog to Digital Converter                    | . <u>9</u>   |

|    | 3.14  | Quad UART                                      | <u>10</u>    |

|    | 3.15  | Microwire/SPI                                  | <u>10</u>    |

|    | 3.16  | Dual ACCESS.BUS Interface                      | <u>10</u>    |

|    | 3.17  | Dual Multi-Function Timer                      | <u>10</u>    |

|    | 3.18  | Versatile Timer Units                          | <u>11</u>    |

|    | 3.19  | Timing and Watchdog Module                     | <u>11</u>    |

|    | 3.20  | Power Management                               | <u>11</u>    |

|    | 3.21  | Multi-Input Wake-up                            | <u>11</u>    |

|    | 3.22  | Input/Output Ports                             | <u>11</u>    |

|    | 3.23  | Clock and Reset Module                         | <u>11</u>    |

|    | 3.24  | DMA Controller                                 | <u>12</u>    |

|    | 3.25  | Serial Debug Interface                         | <u>12</u>    |

|    | 3.26  | Development Support                            | <u>12</u>    |

| 4  | Signa | al Descriptions                                | <u>13</u>    |

| 5  | CPU   | Architecture                                   | <u>18</u>    |

|    | 5.1   | General-Purpose Registers                      | <u>18</u>    |

|    | 5.2   | Dedicated Address Registers                    |              |

|    | 5.3   | Processor Status Register (PSR)                | <u>19</u>    |

|    | 5.4   | Configuration Register (CFG)                   | <u>21</u>    |

|    | 5.5   | Addressing Modes                               | <u>21</u>    |

|    | 5.6   | Stacks                                         | <u>23</u>    |

|    | 5.7   | Instruction Set                                | <u>23</u>    |

| 6  |       | ory                                            | <u>27</u>    |

| 7  | Instr | uction Cache                                   | <u>28</u>    |

|    | 7.1   | Cache Locking                                  | <u>29</u>    |

|    | 7.2   | Cache Invalidation                             | <u>30</u>    |

| 8  | CPU   | Core Bus Arbitration                           | <u>30</u>    |

|    | 8.1   | Bus Arbiter Registers                          | <u>31</u>    |

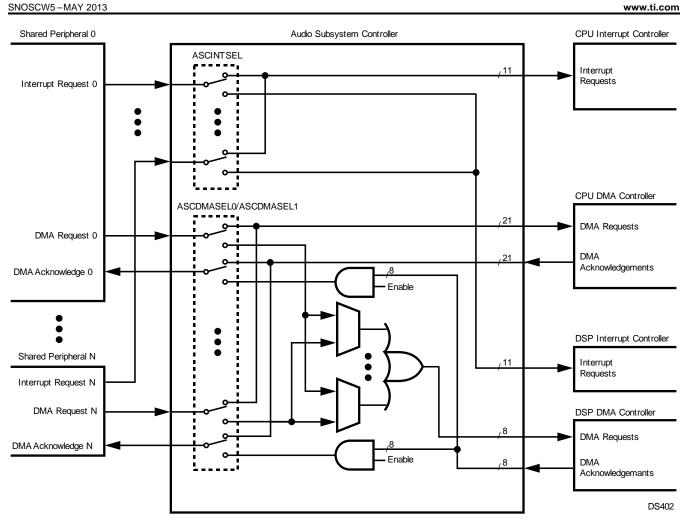

| 9  | DSP   | and Audio Peripherals                          | <u>32</u>    |

|    | 9.1   | DSP Memory Spaces                              | <u>34</u>    |

|    | 9.2   | CPU/DSP Interface                              | <u>34</u>    |

|    | 9.3   | DSP and ASC Registers                          | <u>37</u>    |

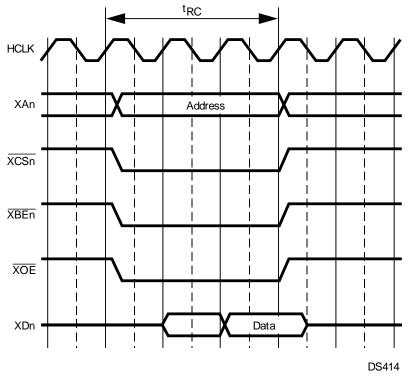

| 10 | Exte  | rnal Bus Interface Unit                        | <u>44</u>    |

|    | 10.1  | External Bus Signals                           | <u>44</u>    |

|    | 10.4  | EBIU Registers                         | <u>48</u>       |

|----|-------|----------------------------------------|-----------------|

|    | 10.5  | Usage Notes                            | <u>52</u>       |

| 11 | Syste | em Configuration                       | <u>52</u>       |

|    | 11.1  | Operating Environment                  | <u>52</u>       |

|    | 11.2  | Freeze Mode                            | 52              |

|    | 11.3  | System Configuration Registers         | 53              |

|    | 11.4  | Module Configuration Register (MCFG)   | 53              |

|    | 11.5  | Module Status Register (MSTAT)         | 54              |

|    | 11.6  | Software Reset Register (SWRESET)      | 54              |

|    | 11.7  | System Configuration Register (SYSCFG) | 54              |

| 12 | CPU   | DMA Controller                         | 55              |

|    | 12.1  | DMA-Capable Peripherals                | <u>56</u>       |

|    | 12.2  | Transfer Types                         | <u>57</u>       |

|    | 12.3  | Transfer Modes                         | <u>58</u>       |

|    | 12.4  | Software DMA Request                   | <u>60</u>       |

|    | 12.5  | DMA Request Timeout                    | <u>61</u>       |

|    | 12.6  | Error Response                         | 61              |

|    | 12.7  | Freeze Mode                            | 61              |

|    | 12.8  | Register Programming                   | <u>61</u>       |

|    | 12.9  | DMA Controller Register Set            | <u>61</u>       |

| 13 | Inter | rupts                                  | <b>68</b>       |

|    | 13.1  | Non-Maskable Interrupts                | <u>68</u>       |

|    | 13.2  | Maskable Interrupts                    | <u>68</u>       |

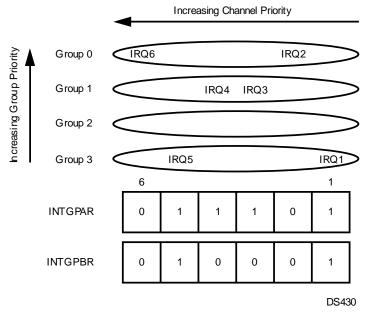

|    | 13.3  | Interrupt Priority Groups              | <u>70</u>       |

|    | 13.4  | Nested Interrupts                      | <u>71</u>       |

|    | 13.5  | Software Interrupts                    | <u>71</u>       |

|    | 13.6  | Interrupt Controller Registers         | <u>71</u>       |

|    | 13.7  | Usage Notes                            | <u>77</u>       |

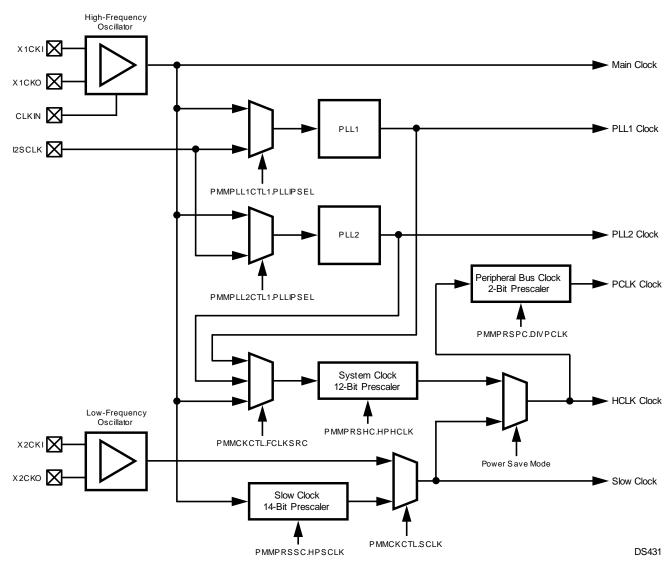

| 14 | Cloc  | k Generation                           | <u>77</u>       |

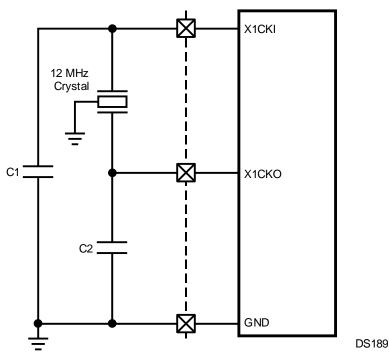

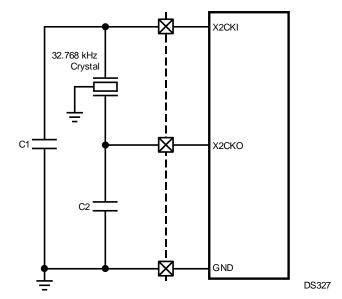

|    | 14.1  | Extrnal Crystal Networks               | <u>78</u>       |

|    | 14.2  | Main Clock                             | <u>80</u>       |

|    | 14.3  | Slow Clock                             | <u>80</u>       |

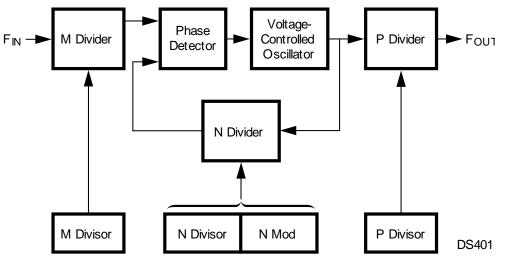

|    | 14.4  | PLL Clocks                             | <u>81</u>       |

|    | 14.5  | HCLK Clock                             | <u>84</u>       |

|    | 14.6  | PCLK Clock                             | <u>84</u>       |

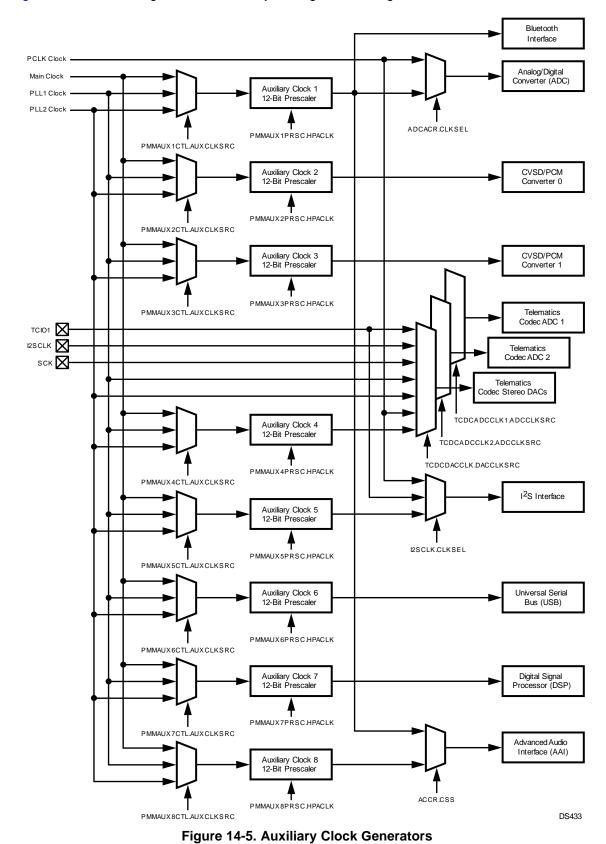

|    | 14.7  | Auxiliary Clocks                       | <u>84</u>       |

|    | 14.8  | Clock Generation Registers             | <u>87</u>       |

| 15 | Rese  | ۰t                                     | <mark>92</mark> |

|    | 15.1  | Power-On Reset                         | <u>92</u>       |

|    | 15.2  | Reset Input Timing                     | <u>92</u>       |

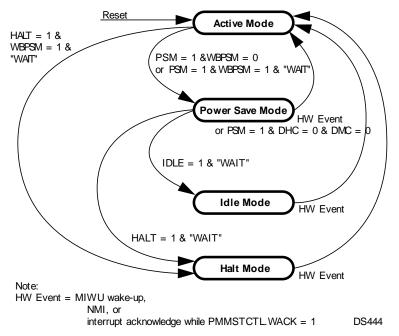

| 16 | Powe  | er Management Module                   | <mark>96</mark> |

|    | 16.1  | Active Mode                            | <u>97</u>       |

|    | 16.2  | Power Save Mode                        | <u>97</u>       |

|    | 16.3  | Idle Mode                              | <u>97</u>       |

|    | 16.4  | Halt Mode                              | <u>98</u>       |

|    | 16.5  | Hardware Clock Control                 | <u>98</u>       |

|    | 16.6  | Switching Between Power Modes          | <u>98</u>       |

|    | 16.7  | Power Management Register              | 101             |

| 17 | Multi | -Input Wake-Up                         | 103             |

|    | 17.1  |                                        | 105             |

| 18 | Input | t/Output Ports                         | 109             |

10.2Default Memory Configuration4410.3External Bus Cycle Timing45

Copyright © 2013, Texas Instruments Incorporated

3

# CP3SP33

SNOSCW5-MAY 2013

|    | 18.1  | Open-Drain Operation                    | <u>111</u> |

|----|-------|-----------------------------------------|------------|

|    | 18.2  | Port Registers                          | <u>111</u> |

| 19 | Blue  | tooth Controller                        | 115        |

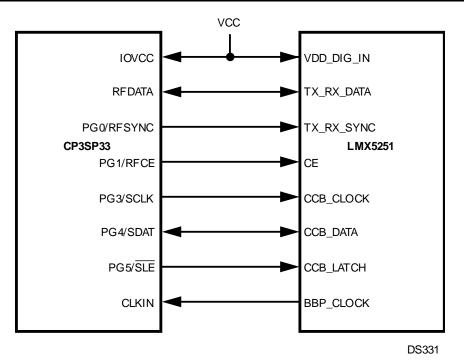

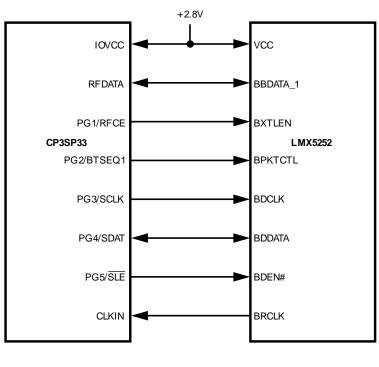

|    | 19.1  | RF Interface                            | 115        |

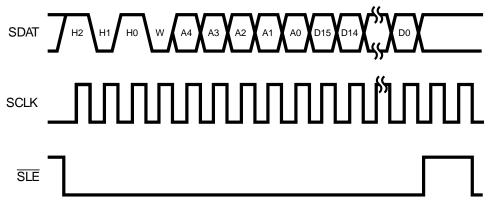

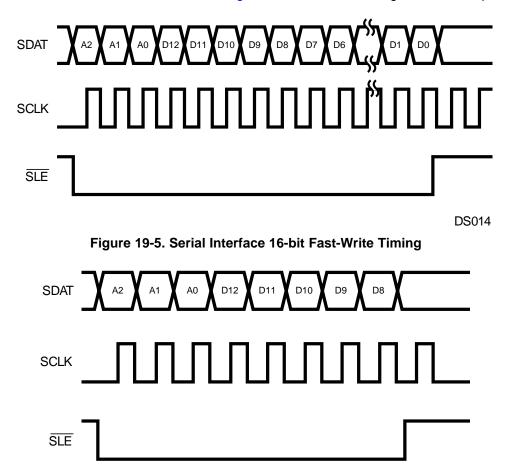

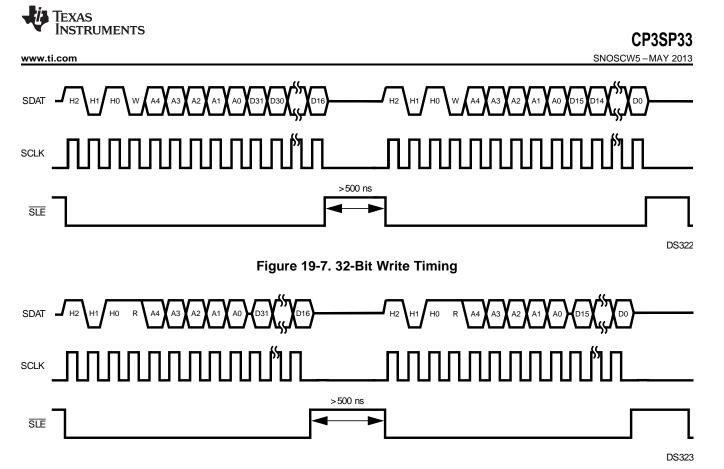

|    | 19.2  | Serial Interface                        | 118        |

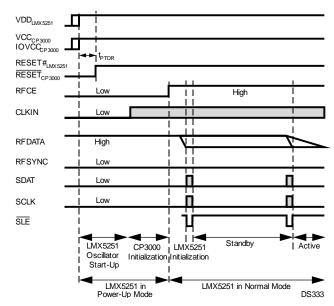

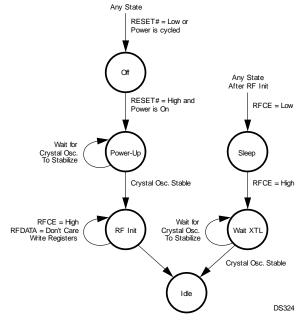

|    | 19.3  | LMX5251 Power-Up Sequence               | 122        |

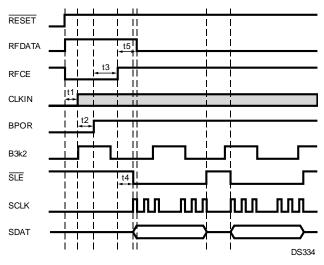

|    | 19.4  | LMX5252 Power-Up Sequence               | 123        |

|    | 19.5  | Bluetooth Sleep Mode                    | 124        |

|    | 19.6  | Bluetooth Global Registers              | 125        |

|    | 19.7  | Bluetooth Sequencer RAM                 | 126        |

|    | 19.8  | Bluetooth Shared Data RAM               | 126        |

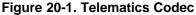

| 20 | Teler | natics Codec                            | 126        |

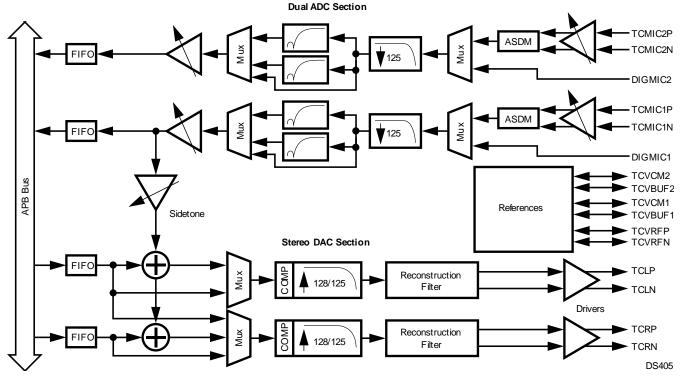

|    | 20.1  | CODEC ADC                               | 127        |

|    | 20.2  | CODEC DAC                               | 128        |

|    | 20.3  | Compensation Filter                     | 128        |

|    | 20.4  | Reconstruction Filter                   | 129        |

|    | 20.5  | Peripheral Bus Interface                | 129        |

|    | 20.6  | Freeze Mode                             | 130        |

|    | 20.7  | Reset                                   | 130        |

|    | 20.8  | DC Protection Monitor                   | 131        |

|    | 20.9  | Sidetone Injection                      | 131        |

|    | 20.10 | Telematics Codec Register Set           | 131        |

|    | 20.11 | Usage Notes                             | 144        |

|    | 20.12 | Tuning the Compensation Filter          | 145        |

|    | 20.13 | Obtaining Maximum DAC SNR               | 145        |

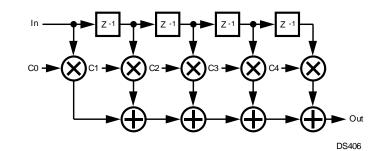

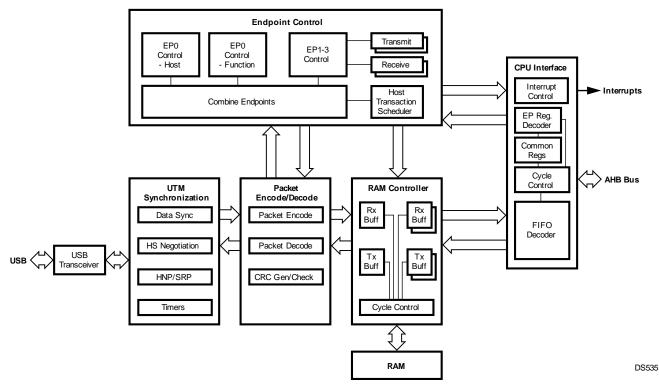

| 21 | USB   | Controller                              | <u>145</u> |

|    | 21.1  | Modes of Operation                      | 146        |

|    | 21.2  | USB Connector Interface                 | 147        |

|    | 21.3  | USB Controller Register Set             | 148        |

| 22 | Dual  | CAN Interfaces                          | <u>166</u> |

|    | 22.1  | Functional Description                  | <u>167</u> |

|    | 22.2  | Basic CAN Concepts                      | 169        |

|    | 22.3  | Message Transfer                        | 182        |

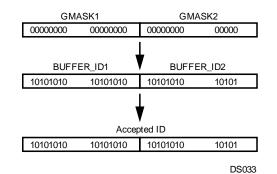

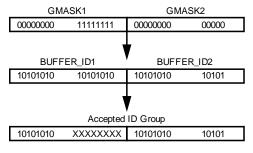

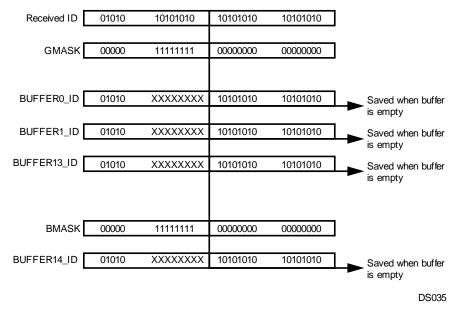

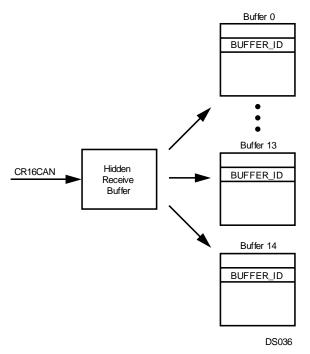

|    | 22.4  | Acceptance Filtering                    | 182        |

|    | 22.5  | Receive Structure                       | <u>184</u> |

|    | 22.6  | Transmit Structure                      | 189        |

|    | 22.7  | Interrupts                              | 192        |

|    | 22.8  | Time Stamp Counter                      | 194        |

|    | 22.9  | Memory Organization                     | 194        |

|    | 22.10 | CAN Controller Registers                | 195        |

|    | 22.11 | System Start-Up and Multi-Input Wake-Up | 209        |

|    | 22.12 | Usage Notes                             | 213        |

| 23 | Anal  | og-to-Digital Converter                 | <u>213</u> |

|    | 23.1  | Funcational Description                 | <u>214</u> |

|    | 23.2  | Operation in Low-Power Modes            | 216        |

|    | 23.3  | Freeze Mode                             | 216        |

|    | 23.4  | ADC Register Set                        | 217        |

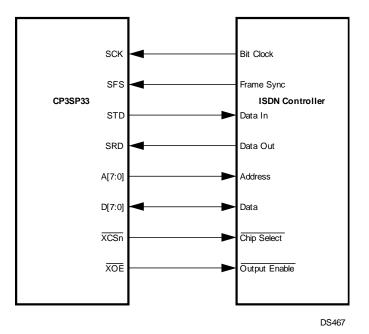

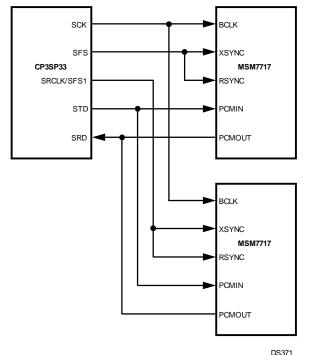

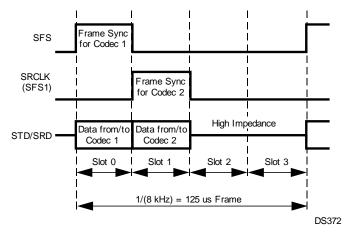

| 24 | Adva  | nced Audio Interface                    | <u>221</u> |

|    | 24.1  | Audio Interface Signals                 | 221        |

|    | 24.2  | Audio Interface Modes                   | 222        |

|    | 24.3  | Bit Clock Generation                    | 227        |

|    | 24.4  | Frame Clock Generation                  | 228        |

|    | 24.5  | Audio Interface Operation               | 228        |

|    |       |                                         |            |

24.6

24.7

24.8

25.1

25.2

25.3

26.1

26.2

26.3

26.4

26.5

26.6

26.7

26.8

26.9

26.10

26.11

26.12

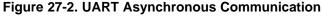

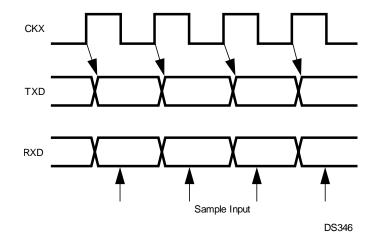

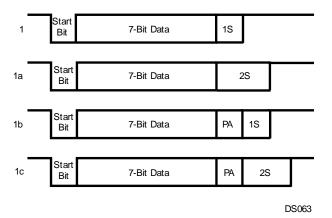

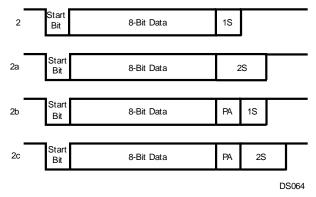

27.1

27.2

27.3

27.4

28.1

28.2

28.3

28.4 28.5

28.6

28.7

29.1

29

25

|    |      | · · · · ·                           |            |

|----|------|-------------------------------------|------------|

|    | 29.3 | Interrupt Support                   | <u>303</u> |

|    | 29.4 | SMA Support                         | 303        |

|    | 29.5 | ACCESS.bus Interface Registers      | <u>303</u> |

|    | 29.6 | Usage Notes                         | 309        |

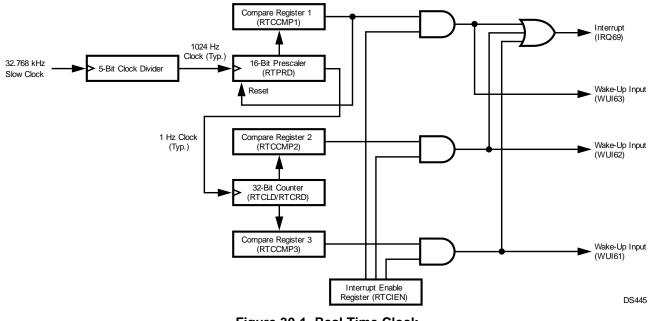

| 30 | Real | Time Clock 3                        | 310        |

|    | 30.1 | Programming                         | 311        |

|    | 30.2 | Interrupt                           | 311        |

|    | 30.3 | Reset                               | 311        |

|    | 30.4 | Real-Time Clock Interface Registers | 311        |

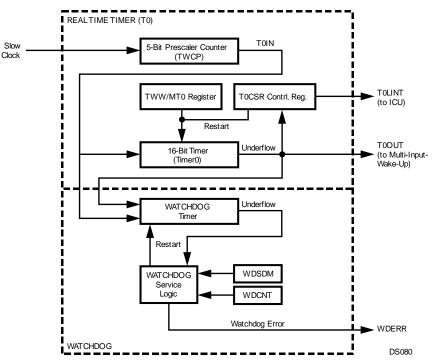

| 31 | Timi | ng and Watchdog Module 3            | 315        |

|    | 31.1 | TWM Structure                       | <u>315</u> |

|    | 31.2 | Timer to Operation                  | 315        |

|    | 31.3 | Watchdog Operation                  | 316        |

|    | 31.4 | TWM Registers                       | 317        |

|    | 31.5 | Watchdog Programming Procedure      | 320        |

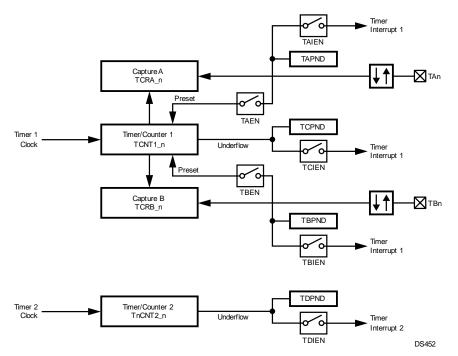

| 32 | Dual | Multi-Function Timers               | 321        |

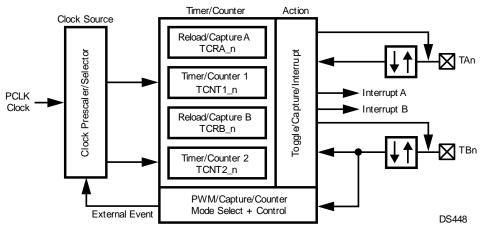

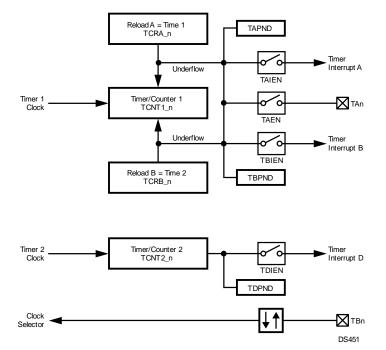

|    | 32.1 | Timer Structure                     | 321        |

4

Copyright © 2013, Texas Instruments Incorporated

#### www.ti.com

|    | 32.2  | Timer Operating Modes                             | <u>323</u> |

|----|-------|---------------------------------------------------|------------|

|    | 32.3  | Timer Interrupts                                  | <u>328</u> |

|    | 32.4  | Timer I/O Functions                               | <u>328</u> |

|    | 32.5  | Timer Registers                                   | <u>329</u> |

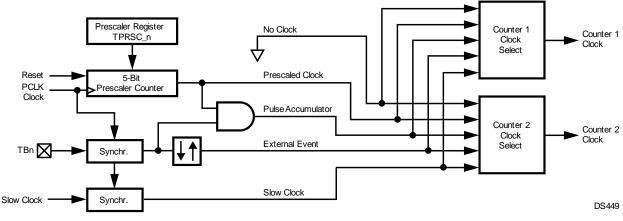

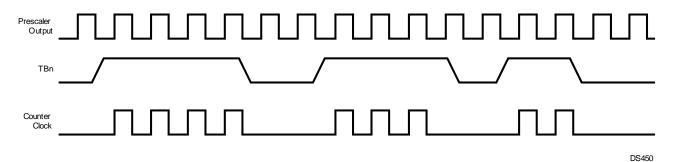

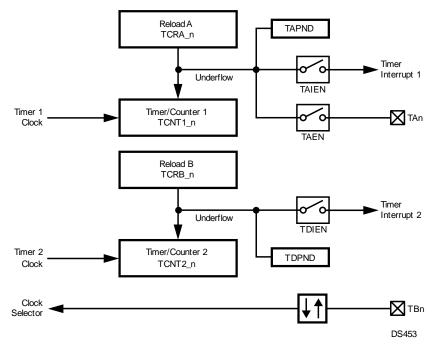

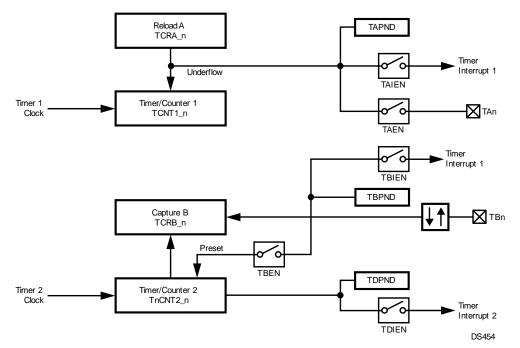

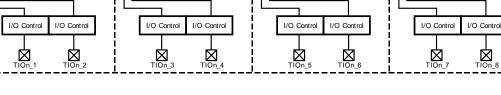

| 33 | Dual  | Versatile Timer Units (VTU)                       | <u>334</u> |

|    | 33.1  | VTU Functional Description                        | <u>334</u> |

|    | 33.2  | VTU Registers                                     | <u>340</u> |

| 34 | Regi  | ster Map                                          | <b>345</b> |

| 35 | Regi  | ster Bit Fields                                   | 361        |

| 36 | Elect | rical Specifications                              | 373        |

|    | 36.1  | Absolute Maximum Ratings                          | 373        |

|    | 36.2  | DC Electrical Characteristics: Temperature: -40°C | ≤          |

|    |       | $T_A \le 85^{\circ}C)$                            | <u>373</u> |

|    | 36.3  | USB Transceiver Electrical Characteristics        | <u>374</u> |

|    | 36.4  | Telematics Codec Electrical Characteristics       | <u>375</u> |

|    | 36.5  | ADC Electrical Characteristics                    | <u>376</u> |

|    |       |                                                   |            |

|    | 36.6  | Output Signal Levels                               | <u>376</u> |

|----|-------|----------------------------------------------------|------------|

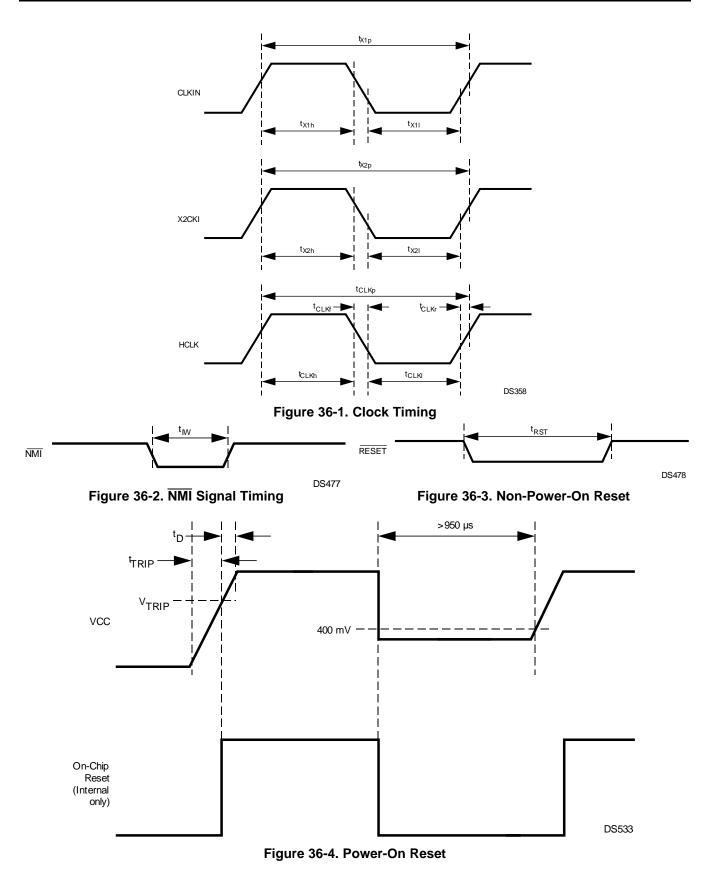

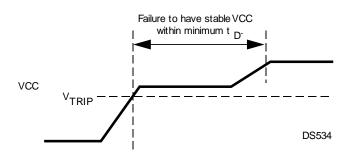

|    | 36.7  | Clock and Reset Timing                             | <u>377</u> |

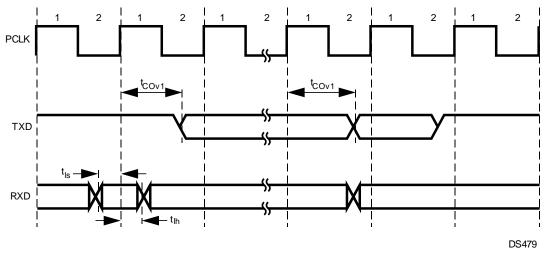

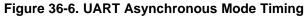

|    | 36.8  | UART Timing                                        | <u>379</u> |

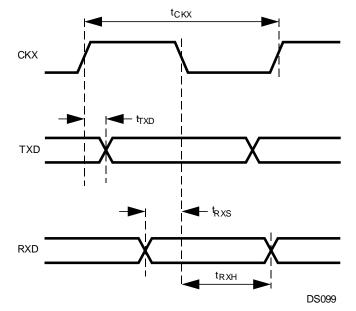

|    | 36.9  | I/O Port Timing                                    | <u>380</u> |

|    | 36.10 | Advanced Audio Interface (AAI) Timing              | <u>381</u> |

|    | 36.11 | Microwire/SPI Timing                               | 383        |

|    | 36.12 | ACCESS.BUS Timing                                  | 386        |

|    | 36.13 | USB Port AC Characteristics                        | 389        |

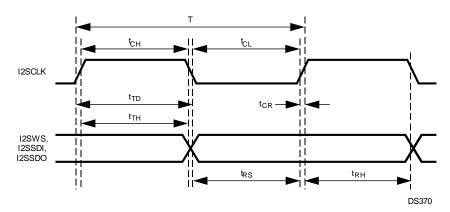

|    | 36.14 | I <sup>2</sup> S Interface Timing                  | 389        |

|    | 36.15 | Multi-Function Timer (MFT) Timing                  | 390        |

|    | 36.16 | Versatile Timing Unit (VTU) Timing                 | 390        |

|    | 36.17 | External Memory Interface                          | 390        |

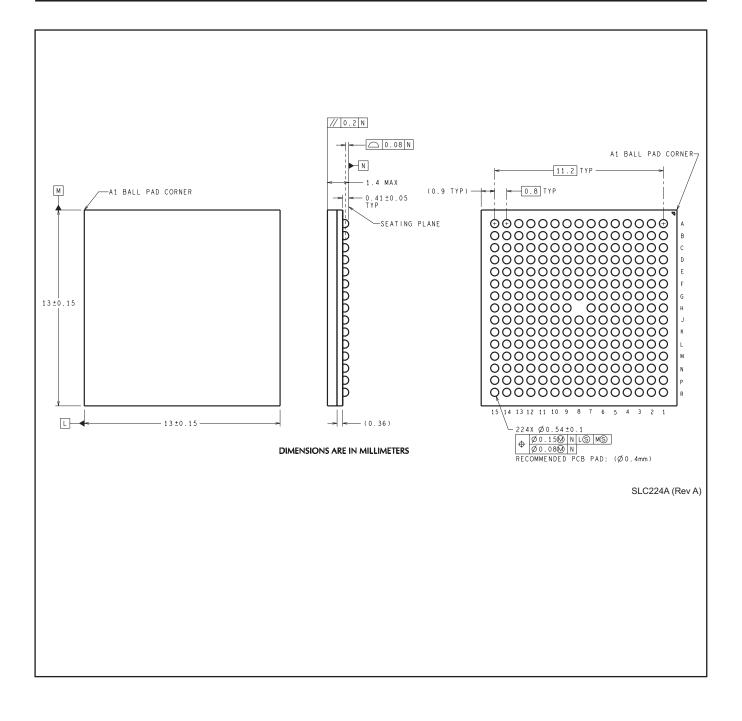

| 37 | Pin A | Assignments                                        | 392        |

|    | 37.1  | Physical Dimensions (millimeters) unless otherwise | ;          |

|    |       | noted                                              | <u>401</u> |

|    |       |                                                    |            |

SNOSCW5-MAY 2013

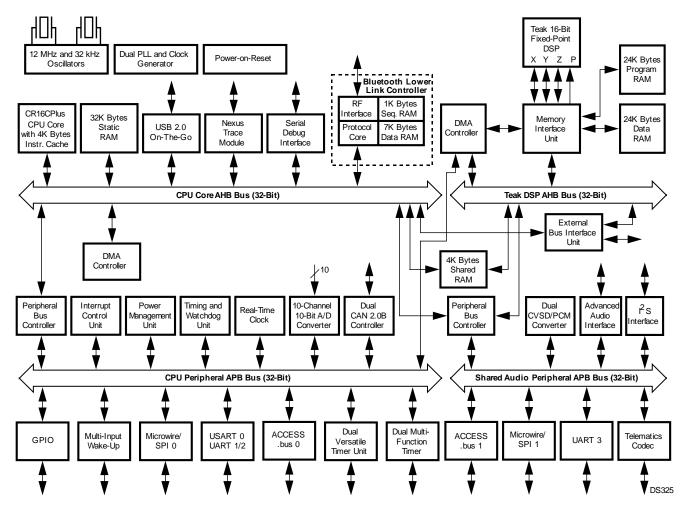

#### 2 Description

The CP3SP33 connectivity processor combines high performance with the massive integration needed for embedded Bluetooth applications. A powerful RISC core with 4Kbyte instruction cache and a Teak<sup>®</sup> DSP coprocessor provides high computing bandwidth, DMA-driven hardware communications peripherals provide high I/O bandwidth, and an external bus provides system expandability.

On-chip communications peripherals include: Bluetooth Lower Link Controller, Universal Serial Bus (2.0) OTG node and host controller, dual CAN, dual Microwire/Plus/SPI, dual ACCESS.bus, quad UART, 10-bit A/D converter, and telematics/audio codec. Additional on-chip peripherals include DMA controller, dual CVSD/PCM conversion module, I<sup>2</sup>S and AAI digital audio bus interfaces, Timing and Watchdog Unit, dual Versatile Timer Unit, dual Multi-Function Timer, and Multi-Input Wake-Up (MIWU) unit.

In addition to providing the features needed for the next generation of embedded Bluetooth products, the CP3SP33 is backed up by the software resources that designers need for rapid time-to-market, including an operating system, Bluetooth protocol stack implementation, peripheral drivers, reference designs, and an integrated development environment. Combined with an external program memory and a Bluetooth radio transceiver such as National's LMX5252, the CP3SP33 provides a complete Bluetooth system solution.

National Semiconductor offers a complete and industry proven application development environment for CP3SP33 applications, including the IAR Embedded Workbench, iSYSTEM winIDEA and iC3000 Active Emulator, Bluetooth Development Board, Bluetooth protocol stack, and application examples.

#### 2.1 Block Diagram

#### 3 Device Overview

The CP3SP33 connectivity processor is an advanced microcomputer with system timing, interrupt logic, instruction cache, data memory, and I/O ports included on-chip, making it well-suited to a wide range of embedded applications. The Section 2.1 shows the major on-chip components of the CP3SP33.

#### 3.1 CR16CPlus CPU Core

The CP3SP33 contains a CR16CPlus CPU core. This core improves upon the performance of previous CP3000 devices by adding a 4-Kbyte instruction cache and doubling the CPU core data bus bandwidth. The cache greatly reduces instruction-fetch bandwidth on the 32-bit system bus, which leaves more bus bandwidth available for DMA-based I/O. The cache moves the average execution rate closer to the peak rate of one instruction per clock cycle, especially when executing from off-chip program memory. The DMA controller provides efficient sharing of the CPU core bus between the CPU and high-bandwidth peripherals such as wired and wireless communication interfaces.

For information on the instruction set architecture, refer to the *CR16C Programmer's Reference Manual* (document number 424521772-101, which may be downloaded from Texas Instruments web site at <a href="http://www.ti.com">http://www.ti.com</a>).

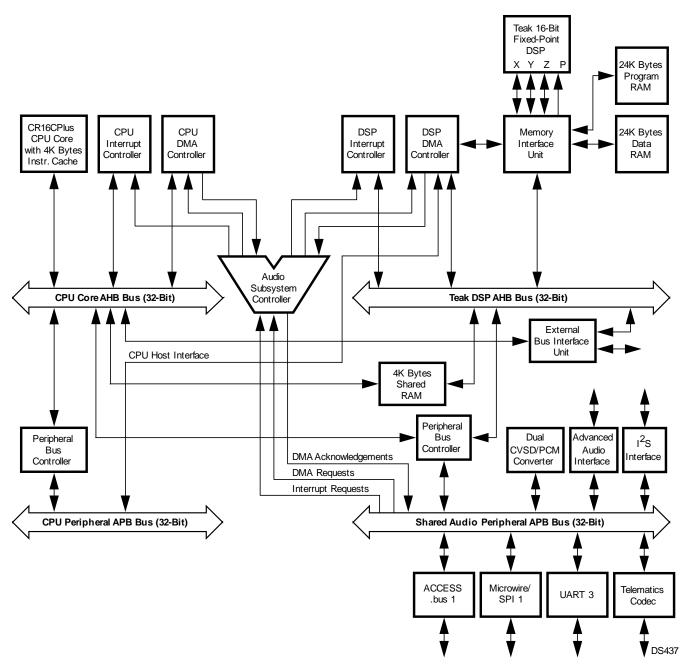

#### 3.2 Teak DSP Core

The Teak 16-bit fixed-point DSP core is designed for lowpower, high-speed digital signal processing applications, including acoustic echo cancellation, noise reduction, and MP3/WMA decoding. It features a four-bus, dual-MAC, enhanced Harvard architecture. The DSP has 24K bytes of dedicated program RAM, 24K bytes of data RAM, and a 4K-byte RAM shared with the CPU. The DSP has a bus master interface to the 4K-byte shared RAM and an external memory bus. It also has a bus master interface to a shared audio peripheral bus. The DSP is slave on the CPU peripheral bus, for downloading software to the program RAM.

The DSP has its own DMA controller for I/O and memory access.

#### 3.3 AMBA Bus Architecture

The CPU and DSP core buses implement AMBA-compatible AHB high-performance 32-bit buses with bursting and split transactions. The CPU peripheral bus and CPU/DSP shared audio peripheral bus implement AMBA-compatible 32-bit APB buses. The CPU and DSP buses operate at independent rates up to 96 MHz. The APB buses operate at a rate which is a factor of 1, 2, or 4 slower than the CPU AHB bus.

#### 3.4 External Bus Interface Unit

The External Bus Interface Unit (EBIU) provides programmable timing, memory type, base address, size, and bus width (8, 16, or 32 bits) for three regions of up to 32M bytes. An 8-level write buffer releases the bus master to continue execution without waiting for write cycles to complete.

#### 3.5 Memory

The CP3SP33 devices support a uniform linear address space. Three types of on-chip memory occupy specific regions within this address space, along with any external memory:

- 32K bytes of CPU RAM

- 4K bytes of CPU/DSP shared RAM

- 8K bytes of Bluetooth sequencer and data RAM

- Up to 96M bytes of external memory

A non-volatile external program memory is used to store the application program, Bluetooth protocol stack, and real-time operating system.

The 32K bytes of CPU RAM are used for temporary storage of data and for the program stack and interrupt stack. Read and write operations can be byte-wide or word-wide, depending on the instruction executed by the CPU.

#### 3.6 Bluetooth LLC

The integrated hardware Bluetooth Lower Link Controller (LLC) complies to the Bluetooth Specification Version 1.2 and integrates the following functions:

- 7K-byte dedicated Bluetooth data RAM

- 1K-byte dedicated Bluetooth sequencer RAM

- Support of all Bluetooth 1.2 packet types and extended Synchronous Connection-Oriented (eSCO) links

- Support for fast frequency hopping of 1600 hops/s

- Access code correlation and slot timing recovery circuit

- Power Management Control Logic

- BlueRF-compatible interface (mode 2/3) to connect with National's LMX5252 and other RF transceiver chips

#### 3.7 USB

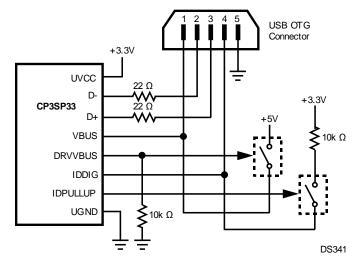

The full-speed Universal Serial Bus (USB) node and host controller is compatible with USB Specification 2.0 and USB On-The-Go. It integrates the required USB transceiver, the Serial Interface Engine (SIE), and USB endpoint FIFOs. A total of seven endpoint pipes are supported: one bidirectional pipe for the mandatory control EP0 and an additional six pipes for unidirectional endpoints to support USB interrupt, bulk, and isochronous data transfers.

The on-chip USB transceiver features an integrated pullup resistor on the D+ line to UVCC. This pullup resistor can be switched in or out by the USB VBUS sense input (VBUS), which eliminates the need for external components.

#### 3.8 CAN Interface

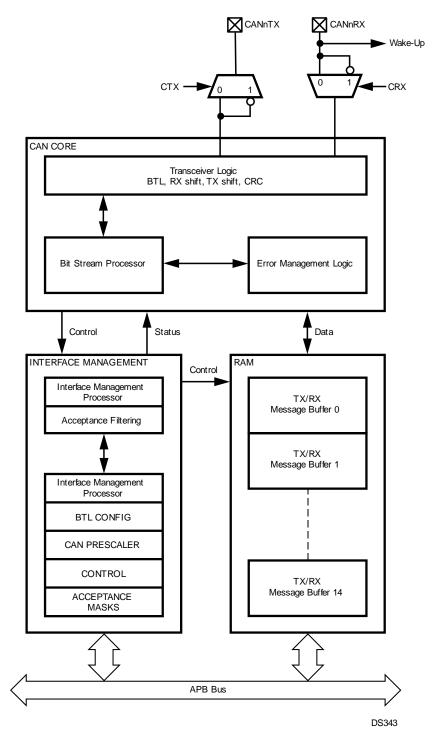

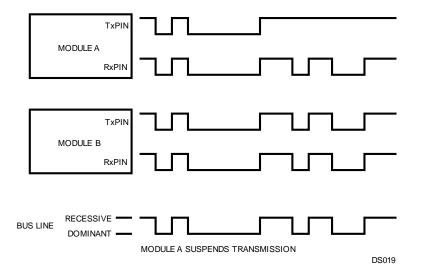

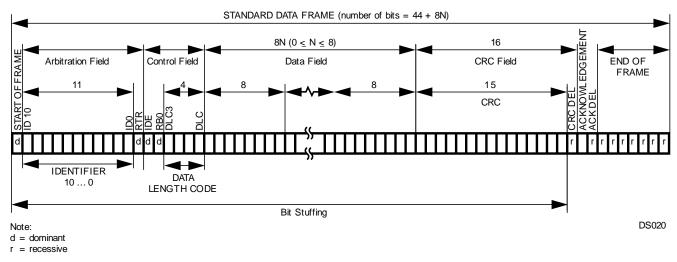

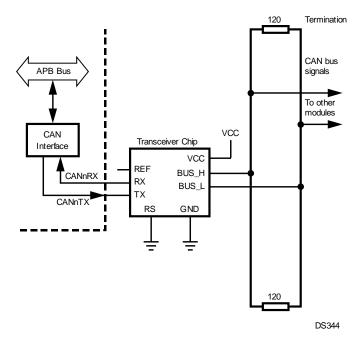

The two CAN modules support Full CAN 2.0B class, CAN serial bus interfaces for applications that require a highspeed (up to 1 Mbits per second) or a low-speed interface with CAN bus master capability. The data transfer between CAN and the CPU is established by 15 memory-mapped message buffers, which can be individually configured as receive or transmit buffers. An incoming message is filtered by two masks, one for the first 14 message buffers and another one for the 15th message buffer to provide a basic CAN path. A priority decoder allows any buffer to have the highest or lowest transmit priority. Remote transmission requests can be processed automatically by automatic reconfiguration to a receiver after transmission or by automated transmit scheduling upon reception. In addition, a 16-bit time stamp counter supports real-time applications.

The CAN modules allow single-cycle byte or word read/ write access. A set of diagnostic features (such as loopback, listen only, and error identification) support the development with the CAN modules and provide a sophisticated error management tool.

The CAN receivers can trigger a wake-up condition out of low-power modes through the Multi-Input Wake-Up unit.

#### 3.9 Audio/Telematics Codec

The on-chip codec is designed for voice input and stereo audio playback. It includes dual mono ADC channels operating at a sample rate of 8–24 kHz (125× oversampling clock required). A stereo DAC operates at selected sample rates from a 125× or 128× oversampling clock, driving two configurable, gain-programmable differential line driver outputs. The DAC features click and pop reduction, zero-crossing detection, tone/compensation filter, sidetone injection from the ADC, and internal power management. The ADCs accept differential or single-ended analog microphone inputs. The DAC employs fully differential signaling for high PSRR and low crosstalk. DMA transfers are supported to allow for fast CPU-independent receive and transmit.

### 3.10 CVSD/PCM Conversion Modules

The two CVSD/PCM modules perform conversion between CVSD data and PCM data, in which the CVSD encoding is as defined in the Bluetooth specification and the PCM data can be 8-bit  $\mu$ -Law, 8-bit A-Law, or 13-bit to 16-bit Linear.

#### 3.11 I<sup>2</sup>S Digital Audio Bus

The Inter-IC Sound ( $l^2S$ ) interface is a synchronous serial interface intended for the transfer of digital audio data. The  $l^2S$  interface can be configured as a master or a slave, and it supports all three common data formats:  $l^2S$ -mode, left-justified, and right-justified. It has programmable word length from 8 to 32 bits and programmable valid data resolution from 8 to 24 bits.

#### 3.12 Advanced Audio Interface

The Advanced Audio Interface (AAI) provides a serial synchronous, full-duplex interface to codecs and similar serial devices. Transmit and receive paths operate asynchronously with respect to each other. Each path uses three signals for communication: shift clock, frame synchronization, and data.

When the receiver and transmitter use external shift clocks and frame sync signals, the interface operates in its asynchronous mode. Alternatively, the transmit and receive path can share the same shift clock and frame sync signals for synchronous mode operation.

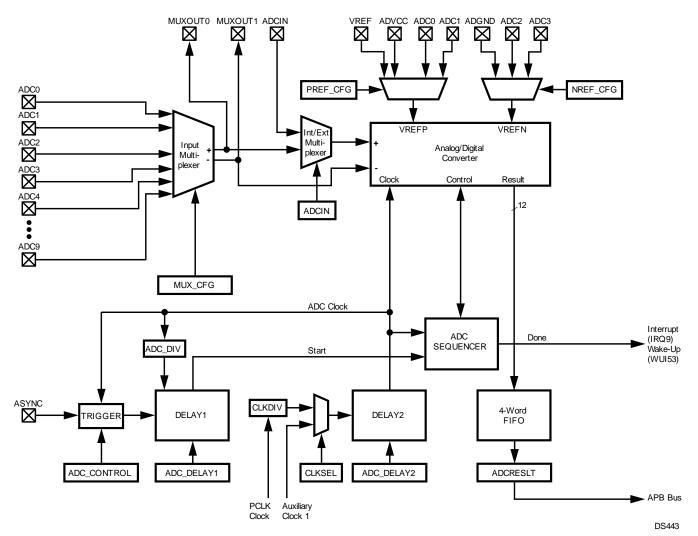

### 3.13 Analog to Digital Converter

This device contains a 10-channel, multiplexed input, successive approximation, 10-bit Analog-to-Digital Converter. It supports both single-ended and differential modes of operation.

The integrated 10-bit ADC provides the following features:

- 10-channel, multiplexed input

- 5 differential channels

- Single-ended and differential external filtering capability

- 12-bit resolution; 10-bit accuracy

- Sign bit

- 10-microsecond conversion time

- External start trigger

- Programmable start delay after start trigger

- Poll or interrupt on conversion completion

The ADC provides several options for the voltage reference source. The positive reference can be ADVCC (internal), VREF, ADC0, or ADC1. The negative reference can be AD-VCC (internal), ADC2, or ADC3.

Two specific analog channel selection modes are supported. These are as follows:

Allow any specific channel to be selected at one time. The A/D Converter performs the specific conversion requested and stops. • Allow any differential channel pair to be selected at one time. The A/D Converter performs the specific differential conversion requested and stops.

In both single-ended and differential modes, there is the capability to connect the analog multiplexer output and A/D converter input to external pins. This provides the ability to externally connect a common filter/signal conditioning circuit for the A/D Converter.

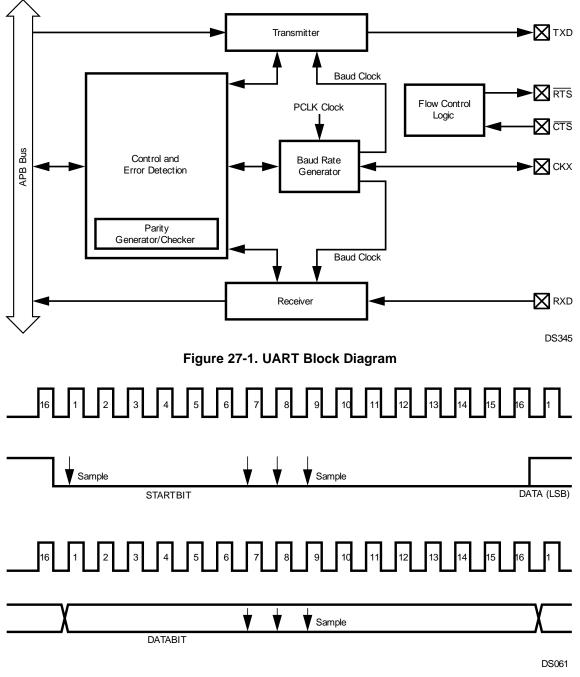

#### 3.14 Quad UART

Four UART modules support a wide range of programmable baud rates and data formats, parity generation, and several error detection schemes. The baud rate is generated on-chip, under software control. All UART modules support DMA and hardware flow control. One module has USART capability (synchronous mode). The maximum speed is 3.072 Mbaud in either synchronous or asynchronous mode.

The UARTs offer a wake-up condition from the low-power modes using the Multi-Input Wake-Up module.

#### 3.15 Microwire/SPI

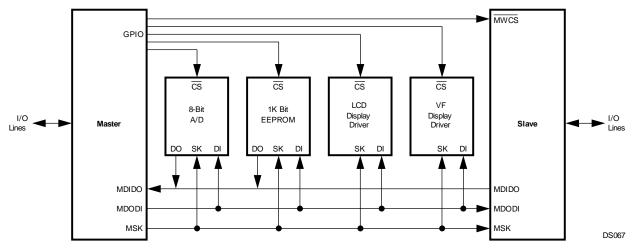

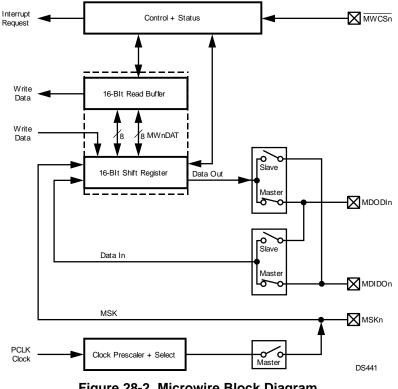

The two Microwire/SPI (MWSPI) interface modules support synchronous serial communications with other devices that conform to Microwire or Serial Peripheral Interface (SPI) specifications. It supports 8-bit and 16-bit data transfers. The maximum bus clock frequency is 12 MHz.

The Microwire interfaces allows several devices to communicate over a single system consisting of four wires: serial in, serial out, shift clock, and slave enable. At any given time, the Microwire interfaces operate as a master or a slave. The Microwire interfaces supports the full set of slave select for multi-slave implementation.

In master mode, the shift clock is generated on-chip under software control. In slave mode, a wake-up out of a low-power mode may be triggered using the Multi-Input WakeUp module.

#### 3.16 Dual ACCESS.BUS Interface

The two ACCESS.bus (ACB) interface modules support a two-wire serial interface compatible with the ACCESS.bus physical layer. It is also compatible with Intel's System Management Bus (SMBus) and Philips' I<sup>2</sup>C bus. The ACB modules can be configured as a bus master or slave, and they can maintain bidirectional communications with both multiple master and slave devices. The maximum bus clock frequency is 400 kHz (Fast-mode).

The ACCESS.bus receivers can trigger a wake-up condition out of the low-power modes through the Multi-Input Wake-Up module.

#### 3.17 Dual Multi-Function Timer

The two Multi-Function Timer (MFT) modules each contain a pair of 16-bit timer/counter registers. Each timer/counter unit can be configured to operate in any of the following modes:

- *Processor-Independent Pulse Width Modulation (PWM) mode:* Generates pulses of a specified width and duty cycle and provides a general-purpose timer/ counter.

- *Dual Input Capture mode:* Measures the elapsed time between occurrences of external event and provides a general-purpose timer/counter.

- *Dual Independent Timer mode:* Generates system timing signals or counts occurrences of external events.

- Single Input Capture and Single Timer mode: Provides one external event counter and one system timer.

#### 3.18 Versatile Timer Units

The two Versatile Timer Unit (VTU) modules each contain four independent timer subsystems, which operate as a dual 8-bit PWM configuration, a single 16-bit PWM timer, or a 16-bit counter with two input capture channels. Each of the timer subsystems offer an 8-bit clock prescaler to accommodate a wide range of frequencies.

#### 3.19 Timing and Watchdog Module

The Timing and Watchdog Module (TWM) contains a Real-Time timer and a Watchdog unit. The Real-Time Clock Timing function can be used to generate periodic real-time based system interrupts. The timer output is one of 16 inputs to the Multi-Input Wake-Up module which can be used to exit from a low-power mode. The Watchdog unit is designed to detect the application program getting stuck in an infinite loop resulting in loss of program control or "runaway" programs. When the watchdog triggers, it resets the device. The TWM is clocked by the low-speed Slow Clock.

#### 3.20 Power Management

The Power Management Module (PMM) improves the efficiency of the device by changing the operating mode and power consumption to match the required level of activity.

The device can operate in any of four power modes:

- *Active:* The device operates at full speed using the high-frequency clock. All device functions are fully operational.

- *Power Save:* The device operates at reduced speed using the Slow Clock. The CPU and some modules can continue to operate at this low speed.

- *Idle:* The device is inactive except for the Power Management Module and Timing and Watchdog Module, which continue to operate using the Slow Clock.

- Halt: The device is inactive but still retains its internal state (RAM and register contents).

The PMM provides a mechanism to handle Bluetooth-specific power management modes, for optimizing power consumption during special Bluetooth states, like Park, Page Scan, Inquiry Scan, etc.

#### 3.21 Multi-Input Wake-up

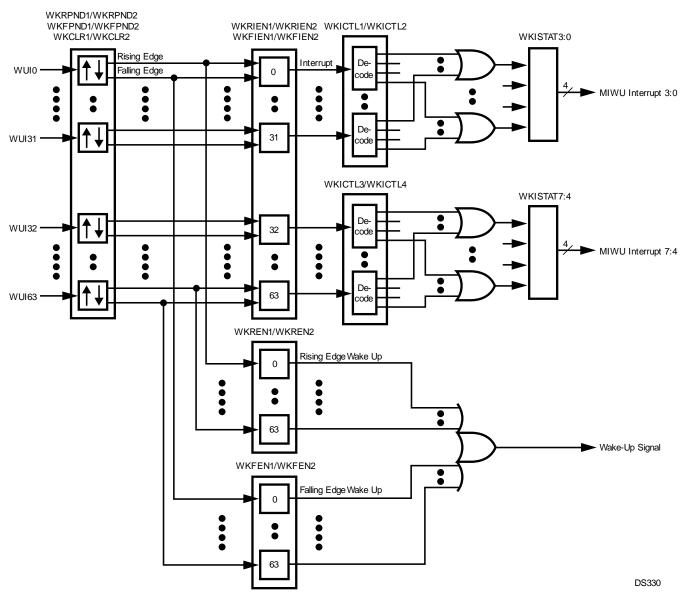

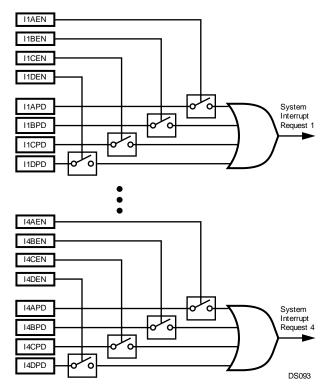

The Multi-Input Wake-Up (MIWU) feature is used to return (wake-up) the device from low-power modes to the active mode. The 64-channel MIWU unit receives wake-up signals from various internal and external sources. In addition to the wake-up function, the MIWU unit can generate up to eight interrupt requests. Each MIWU channel can be individually programmed to activate one of the interrupt requests.

#### 3.22 Input/Output Ports

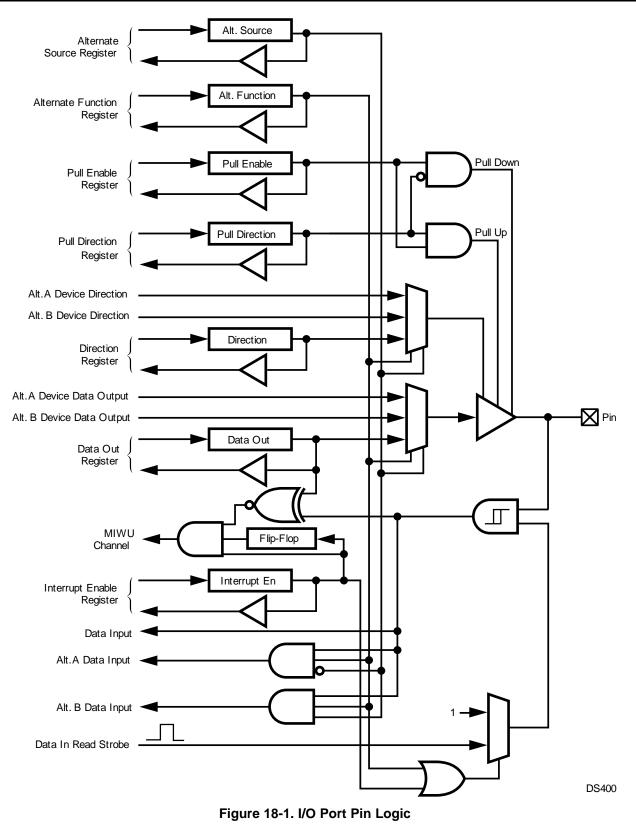

The device has 64 software-configurable I/O pins (36 in the FBGA-144 package), organized into four ports called Port E, Port F, Port G, and Port H. Each pin can be configured to operate as a general-purpose input or general-purpose output. In addition, many I/O pins can be configured to operate as inputs or outputs for on-chip peripheral modules such as the UARTs or timers.

The I/O pin characteristics are fully programmable. Each pin can be configured to operate as a TRI-STATE output, push-pull output, weak pullup/pulldown input, high-speed drive, or high-impedance input.

#### 3.23 Clock and Reset Module

The Clock and Reset module generates a 12-MHz Main Clock from an external crystal network or external clock in-put. Main Clock may be used as a reference clock for two PLL-based clock multipliers available for generating higher-speed clocks.

Most modules operate from clocks derived from Main Clock or a PLL clock. Modules on the CPU core AHB bus operate from HCLK Clock, while modules on the peripheral APB buses operate from PCLK Clock. PCLK Clock is generated by dividing HCLK Clock by 1, 2, or 4. Some peripheral modules may use one of several auxiliary clocks, which also are derived from Main Clock or a PLL clock using 12-bit programmable prescalers.

In Power-Save mode, HCLK Clock is driven by Slow Clock, which is typically a 32.768 kHz signal generated from an external clock network or a prescaled Main Clock may be used to eliminate the 32.768 kHz crystal network, for the most cost-sensitive applications. In the most power-sensitive applications, operation from an external 32.768 kHz crystal network allows the high-frequency oscillator and PLLs to be shut down.

In addition, the Clock and Reset module generates the device reset by using reset input signals coming from an external reset, the watchdog timer, or the SDI debugging interface. A power-on reset (POR) circuit eliminates the need for an external RC network. The POR circuit generates an internal reset of sufficient length if the power supply rise time specification is met.

#### 3.24 DMA Controller

The Direct Memory Access Controller (DMAC) can speed up data transfer between memory and I/O devices or between two regions of memory, as compared to data transfers performed directly by the CPU. Cycle stealing allows the CPU and the DMAC to interleave access to the CPU core bus for greater utilization of the available bandwidth. The following on-chip modules can assert a DMA request to the DMA controller:

- USART 0 (2 request channels)

- UART 1/2/3 (6 request channels

- Advanced Audio Interface (6 request channels)

- CVSD/PCM Converter 0/1 (8 request channels)

- Microwire/SPI 0/1 (4 request channels)

- ACCESS.bus 0/1 (2 request channels)

- Codec (4 request channels)

- I2S Interface (4 request channels)

The DSP has its own DMA controller which can be configured to accept DMA requests from peripherals on the shared audio peripheral APB bus.

#### 3.25 Serial Debug Interface

The Serial Debug Interface module (SDI module) provides a JTAG-based serial link to an external debugger, for example running on a PC. In addition, the SDI module integrates an on-chip debug module, which allows the user to set up to eight hardware breakpoints on instruction execution and data transfer. The SDI module can act as a CPU bus master to access all memory-mapped resources, such as RAM and peripherals. Therefore it also allows for fast program code download using the JTAG interface.

#### 3.26 Development Support

In addition to providing the features needed for the next generation of embedded Bluetooth products, the CP3SP33 devices are backed up by the software resources that designers need for rapid product development, including an operating system, Bluetooth protocol stack implementation, peripheral drivers, reference designs, and an integrated development environment. Combined with National's LMX5252 Bluetooth radio transceiver, the CP3SP33 devices provide a total Bluetooth system solution.

Texas Instruments offers a complete and industry-proven application development environment for CP3SP33 applications, including the IAR Embedded Workbench, iSYSTEM winIDEA and iC3000 Active Emulator, Bluetooth Development Board, Bluetooth Protocol Stack, and Application Software. See your Texas Instruments sales representative for current information on availability and features of emulation equipment and evaluation boards.

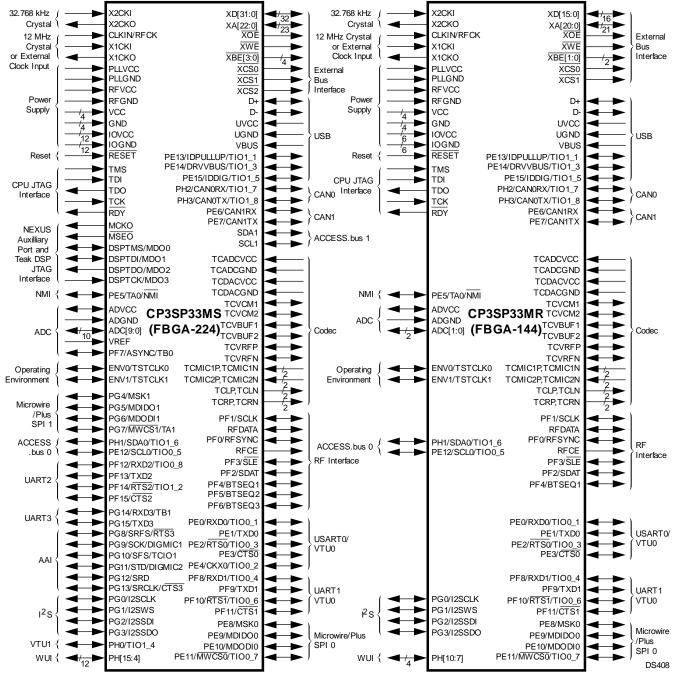

# 4 Signal Descriptions

Some pins may be enabled as general-purpose I/O-port pins or as alternate functions associated with specific peripherals or interfaces. These pins may be individually configured as port pins, even when the associated peripheral or interface is enabled.

Table 4-1 describes the device signals. When the number of signals differs between packages, the first number in the Pins column is for the FBGA-224 package and the second number is for the FBGA-144 package.

| NAME         | PINS | I/O    | PRIMARY FUNCTION                                               | ALTERNATE<br>NAME | I/O    | ALTERNATE FUNCTION      |

|--------------|------|--------|----------------------------------------------------------------|-------------------|--------|-------------------------|

| CLKIN        | 1    | Input  | 12 MHz Clock Input                                             | RFCK              | Input  | RF Interface Clock      |

| X1CKI        | 1    | Input  | 12 MHz Oscillator Input                                        | None              | None   | None                    |

| X1CKO        | 1    | Output | 12 MHz Oscillator Output                                       | None              | None   | None                    |

| X2CKI        | 1    | Input  | 32 kHz Oscillator Input                                        | None              | None   | None                    |

| X2CKO        | 1    | Output | 32 kHz Oscillator Output                                       | None              | None   | None                    |

| RESET        | 1    | Input  | Chip general reset                                             | None              | Input  | None                    |

| ENV0         | 1    | Input  | Special mode select input with internal<br>pullup during reset | TSTCLK0           | Output | Internal Clock Output   |

| ENV1         | 1    | Input  | Special mode select input with internal pullup during reset    | TSTCLK1           | Output | Internal Clock Output   |

| VCC          | 4    | Input  | Core Logic, 1.8V Power Supply                                  | None              | None   | None                    |

| GND          | 4    | Input  | Core Ground                                                    | None              | None   | None                    |

| IOVCC        | 12/6 | Input  | I/O 3.3V Power Supply                                          | None              | None   | None                    |

| IOGND        | 12/6 | Input  | I/O Ground                                                     | None              | None   | None                    |

| PLLVCC       | 1    | Input  | PLL 1.8V Power Supply                                          | None              | None   | None                    |

| PLLGND       | 1    | Input  | PLL Ground                                                     | None              | None   | None                    |

| ADVCC        | 1    | Input  | ADC 1.8V Power Supply                                          | None              | None   | None                    |

| ADGND        | 1    | Input  | ADC Ground                                                     | None              | None   | None                    |

| TCDACVC<br>C | 1    | Input  | Codec 3.3V Power Supply                                        | None              | None   | None                    |

| TCDACGN<br>D | 1    | Input  | Codec 3.3V Ground                                              | None              | None   | None                    |

| TCADCVC<br>C | 1    | Input  | Codec 1.8V Power Supply                                        | None              | None   | None                    |

| TCADCGN<br>D | 1    | Input  | Codec 1.8V Ground                                              | None              | None   | None                    |

| RFVCC        | 1    | Input  | RF Interface Power Supply                                      | None              | None   | None                    |

| RFGND        | 1    | Input  | RF Interface Ground                                            | None              | None   | None                    |

| UVCC         | 1    | Input  | USB 3.3V Transceiver Supply                                    | None              | None   | None                    |

| UGND         | 1    | Input  | USB 3.3V Transceiver Ground                                    | None              | None   | None                    |

| TMS          | 1    | Input  | CPU JTAG Test Mode Select (with internal weak pullup)          | None              | None   | None                    |

| ТСК          | 1    | Input  | CPU JTAG Test Clock Input (with internal weak pullup)          | None              | None   | None                    |

| TDI          | 1    | Input  | CPU JTAG Test Data Input (with internal weak pullup)           | None              | None   | None                    |

| TDO          | 1    | Output | CPU JTAG Test Data Output                                      | None              | None   | None                    |

| RDY          | 1    | Output | NEXUS Ready Output                                             | None              | None   | None                    |

| МСКО         | 1/0  | Output | NEXUS Trace Clock Output                                       | None              | None   | None                    |

| MSEO         | 1/0  | Output | NEXUS Trace End of Message Output                              | None              | None   | None                    |

| DSPTMS       | 1/0  | Input  | DSP JTAG Test Mode Select (with internal weak pullup)          | MDO0              | Output | NEXUS Trace Data Output |

| DSPTDI       | 1/0  | Input  | DSP JTAG Test Data Input (with internal weak pullup)           | MDO1              | Output | NEXUS Trace Data Output |

| DSPTDO       | 1/0  | Output | DSP JTAG Test Data Output                                      | MDO2              | Output | NEXUS Trace Data Output |

| DSPTCK       | 1/0  | Input  | DSP JTAG Test Clock Input (with internal weak pullup)          | MDO3              | Output | NEXUS Trace Data Output |

| RFDATA       | 1    | I/O    | RF Interface Data                                              | None              | None   | None                    |

| RFCE         | 1    | Output | RF Interface Chip Enable                                       | None              | None   | None                    |

| VBUS         | 1    | Input  | USB VSENSE (5V tol.)                                           | None              | None   | None                    |

|            |      |        |                                                                                    | 1                 | ,      |                                |

|------------|------|--------|------------------------------------------------------------------------------------|-------------------|--------|--------------------------------|

| NAME       | PINS | I/O    | PRIMARY FUNCTION                                                                   | ALTERNATE<br>NAME | I/O    | ALTERNATE FUNCTION             |

| D+         | 1    | I/O    | USB D+ Upstream Port                                                               | None              | None   | None                           |

| D-         | 1    | I/O    | USB D– Upstream Port                                                               | None              | None   | None                           |

| ADC0       | 1    | Input  | ADC Input Channel 0                                                                | None              | None   | None                           |

| ADC1       | 1    | Input  | ADC Input Channel 1                                                                | None              | None   | None                           |

| ADC2       | 1/0  | Input  | ADC Input Channel 2                                                                | None              | None   | None                           |

| ADC3       | 1/0  | Input  | ADC Input Channel 3                                                                | None              | None   | None                           |

| ADC4       | 1/0  | Input  | ADC Input Channel 4                                                                | MUXOUT0           | Output | Analog Multiplexer Output 0    |

| ADC5       | 1/0  | Input  | ADC Input Channel 5                                                                | MUXOUT1           | Output | Analog Multiplexer Output 1    |

| ADC6       | 1/0  | Input  | ADC Input Channel 6                                                                | None              | None   | None                           |

| ADC7       | 1/0  | Input  | ADC Input Channel 7                                                                | ADCIN             | Input  | ADC Input (in MUX mode)        |

| ADC8       | 1/0  | Input  | ADC Input Channel 8                                                                | None              | None   | None                           |

| ADC9       | 1/0  | Input  | ADC Input Channel 9                                                                | None              | None   | None                           |

| VREF       | 1/0  | Input  | ADC Voltage Reference                                                              | None              | None   | None                           |

| TCVBUF1    | 1    | Input  | Codec ADC1 External Filter Capacitor Pin<br>(1.5V)                                 | None              | None   | None                           |

| TCVBUF2    | 1    | Input  | Codec ADC2 External Filter Capacitor Pin<br>(1.5V)                                 | None              | None   | None                           |

| TCVCM1     | 1    | Input  | Codec ADC1 External Filter Capacitor Pin (0.9V)                                    | None              | None   | None                           |

| TCVCM2     | 1    | Input  | Codec ADC2 External Filter Capacitor Pin (0.9V)                                    | None              | None   | None                           |

| TCVRFP     | 1    | Output | Codec ADC1/ADC2 1.5V Reference<br>(buffered version to provide microphone<br>bias) | None              | None   | None                           |

| TCVRFN     | 1    | Input  | Codec ADC1/ADC2 Reference Ground (connect to 0V)                                   | None              | None   | None                           |

| TCMIC1P    | 1    | Input  | Codec Microphone 1 Input (+)                                                       | None              | None   | None                           |

| TCMIC1N    | 1    | Input  | Codec Microphone 1 Input (-)                                                       | None              | None   | None                           |

| TCMIC2P    | 1    | Input  | Codec Microphone 2 Input (+)                                                       | None              | None   | None                           |

| TCMIC2N    | 1    | Input  | Codec Microphone 2 Input (-)                                                       | None              | None   | None                           |

| TCRP       | 1    | Output | Codec Right Channel Output (+)                                                     | None              | None   | None                           |

| TCRN       | 1    | Output | Codec Right Channel Output (-)                                                     | None              | None   | None                           |

| TCLP       | 1    | Output | Codec Left Channel Output (+)                                                      | None              | None   | None                           |

| TCLN       | 1    | Output | Codec Left Channel Output (-)                                                      | None              | None   | None                           |

| SCL1       | 1    | I/O    | ACCESS.bus 1 Clock                                                                 | None              | None   | None                           |

| SDA1       | 1    | I/O    | ACCESS.bus 1 Serial Data                                                           | None              | None   | None                           |

|            |      |        |                                                                                    | RXD0              | Input  | UART 0 Receive Data Input      |

| PE0        | 1    | I/O    | Generic I/O                                                                        | TIO0_1            | I/O    | Versatile Timer Unit 0 Input 1 |

| PE1        | 1    | I/O    | Generic I/O                                                                        | TXD0              | Output | UART 0 Transmit Data Output    |

|            |      |        |                                                                                    | RTS0              | Output | UART 0 Ready-To-Send Output    |

| PE2        | 1    | I/O    | Generic I/O                                                                        | TIO0_3            | I/O    | Versatile Timer Unit 0 Input 3 |

| PE3        | 1    | I/O    | Generic I/O                                                                        | CTSO              | Input  | UART 0 Clear-To-Send Input     |

|            |      |        |                                                                                    | CKX0              | I/O    | UART 0 Clock Input             |

| PE4        | 1/0  | I/O    | Generic I/O                                                                        | TIO0_2            | 1/O    | Versatile Timer Unit 0 Input 2 |

|            |      |        |                                                                                    | TA0               | 1/O    | Multi-Function Timer 0 Port A  |

| PE5        | 1    | I/O    | Generic I/O                                                                        | NMI               | Input  | Non-Maskable Interrupt         |

| PE6        | 1    | I/O    | Generic I/O                                                                        | CAN1RX            | Input  | CAN 1 Receive Input            |

| PE0<br>PE7 | 1    | 1/O    | Generic I/O                                                                        | CANTRX<br>CAN1TX  |        | CAN 1 Receive input            |

|            |      |        |                                                                                    |                   | Output |                                |

| PE8        | 1    | I/O    | Generic I/O                                                                        | MSK0              | I/O    | Microwire/SPI 0 Shift Clock    |

# Table 4-1. CP3SP33 Signal Descriptions (continued)

Copyright © 2013, Texas Instruments Incorporated

| NAME   | PINS | I/O | PRIMARY FUNCTION | ALTERNATE | I/O    | ALTERNATE FUNCTION                                              |

|--------|------|-----|------------------|-----------|--------|-----------------------------------------------------------------|

| PE9    | 1    | I/O | Generic I/O      | MDIDO0    | I/O    | Microwire/SPI 0 Master In Slave<br>Out                          |

| PE10   | 1    | I/O | Generic I/O      | MDODI0    | I/O    | Microwire/SPI 0 Master Out<br>Slave In                          |

| PE11   | 1    | I/O | Generic I/O      | MWCS0     | I/O    | Microwire/SPI 0 Slave Select<br>Input                           |

|        |      |     |                  | TIO0_7    | I/O    | Versatile Timer Unit 0 Input 7                                  |

| PE12   | 1    | I/O | Generic I/O      | SCL0      | I/O    | ACCESS.bus 0 Clock                                              |

|        | 1    |     | Generic i/O      | TIO0_5    | I/O    | Versatile Timer Unit 0 Input 5                                  |

| PE13   | 1    | I/O | Generic I/O      | IDPULLUP  | Output | USB OTG ID Pullup Enable                                        |

|        |      | 20  |                  | TIO1_1    | I/O    | Versatile Timer Unit 1 Input 6                                  |

| PE14   | 1    | I/O | Generic I/O      | DRVVBUS   | Output | USB OTG VBUS Driver Enable                                      |

| 1 L 14 | 1    |     | Generic i/O      | TIO1_3    | I/O    | Versatile Timer Unit 1 Input 3                                  |

| PE15   | 1    | I/O | Generic I/O      | IDDIG     | Input  | USB OTG ID Input                                                |

| FEIO   |      | 10  |                  | TIO1_5    | I/O    | Versatile Timer Unit 1 Input 5                                  |

| PF0    | 1    | I/O | Generic I/O      | RFSYNC    | Output | RF Interface Frequency<br>Correlation/DC Compensation<br>Output |

| PF1    | 1    | I/O | Generic I/O      | SCLK      | Output | RF Interface Shift Clock Output                                 |

| PF2    | 1    | I/O | Generic I/O      | SDAT      | I/O    | RF Interface Data                                               |

| PF3    | 1    | I/O | Generic I/O      | SLE       | Output | RF Interface Load Enable                                        |

| PF4    | 1    | I/O | Generic I/O      | BTSEQ1    | Output | Bluetooth Sequencer Status                                      |

| PF5    | 1/0  | I/O | Generic I/O      | BTSEQ2    | Output | Bluetooth Sequencer Status                                      |

| PF6    | 1/0  | I/O | Generic I/O      | BTSEQ3    | Output | Bluetooth Sequencer Status                                      |

|        |      | ŝ   |                  | ASYNC     | Input  | ADC External Start Trigger                                      |

| PF7    | 1/0  | I/O | Generic I/O      | TB0       | Input  | Multi-Function Timer 0 Port B                                   |

|        |      |     |                  | RXD1      | Input  | UART 1 Receive Data Input                                       |

| PF8    | 1    | I/O | Generic I/O      | TIO0_4    | I/O    | Versatile Timer Unit 0 Input 4                                  |

| PF9    | 1    | I/O | Generic I/O      | TXD1      | Output | UART 1 Transmit Data Output                                     |

|        |      |     |                  | RTS1      | Output | UART 1 Ready-To-Send Output                                     |

| PF10   | 1    | I/O | Generic I/O      | TIO0_6    | I/O    | Versatile Timer Unit 6 Input 6                                  |

| PF11   | 1    | I/O | Generic I/O      | CTS1      | Input  | UART 1 Clear-To-Send Input                                      |

|        |      |     |                  | RXD2      | Input  | UART 2 Receive Data Input                                       |

| PF12   | 1/0  | I/O | Generic I/O      | TIO0_8    | I/O    | Versatile Timer Unit 0 Input 8                                  |

| PF13   | 1/0  | I/O | Generic I/O      | TXD2      | Output | UART 2 Transmit Data Output                                     |

|        |      |     |                  | RTS2      | Output | UART 2 Ready-To-Send Output                                     |

| PF14   | 1/0  | I/O | Generic I/O      | TIO1_2    | I/O    | Versatile Timer Unit 1 Input 2                                  |

| PF15   | 1/0  | I/O | Generic I/O      | CTS2      | Input  | UART 2 Clear-To-Send Input                                      |

| PG0    | 1    | I/O | Generic I/O      | I2SCLK    | I/O    | I <sup>2</sup> S Serial Clock                                   |

| PG1    | 1    | I/O | Generic I/O      | I2SWS     | I/O    | I <sup>2</sup> S Word Select                                    |

| PG2    | 1    | I/O | Generic I/O      | I2SSDI    | Input  | I <sup>2</sup> S Serial Data Input                              |

| PG3    | 1    | I/O | Generic I/O      | I2SSDO    | Output | I <sup>2</sup> S Serial Data Output                             |

| PG4    | 1/0  | I/O | Generic I/O      | MSK1      | I/O    | Microwire/SPI 1 Shift Clock                                     |

| PG5    | 1/0  | I/O | Generic I/O      | MDIDO1    | I/O    | Microwire/SPI 1 Master In Slave<br>Out                          |

| PG6    | 1/0  | I/O | Generic I/O      | MDODI1    | I/O    | Microwire/SPI 1 Master Out<br>Slave In                          |

# Table 4-1. CP3SP33 Signal Descriptions (continued)

| NAME     | PINS  | I/O    | PRIMARY FUNCTION           | ALTERNATE<br>NAME | I/O    | ALTERNATE FUNCTION                    |

|----------|-------|--------|----------------------------|-------------------|--------|---------------------------------------|

| PG7      | 1/0   | I/O    | Generic I/O                | MWCS1             | I/O    | Microwire/SPI 1 Slave Select<br>Input |

|          |       |        |                            | TA1               | I/O    | Multi-Function Timer 1 Port A         |

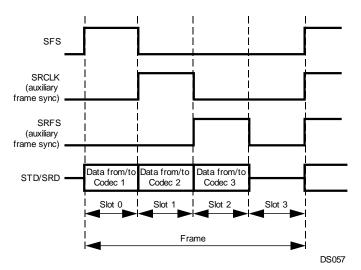

| PG8      | 1/0   | I/O    | Conorio I/O                | SRFS              | I/O    | AAI Serial Receive Frame Sync         |

| PGo      | 1/0   | 1/0    | Generic I/O                | RTS3              | Output | UART 3 Ready-To-Send Output           |

| PG9      | 1/0   | I/O    | Conorio I/O                | SCK               | I/O    | AAI Serial Transmit Clock             |

| PG9      | 1/0   | 1/0    | Generic I/O                | DIGMIC1           | Input  | Digital Microphone Input 1            |

| PG10     | 1/0   | I/O    | Generic I/O                | SFS               | I/O    | AAI Serial Transmit Frame Sync        |

| FGIU     | 1/0   | 1/0    |                            | TCIO1             | I/O    | Codec GPIO                            |

| PG11     | 1/0   | I/O    | Generic I/O                | STD               | Output | AAI Serial Transmit Data              |

| FGII     | 1/0   | 1/0    | Generic I/O                | DIGMIC2           | Input  | Digital Microphone Input 2            |

| PG12     | 1/0   | I/O    | Generic I/O                | SRD               | Input  | AAI Serial Receive Data               |

| DC12     | 1/0   | 1/0    | Conorio I/O                | SRCLK             | I/O    | AAI Serial Receive Clock              |

| PG13     | 1/0   | I/O    | Generic I/O                | CTS3              | Input  | UART 3 Clear-To-Send Input            |

| PG14     | 1/0   | I/O    | Generic I/O                | RXD3              | Input  | UART 3 Receive Data Input             |

| FG14     | 1/0   | 1/0    | Generic I/O                | TB1               | Input  | Multi-Function Timer 1 Port B         |

| PG15     | 1/0   | I/O    | Generic I/O                | TXD3              | Output | UART 3 Transmit Data Output           |

| PH0      | 1/0   | I/O    | Generic I/O                | TIO1_4            | I/O    | Versatile Timer Unit 1 Input 4        |

| PH1      | 1     | I/O    | Generic I/O                | SDA0              | I/O    | ACCESS.bus 0 Serial Data              |

| FUI      | I     | 1/0    | Generic I/O                | TIO1_6            | I/O    | Versatile Timer Unit 1 Input 6        |

| PH2      | 1     | I/O    | O Generic I/O              | CANORX            | Input  | CAN 0 Receive Input                   |

| FTIZ     | 1     | 1/0    | Generic 1/O                | TIO1_7            | I/O    | Versatile Timer Unit 1 Input 7        |

| PH3      | 1     | I/O    | Generic I/O                | CAN0TX            | Output | CAN 0 Transmit Output                 |

| 1115     | 1     | 1/0    |                            | TIO1_8            | I/O    | Versatile Timer Unit 1 Input 8        |

| PH4      | 1/0   | I/O    | Generic I/O                | None              | None   | None                                  |

| PH5      | 1/0   | I/O    | Generic I/O                | None              | None   | None                                  |

| PH6      | 1/0   | I/O    | Generic I/O                | None              | None   | None                                  |

| PH7      | 1     | I/O    | Generic I/O                | None              | None   | None                                  |

| PH8      | 1     | I/O    | Generic I/O                | None              | None   | None                                  |

| PH9      | 1     | I/O    | Generic I/O                | None              | None   | None                                  |

| PH10     | 1     | I/O    | Generic I/O                | None              | None   | None                                  |

| PH11     | 1/0   | I/O    | Generic I/O                | None              | None   | None                                  |

| PH12     | 1/0   | I/O    | Generic I/O                | None              | None   | None                                  |

| PH13     | 1/0   | I/O    | Generic I/O                | None              | None   | None                                  |

| PH14     | 1/0   | I/O    | Generic I/O                | None              | None   | None                                  |

| PH15     | 1/0   | I/O    | Generic I/O                | None              | None   | None                                  |

| XWE      | 1     | Output | External Bus Write Enable  | None              | Output | None                                  |

| XOE      | 1     | Output | External Bus Output Enable | None              | Output | None                                  |

| XBE[3:0] | 4/2   | Output | External Bus Byte Enables  | None              | Output | None                                  |

| XCS[2:0] | 3/2   | Output | External Bus Chip Selects  | None              | Output | None                                  |

| XA[22:0] | 23/21 | Output | External Address Bus       | None              | Output | None                                  |

| XD[31:0] | 32/16 | I/O    | External Data Bus          | None              | I/O    | None                                  |

# Table 4-1. CP3SP33 Signal Descriptions (continued)

### 5 CPU Architecture

The CP3SP33 uses the CR16CPlus third-generation 16-bit CompactRISC processor core. The CPU implements a Reduced Instruction Set Computer (RISC) architecture that allows an effective execution rate of up to one instruction per clock cycle. For a detailed description of the CR16CPlus architecture, see the *CompactRISC CR16C Programmer's Reference Manual* which is available on the Texas Instruments web site (http://www.ti.com).

The CR16CPlus CPU core includes these internal registers:

- General-purpose registers (R0-R13, RA, and SP)

- Dedicated address registers (PC, ISP, USP, and INTBASE)

- Processor Status Register (PSR)

- Configuration Register (CFG)

The R0-R11, PSR, and CFG registers are 16 bits wide. The R12, R13, RA, SP, ISP and USP registers are 32 bits wide. The PC register is 24 bits wide. Figure 5-1 shows the CPU registers.

|         | Dedicated Address Registers<br>23 15 0  |  |  |  |  |  |  |

|---------|-----------------------------------------|--|--|--|--|--|--|

| 20      | PC                                      |  |  |  |  |  |  |

| ISPH    | ISPL                                    |  |  |  |  |  |  |

| USPH    | USPL                                    |  |  |  |  |  |  |

| NTBASEH | INTBASEL                                |  |  |  |  |  |  |

|         | rocessor Status Register<br>15 0<br>PSR |  |  |  |  |  |  |

|         | Configuration Register<br>15 0          |  |  |  |  |  |  |

|         | CFG                                     |  |  |  |  |  |  |

|         |                                         |  |  |  |  |  |  |

| C | eneral-Purpose Registers <u>15 0</u> |

|---|--------------------------------------|

|   | R0                                   |

|   | R1                                   |

|   | R2                                   |

|   | R3                                   |

|   | R4                                   |

|   | R5                                   |

|   | R6                                   |

|   | R7                                   |

|   | R8                                   |

|   | R9                                   |

|   | R10                                  |

|   | R11                                  |

|   | R12                                  |

|   | R13                                  |

|   |                                      |

|   | RA                                   |

|   | SP                                   |

DS004

#### Figure 5-1. CPU Registers

Some register bits are designated as "reserved." Software must write a zero to these bit locations when it writes to the register. Read operations from reserved bit locations return undefined values.

#### 5.1 General-Purpose Registers

The CompactRISC CPU features 16 general-purpose registers. These registers are used individually as 16-bit operands or as register pairs for operations on addresses greater than 16 bits.

- General-purpose registers are defined as R0 through R13, RA, and SP.

- Registers are grouped into pairs based on the setting of the Short Register bit in the Configuration Register (CFG.SR). When the CFG.SR bit is set, the grouping of register pairs is upward-compatible with the architecture of the earlier CR16A/B CPU cores: (R1,R0), (R2,R1) ... (R11,R10), (R12\_L, R11), (R13\_L, R12\_L), (R14\_L, R13\_L) and SP. (R14\_L, R13\_L) is the same as (RA,ERA).

- When the CFG.SR bit is clear, register pairs are grouped in the manner used by native CR16CPlus software: (R1,R0), (R2,R1) ... (R11,R10), (R12\_L, R11), R12, R13, RA, SP. R12, R13, RA, and SP are 32-bit registers for holding addresses greater than 16 bits.

With the recommended calling convention for the architecture, some of these registers are assigned special hardware and software functions. Registers R0 to R13 are for general-purpose use, such as holding variables, addresses, or index values. The SP register holds a pointer to the program run-time stack. The RA register holds a subroutine return address. The R12 and R13 registers are available to hold base addresses used in the index addressing mode.

If a general-purpose register is specified by an operation that is 8 bits long, only the lower byte of the register is used; the upper part is not referenced or modified. Similarly, for word operations on register pairs, only the lower word is used. The upper word is not referenced or modified.

#### 5.2 Dedicated Address Registers

The CR16CPlus has four dedicated address registers to implement specific functions: the PC, ISP, USP, and INTBASE registers.

#### 5.2.1 Program Counter (PC) Register

The 24-bit value in the PC register points to the first byte of the instruction currently being executed. CR16CPlus instructions are aligned to even addresses, therefore the least significant bit of the PC is always 0. At reset, the PC is initialized to 0 or an optional predetermined value. When a warm reset occurs, value of the PC prior to reset is saved in the (R1,R0) general-purpose register pair.

#### 5.2.2 Interrupt Stack Pointer (ISP)

The 32-bit ISP register points to the top of the interrupt stack. This stack is used by hardware to service exceptions (interrupts and traps). The stack pointer may be accessed as the ISP register for initialization. The interrupt stack can be located anywhere in the CPU address space. The ISP cannot be used for any purpose other than the interrupt stack, which is used for automatic storage of the CPU registers when an exception occurs and restoration of these registers when the exception handler returns. The interrupt stack grows downward in memory. The least significant bit and the 8 most significant bits of the ISP register are always 0.

#### 5.2.3 User Stack Pointer (USP)

The USP register points to the top of the user-mode program stack. Separate stacks are available for user and supervisor modes, to support protection mechanisms for multitasking software. The processor mode is controlled by the U bit in the PSR register (which is called PSR.U in the shorthand convention). Stack grow downward in memory. If the USP register points to an illegal address (any address greater than 0x00FF\_FFFF) and the USP is used for stack access, an IAD trap is taken.

#### 5.2.4 Interrupt Base Register (INTBASE)

The INTBASE register holds the address of the dispatch table for exceptions. The dispatch table can be located any where in the CPU address space. When loading the INTBASE register, bits 31 to 24 and bit 0 must written with 0.

#### 5.3 Processor Status Register (PSR)

| 15 1     | 2 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|---|----|----|---|---|---|---|---|---|---|---|---|---|

| Reserved |   | I  | Р  | Е | 0 | Ν | Z | F | 0 | U | L | Т | С |

C The Carry bit indicates whether a carry or borrow occurred after addition or subtraction. 0 – No carry or borrow occurred.

1 – Carry or borrow occurred.

- T The Trace bit enables execution tracing, in which a Trace trap (TRC) is taken after every instruction. Tracing is automatically disabled during the execution of an exception handler.

- 0 Tracing disabled.

- 1 Tracing enabled.

- L The Low bit indicates the result of the last comparison operation, with the operands interpreted as unsigned integers.

- 0 Second operand greater than or equal to first operand.

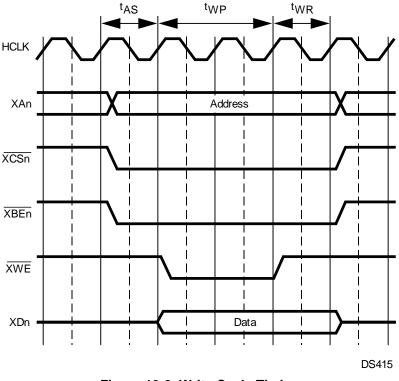

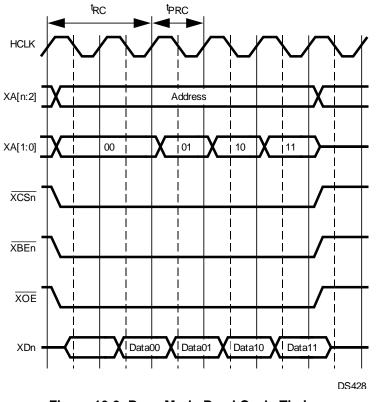

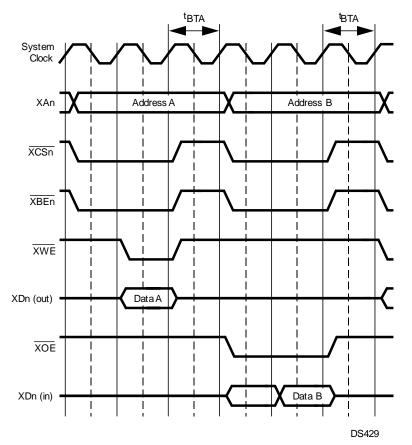

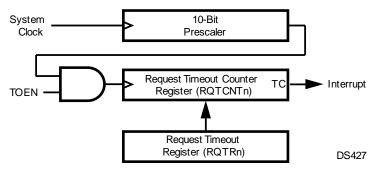

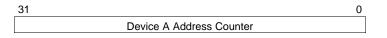

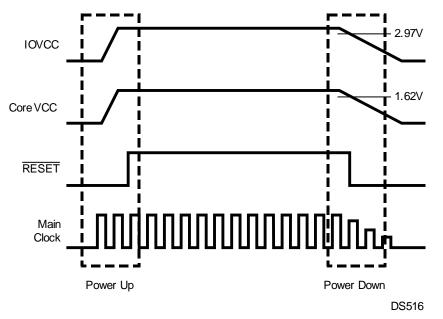

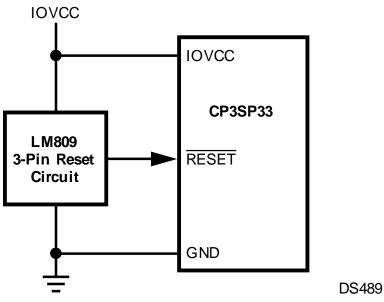

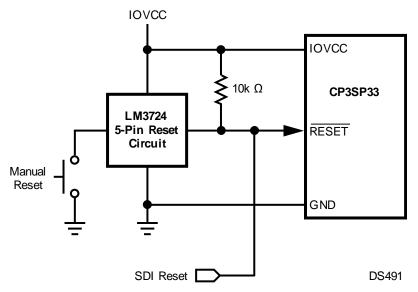

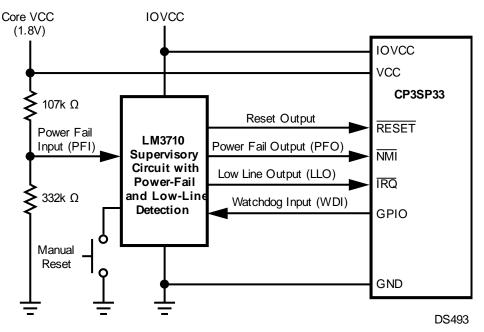

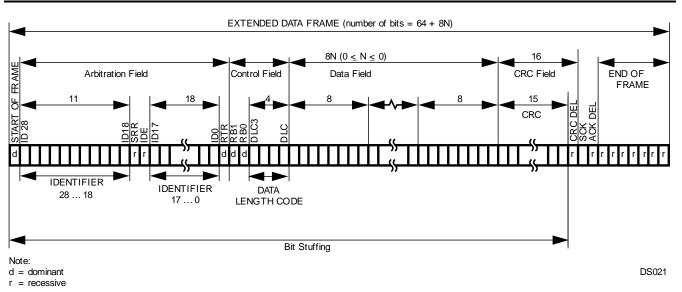

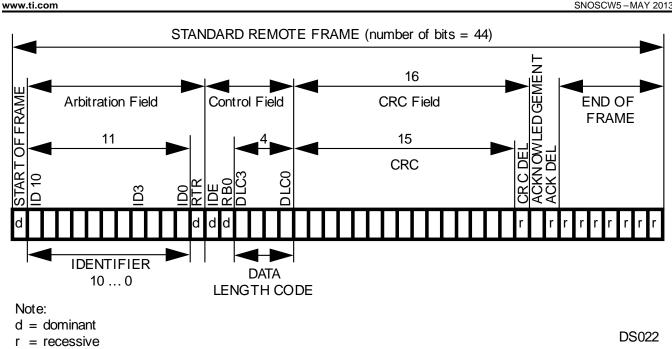

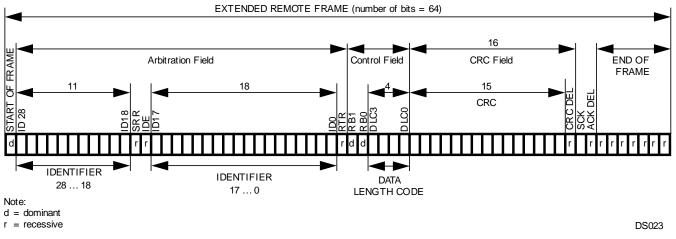

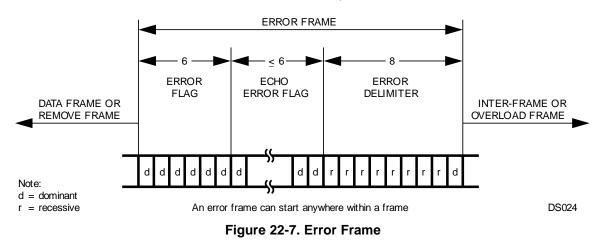

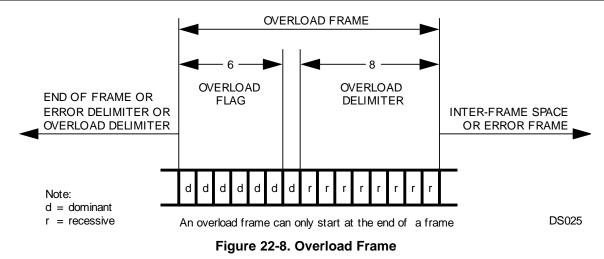

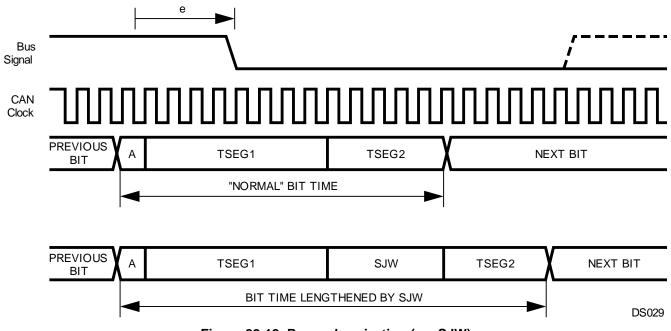

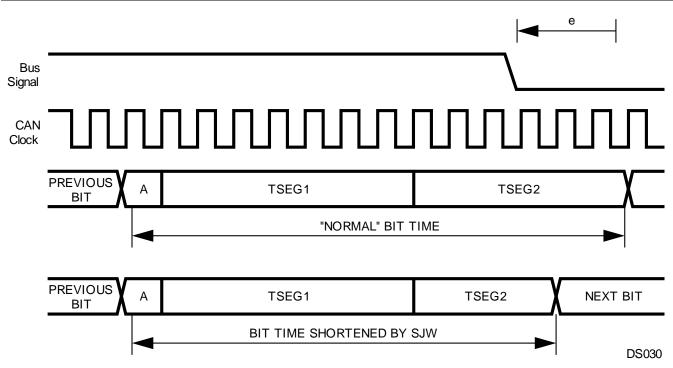

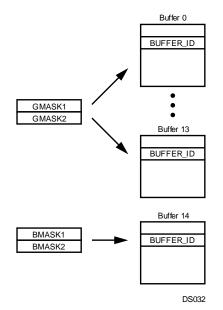

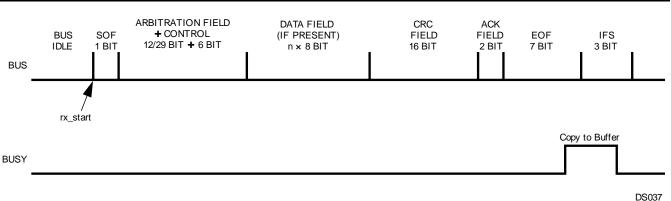

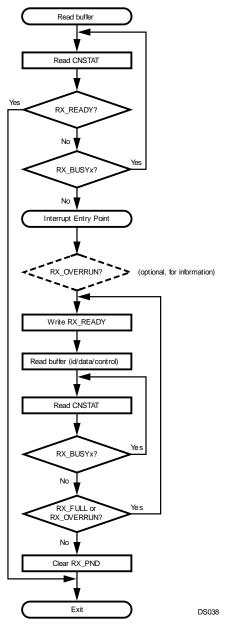

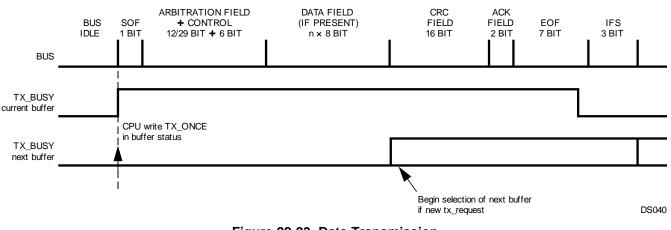

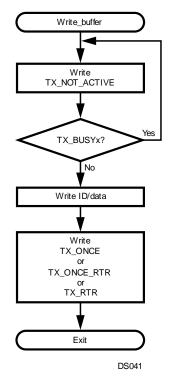

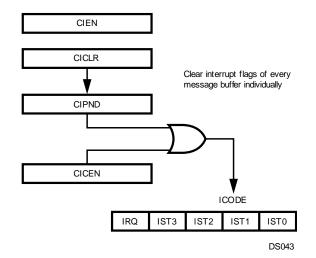

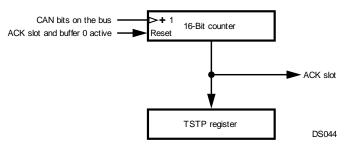

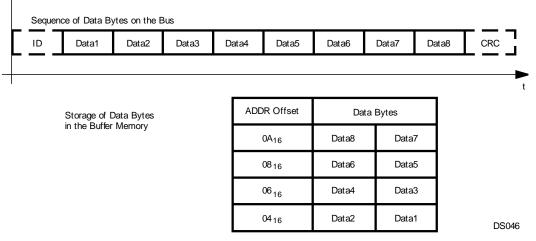

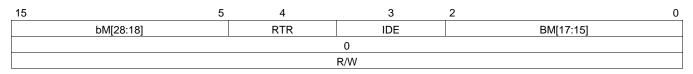

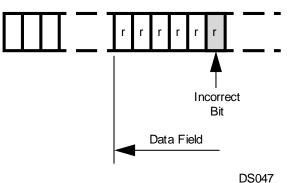

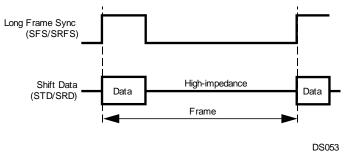

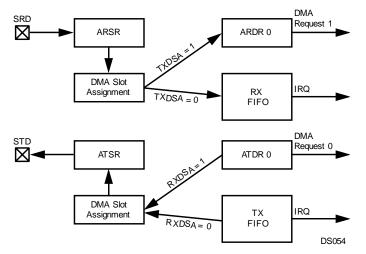

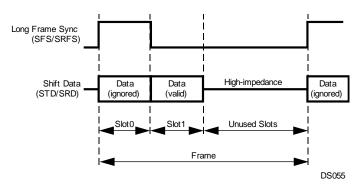

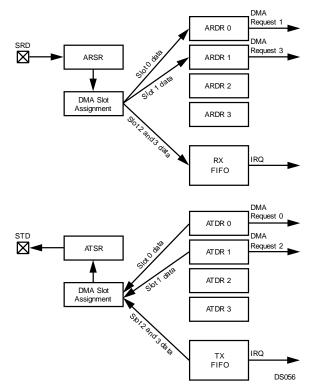

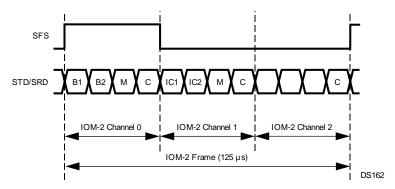

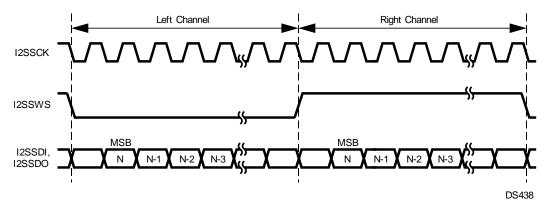

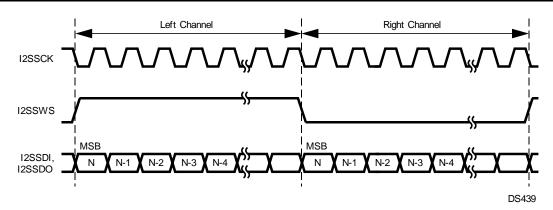

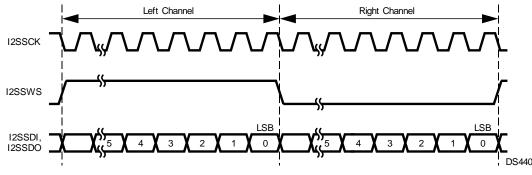

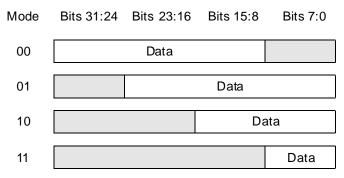

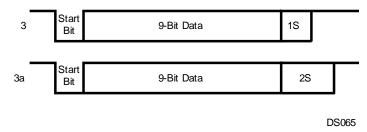

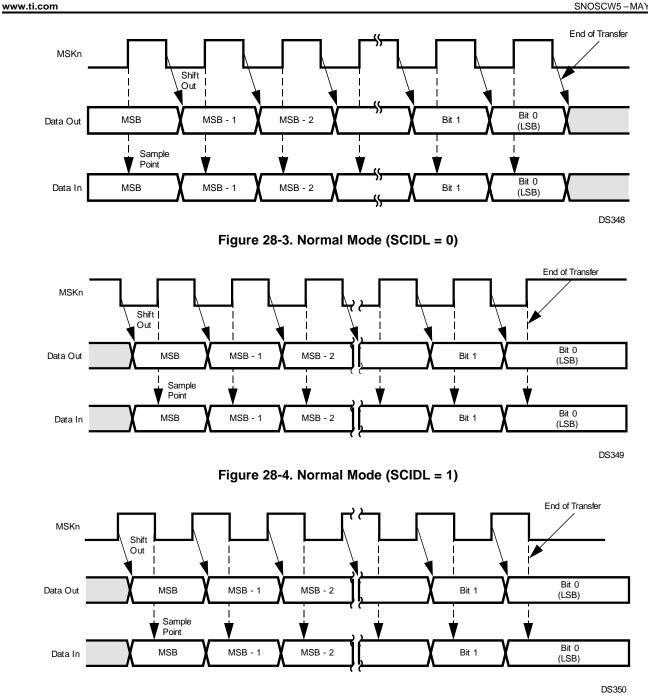

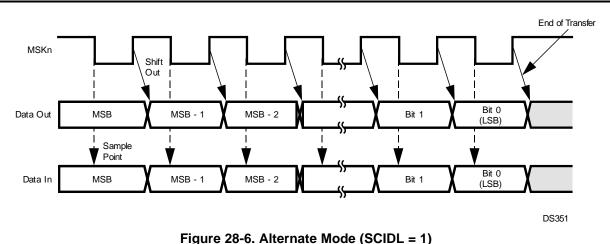

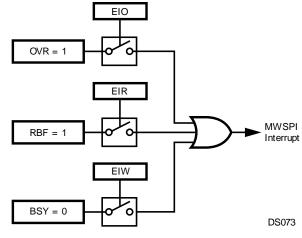

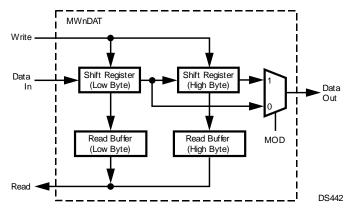

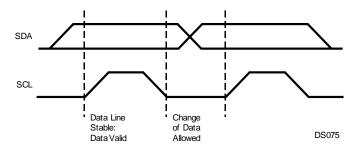

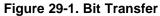

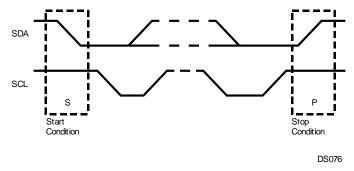

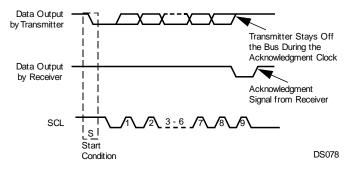

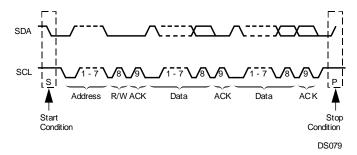

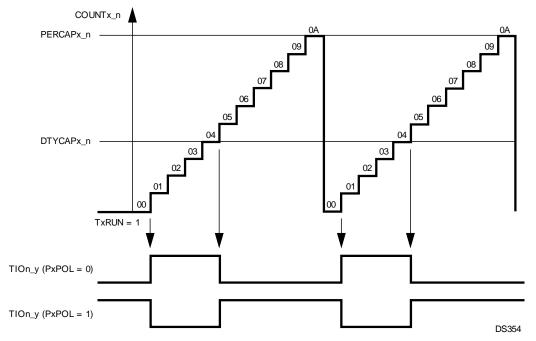

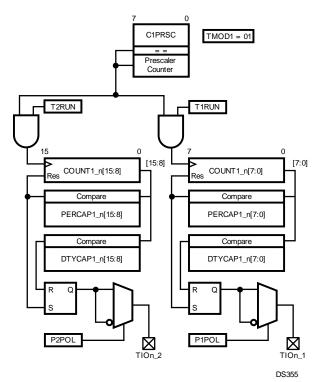

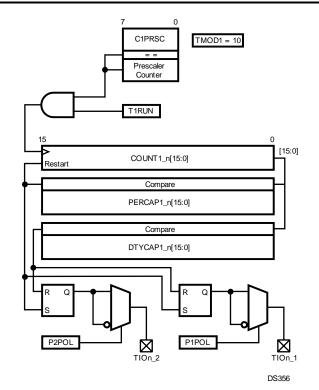

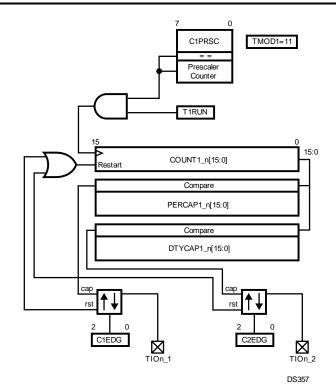

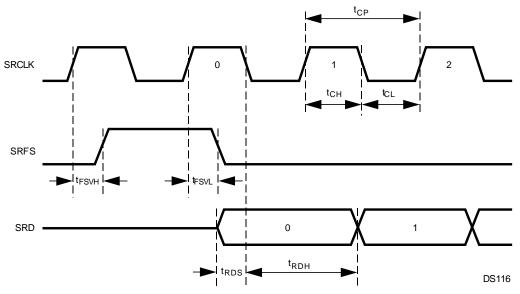

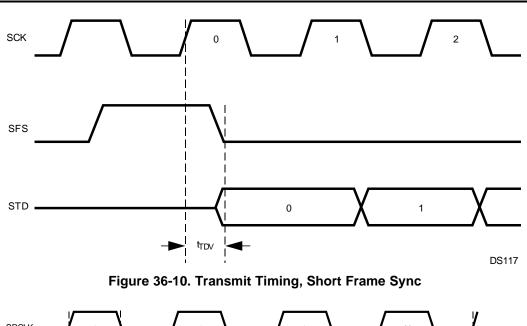

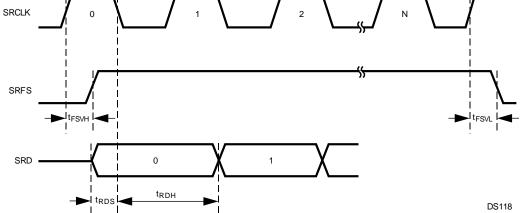

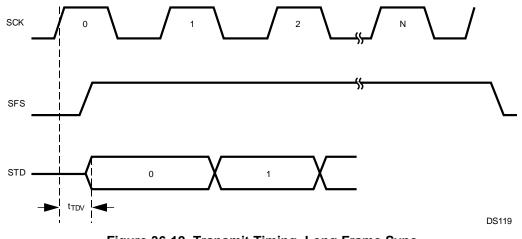

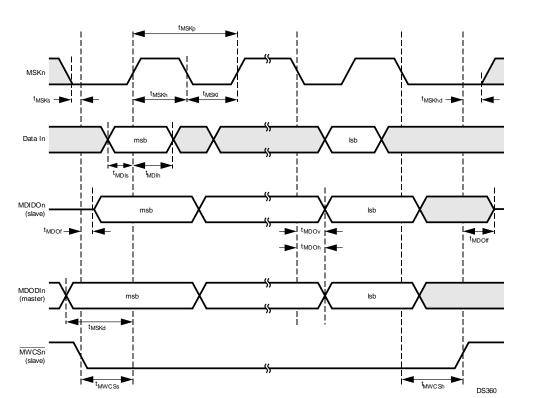

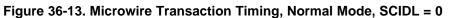

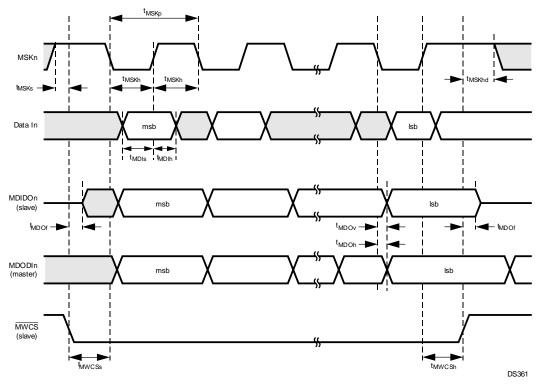

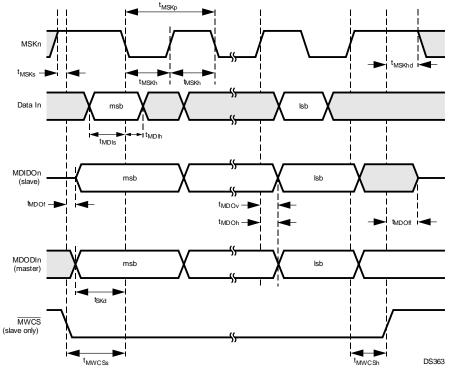

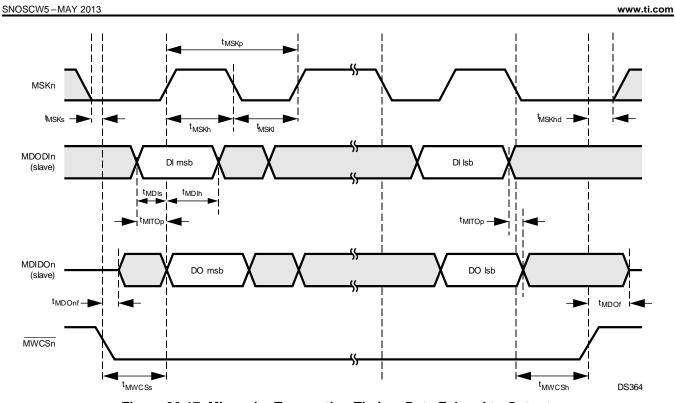

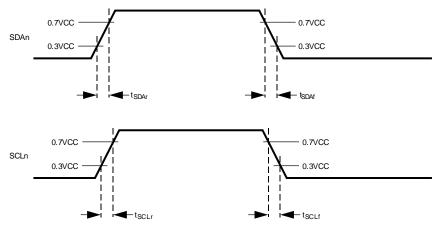

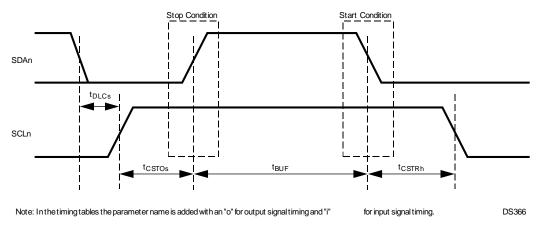

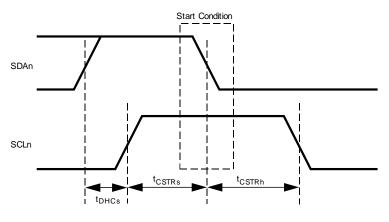

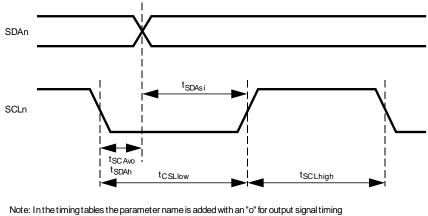

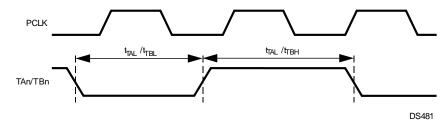

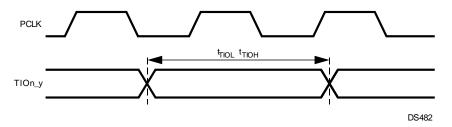

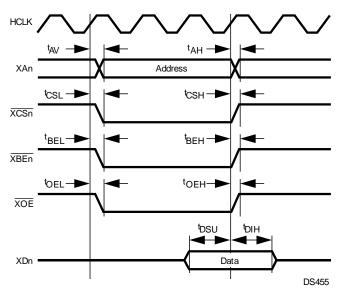

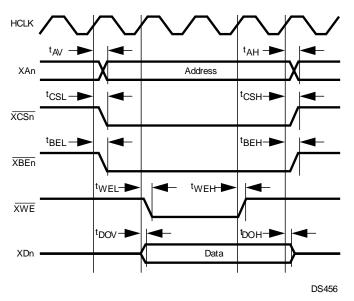

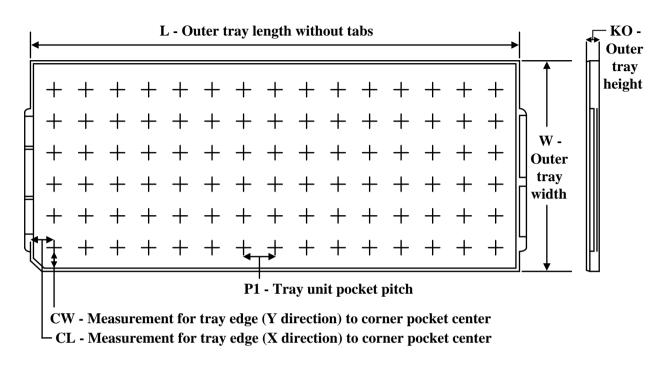

- 1 Second operand less than first operand.