JAJSNI4 December 2021 DAC11001B

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 Timing Requirements: Write, 4.5 V ≤ DVDD ≤ 5.5 V

- 6.7 Timing Requirements: Write, 2.7 V ≤ DVDD < 4.5 V

- 6.8 Timing Requirements: Read and Daisy-Chain Write, 4.5 V ≤ DVDD ≤ 5.5 V

- 6.9 Timing Requirements: Read and Daisy-Chain Write, 2.7 V ≤ DVDD < 4.5 V

- 6.10 Timing Diagrams

- 6.11 Typical Characteristics

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6

Register Map

- 7.6.1 NOP Register (address = 00h) [reset = 0x000000h for bits [23:0]]

- 7.6.2 DAC-DATA Register (address = 01h) [reset = 0x000000h for bits [23:0]]

- 7.6.3 CONFIG1 Register (address = 02h) [reset = 004C80h for bits [23:0]]

- 7.6.4 DAC-CLEAR-DATA Register (address = 03h) [reset = 000000h for bits [23:0]]

- 7.6.5 TRIGGER Register (address = 04h) [reset = 000000h for bits [23:0]]

- 7.6.6 STATUS Register (address = 05h) [reset = 000000h for bits [23:0]]

- 7.6.7 CONFIG2 Register (address = 06h) [reset = 000040h for bits [23:0]]

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

8.2.3 Arbitrary Waveform Generation (AWG)

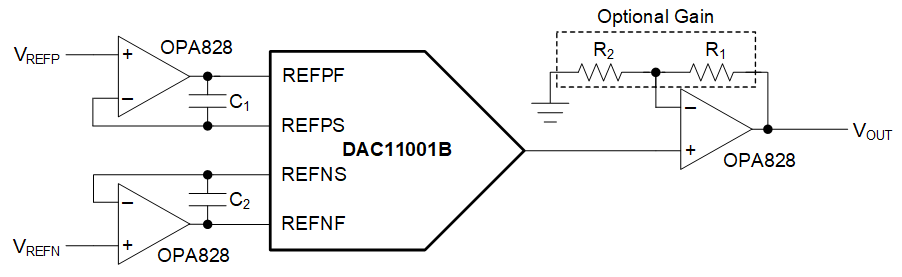

Arbitrary waveform generation circuits are common in memory and semiconductor test equipment. These circuits are used to generate reference ac waveforms to test semiconductor devices. The key performance parameters of such circuits are THD, SNR, and the update rate. Figure 8-7 shows the basic building block example of an AWG circuit using the DAC11001B.

Figure 8-7 Arbitrary

Waveform Generation

Figure 8-7 Arbitrary

Waveform Generation