JAJSNI4 December 2021 DAC11001B

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics

- 6.6 Timing Requirements: Write, 4.5 V ≤ DVDD ≤ 5.5 V

- 6.7 Timing Requirements: Write, 2.7 V ≤ DVDD < 4.5 V

- 6.8 Timing Requirements: Read and Daisy-Chain Write, 4.5 V ≤ DVDD ≤ 5.5 V

- 6.9 Timing Requirements: Read and Daisy-Chain Write, 2.7 V ≤ DVDD < 4.5 V

- 6.10 Timing Diagrams

- 6.11 Typical Characteristics

-

7 Detailed Description

- 7.1 Overview

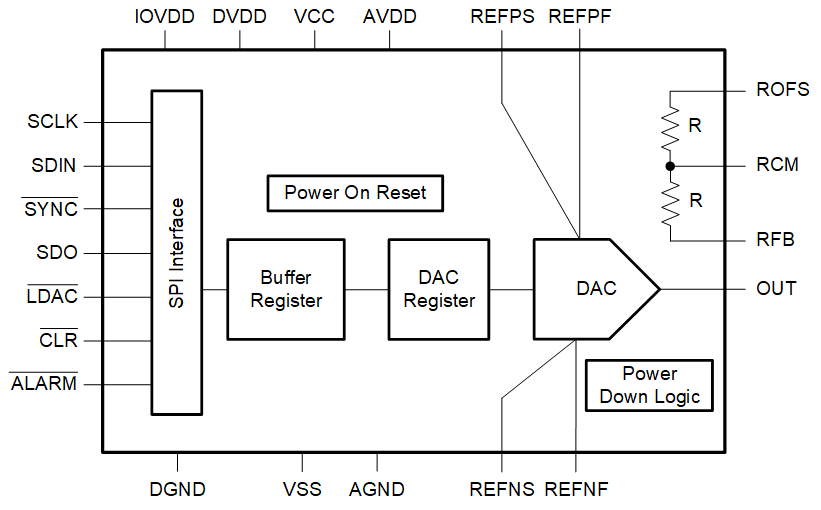

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6

Register Map

- 7.6.1 NOP Register (address = 00h) [reset = 0x000000h for bits [23:0]]

- 7.6.2 DAC-DATA Register (address = 01h) [reset = 0x000000h for bits [23:0]]

- 7.6.3 CONFIG1 Register (address = 02h) [reset = 004C80h for bits [23:0]]

- 7.6.4 DAC-CLEAR-DATA Register (address = 03h) [reset = 000000h for bits [23:0]]

- 7.6.5 TRIGGER Register (address = 04h) [reset = 000000h for bits [23:0]]

- 7.6.6 STATUS Register (address = 05h) [reset = 000000h for bits [23:0]]

- 7.6.7 CONFIG2 Register (address = 06h) [reset = 000040h for bits [23:0]]

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

3 概要

DAC11001B は、高精度、低ノイズ、電圧出力の 20 ビット・シングル・チャネル D/A コンバータ (DAC) です。DAC11001B は、単調性が設計で仕様規定されており、出力範囲全体にわたって非常に優れた直線性を示します。

バッファなしの電圧出力により、低ノイズ性能 (7nV/√Hz) と高速セトリング時間 (1µs) を両立させているため、このデバイスは低ノイズ、高速制御ループ、波形生成アプリケーションに最適です。DAC11001B には拡張グリッチ除去回路が内蔵されており、コードに依存しない超低グリッチ (1nV-s) を実現しているため、全高調波歪み (THD) が非常に小さいクリーンな波形ランプを生成できます。

DAC11001B デバイスには、DAC の電源オン時にレジスタが既知の値になるようにパワー・オン・リセット (POR) 回路が組み込まれています。外部基準電圧を使用すると、VREFPF~VREFNF までの DAC 出力範囲 (非対称な出力範囲も含む) を実現できます。

DAC11001B デバイスは、最高 50MHz のクロック速度で動作する多用途の 4 線式シリアル・インターフェイスを使用しています。

製品情報

| 部品番号 | パッケージ(1) | 本体サイズ (公称) |

|---|---|---|

| DAC11001B | TQFP (48) | 7.00mm × 7.00mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にあるパッケージ・オプションについての付録を参照してください。

機能ブロック図

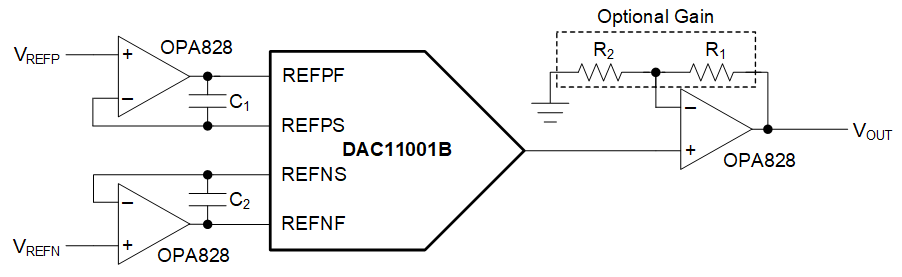

機能ブロック図 任意波形生成回路

任意波形生成回路