JAJSHK3E November 2014 – February 2021 DLPC3439

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Power Electrical Characteristics

- 6.6 Pin Electrical Characteristics

- 6.7 Internal Pullup and Pulldown Electrical Characteristics

- 6.8 DMD Sub-LVDS Interface Electrical Characteristics

- 6.9 DMD Low-Speed Interface Electrical Characteristics

- 6.10 System Oscillator Timing Requirements

- 6.11 Power Supply and Reset Timing Requirements

- 6.12 Parallel Interface Frame Timing Requirements

- 6.13 Parallel Interface General Timing Requirements

- 6.14 Flash Interface Timing Requirements

- 6.15 Other Timing Requirements

- 6.16 DMD Sub-LVDS Interface Switching Characteristics

- 6.17 DMD Parking Switching Characteristics

- 6.18 Chipset Component Usage Specification

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5 Programming

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

3 概要

DLP4710 (.47 .1080p) チップセットの一部である DLPC3439 デジタル・コントローラを使用すると、DLP4710 デジタル・マイクロミラー・デバイス (DMD) を安定して動作させることができます。DLPC3439 コントローラは、システムの電子回路と DMD の間を接続する、使いやすい多機能インターフェイスを提供し、小型で低消費電力のフル HD 高解像度ディスプレイを実現します。

設計を開始する方法については、TI の DLP® Pico™ ディスプレイ・テクノロジーを使用した設計の開始ページを参照し、「プログラマーズ・ガイド」 (英語) をご覧ください。

このチップセットには、設計期間の短縮に役立つ定評あるリソースが用意されており、これにはすぐに量産可能な光モジュール、光モジュール・メーカー、デザインハウスなどが含まれます。

デバイス情報(1)

| 部品番号 | パッケージ | 本体サイズ (公称) |

|---|---|---|

| DLPC3439 | NFBGA (201) | 13.00×13.00mm2 |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

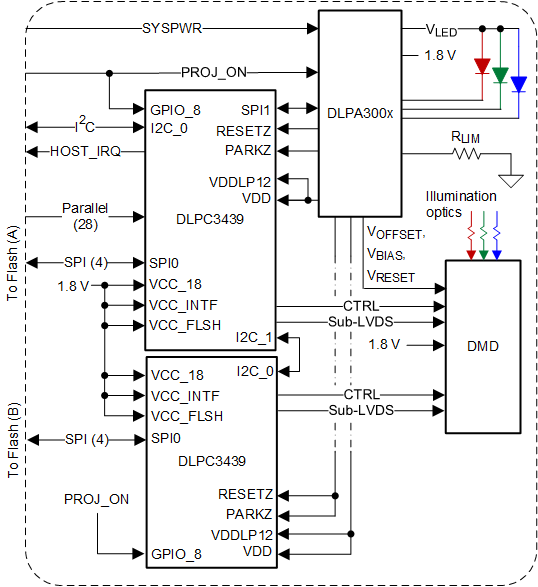

標準的なシステムの概略図

標準的なシステムの概略図