JAJSCF9A June 2015 – June 2015 FDC2112 , FDC2114 , FDC2212 , FDC2214

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 デバイス比較表

- 7 ピン構成および機能

- 8 仕様

-

9 詳細説明

- 9.1 概要

- 9.2 機能ブロック図

- 9.3 機能説明

- 9.4 デバイスの機能モード

- 9.5 プログラミング

- 9.6

レジスタ・マップ

- 9.6.1 レジスタ一覧

- 9.6.2 アドレス0x00、DATA_CH0

- 9.6.3 アドレス0x01、DATA_LSB_CH0(FDC2212 / FDC2214のみ)

- 9.6.4 アドレス0x02、DATA_CH1

- 9.6.5 アドレス0x03、DATA_LSB_CH1(FDC2212 / FDC2214のみ)

- 9.6.6 アドレス0x04、DATA_CH2(FDC2114, FDC2214のみ)

- 9.6.7 アドレス0x05、DATA_LSB_CH2(FDC2214のみ)

- 9.6.8 アドレス0x06、DATA_CH3(FDC2114, FDC2214のみ)

- 9.6.9 アドレス0x07、DATA_LSB_CH3(FDC2214のみ)

- 9.6.10 アドレス0x08、RCOUNT_CH0

- 9.6.11 アドレス0x09、RCOUNT_CH1

- 9.6.12 アドレス0x0A、RCOUNT_CH2(FDC2114, FDC2214のみ)

- 9.6.13 アドレス0x0B、RCOUNT_CH3(FDC2114, FDC2214のみ)

- 9.6.14 アドレス0x0C、OFFSET_CH0(FDC2112 / FDC2114のみ)

- 9.6.15 アドレス0x0D、OFFSET_CH1(FDC2112 / FDC2114のみ)

- 9.6.16 アドレス0x0E、OFFSET_CH2(FDC2114のみ)

- 9.6.17 アドレス0x0F、OFFSET_CH3(FDC2114のみ)

- 9.6.18 アドレス0x10、SETTLECOUNT_CH0

- 9.6.19 アドレス0x11、SETTLECOUNT_CH1

- 9.6.20 アドレス0x12、SETTLECOUNT_CH2(FDC2114, FDC2214のみ)

- 9.6.21 アドレス0x13、SETTLECOUNT_CH3(FDC2114, FDC2214のみ)

- 9.6.22 アドレス0x14、CLOCK_DIVIDERS_CH0

- 9.6.23 アドレス0x15、CLOCK_DIVIDERS_CH1

- 9.6.24 アドレス0x16、CLOCK_DIVIDERS_CH2(FDC2114, FDC2214のみ)

- 9.6.25 アドレス0x17、CLOCK_DIVIDERS_CH3(FDC2114, FDC2214のみ)

- 9.6.26 アドレス0x18、STATUS

- 9.6.27 アドレス0x19、ERROR_CONFIG

- 9.6.28 アドレス0x1A、CONFIG

- 9.6.29 アドレス0x1B、MUX_CONFIG

- 9.6.30 アドレス0x1C、RESET_DEV

- 9.6.31 アドレス0x1E、DRIVE_CURRENT_CH0

- 9.6.32 アドレス0x1F、DRIVE_CURRENT_CH1

- 9.6.33 アドレス0x20、DRIVE_CURRENT_CH2(FDC2114 / FDC2214のみ)

- 9.6.34 アドレス0x21、DRIVE_CURRENT_CH3(FDC2114 / FDC2214のみ)

- 9.6.35 アドレス0x7E、MANUFACTURER_ID

- 9.6.36 アドレス0x7F、DEVICE_ID

- 10アプリケーションと実装

- 11電源に関する推奨事項

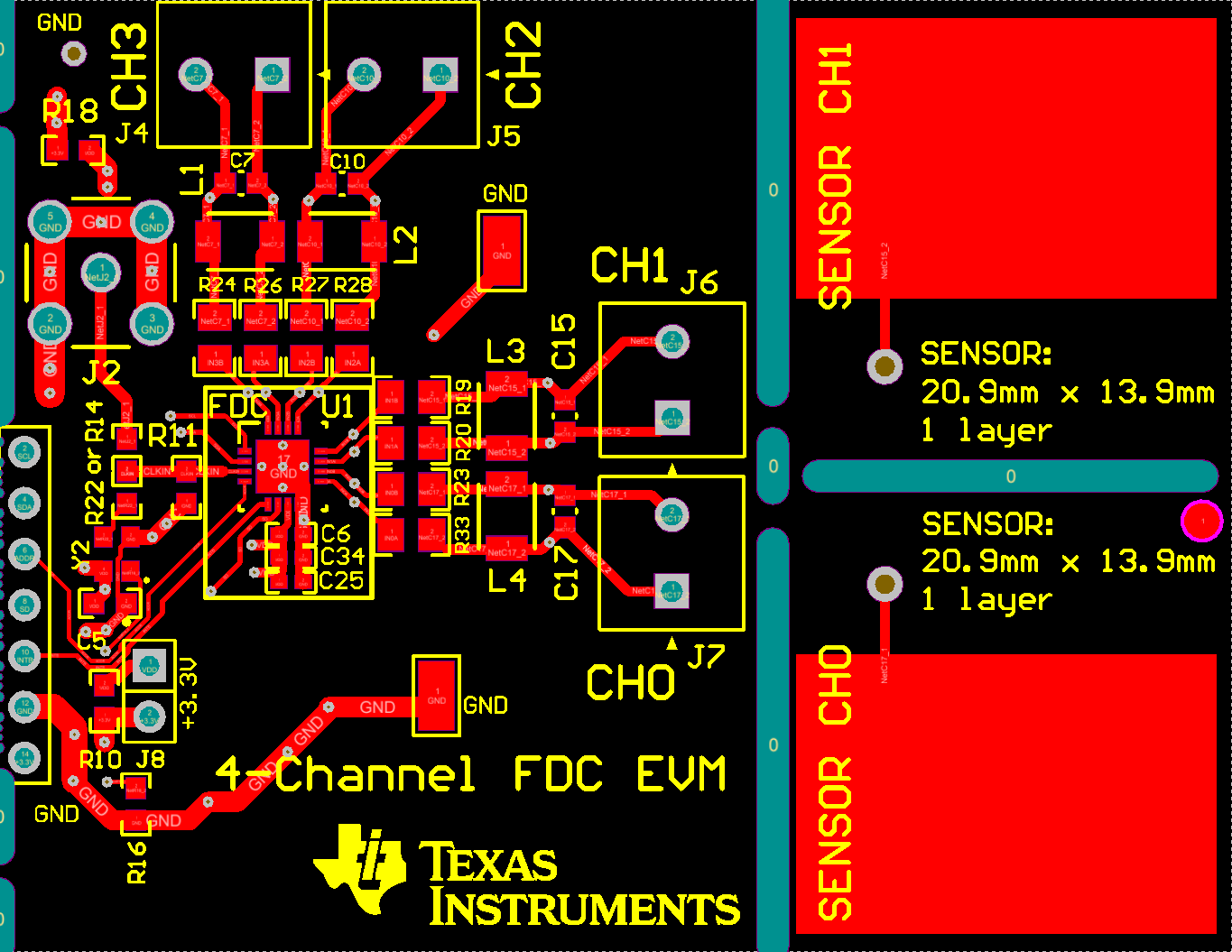

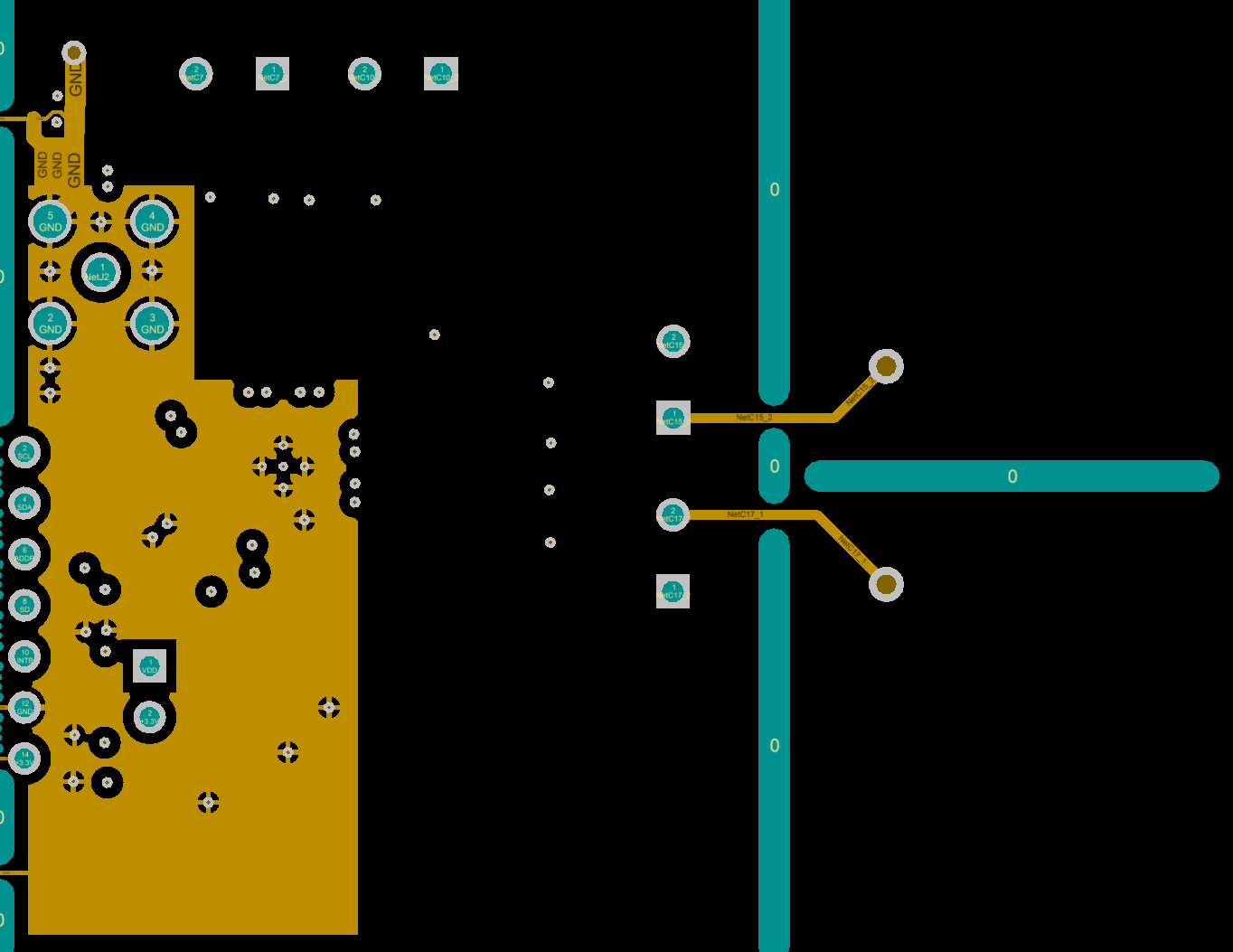

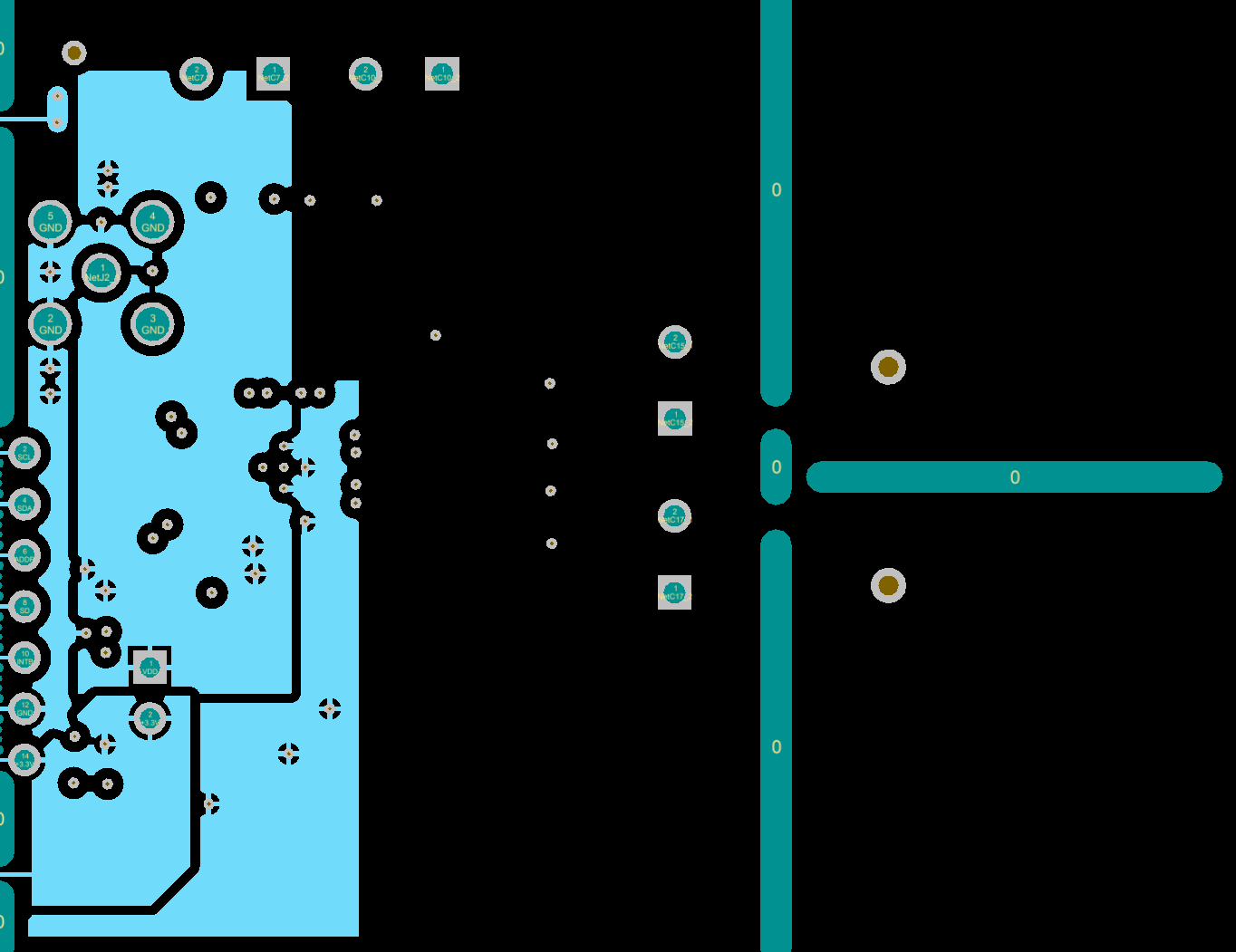

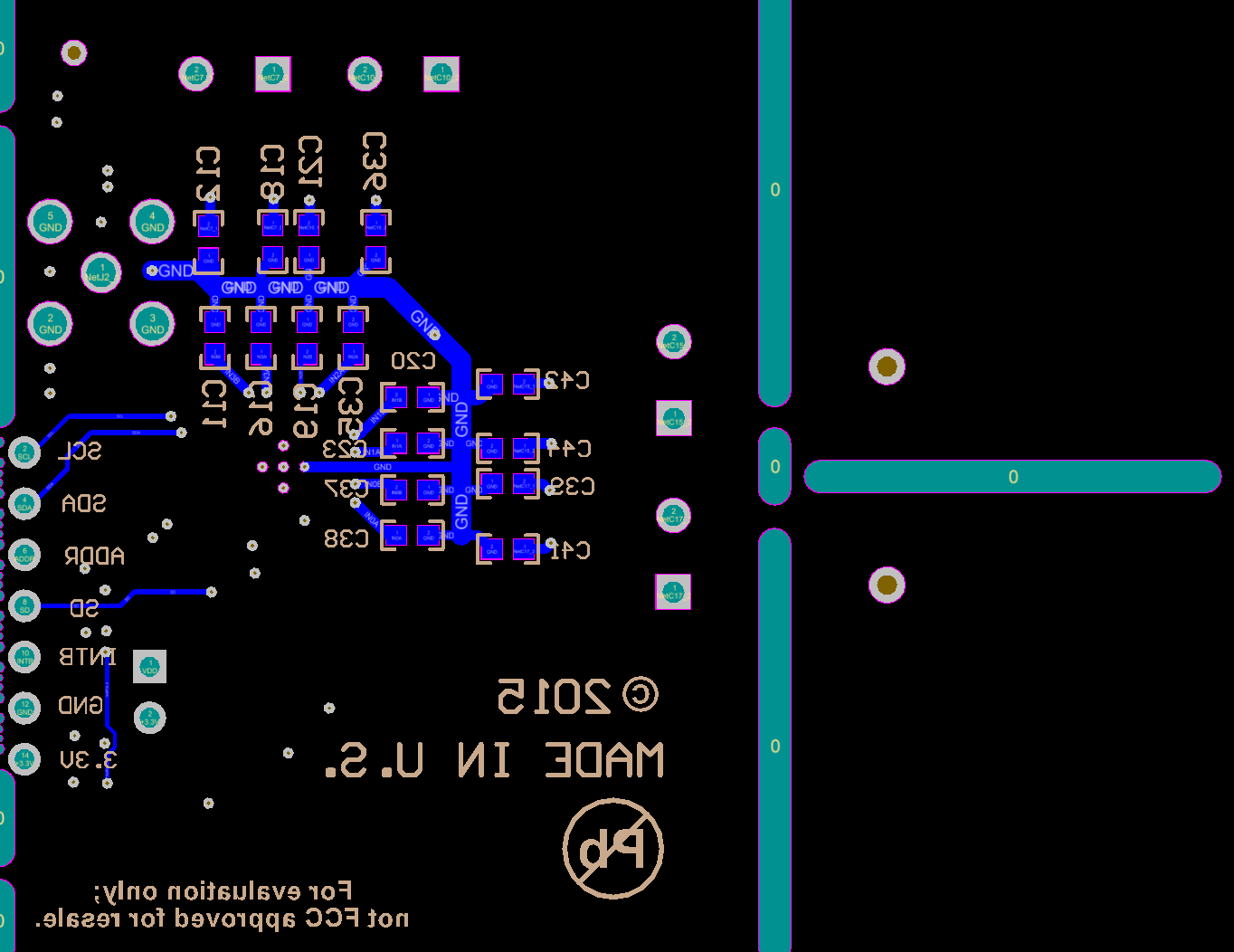

- 12レイアウト

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

12 レイアウト

12.1 レイアウトのガイドライン

- センサとFDCの間を長いパターンで接続することは避けてください。短いパターンを使用することで、センサ・インダクタ間の寄生容量が低減され、システム性能が向上します。

- マッチングされたチャネル応答が必要なシステムでは、すべてのアクティブ・チャネルのパターン長を一致させる必要があります。