JAJSDW2C November 2016 – August 2021 LMS3635-Q1 , LMS3655-Q1

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Device Comparison Tables

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1

General Application

- 9.2.1.1 Design Requirements

- 9.2.1.2 Detailed Design Procedure

- 9.2.1.3 Application Curves

- 9.2.2 Fixed 5-V Output for USB-Type Applications

- 9.2.3 Fixed 3.3-V Output

- 9.2.4 6-V Adjustable Output

- 9.2.1

General Application

- 9.3 Do's and Don't's

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RNL|22

サーマルパッド・メカニカル・データ

- RNL|22

発注情報

3 概要

LMS3635-Q1 および LMS3655-Q1 同期整流降圧レギュレータは、高性能アプリケーション用に最適化されており、3.3V、5V、または1V~20Vの範囲で調整可能な電圧を出力できます。PWMモードとPFMモードの間でシームレスに遷移し、低い静止電流とともに、あらゆる負荷領域について高い効率と優れた過渡応答を確実にします。

LMS3655-Q1は高度な高速回路を使用しているため、24Vの入力を400kHzの固定周波数で3.3Vの出力にレギュレートでき、5.5Aの連続負荷電流に対応できます。革新的な周波数フォールドバック・アーキテクチャにより、このデバイスはわずか3.5Vの入力電圧からでも、3.3Vの出力をレギュレートできます。入力電圧は最高36Vまで可能で、42Vまでの過渡電圧が許容されるため、入力サージ保護の設計が簡単になります。

フィルタリングと遅延を備えたオープン・ドレインのリセット出力により、システムの真の状態を示すことができます。この機能により、追加のスーパーバイザ部品が必要なくなるため、コストと基板面積を削減できます。

製品情報

| 型番 | パッケージ(1) | 本体サイズ |

|---|---|---|

| LMS3635-Q1 | SON (22) | 4.00mm×5.00mm |

| LMS3655-Q1 |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

LMS3655-Q1 の効率:VOUT = 5V

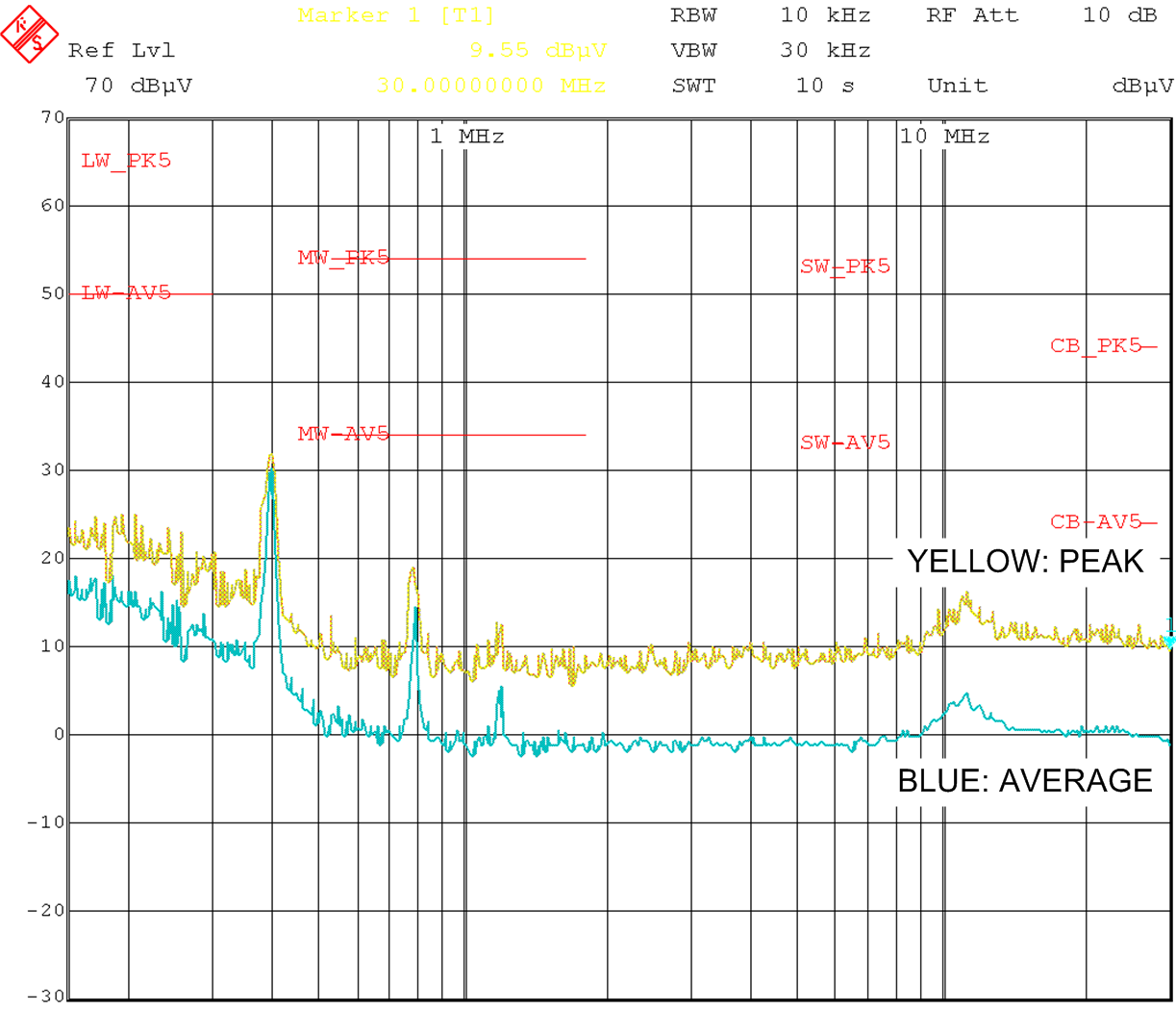

LMS3655-Q1 の効率:VOUT = 5V LMS3655-Q1 の伝導 EMI :VOUT = 5V、IOUT = 5A

LMS3655-Q1 の伝導 EMI :VOUT = 5V、IOUT = 5A