JAJSIO9E March 2014 – June 2021 TPS25200

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- DRV|6

サーマルパッド・メカニカル・データ

- DRV|6

発注情報

9.2.2.2 Input and Output Capacitance

Input and output capacitance improves the performance of the device; the actual capacitance must be optimized for the particular application. For all applications, a 0.1-µF or greater ceramic bypass capacitor between IN and GND is recommended as close to the device as possible for local noise decoupling.

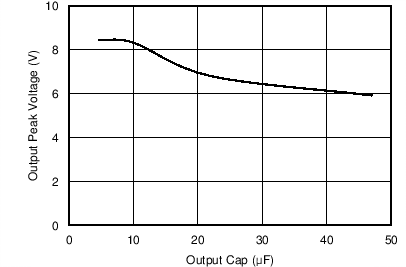

When VIN ramp up exceed 7.6 V, VOUT follows VIN until the TPS25200 turns off the internal MOSFET after t(OVLO_off_delay). Since t(OVLO_off_delay) largely depends on the VIN ramp rate, VOUT sees some peak voltage. Increasing the output capacitance can lower the output peak voltage as shown in Figure 9-3.

Figure 9-3 VOUT Peak Voltage vs COUT (VIN Step From 5 V to 15 V with 1-V/µs Ramp Up Rate)

Figure 9-3 VOUT Peak Voltage vs COUT (VIN Step From 5 V to 15 V with 1-V/µs Ramp Up Rate)