JAJSD75C August 2011 – February 2016 ADS8528 , ADS8548 , ADS8568

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics: General

- 7.6 Electrical Characteristics: ADS8528

- 7.7 Electrical Characteristics: ADS8548

- 7.8 Electrical Characteristics: ADS8568

- 7.9 Serial Interface Timing Requirements

- 7.10 Parallel Interface Timing Requirements (Read Access)

- 7.11 Parallel Interface Timing Requirements (Write Access)

- 7.12 Typical Characteristics

- 8 Parameter Measurement information

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

10 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

10.1 Application Information

The ADS85x8 enables high-precision measurement of up to eight analog signals simultaneously. The Typical Application section summarizes some of the typical use cases for the ADS85x8 and the main steps and components used around the analog-to-digital converter (ADC).

10.2 Typical Application

The accurate measurement of electrical variables in a power grid is extremely critical because this measurement helps determine the operating status and running quality of the grid. Such accurate measurements also help diagnose problems with the power network, thereby enabling prompt solutions and minimizing down time. The key electrical variables measured in 3-phase power systems are the three line voltages, the neutral voltage at the load, the three line currents, and the neutral return current; see Figure 45. These variables enable metrology and power automation systems to determine the amplitude, frequency, and phase information in order to perform harmonic analysis, power factor calculations, and power quality assessment, among others.

10.2.1 Design Requirements

To begin the design process, a few parameters must be decided upon. The designer must know the following:

- Output range of the potential transformers (elements labeled PT1, PT2, and PT3 in Figure 45)

- Output range of the current transformers (elements labeled CT1, CT2, and CT3 in Figure 45)

- Input impedance required from the analog front-end for each channel

- Fundamental frequency of the power system

- Number of harmonics that must be acquired, and

- Type of signal conditioning required from the analog front-end for each channel

10.2.2 Detailed Design Procedure

Figure 46 shows the topology chosen to meet the design requirements.

NOTE

A feedback capacitor CF is included in order to provide a low-pass filter characteristic and attenuate signals outside the band of interest.

Figure 46. Op Amp in an Inverting Configuration

Figure 46. Op Amp in an Inverting Configuration

The potential transformers and current transformers used in the system depicted in Figure 45 provide the eight inputs required. These transformers have a ±10-V output range. Although the PT and CT elements provide isolation from the power system, the value of RIN is selected as 100 kΩ in order to provide an additional, high-impedance safety element in the current path leading up to the input of the ADC. Moreover, selecting a low-frequency gain of –1 V/V (as shown in Equation 5) provides a ±10-V output that can be fed into the ADS8568; therefore, the value of RF is selected as 100 kΩ too.

The primary goal of the acquisition system depicted in Figure 45 is to measure up to 20 harmonics in a 60-Hz power network. With this goal in mind, the analog front-end must have sufficient bandwidth to measure signals up to 1260 Hz as shown in Equation 6.

Based on the bandwidth from in Equation 6, the ADS8568 is set to simultaneously sample all six channels at 15.36 kSPS, thus providing enough samples to clearly resolve even the highest harmonic required.

The passband of the configuration shown in Figure 46 is determined by the –3-dB frequency according to Equation 7. The value of CF is selected as 820 pF because CF is a standard capacitance value available in 0603 size (surface-mount component) and such values, combined with that of RF, result in sufficient bandwidth to accommodate the required 20 harmonics (at 60 Hz).

The value of R1 is selected as the parallel combination of RIN and RF to prevent the input bias current of the operational amplifier from generating an offset error.

The value of component C1 is chosen as 0.1 µF to provide a low-impedance path for noise signals that can be picked up by R1, thus improving the EMI robustness and noise performance of the system.

The OPA2277 is chosen for its low input offset voltage, low drift, bipolar swing, sufficient gain-bandwidth product, and low quiescent current. For additional information on the procedure to select SAR ADC input drivers, see the TIPD151 verified design guide, 16-Bit 100-KSPS 4-Channel Multiplexed Data Acquisition System Design Guide.

The charge injection damping circuit is composed by R2 (49.9 Ω) and C2 (370 pF); these components reject high-frequency noise and meet the settling requirements of the ADS8568 input.

Figure 47 shows the reference block used in this design.

Figure 47. Reference Block

Figure 47. Reference Block

For more information on the design of charge injection damping circuits and reference driving circuits for SAR ADCs, see the TIPD149 verified design reference guide, Power-Optimized 16-Bit 1-MSPS Data Acquisition Block for Lowest Distortion and Noise.

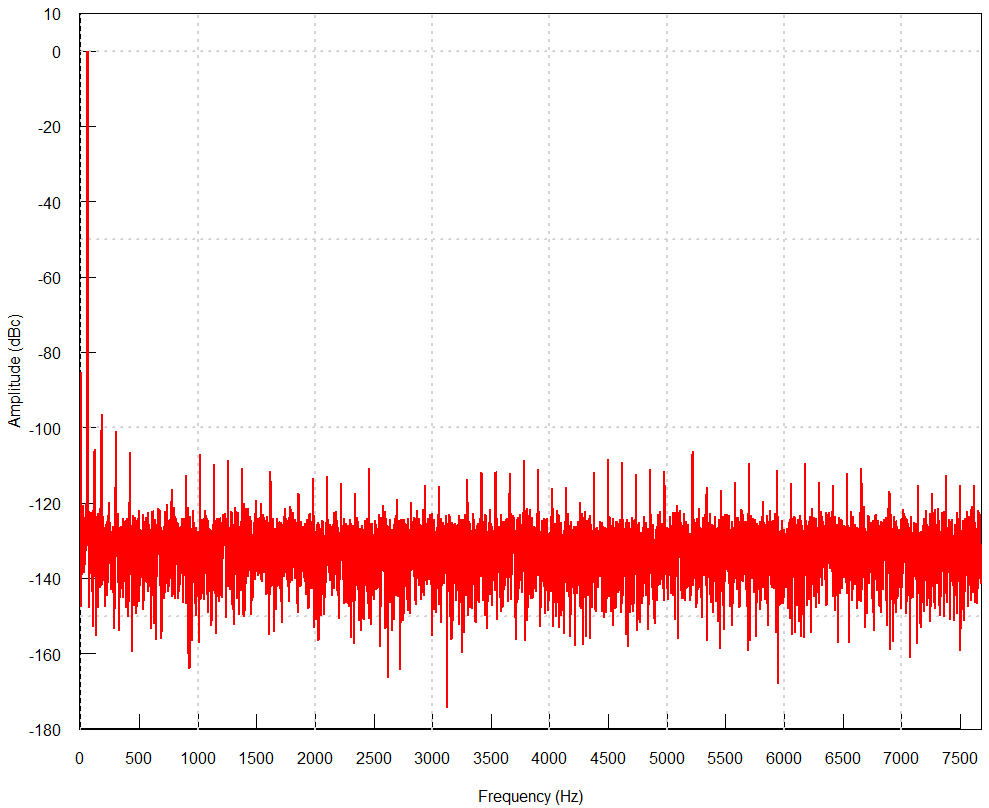

10.2.3 Application Curve

Figure 48 shows the frequency spectrum of the data acquired by the ADS8568 for a sinusoidal, 20-VPP input at 60 Hz.

Figure 48. Frequency Spectrum for a Sinusoidal 20-VPP Signal at 60 Hz

Figure 48. Frequency Spectrum for a Sinusoidal 20-VPP Signal at 60 Hz

The ac performance parameters are:

- SNR: 91.16 dB

- THD: –94.34 dB

- SNDR: 89.45 dB

- SFDR: 96.56 dB