LDO および SPI 内蔵 TIOL221 デュアル チャネル IO-Link デバイス PHY

1 特長

- 電源電圧: 7V~36V

- 補助デジタル出力 (DO) チャネルとデジタル入力 (DI) チャネルを搭載した、IO-Link が構成可能な CQ 出力

- ピン制御または SPI により構成可能

- CQ および DO の両チャネルを IO-link メイン モジュールで使用するように構成可能

- PNP、NPN、または IO-Link が構成可能な CQ 出力

- IEC 61131-9 COM1、COM2、COM3 のデータレートをサポート

- ≥60m までの長いケーブル長をサポート

- 低消費電力で高い構成能力の出力ドライバ

- 低  $R_{DS(ON)}$  2.5Ω (標準値)

- アクティブ ドライバの電流制限機能

- ドライバの過電流制限を設定可能: 50mA~500mA

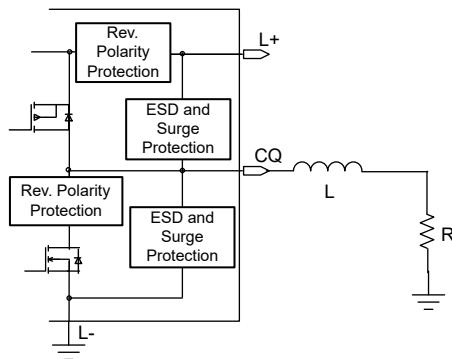

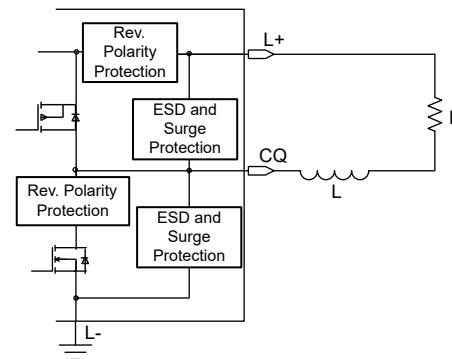

- LP、CQ、DO、DI で最大 65V のアクティブ逆極性保護

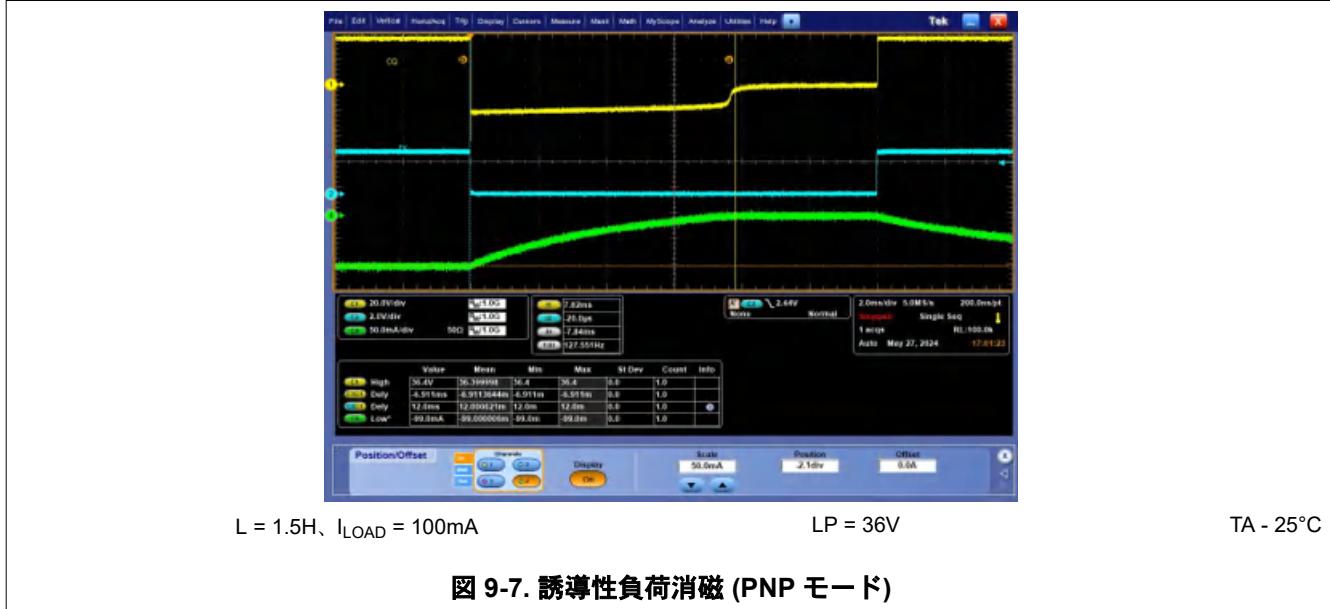

- 誘導性負荷に対する安全で高速な消磁

- 堅牢なシステムのための保護機能を内蔵

- 過電流、過熱、UVLO フォルトのフォルト インジケータ

- 拡張周囲温度動作範囲: -40°C~125°C

- ±8kV IEC 61000-4-2 ESD 接触放電

- ±4kV IEC 61000-4-4 電気的高速過渡

- ±1.2kV、500Ω の IEC 61000-4-5 サージ

- 大容量誘導性負荷駆動能力

- 最大電流 20mA 対応の LDO を搭載

- オプションの外部レギュレータ入力 (5V) により、LDO の内部消費電力を低減

- スペースを節約する小型のパッケージ オプション

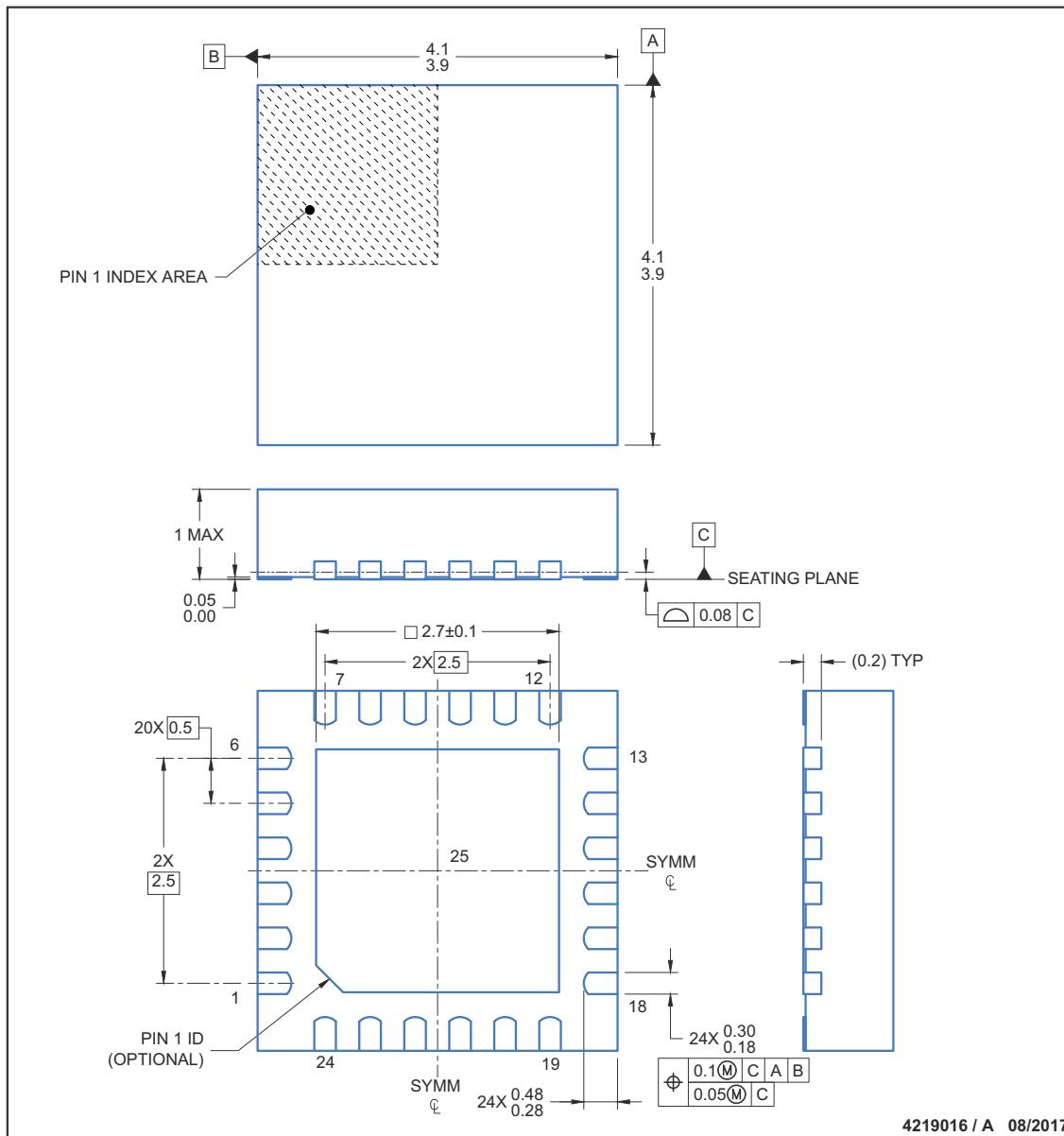

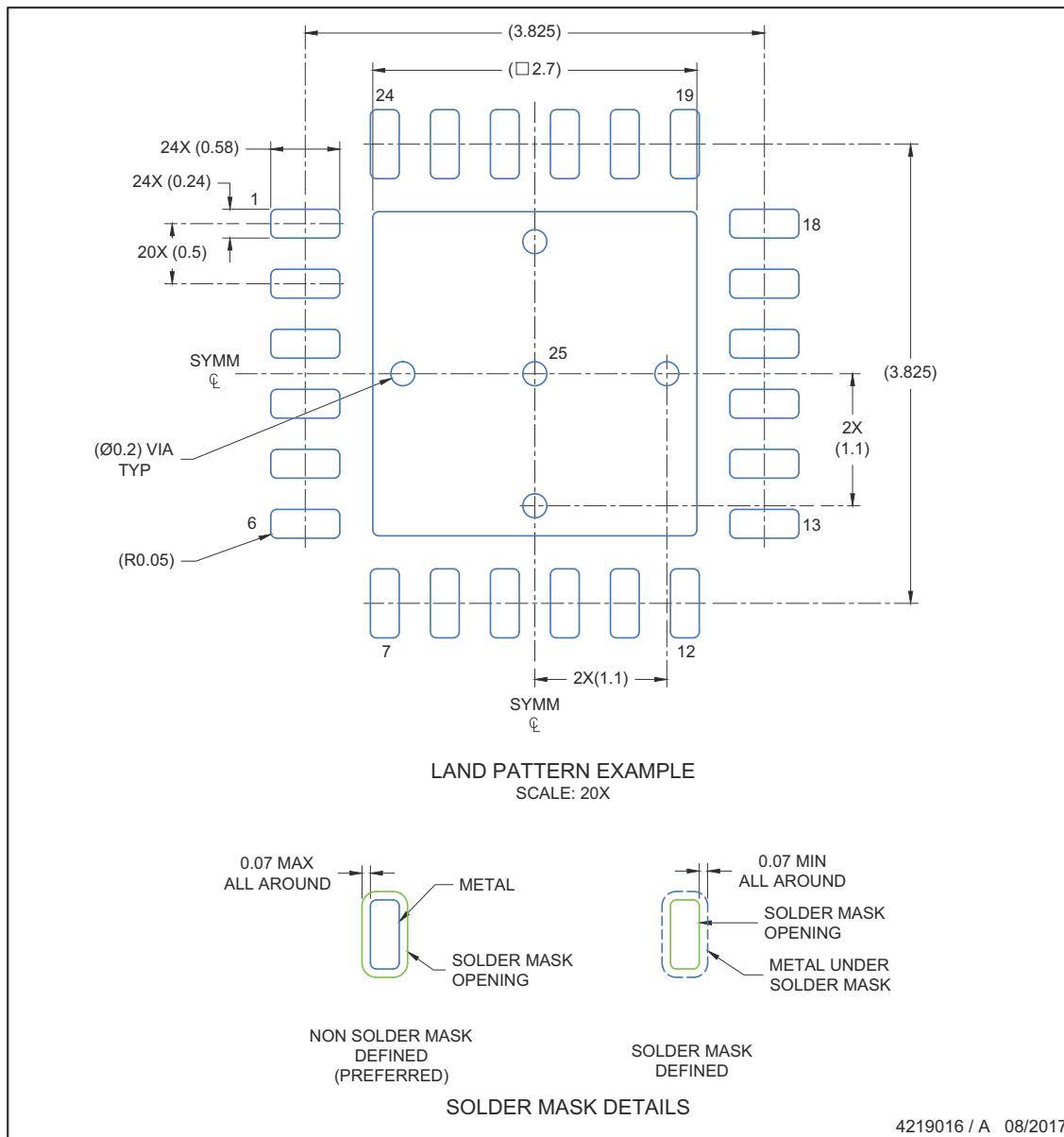

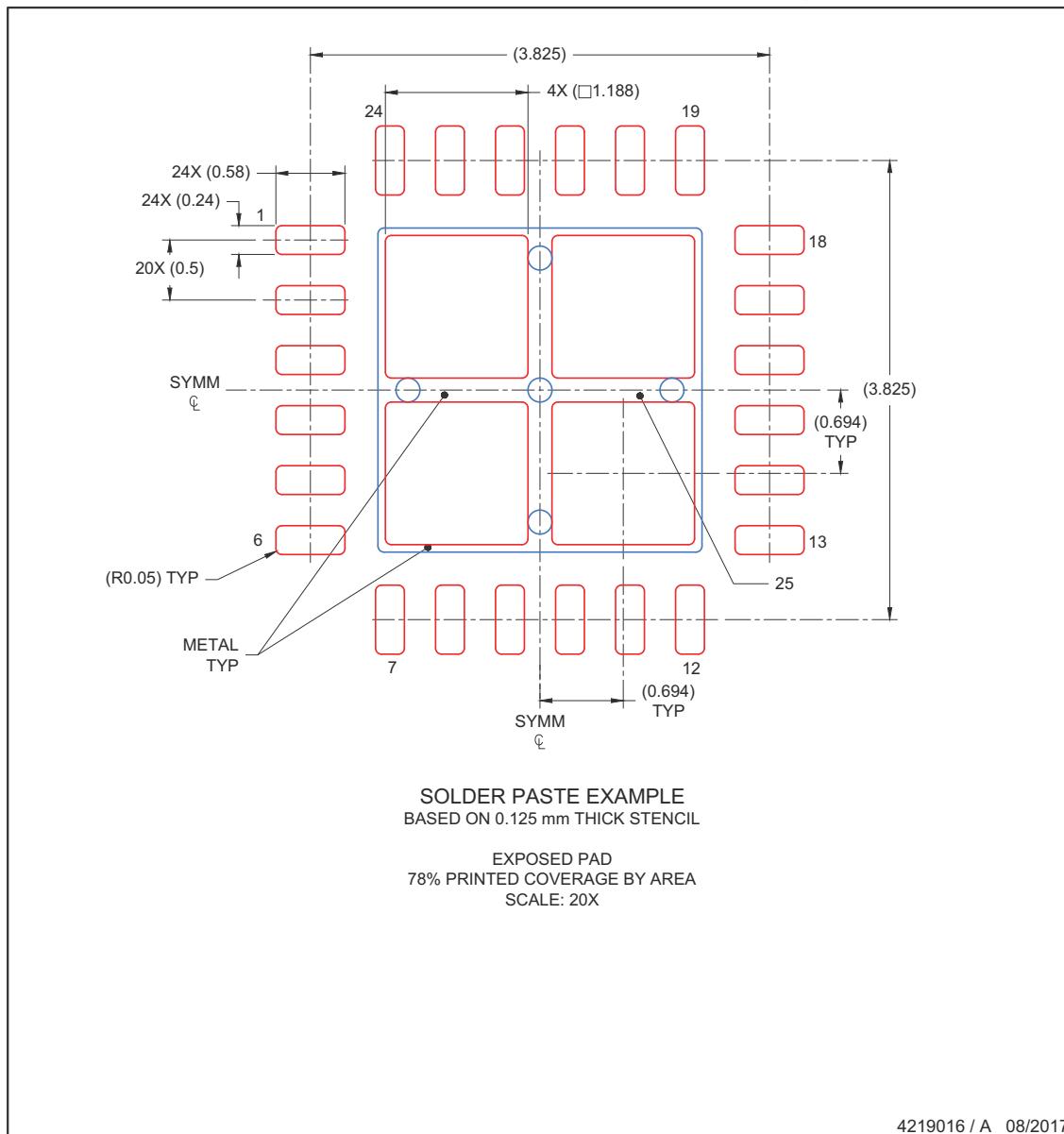

- 4mm × 4mm VQFN パッケージ

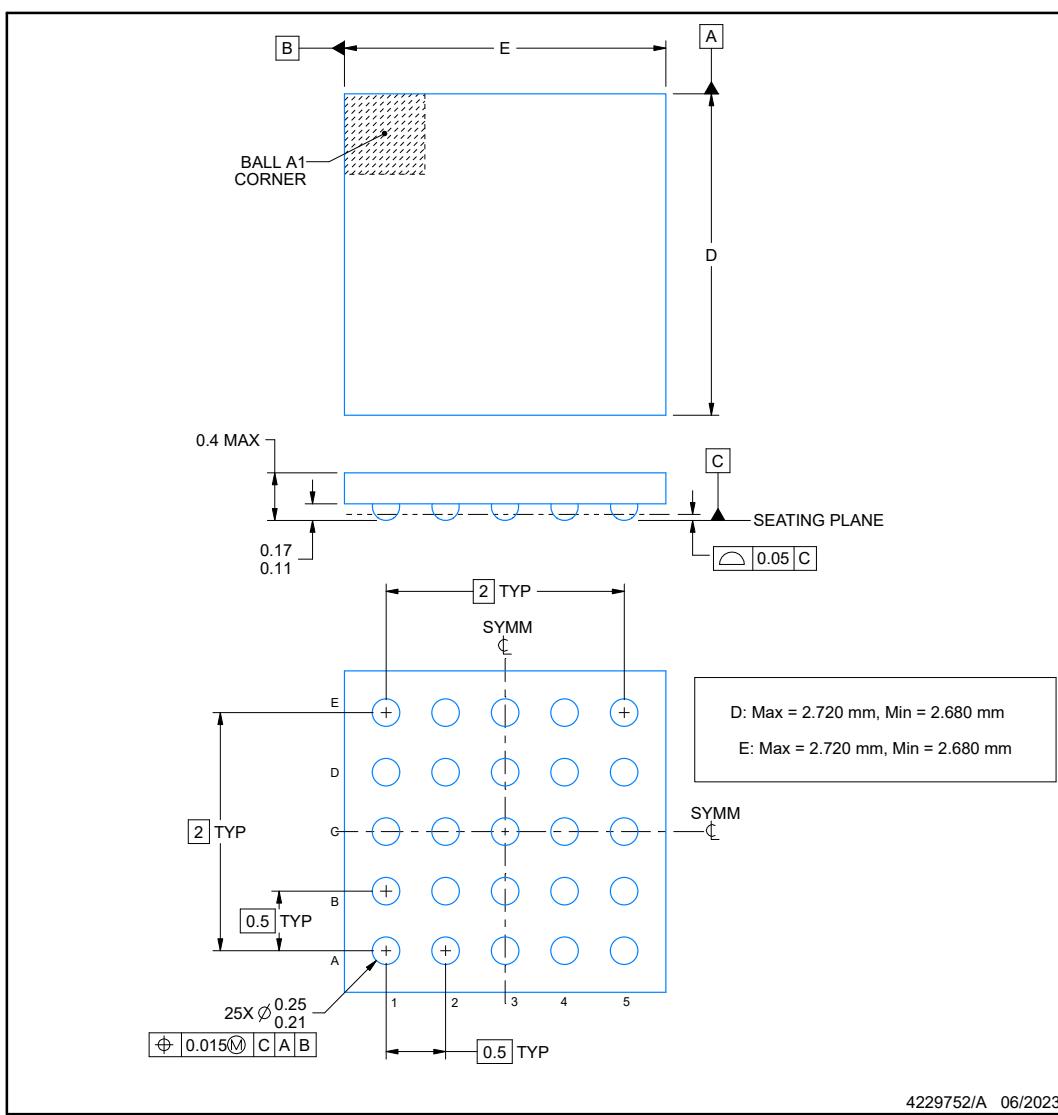

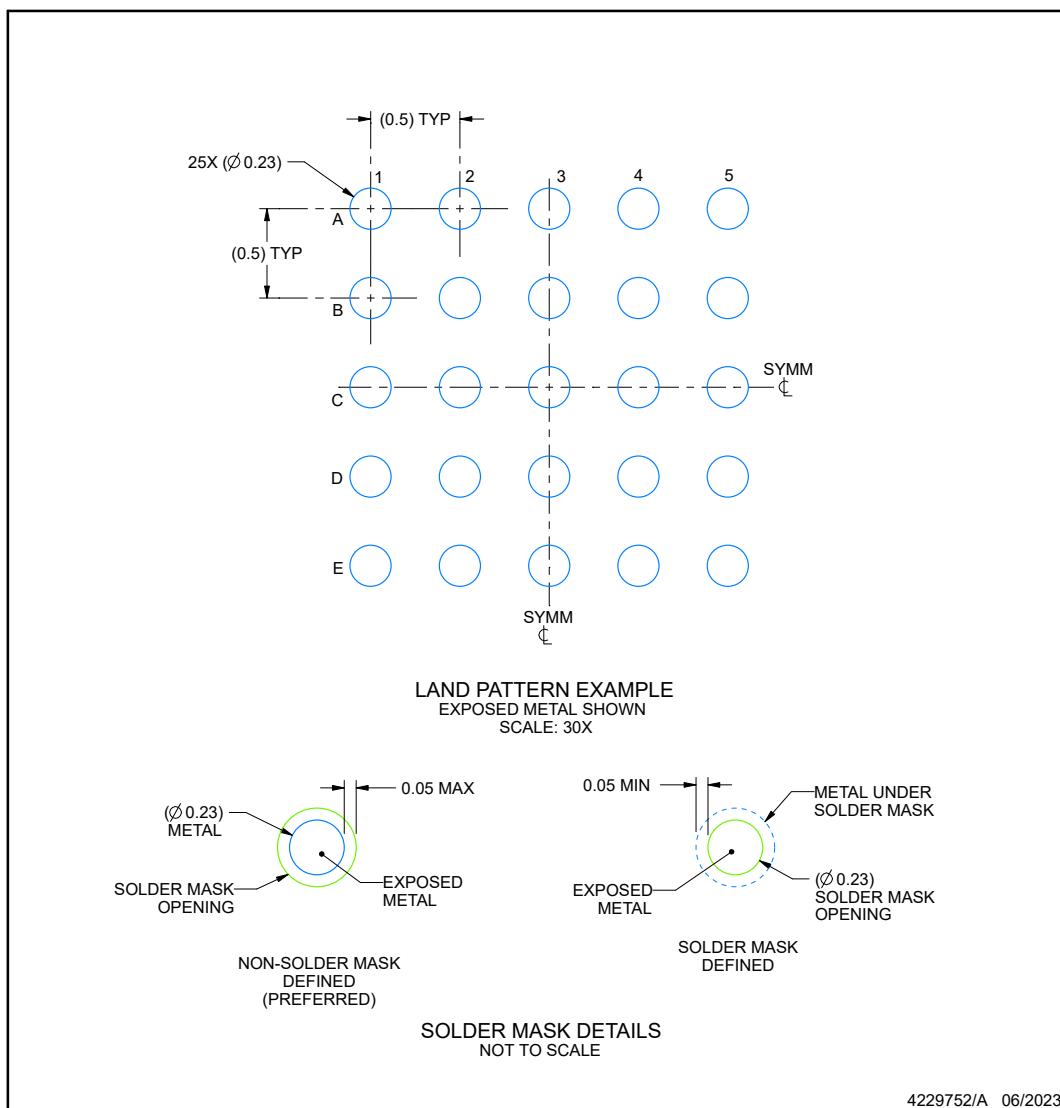

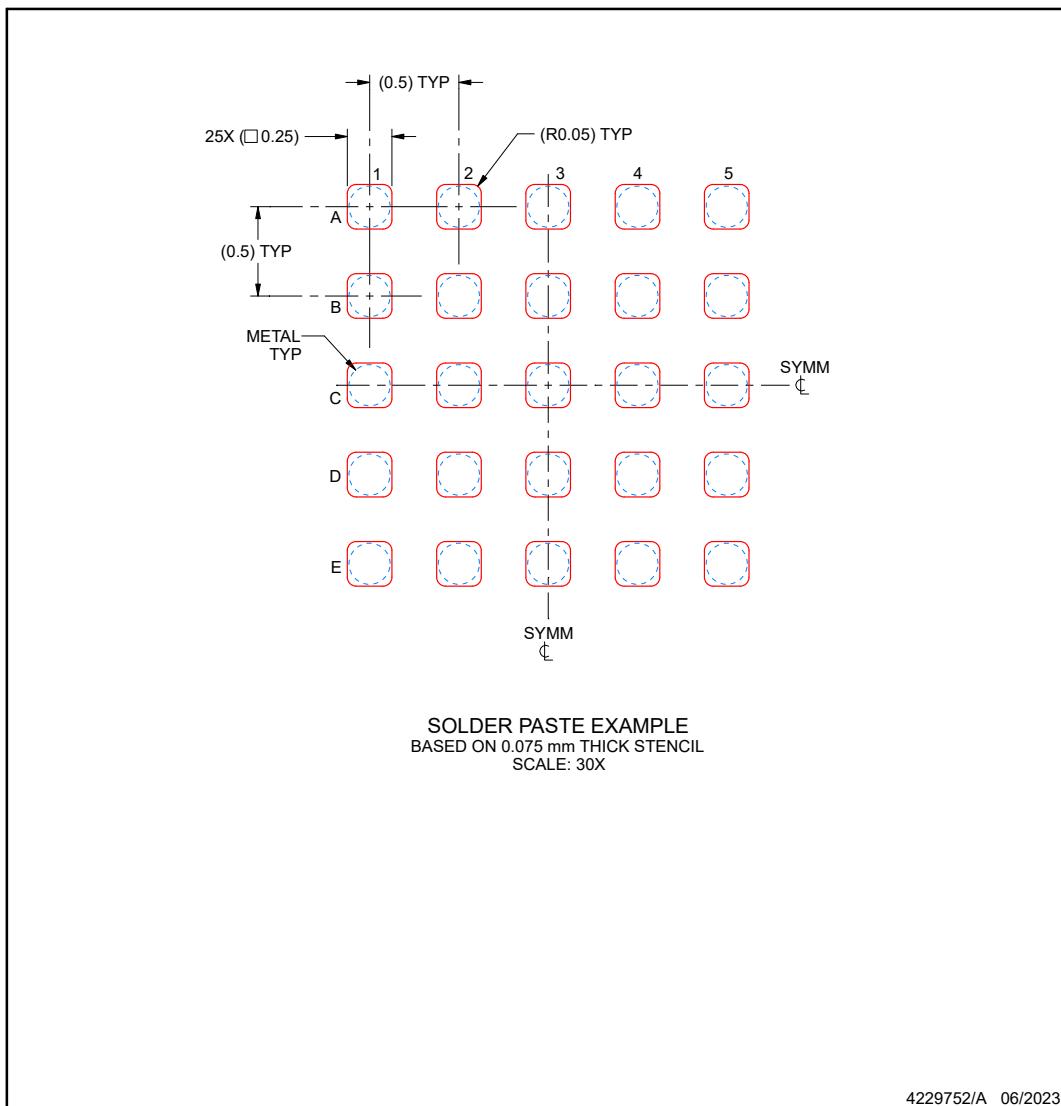

- 2.7mm × 2.7mm DSBGA パッケージ

## 2 アプリケーション

- フィールドトランシミッタおよびアクチュエータ

- ファクトリオートメーション

- プロセスオートメーション

- リモートIOのIO-link PHY

### 3 説明

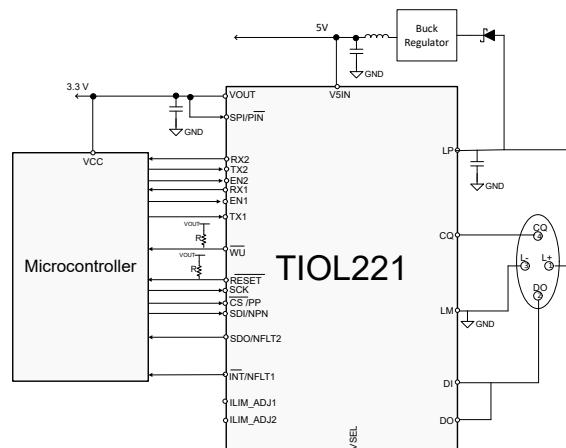

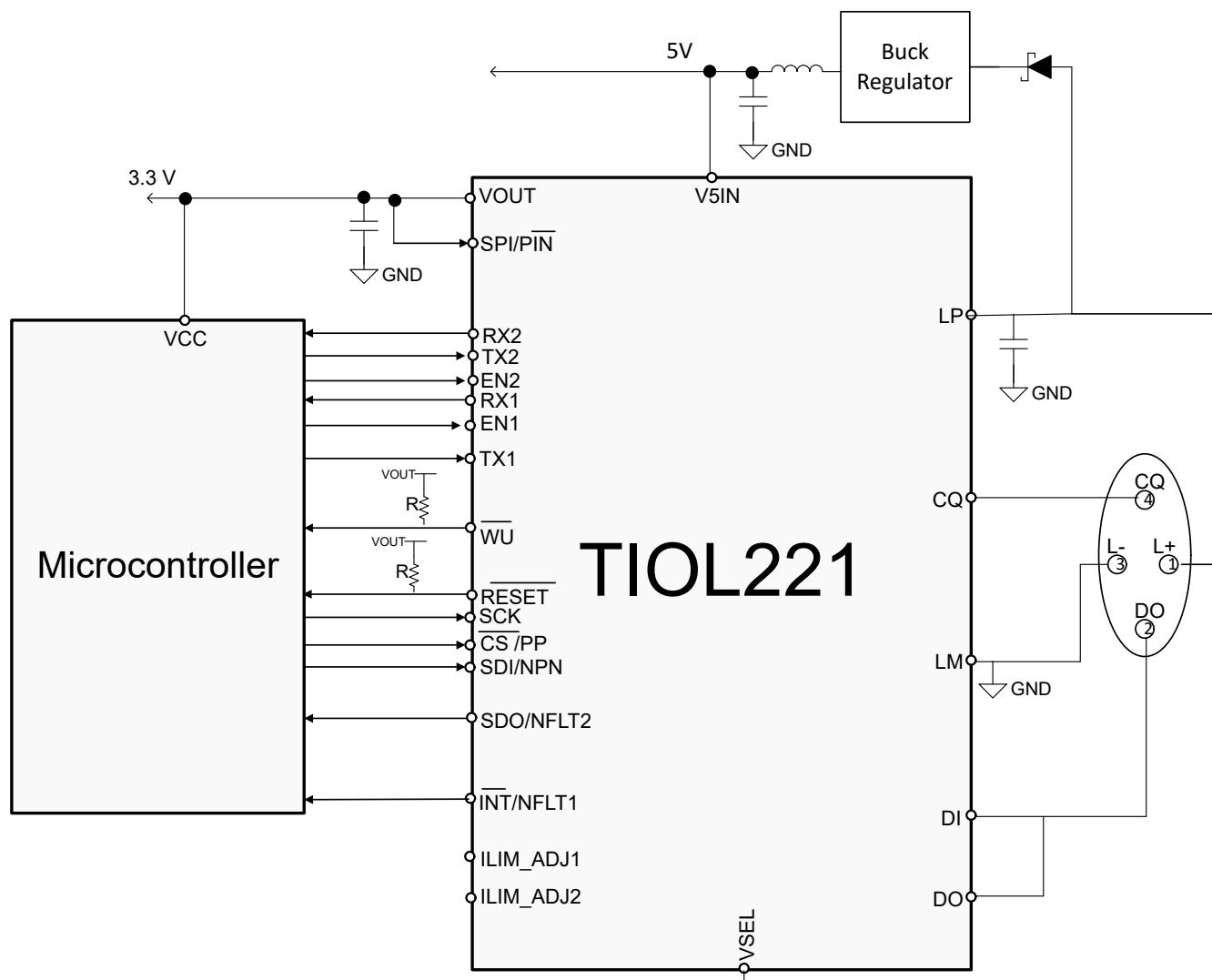

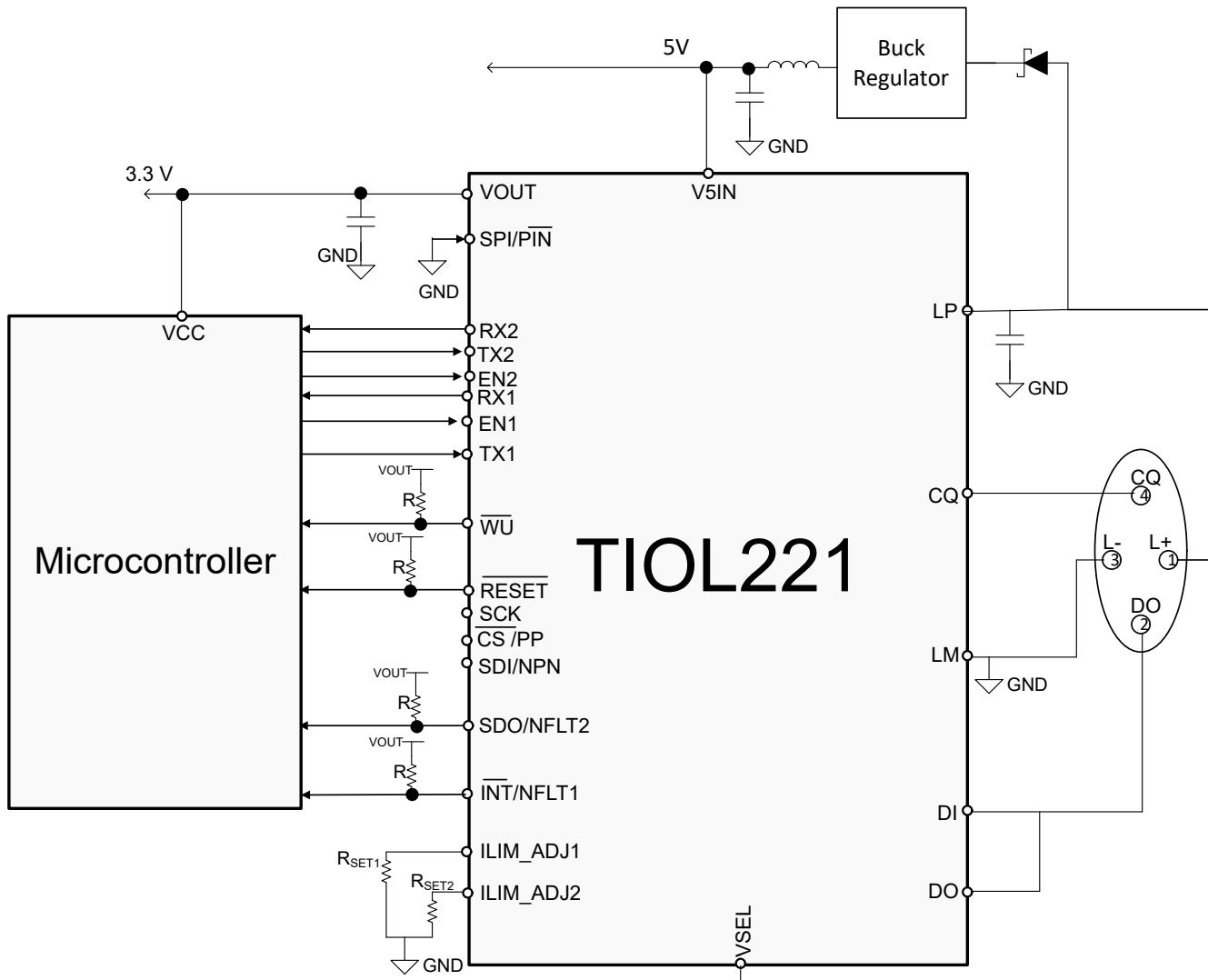

**TIOL221** トランシーバは、アクティブ逆極性保護機能を備えたデュアル低消費電力出力ドライバを内蔵しています。デバイスが 3 線式のインターフェイス経由で **IO-Link** マスターに接続されているとき、コントローラはリモートノードとの通信を開始してデータを交換でき、**TIOL221** は通信の完全な物理レイヤとして機能します。このデバイスには、補助 DI チャンネルも内蔵されています。

このデバイスは、最大 1.2kV (500Ω) の IEC 61000-4-5 サージに耐えることができ、また、逆極性保護を内蔵しています。構成可能で拡張された診断機能を有する SPI に加えて、シンプルなピン プログラマブル インターフェイスによりコントローラの回路と簡単に接続できます。出力電流制限は、外付け抵抗を使用して構成するか、SPI 経由で構成済みの制限値を使用して構成できます。TIOL221 は ウエークアップ パルスを生成するように構成することができ、IO-Link のマスター アプリケーションで使用できます。低電圧、過電流、過熱状態に対するフォルト通知および内部保護機能を備えています。

パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup>      | パッケージ サイズ <sup>(2)</sup> |

|---------|---------------------------|--------------------------|

| TIOL221 | VQFN (24)                 | 4 mm × 4 mm              |

|         | DSBGA (25) <sup>(3)</sup> | 2.7mm × 2.7 mm           |

- (1) 詳細については、セクション 12 を参照してください。

(2) パッケージサイズ(長さ×幅)は公称値であり、該当する場合はビンも含まれます。

(3) 製品レビュー

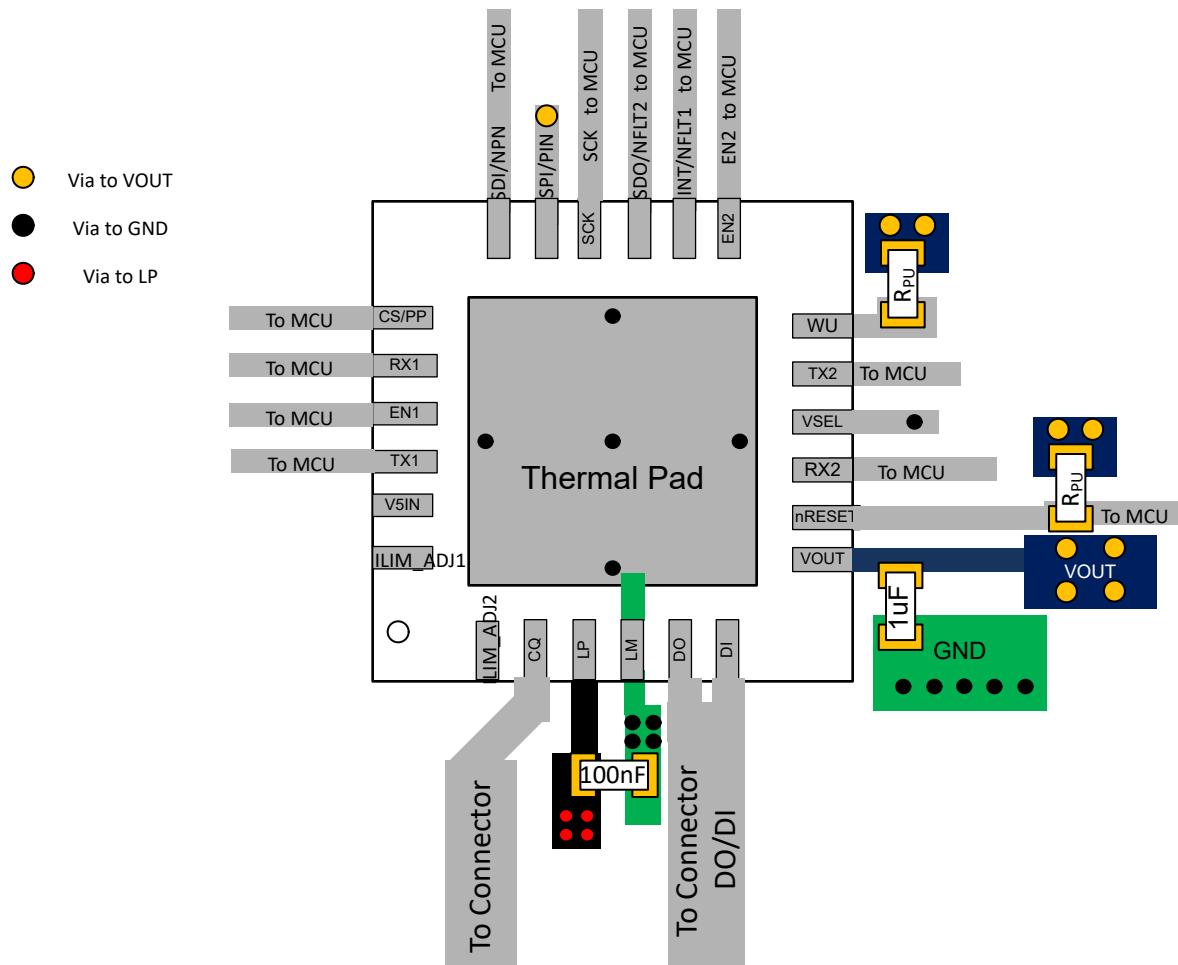

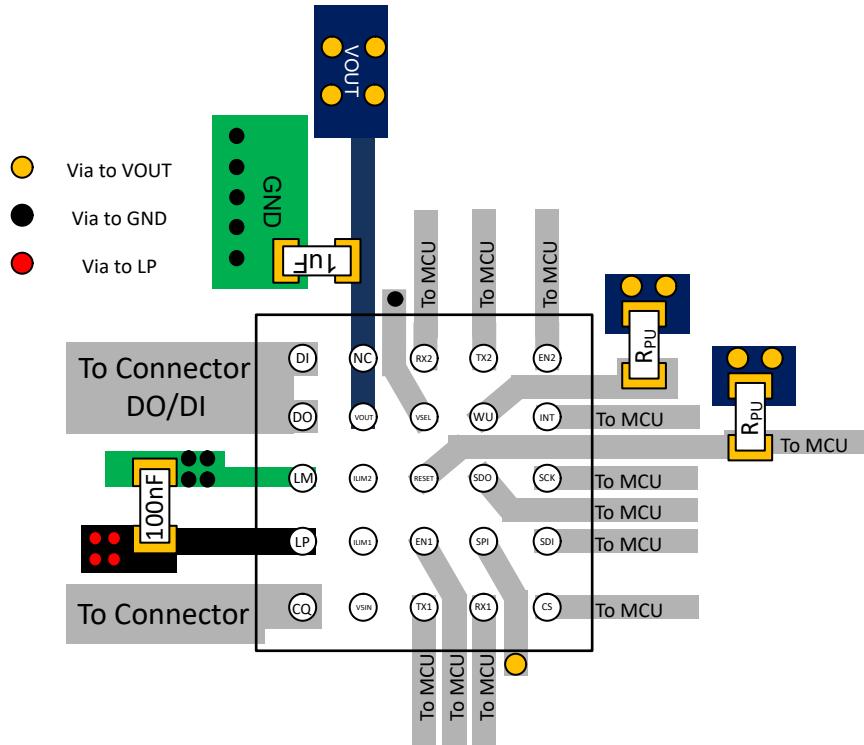

#### 代表的なアプリケーションの図

## 目次

|                     |    |                         |    |

|---------------------|----|-------------------------|----|

| 1 特長                | 1  | 7.4 デバイスの機能モード          | 26 |

| 2 アプリケーション          | 1  | 7.5 SPI のプログラミング        | 27 |

| 3 説明                | 1  | 8 TIOL221 のレジスタ         | 30 |

| 4 ピン構成および機能         | 3  | 9 アプリケーションと実装           | 41 |

| 5 仕様                | 5  | 9.1 アプリケーション情報          | 41 |

| 5.1 絶対最大定格          | 5  | 9.2 代表的なアプリケーション        | 41 |

| 5.2 ESD 定格          | 5  | 9.3 電源に関する推奨事項          | 44 |

| 5.3 ESD 定格 - IEC 仕様 | 5  | 9.4 レイアウト               | 45 |

| 5.4 推奨動作条件          | 5  | 10 デバイスおよびドキュメントのサポート   | 47 |

| 5.5 熱に関する情報         | 6  | 10.1 ドキュメントのサポート        | 47 |

| 5.6 電気的特性           | 6  | 10.2 ドキュメントの更新通知を受け取る方法 | 47 |

| 5.7 スイッチング特性        | 9  | 10.3 サポート・リソース          | 47 |

| 5.8 代表的特性           | 12 | 10.4 商標                 | 47 |

| 6 パラメータ測定情報         | 13 | 10.5 静電気放電に関する注意事項      | 47 |

| 7 詳細説明              | 17 | 10.6 用語集                | 47 |

| 7.1 概要              | 17 | 11 改訂履歴                 | 47 |

| 7.2 機能ブロック図         | 18 | 12 メカニカル、パッケージ、および注文情報  | 48 |

| 7.3 機能説明            | 18 | 12.1 メカニカル データ          | 49 |

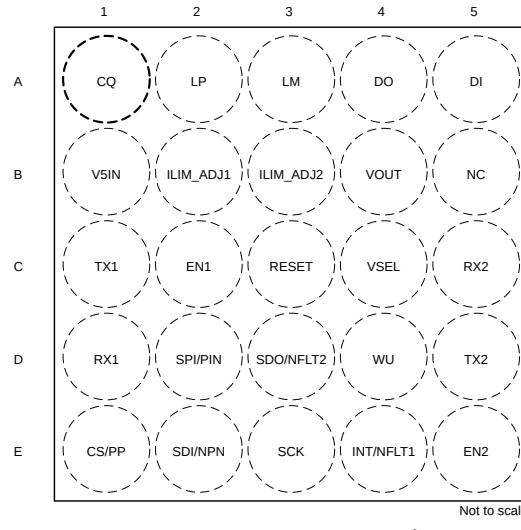

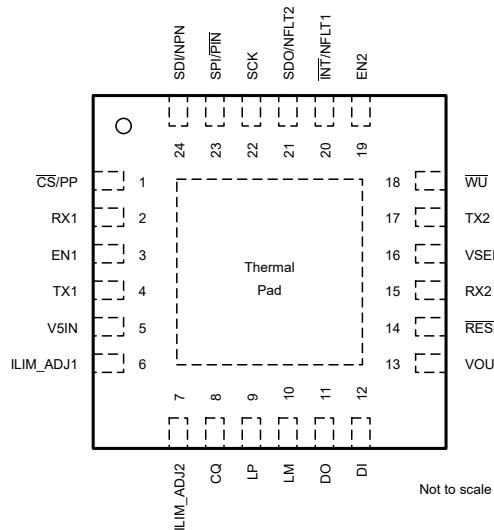

## 4 ピン構成および機能

図 4-1. RGE (VQFN)、24 ピン

(上面図)

図 4-2. YAH (DSBGA)、25 ピン

(上面図、バンプダウン)

表 4-1. ピンの機能

| ピン名       | ピン番号 |       | タイプ <sup>(1)</sup> | タイプ     | 説明                                                                               |

|-----------|------|-------|--------------------|---------|----------------------------------------------------------------------------------|

|           | VQFN | DSBGA |                    |         |                                                                                  |

| CQ        | 8    | A1    | I/O                | 高電圧     | IO-Link 信号データピン。                                                                 |

| CS/PP     | 1    | E1    | I                  | デジタル    | SPI モードのチップセレクト入力ピン。<br>ピンモードでのプッシュプル モード選択入力                                    |

| DI        | 12   | A5    | I                  | 高電圧     | DI レシーバ入力。DI レシーバ出力は、RX2 ピンで監視できます。                                              |

| DO        | 11   | A4    | O                  | 高電圧     | DO ドライバ出力。DO は、TX2 ピンの入力の逆ロジック レベルです。                                            |

| EN1       | 3    | C2    | I                  | 低電圧デジタル | CQ ドライバがローカル コントローラからの入力信号を有効にします。ロジック Low では、CQ 出力がハイ インピーダンスに設定されます。弱い内部ブルダウン。 |

| EN2       | 19   | E5    | I                  | 低電圧デジタル | DO ドライバがローカル コントローラからの入力信号を有効にします。ロジック Low では、DO 出力がハイ インピーダンスに設定されます。弱い内部ブルダウン。 |

| ILIM_ADJ1 | 6    | B2    | I                  | 低電圧アナログ | CQ ドライバの電流制限調整の入力。ILIM_ADJ1 と LM との間に抵抗 RSET1 を接続します。                            |

| ILIM_ADJ2 | 7    | B3    | I                  | 低電圧アナログ | DO ドライバの電流制限調整の入力。ILIM_ADJ2 と LM との間に抵抗 RSET2 を接続します。                            |

| INT/NFLT1 | 20   | E4    | O                  | 低電圧デジタル | CQ チャネル、オープンドレイン (ピンモード) の割り込み出力、プッシュプル (SPI モード) またはフォルト インジケータ                 |

| LM        | 10   | A3    | G                  | グランド    | グランド。                                                                            |

| LP        | 9    | A2    | PI                 | 高電圧     | デバイスへの電源入力 (標準値 24V)。1μF コンデンサを LM (グランド) に、デバイスにできる限り近づけて接続します。                 |

| NC        | --   | B5    | NC                 | 接続なし    | 内部未接続。                                                                           |

| RX1       | 2    | D1    | O                  | 低電圧デジタル | C/Q レシーバ ロジック出力。RX2 は、CQ 入力における信号の逆ロジック レベルです。                                   |

| RX2       | 15   | C5    | O                  | 低電圧デジタル | DI レシーバ ロジック出力。RX2 は、DI 入力における信号の逆ロジック レベルです。                                    |

| SCK       | 22   | E3    | I                  | 低電圧デジタル | SPI クロック入力。                                                                      |

| SDI/NPN   | 24   | E2    | I                  | 低電圧デジタル | SPI シリアル データ入力 (SPI モード)<br>または NPN モード セレクタ (ピンモード)                             |

**表 4-1. ピンの機能 (続き)**

| ピン名       | ピン番号     |       | タイプ <sup>(1)</sup> | タイプ     | 説明                                                                                                                                                                                                                         |

|-----------|----------|-------|--------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | VQFN     | DSBGA |                    |         |                                                                                                                                                                                                                            |

| SDO/NFLT2 | 21       | D3    | O                  | 低電圧デジタル | SPI シリアル データ出力、プッシュプル (SPI モード) または DO チャネル用フォルト インダクタ、オープンドレイン (ピンモード)                                                                                                                                                    |

| SPI/PIN   | 23       | D2    | I                  | 低電圧デジタル | SPI またはピンモード選択入力。ピンモード動作を行う場合は、このピンを Low に駆動します。SPI モード制御を行う場合は、このピンを High に駆動します。                                                                                                                                         |

| TX1       | 4        | C1    | I                  | 低電圧デジタル | ローカル マイコンからの CQ ドライバ入力データ。弱い内部プルアップ。                                                                                                                                                                                       |

| TX2       | 17       | D5    | I                  | 低電圧デジタル | ローカル マイコンからの DO ドライバ入力データ。弱い内部プルアップ。                                                                                                                                                                                       |

| VOUT      | 13       | B4    | PO                 | 低電圧     | LDO レギュレータ出力。出力レベルは VSEL ピンにより決定されます                                                                                                                                                                                       |

| VSEL      | 16       | C4    | I                  | 低電圧     | <ul style="list-style-type: none"> <li>3.3V LDO 出力の場合は、LP を LDO 入力電源として使用し、GND に接続します</li> <li>5V LDO 出力の場合は、LP を LDO 入力電源として使用し、VOUT に接続します</li> <li>3.3V LDO 出力の場合は、V5IN を LDO 入力電源として使用し、このピンをフローティングのままにします</li> </ul> |

| リセット      | 14       | C3    | O                  | 低電圧     | 出力ピン、オープンドレイン、アクティブ Low をリセットします。このピンはリセットピンとして動作し、LP または VOUT の UV を示します。                                                                                                                                                 |

| V5IN      | 5        | B1    | PI                 | 低電圧     | (オプション) この 5V 電源入力ピンを外部レギュレータから接続して、内部レギュレータからの消費電力を低減できます。使わない場合は、このピンをフローティングのままにします。                                                                                                                                    |

| WU        | 18       | D4    | O                  | 低電圧デジタル | ローカル マイコンへのウェークアップ インジケータ。オープンドレイン出力。このピンはプルアップ抵抗を介して VOUT に接続します。                                                                                                                                                         |

| サーマル パッド  | サーマル パッド | 該当なし  | G                  | グランド    | 最適な熱特性と電気的性能を実現するため、露出したサーマル パッドをグランド (LM) に接続します                                                                                                                                                                          |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                                                                                                                                                                                                                                                         |                                     | 最小値  | 最大値                           | 単位 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------|-------------------------------|----|

| LP, CQ, DO, DI                                                                                                                                                                                                                                          | LP, CQ, DO, DI の定常状態電圧              | -65  | 65                            | V  |

|                                                                                                                                                                                                                                                         | LP, CQ, DO, DI の過渡パルス幅 < 100μs      | -70  | 70                            | V  |

| V <sub>(LP)</sub> - V <sub>(CQ)</sub>  ,  V <sub>(LP)</sub> - V <sub>(DO)</sub>  ,  V <sub>(LP)</sub> - V <sub>(DI)</sub>  ,  V <sub>(CQ)</sub> - V <sub>(DO)</sub>  ,  V <sub>(CQ)</sub> - V <sub>(DI)</sub>  ,  V <sub>(DO)</sub> - V <sub>(DI)</sub> | バスピン間の電圧降下                          |      | 65                            | V  |

| V <sub>OUT</sub>                                                                                                                                                                                                                                        | レギュレータ出力電圧                          | -0.3 | 6                             | V  |

| TX1, TX2, EN1, EN2, VSEL, RX1, RX2, CS/PP, SDI/NPN, SDO/NFLT2, SCK, INT/NFLT1, WU, ILIM_ADJ1, ILIM_ADJ2, SPI/PIN                                                                                                                                        | ロジックピン電圧                            | -0.3 | 最小 (V <sub>OUT</sub> +0.3, 6) | V  |

| 出力電流                                                                                                                                                                                                                                                    | RX1, RX2, WU, INT/NFLT1, SDO/NFLT2, | -5   | 5                             | mA |

| 保管温度, T <sub>stg</sub>                                                                                                                                                                                                                                  |                                     | -55  | 170                           | °C |

- (1) 「絶対最大定格」外での操作は、デバイスに恒久的な損傷を引き起こす可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内で、一時的に「推奨動作条件」の範囲を超えた動作をさせる場合、必ずしもデバイスが損傷を受けるものではありませんが、完全には機能しない可能性があります。この方法でデバイスを動作させると、デバイスの信頼性、機能性、性能に影響を及ぼし、デバイスの寿命を短縮する可能性があります。特に指定のない限り、すべての電圧値は L ピンを基準としています。

### 5.2 ESD 定格

|                    |      |                                                            | 値      | 単位    |   |

|--------------------|------|------------------------------------------------------------|--------|-------|---|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM), ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>      | すべてのピン | ±4000 | V |

| V <sub>(ESD)</sub> | 静電放電 | デバイス帯電モデル (CDM), ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup> | すべてのピン | ±750  | V |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 ESD 定格 - IEC 仕様

|                    |      |                                                                           | 値      | 単位 |

|--------------------|------|---------------------------------------------------------------------------|--------|----|

| V <sub>(ESD)</sub> | 静電放電 | IEC 61000-4-2 ESD (接触放電), LP, CQ, DO, DI, LM <sup>(1) (2)</sup>           | ±8,000 | V  |

|                    | 静電放電 | IEC 61000-4-5, 1.2μs/50μs サージ、直列 500 Ω, LP, CQ, DO, DI, LM <sup>(1)</sup> | ±1,200 |    |

|                    | 静電放電 | IEC 61000-4-4 EFT (高速過渡またはバースト), LP, CQ, DO, DI, LM <sup>(1)</sup>        | ±4,000 |    |

- (1) LP と LMとの間には、最低 100nF のコンデンサが必要です。V<sub>OUT</sub> と LM との間には、最低 1μF のコンデンサが必要です。

(2) デバイスでは、±8000V を通過させるために、CQ/DO ドライバ出力と LM の間に最小 1nF のコンデンサが必要です。合格レベルは、最小 1nF のコンデンサなしで ±4000V です

### 5.4 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                      |                                                               | 最小値     | 公称値 | 最大値 | 単位   |

|----------------------|---------------------------------------------------------------|---------|-----|-----|------|

| V <sub>(LP)</sub>    | 24V 入力電源電圧                                                    | 7       | 24  | 36  | V    |

| V <sub>(VSSIN)</sub> | 5V 入力電源電圧                                                     | 4.5     | 5   | 5.5 | V    |

| V <sub>(I)</sub>     | TX1, TX2, EN1, EN2, CS/PP, SDI/NPN, SCK, SPI/PIN のロジックレベル入力電圧 | 3.3V 構成 | 3   | 3.3 | 3.6  |

|                      |                                                               | 5V 構成   | 4.5 | 5   | 5.5  |

| 1/t <sub>BIT</sub>   | データレート (通信モード)                                                |         |     | 250 | kbps |

| I <sub>(VOUT)</sub>  | LDO 出力電流                                                      |         |     | 20  | mA   |

| T <sub>A</sub>       | 動作時周囲温度                                                       | -40     |     | 125 | °C   |

| T <sub>J</sub>       | 接合部温度                                                         | -40     |     | 150 | °C   |

## 5.5 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                   | TIOL221     |             | 単位   |

|-----------------------|-------------------|-------------|-------------|------|

|                       |                   | RGE (24 ピン) | YAH (25 ピン) |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 32.2        | 58.5        | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 27.2        | 0.2         | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 11.4        | 14.5        | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 0.3         | 0.1         | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 11.4        | 14.3        | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)への熱抵抗 | 2.7         | 該当なし        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、[yes アプリケーションノート](#)を参照してください。

## 5.6 電気的特性

推奨動作条件および推奨自由空気温度範囲を超える場合(特に記述のない限り)。LP = 24V、V<sub>VOUT</sub> = 3.3V、T<sub>A</sub> = 25°C の場合の標準的な値(特に記述のない限り)。

| パラメータ                              | テスト条件                                                   |                                                                                                                                              | 最小値                                                     | 標準値 | 最大値  | 単位   |

|------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|------|------|

| <b>電源 (LP)</b>                     |                                                         |                                                                                                                                              |                                                         |     |      |      |

| I <sub>(LP-SHDN)</sub>             | シャットダウン モードでの電源静止電流                                     | CQ TX および RX、DO、DI はディスエーブルになります。VOUT で無負荷 SPI モードのみ                                                                                         |                                                         | 1.2 | 2.1  | mA   |

| I <sub>(LP-RX-ONLY)</sub>          | 入力のみがイネーブルされたときの電源電流                                    | CQ と DO はディセーブルになります。CQ RX および DI はイネーブルになります。VOUT で無負荷。<br>R <sub>SETx</sub> ≥ 10kΩ (電流制限 < 500mA)、EN1 = EN2 = L                            | CQ と DO はディセーブルになります。CQ RX および DI はイネーブルになります。VOUT で無負荷 | 1.4 | 2.5  | mA   |

| I <sub>(LP-CQ-DO)</sub>            | CQ と DO の両方がイネーブルのときの静止電源電流。外部から供給される V5IN              | R <sub>SETx</sub> ≥ 10kΩ。TX1= TX2 = H、CQ または DO で無負荷、プッシュブルまたは NPN モードのみ                                                                     |                                                         | 4.5 | 5.5  | mA   |

| I <sub>(LP-CQ-DO)</sub>            |                                                         | R <sub>SETx</sub> ≥ 10kΩ。TX1= TX2 = L、CQ または DO で無負荷                                                                                         |                                                         | 3.6 | 4.5  | mA   |

| V <sub>(LP-UVLO)</sub>             | LP 低電圧ロックアウト                                            | LP 立ち下がり:RESET ピンが Low になると UVLO を示します                                                                                                       | 6                                                       | 6.3 |      | V    |

| V <sub>(LP-UVLO)</sub>             | LP 低電圧ロックアウト                                            | LP 立ち上がり:RESET ピンが High になると UVLO 回復を通知します                                                                                                   |                                                         | 6.5 | 6.8  | V    |

| V <sub>(LP-UVLO,HYS)</sub>         | LP 低電圧ヒステリシス                                            | 立ち上がりから立ち下がりへのスレッショルド                                                                                                                        | 150                                                     | 250 |      | mV   |

| V <sub>(LPW)</sub>                 | LP 低電圧警告                                                | LP 立ち下がり                                                                                                                                     | 14                                                      | 16  | 18   | V    |

| V <sub>(LPW-HYS)</sub>             | LP 低電圧警告ヒステリシス                                          |                                                                                                                                              |                                                         | 530 |      | mV   |

| <b>V5IN</b>                        |                                                         |                                                                                                                                              |                                                         |     |      |      |

| V5IN (UVLO, F)                     | V5IN の立ち下がり UVLO レベル                                    | V5IN の立ち下がり                                                                                                                                  | 3.4                                                     | 3.5 | 3.6  | V    |

| V5IN (UVLO, R)                     | V5IN の立ち上がり UVLO レベル                                    | V5IN の立ち上がり                                                                                                                                  | 3.7                                                     | 3.8 | 4.0  | V    |

| V5IN (UVLO, HYS)                   | V5IN UVLO ヒステリシス                                        |                                                                                                                                              |                                                         | 0.3 |      | V    |

| I <sub>5_IN</sub>                  | 5VIN での入力電源電流                                           | CQ および DO ディスエーブル、VOUT で無負荷                                                                                                                  | 0.15                                                    | 1   |      | mA   |

| <b>リニアレギュレータ (VOUT)</b>            |                                                         |                                                                                                                                              |                                                         |     |      |      |

| V <sub>(VOUT)</sub>                | 電圧レギュレータ出力                                              | VOUT を 5V に設定                                                                                                                                | 4.75                                                    | 5   | 5.25 | V    |

|                                    |                                                         | VOUT を 3.3V に設定                                                                                                                              | 3.13                                                    | 3.3 | 3.46 | V    |

| LINEREG <sub>V<sub>UT</sub></sub>  | ラインレギュレーション (dV <sub>(VOUT)</sub> /dV <sub>(LP)</sub> ) | I <sub>(VCC_OUT)</sub> = 1mA<br>V <sub>(LP)</sub> = 7V ~ 36V (VOUT = 5V)<br>V <sub>(LP)</sub> = 7V ~ 36V または V5IN = 4.5 ~ 5.5V (VOUT = 3.3V) |                                                         |     | 1.7  | mV/V |

| LOADREG <sub>V<sub>OUT</sub></sub> | ロードレギュレーション (dV <sub>(VOUT)</sub> /V <sub>(OUT)</sub> ) | VOUT = 5V の場合、V <sub>(LP)</sub> = 24V<br>VOUT = 3.3V の場合、V <sub>(LP)</sub> = 24V または V5IN = 5V<br>I <sub>(VCC_OUT)</sub> = 100µA ~ 20mA      |                                                         |     | 1    | %    |

推奨動作条件および推奨自由空気温度範囲を超える場合(特に記述のない限り)。LP = 24V、V<sub>VOUT</sub> = 3.3V、T<sub>A</sub> = 25°C の場合の標準的な値(特に記述のない限り)。

| パラメータ                  |                                                          | テスト条件                                                                                | 最小値                         | 標準値                 | 最大値  | 単位  |

|------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------|---------------------|------|-----|

| UV <sub>VOUT5F</sub>   | VOUT の立ち下がり UV スレッショルド (5V 設定)                           | VSEL を VOUT に接続、VOUT 立ち下がり                                                           | 3.4                         | 3.6                 | 3.8  | V   |

| UV <sub>VOUT5R</sub>   | VOUT の立ち上がり UV スレッショルド (5V 設定)                           | VSEL を VOUT に接続、VOUT 立ち上がり                                                           | 3.6                         | 3.8                 | 4.0  | V   |

| UV <sub>VOUT3F</sub>   | VOUT の立ち下がり UV スレッショルド (3.3V 設定)                         | VSEL を GND またはフローティング (V5IN 電源) に接続、VOUT 立ち下がり                                       | 2.5                         | 2.7                 | 2.9  | V   |

| UV <sub>VOUT3R</sub>   | VOUT の立ち上がり UV スレッショルド (3.3V 設定)                         | VSEL を GND またはフローティング (V5IN 電源) に接続、VOUT 立ち上がり                                       | 2.6                         | 2.8                 | 3.0  | V   |

| PSSR                   | 電源除去比                                                    | 100kHz、I <sub>(VCC_OUT)</sub> = 20mA                                                 |                             | 40                  |      | dB  |

| <b>ドライバ出力 (CQ, DO)</b> |                                                          |                                                                                      |                             |                     |      |     |

| R <sub>DSON-HS</sub>   | ハイサイド ドライバ オン抵抗                                          | I <sub>LOAD</sub> = 200mA、電流制限 = 300mA                                               |                             |                     | 2.5  | 4.5 |

| R <sub>DSON-LS</sub>   | ローサイド ドライバ オン抵抗                                          | I <sub>LOAD</sub> = 200mA、電流制限 = 300mA                                               |                             |                     | 2.5  | 4.5 |

| I <sub>O(LIM)</sub>    | ドライバ出力電流制限                                               | SPI/PIN = LOW<br>V <sub>(DRIVER)</sub> = (V <sub>LP</sub> - 3)V または 3V、              | R <sub>SETx</sub> = 110kΩ   | 35                  | 55   | 70  |

|                        |                                                          |                                                                                      | R <sub>SETx</sub> = 10kΩ    | 300                 | 350  | 400 |

|                        |                                                          |                                                                                      | R <sub>SETx</sub> = 0 ~ 5kΩ | 500                 |      | mA  |

|                        |                                                          |                                                                                      | R <sub>SETx</sub> = OPEN    | 260                 | 330  | 415 |

| I <sub>O(LIM)</sub>    | ドライバ出力電流制限                                               | SPI/PIN = HIGH、<br>V <sub>(DRIVER)</sub> = (V <sub>LP</sub> - 3) V または 3V、           | 3h[7:6] = 0h                | 35                  | 60   | 75  |

|                        |                                                          |                                                                                      | 3h[7:6] = 1h                | 50                  | 75   | 95  |

|                        |                                                          |                                                                                      | 3h[7:6] = 2h                | 100                 | 140  | 175 |

|                        |                                                          |                                                                                      | 3h[7:6] = 3h                | 150                 | 190  | 260 |

|                        |                                                          |                                                                                      | 3h[7:6] = 4h                | 200                 | 230  | 330 |

|                        |                                                          |                                                                                      | 3h[7:6] = 5h                | 250                 | 290  | 410 |

|                        |                                                          |                                                                                      | 3h[7:6] = 6h                | 300                 | 350  | 485 |

|                        |                                                          |                                                                                      | 3h[7:6] = 7h                | 500                 | 700  | mA  |

| I <sub>OZ(CQ)</sub>    | CQ リーケージ                                                 | EN1 = LOW、0 ≤ V <sub>(CQ)</sub> ≤ (V <sub>LP</sub> - 0.1V)                           |                             | -2                  | 2    | μA  |

| I <sub>LLM(CQ)</sub>   | CQ 負荷放電電流                                                | EN1 = LOW、R <sub>SET1</sub> = 0 ~ 5kΩ <sup>(1)</sup> 、V <sub>(CQ)</sub> ≥ 5V         |                             | 5                   | 8.5  | 15  |

| I <sub>LLM(DO)</sub>   | DO 負荷放電電流                                                | EN2 = LOW、R <sub>SET2</sub> = 0 ~ 5 kΩ; V <sub>(DO)</sub> ≥ 5V                       |                             | 5                   | 8.5  | 15  |

| I <sub>PU-DO</sub>     | DO ドライバの弱プルアップ電流                                         | SPI/PIN = HIGH、EN2 = LOW、<br>TX2 = HIGH、RSET2: 10kΩ ~ 110kΩ、弱プルアップがイネーブル (SPI モードのみ) | 0 ≤ V(DO) ≤ (V(LP) - 2V)    | 40                  | 50   | 80  |

| I <sub>PD-DO</sub>     | DO ドライバの弱プルダウン電流                                         | SPI/PIN = HIGH、EN2 = LOW、<br>TX2 = LOW、RSET2: 10kΩ ~ 110kΩ、弱プルアップがイネーブル (SPI モードのみ)  | 2 ≤ V(DO) ≤ V(LP)           | 40                  | 50   | 80  |

| I <sub>PU-CQ</sub>     | CQ ドライバの弱プルアップ電流                                         | ドライバがディスエーブル、弱プルアップがイネーブル (SPI モード)                                                  | 0 ≤ V(CQ) ≤ (V(LP) - 2V)    | 40                  | 50   | 80  |

| I <sub>PD-CQ</sub>     | CQ ドライバの弱プルダウン電流                                         | ドライバがディスエーブル、弱プルダウンがイネーブル (SPI モード)                                                  | 2 ≤ V(CQ) ≤ V(LP)           | 40                  | 50   | 80  |

| <b>レシーバ入力 (CQ, DI)</b> |                                                          |                                                                                      |                             |                     |      |     |

| V <sub>(THH)</sub>     | 入力スレッショルド「H」                                             | V <sub>(LP)</sub> > 18V、EN = LOW                                                     |                             | 10.5                | 13   | V   |

| V <sub>(THL)</sub>     | 入力スレッショルド「L」                                             |                                                                                      |                             | 8                   | 11.5 | V   |

| V <sub>(HYS)</sub>     | レシーバヒステリシス<br>(V <sub>(THH)</sub> - V <sub>(THL)</sub> ) |                                                                                      |                             | 0.75                |      | V   |

| V <sub>(THH)</sub>     | 入力スレッショルド「H」                                             | V <sub>(LP)</sub> < 18V、EN = LOW                                                     | 注を参照 <sup>(2)</sup>         | 注を参照 <sup>(3)</sup> |      | V   |

推奨動作条件および推奨自由空気温度範囲を超える場合(特に記述のない限り)。LP = 24V、V<sub>VOUT</sub> = 3.3V、T<sub>A</sub> = 25°C の場合の標準的な値(特に記述のない限り)。

| パラメータ              |                                                          | テスト条件                                           |                          | 最小値                 | 標準値                 | 最大値  | 単位 |

|--------------------|----------------------------------------------------------|-------------------------------------------------|--------------------------|---------------------|---------------------|------|----|

| V <sub>(THL)</sub> | 入力スレッショルド「L」                                             | V <sub>(LP)</sub> < 18V、EN = LOW                |                          | 注を参照 <sup>(4)</sup> | 注を参照 <sup>(5)</sup> | 0.75 | V  |

| V <sub>(HYS)</sub> | レシーバヒステリシス<br>(V <sub>(THH)</sub> - V <sub>(THL)</sub> ) |                                                 |                          |                     |                     |      |    |

| C <sub>IN-CQ</sub> | CQ 入力容量                                                  | CQ ドライバがディスエーブル、弱プルアップ/プルダウンがディスエーブル、f = 100kHz |                          |                     | 150                 |      | pF |

| C <sub>IN-DI</sub> | DI 入力容量                                                  | f = 100kHz                                      |                          |                     | 100                 |      | pF |

| I <sub>PU-DI</sub> | DI 弱プルアップ電流                                              | SPI モード、DI ピンで弱プルアップがイネーブル                      | 0 ≤ V(DI) ≤ (V(LP) - 2V) | 40                  | 50                  | 80   | μA |

| I <sub>PD-DI</sub> | DI 弱プルダウン電流                                              | SPI モード、DI ピンで弱プルダウンがイネーブル                      | 2 ≤ V(DI) ≤ V(LP)        | 40                  | 50                  | 80   | μA |

#### ロジックレベル入力 (CS/PP, SCK, SDI/NPN, SPI/PIN, EN1, EN2, TX1, TX2, VSEL)

|                 |                                |  |  |          |    |

|-----------------|--------------------------------|--|--|----------|----|

| V <sub>IL</sub> | 入力ロジック Low 電圧                  |  |  | 0.3xVOUT | V  |

| V <sub>IH</sub> | 入力ロジック High 電圧                 |  |  | 0.7xVOUT | V  |

| R <sub>PD</sub> | EN1、EN2、SDI/NPN、SCK のプルダウン抵抗   |  |  | 100      | kΩ |

| R <sub>PU</sub> | TX1、TX2、CS/PP、SPI/PIN のプルアップ抵抗 |  |  | 100      | kΩ |

| R <sub>PU</sub> | VSEL へのプルアップ抵抗                 |  |  | 500      | kΩ |

#### ロジックレベル出力 (WU, SDO/NFLT2, INT/NFLT1, RX1, RX2, RESET)

|                 |                                             |                                                    |                      |          |      |

|-----------------|---------------------------------------------|----------------------------------------------------|----------------------|----------|------|

| V <sub>OH</sub> | 出力ロジック High 電圧 RX1、RX2、SDO、INT              | I <sub>O</sub> = 4mA                               | I <sub>O</sub> = 4mA | VOUT-0.5 | V    |

| V <sub>OL</sub> | 出力ロジック Low 電圧                               | I <sub>O</sub> = 4mA                               |                      | 0.4      | V    |

| I <sub>OZ</sub> | NFLT1、NFLT2、WU、RESET の出力<br>カハイインピーダンスリーケージ | ハイインピーダンスの出力、V <sub>O</sub> = 0V または<br>VCC_IN/OUT |                      | -1       | 1 μA |

#### 保護回路

|                    |                                        |                                                                                                                                                    |                     |     |    |

|--------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|----|

| T <sub>(WRN)</sub> | 過熱警告                                   |                                                                                                                                                    |                     | 125 | °C |

| T <sub>(SDN)</sub> | サーマル シャットダウン                           | ダイ温度 T <sub>J</sub>                                                                                                                                |                     | 150 | °C |

| T <sub>(HYS)</sub> | シャットダウンの熱ヒステリシス                        |                                                                                                                                                    |                     | 14  | °C |

| T <sub>(WRN)</sub> | 警告用の熱ヒステリシス                            | ダイ温度 T <sub>J</sub>                                                                                                                                | ダイ温度 T <sub>J</sub> | 14  | °C |

| I <sub>REV</sub>   | 逆極性での CQ、DO、DI リーク電流<br>(ドライバがディスエーブル) | EN1/2 = LOW、TX1/2 = x の場合、LP = 24V V <sub>(CQ/ DO/ DI)</sub> = (V <sub>(LP)</sub> - 36V) または V <sub>(CQ/ DO/ DI)</sub> = (V <sub>(LP)</sub> + 36V) |                     | 60  | μA |

|                    |                                        | EN1/2 = LOW、TX1/2 = x の場合、LP = 24V V <sub>(CQ/ DO/ DI)</sub> = (V <sub>(LP)</sub> - 65V) または V <sub>(CQ/ DO/ DI)</sub> = 65V                       |                     | 110 | μA |

|                    | CQ、DO (ドライバがイネーブル)                     | EN1/2 = HIGH、TX1/2 = LOW、V <sub>(CQ/DO ~ LP)</sub> = 3V、R <sub>SET</sub> ≥ 10kΩ                                                                    |                     | 650 | μA |

|                    |                                        | EN1/2 = HIGH、TX1/2 = HIGH、V <sub>(CQ/DO ~ LM)</sub> = -3V                                                                                          |                     | 10  | μA |

(1) 電流フォルト表示と電流フォルト自動回復は無効になります。

(2) V<sub>THH</sub> (min) = 5V + (11/18) [V<sub>(LP)</sub> - 8V]

(3) V<sub>THH</sub> (max) = 6.5V + (13/18) [V<sub>(LP)</sub> - 8V]

(4) V<sub>THL</sub> (min) = 4V + (8/18) [V<sub>(LP)</sub> - 8V]

(5) V<sub>THL</sub> (max) = 6V + (11/18) [V<sub>(LP)</sub> - 8V]

## 5.7 スイッチング特性

推奨動作条件および推奨自由空気温度範囲を超える場合(特に記述のない限り)。LP = 24V、V<sub>VOUT</sub> = 3.3V、T<sub>A</sub> = 25°C の場合の標準的な値(特に記述のない限り)。

| パラメータ                | テスト条件                                             | テスト条件                                                                                                                                                      | 最小値 | 標準値 | 最大値  | 単位 |

|----------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|----|

| <b>CQ、DO ドライバ</b>    |                                                   |                                                                                                                                                            |     |     |      |    |

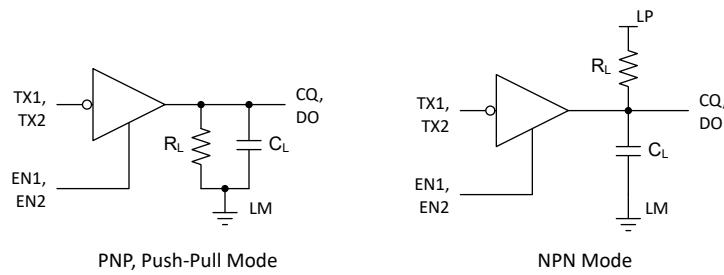

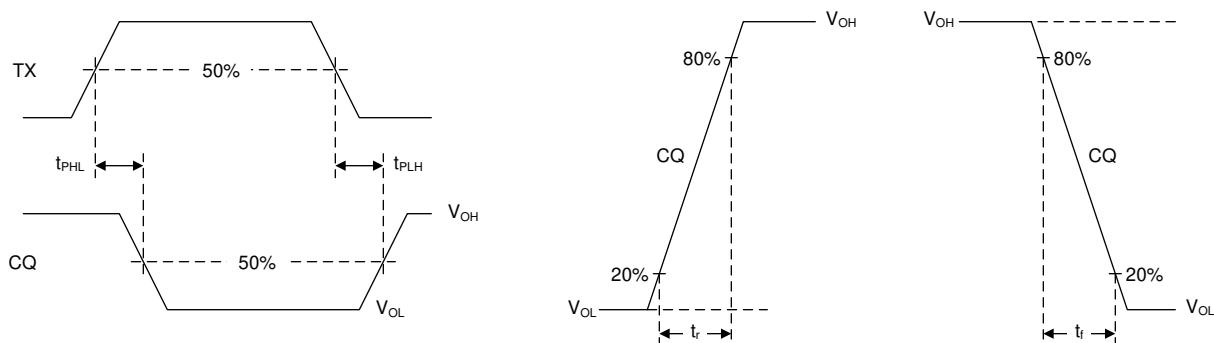

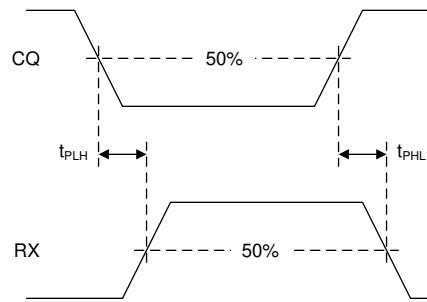

| t <sub>PLH</sub>     | ドライバ伝搬遅延、Low から High へ遷移                          | ドライバ出力測定のテスト回路<br>とドライバ出力スイッチング波形を参照してください<br>R <sub>L</sub> = 2kΩ<br>C <sub>L</sub> = 5nF<br>プッシュプルおよび PNP 構成<br>R <sub>SET</sub> = 10kΩ                  |     | 600 | 1200 | ns |

| t <sub>PHL</sub>     | ドライバ伝搬遅延、High から Low へ遷移                          | ドライバ出力測定のテスト回路<br>とドライバ出力スイッチング波形を参照してください<br>R <sub>L</sub> = 2kΩ<br>C <sub>L</sub> = 5nF<br>プッシュプルおよび NPN 構成<br>R <sub>SET</sub> = 10kΩ                  |     | 600 | 1200 | ns |

| t <sub>P(skew)</sub> | ドライバ伝搬遅延スキュー。 t <sub>PLH</sub> - t <sub>PHL</sub> | ドライバ出力測定のテスト回路を参照してください<br>ドライバ出力スイッチング波形を参照してください<br>R <sub>L</sub> = 2kΩ<br>C <sub>L</sub> = 5nF<br>プッシュプル構成<br>R <sub>SET</sub> = 10kΩ                  |     | 120 |      | ns |

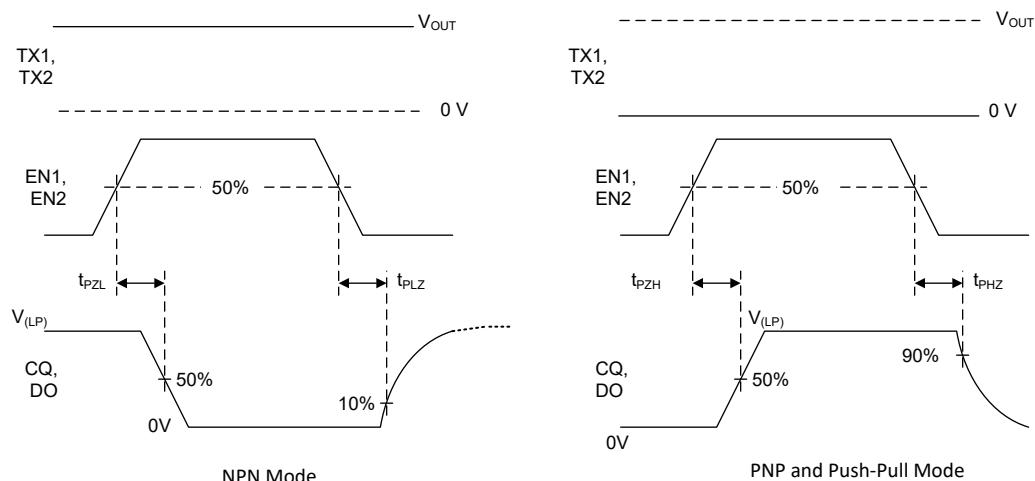

| t <sub>PZH</sub>     | ドライバイネーブル遅延 High                                  | ドライバ出力測定のテスト回路<br>と<br>ドライバのイネーブル/ディスエーブル タイミング図を参照してください<br>R <sub>L</sub> = 2kΩ<br>C <sub>L</sub> = 5nF<br>プッシュプルおよび PNP 構成のみ<br>R <sub>SET</sub> = 10kΩ |     |     | 4    | μs |

| t <sub>PZL</sub>     | ドライバイネーブル遅延 Low                                   | ドライバ出力測定のテスト回路<br>と<br>ドライバのイネーブル/ディスエーブル タイミング図を参照してください<br>R <sub>L</sub> = 2kΩ<br>C <sub>L</sub> = 5nF<br>プッシュプルおよび NPN 構成のみ<br>R <sub>SET</sub> = 10kΩ |     |     | 4    | μs |

| t <sub>PHZ</sub>     | ドライバディスエーブル遅延 High                                | ドライバ出力測定のテスト回路<br>と<br>ドライバのイネーブル/ディスエーブル タイミング図を参照してください<br>R <sub>L</sub> = 2kΩ<br>C <sub>L</sub> = 5nF<br>プッシュプルおよび PNP 構成のみ<br>R <sub>SET</sub> = 10kΩ |     |     | 4    | μs |

| t <sub>PLZ</sub>     | ドライバディスエーブル遅延 Low                                 | ドライバ出力測定のテスト回路<br>と<br>ドライバのイネーブル/ディスエーブル タイミング図を参照してください<br>R <sub>L</sub> = 2kΩ<br>C <sub>L</sub> = 5nF<br>プッシュプルおよび NPN 構成のみ<br>R <sub>SET</sub> = 10kΩ |     |     | 4    | μs |

| t <sub>r</sub>       | ドライバ出力立ち上がり時間                                     | ドライバ出力測定のテスト回路<br>とドライバ出力スイッチング波形を参照してください<br>R <sub>L</sub> = 2kΩ<br>C <sub>L</sub> = 5nF<br>プッシュプルおよび PNP 構成<br>R <sub>SET</sub> = 10kΩ                  | 200 | 530 | 900  | ns |

| t <sub>f</sub>       | ドライバ出力立ち下がり時間                                     | ドライバ出力測定のテスト回路<br>とドライバ出力スイッチング波形を参照してください<br>R <sub>L</sub> = 2kΩ<br>C <sub>L</sub> = 5nF<br>プッシュプルおよび NPN 構成<br>R <sub>SET</sub> = 10kΩ                  | 200 | 480 | 900  | ns |

推奨動作条件および推奨自由空気温度範囲を超える場合(特に記述のない限り)。LP = 24V、V<sub>VOUT</sub> = 3.3V、T<sub>A</sub> = 25°C の場合の標準的な値(特に記述のない限り)。

| パラメータ                                        |                                              | テスト条件                                                                                                                            | テスト条件                                                                                                                            | テスト条件 | 最小値  | 標準値  | 最大値 | 単位 |  |

|----------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-----|----|--|

| t <sub>r</sub> - t <sub>f</sub>              | 立ち上がりおよび立ち下がり時間の差                            | ドライバ出力測定のテスト回路とドライバ出力スイッチング波形を参照してください<br>R <sub>L</sub> = 2kΩ<br>C <sub>L</sub> = 5nF<br>ブッシュホール構成のみ<br>R <sub>SET</sub> = 10kΩ |                                                                                                                                  |       |      | 60   | ns  |    |  |

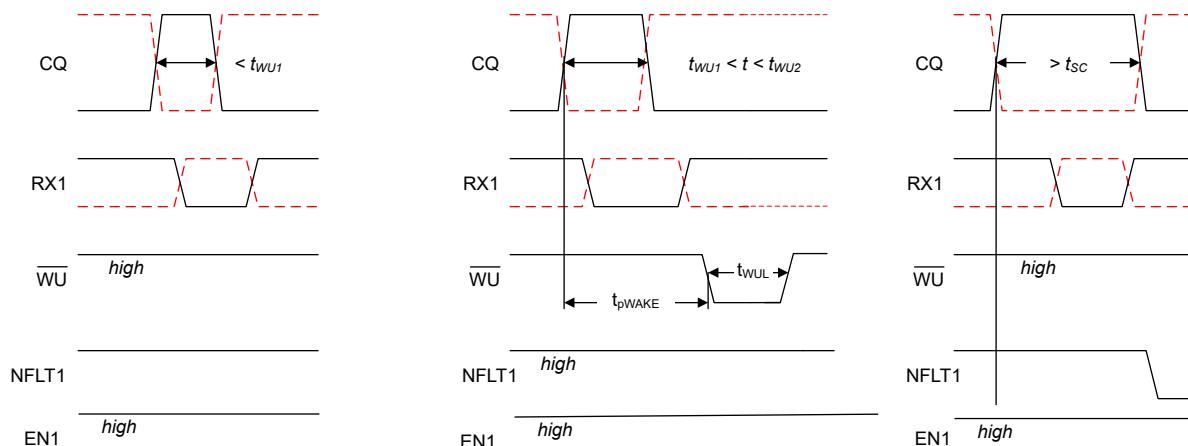

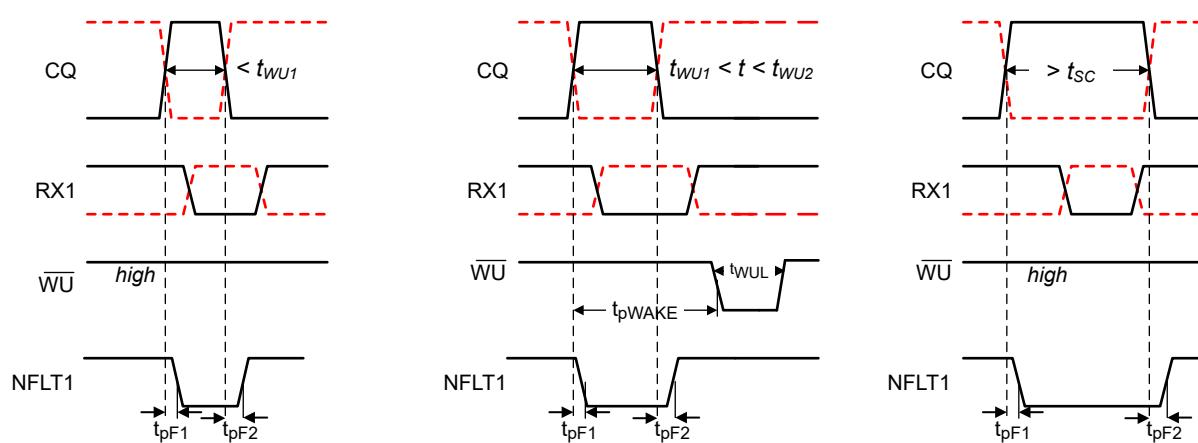

| t <sub>WU1</sub>                             | ウェークアップ認識開始                                  | ウェークアップ認識のタイミング図を参照してください                                                                                                        |                                                                                                                                  |       | 45   | 60   | 75  | μs |  |

| t <sub>WU2</sub>                             | ウェークアップ認識終了                                  |                                                                                                                                  |                                                                                                                                  |       | 85   | 100  | 145 | μs |  |

| t <sub>pWAKE</sub>                           | ウェークアップ出力遅延                                  |                                                                                                                                  |                                                                                                                                  |       | 150  |      | μs  |    |  |

| t <sub>WUL</sub>                             | ウェーク検出時のウェークア出力パルス持続時間                       |                                                                                                                                  |                                                                                                                                  |       | 175  | 225  | 285 | μs |  |

| t <sub>SC</sub>                              | 電流フォルト ブランкиング時間                             | ウェークアップ認識のタイミング図を参照してください                                                                                                        | (SPI/PIN = lowかつ10kΩ ≤ R <sub>SET</sub> x ≤ 110kΩ)または SPI/PIN = highかつ CQ_BL_TIME[1:0] = 00b (CQ) または DO_BL_TIME[1:0] = 00b (DO) | 0.175 |      | 0.2  |     | ms |  |

|                                              |                                              |                                                                                                                                  | SPI/PIN = Highかつ CQ_BL_TIME[1:0] = 01b (CQ) または DO_BL_TIME[1:0] = 01b (DO)                                                       | 0.25  |      | 0.5  |     | ms |  |

|                                              |                                              |                                                                                                                                  | SPI/PIN = Highかつ CQ_BL_TIME[1:0] = 10b (CQ) または DO_BL_TIME[1:0] = 10b (DO)                                                       | 5     |      | ms   |     | ms |  |

|                                              |                                              |                                                                                                                                  | (SPI/PIN = LowかつILIM_ADJ フローティング)または SPI/PIN = Highかつ CQ_BL_TIME[1:0] = 11b (CQ) または DO_BL_TIME[1:0] = 11b (DO)                  | 0.5   | 2    | 4    | μs  |    |  |

| t <sub>AR</sub>                              | 電流フォルト後の自動再試行時間                              | 電流フォルト後の自動再試行時間                                                                                                                  | SPI/PIN = L または SPI/PIN = H かつ CQ_RETRY_TIME = 00b                                                                               | 50    |      | ms   |     |    |  |

|                                              |                                              |                                                                                                                                  | SPI/PIN = H かつ CQ_RETRY_TIME = 01b                                                                                               | 100   |      | ms   |     |    |  |

|                                              |                                              |                                                                                                                                  | SPI/PIN = H かつ CQ_RETRY_TIME = 10b                                                                                               | 200   |      | ms   |     |    |  |

|                                              |                                              |                                                                                                                                  | SPI/PIN = H かつ CQ_RETRY_TIME = 11b                                                                                               | 500   |      | ms   |     |    |  |

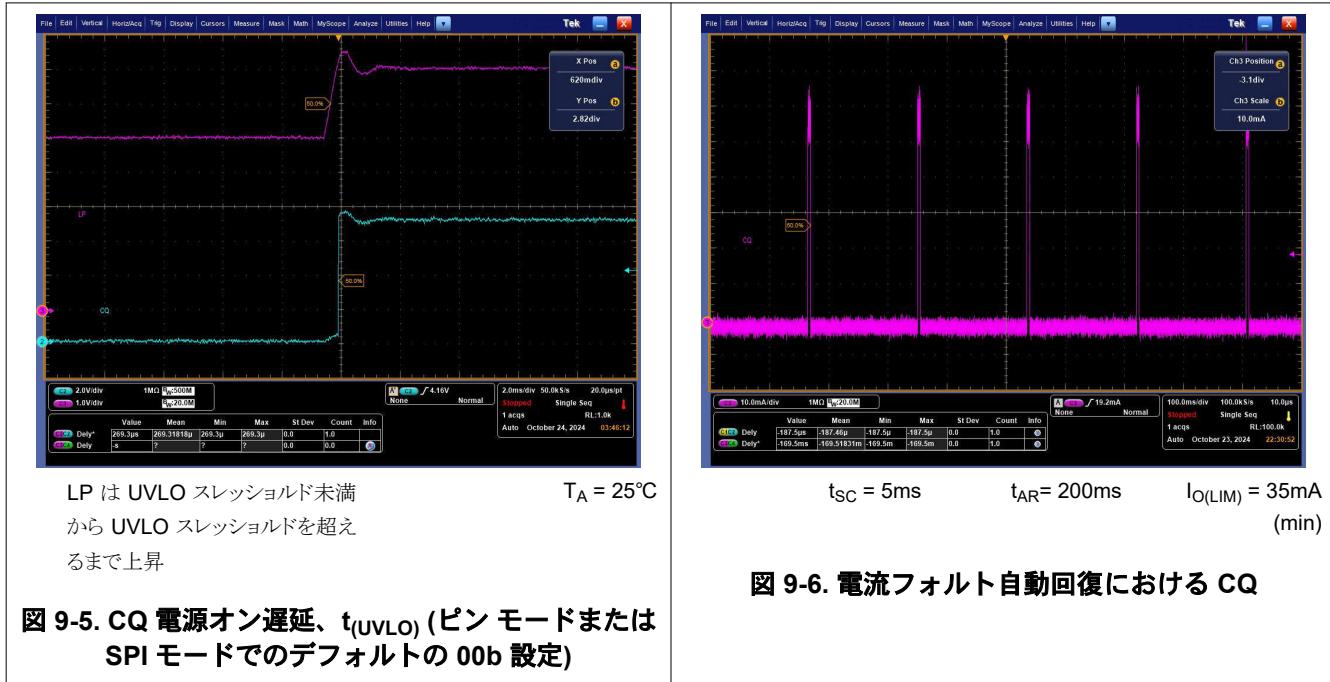

| t <sub>(UVLO)</sub>                          | LP UVLO 後の CQ および DO 再イネーブル遅延 <sup>(1)</sup> | UVLO 後の CQ および DO 再イネーブル遅延 <sup>(1)</sup>                                                                                        | SPI/PIN = L または SPI/PIN = H かつ T_UVLO = 1b0                                                                                      | 0.05  | 0.25 | 0.5  | ms  |    |  |

| t <sub>(UVLO)</sub>                          | LP UVLO 後の CQ および DO 再イネーブル遅延 <sup>(1)</sup> | UVLO 後の CQ および DO 再イネーブル遅延 <sup>(1)</sup>                                                                                        | SPI/PIN=H および T_UVLO=1b1                                                                                                         | 10    | 30   | 50   | ms  |    |  |

| <b>CQ、DI レシーバ</b>                            |                                              |                                                                                                                                  |                                                                                                                                  |       |      |      |     |    |  |

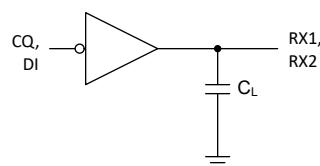

| t <sub>PLH_CQ</sub> 、<br>t <sub>PHL_CQ</sub> | CQ レシーバの伝搬遅延                                 | レシーバのテスト回路図およびレシーバのタイミング図を参照、C <sub>L</sub> = 15pF、                                                                              | SPI/PIN = L または SPI/PIN = H かつ CQ_RX_FILTER = 1b0                                                                                | 0.2   |      | 0.36 | μs  |    |  |

|                                              |                                              |                                                                                                                                  | SPI/PIN = H かつ CQ_RX_FILTER = 1b1                                                                                                | 1.15  |      | 1.6  | μs  |    |  |

| t <sub>PLH_DI</sub> 、<br>t <sub>PHL_DI</sub> | DI レシーバの伝搬遅延                                 |                                                                                                                                  | SPI/PIN = L または SPI/PIN = H かつ DI_RX_FILTER = 1b0                                                                                | 1     |      | 1.5  | μs  |    |  |

|                                              |                                              |                                                                                                                                  | SPI/PIN = H かつ DI_RX_FILTER = 1b1                                                                                                | 1.8   |      | 2.7  | μs  |    |  |

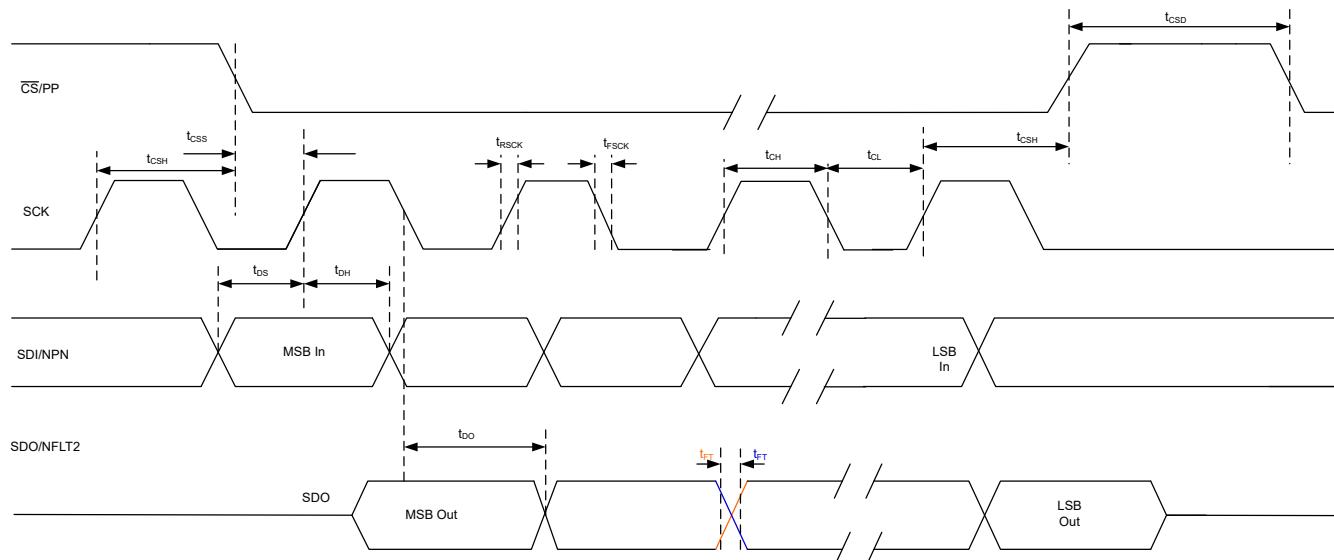

| <b>SPI タイミング (CS、SCK、SDI、SDO/CUR_OK2)</b>    |                                              |                                                                                                                                  |                                                                                                                                  |       |      |      |     |    |  |

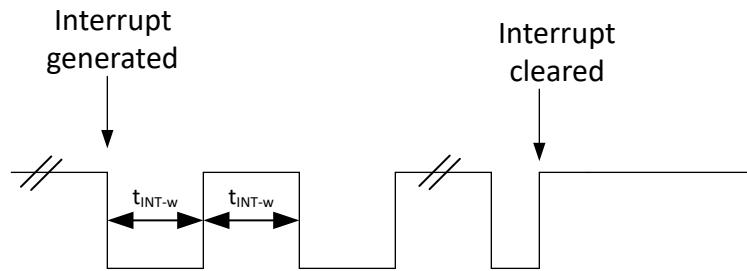

| t <sub>INT_TOG</sub>                         | INT ピンの High/Low 時間(トグル時)                    | C <sub>OUT</sub> = 10pF                                                                                                          |                                                                                                                                  |       | 100  |      | μs  |    |  |

推奨動作条件および推奨自由空気温度範囲を超える場合(特に記述のない限り)。LP = 24V、V<sub>VOUT</sub> = 3.3V、T<sub>A</sub> = 25°C の場合の標準的な値(特に記述のない限り)。

| パラメータ                  | テスト条件                                                     | テスト条件                   | テスト条件 | 最小値 | 標準値 | 最大値  | 単位  |

|------------------------|-----------------------------------------------------------|-------------------------|-------|-----|-----|------|-----|

| f <sub>SCK_BURST</sub> | 最大 SPI クロック周波数<br>SCK 周期<br>SCK パルス幅 High<br>SCK パルス幅 Low | バーストモード<br>非バーストモード     |       |     |     | 10   | MHz |

| t <sub>SCK</sub>       |                                                           |                         |       |     |     | 100  | ns  |

| t <sub>SCKH</sub>      |                                                           |                         |       |     |     | 50   | ns  |

| t <sub>SCKL</sub>      |                                                           |                         |       |     |     | 50   | ns  |

| f <sub>SCK</sub>       | 最大 SPI クロック周波数<br>SCK 周期<br>SCK パルス幅 High<br>SCK パルス幅 Low | 非バーストモード                |       |     |     | 12.5 | MHz |

| t <sub>SCK</sub>       |                                                           |                         |       |     |     | 80   | ns  |

| t <sub>SCKH</sub>      |                                                           |                         |       |     |     | 40   | ns  |

| t <sub>SCKL</sub>      |                                                           |                         |       |     |     | 40   | ns  |

| t <sub>CS</sub>        | CS 立ち下がりエッジから SCK 立ち上がりまでの時間                              |                         |       |     | 20  |      | ns  |

| t <sub>CSH</sub>       | SCK 立ち上がりから CS 立ち上がりまでのホールド時間                             |                         |       |     | 40  |      | ns  |

| t <sub>DH</sub>        | SDI のホールド時間                                               |                         |       |     | 10  |      | ns  |

| t <sub>DS</sub>        | SDI のセットアップ時間                                             |                         |       |     |     | 25   | ns  |

| t <sub>DO</sub>        | SDO データの伝搬遅延                                              | C <sub>OUT</sub> = 10pF |       |     |     | 20   | ns  |

| t <sub>DORF</sub>      | SDO 立ち上がりおよび立ち下がり時間                                       | C <sub>OUT</sub> = 10pF |       |     |     | 20   | ns  |

| t <sub>CSPW</sub>      | 最小 CS パルス幅 (SPI トランザクション間のアイドル時間)                         |                         |       |     | 10  |      | ns  |

(1) この時間において CQ/DO 出力はハイインピーダンスのままです

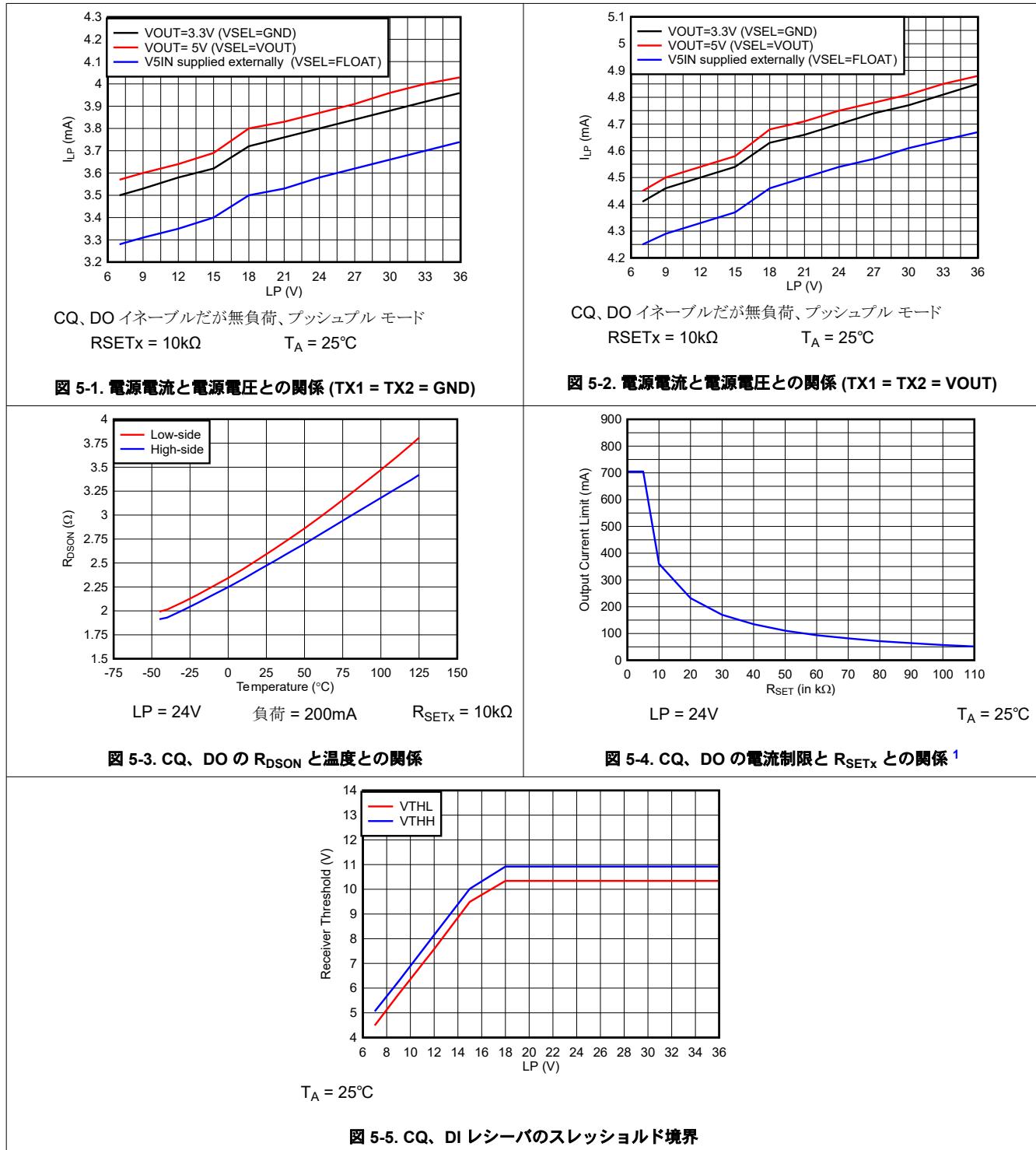

## 5.8 代表的特性

<sup>1</sup>  $R_{SET}$  が 0 ~ 5kΩ 範囲の場合、TIOL221 は IO-Link アプリケーションでのウェークアップ パルスの生成に必要な 500mA をソース / シンクできます。また、 $R_{SET}$  が 0 ~ 5kΩ 範囲の場合、ドライバが無効化されると、TIOL221 はプルダウン電流ソース ( $I_{LLM}$ ) を有効にします。

## 6 パラメータ測定情報

図 6-1. ドライバスイッチングのテスト回路

図 6-2. ドライバ出力のスイッチング測定時の波形

図 6-3. ドライバのイネーブルまたはディスエーブル時間測定の波形

図 6-4. レシーバスイッチングのテスト回路

図 6-5. レシーバのスイッチング測定

図 6-6. EN = H および ILIM\_ADJ = 10kΩ ~ 110kΩ、

TX = H (フル ライン)、TX = L (赤色の点線) の過電流およびウェーク条件図 6-7. EN = H および ILIM\_ADJ = フローティング、TX = H (フル ライン)、TX = L (赤色の点線) の過電流およ

びウェーク条件

図 6-8. SPI 読み取り/書き込みタイミング特性

図 6-9. 誘導性負荷の駆動

図 6-10. 容量性負荷の駆動

図 6-11. 割り込みピンのトグル動作 (SPI モード、`INT_TOG = 1b`)

## 7 詳細説明

### 7.1 概要

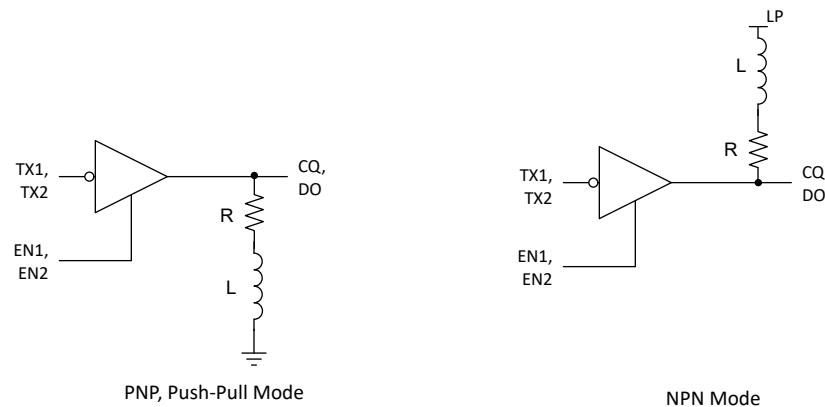

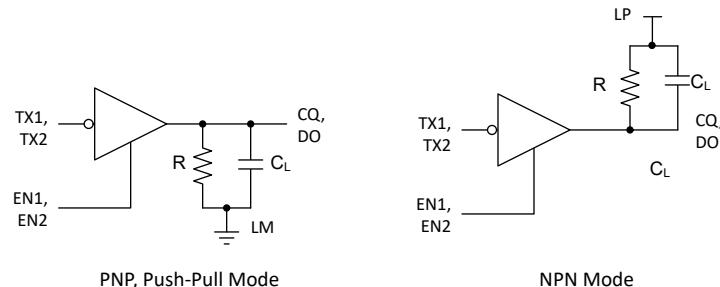

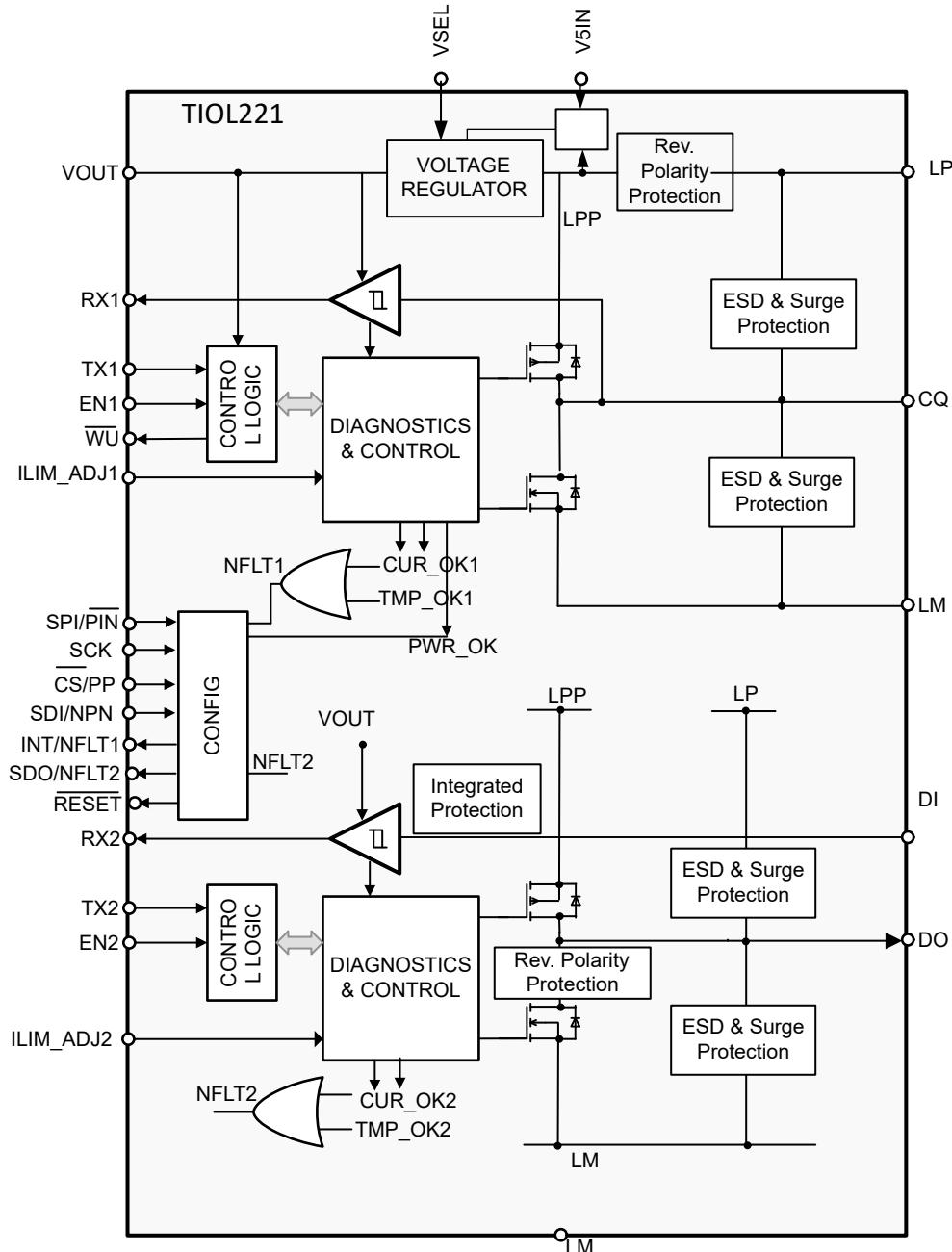

図 7-1 は TIOL221 の機能ブロック図を示しています。このデバイスには、IO-Link 互換のチャネル (CQ)、デジタル出力 ドライバ (DO)、デジタル入力 (DI) インターフェイスがあります。CQ および DO のドライバは、プッシュプル、ハイサイドドライバ (PNP)、またはローサイドドライバ (NPN) 構成のいずれかに、ピンモードの  $\overline{CS}/\overline{PP}$  ピンと SDI/NPN ピンを使用するか、シリアル ペリフェラル インターフェイス (SPI) 経由で使用できます。CQ ラインの内部レシーバは、24V 信号をレシーバ データ出力ピン RX1 の標準ロジック レベルに変換します。同様に、DI ラインの内部レシーバは、24V 信号をレシーバデータ出力ピン RX2 の標準ロジックレベルに変換します。シンプルなパラレル インターフェイスを使用して、デバイスとローカル コントローラとの間でデータやステータス情報を送受信します。

このデバイスは、ピンモード経由のピン (SPI/ $\overline{PIN}$  が Low に接続されている場合) または SPI を使用する (SPI/ $\overline{PIN}$  が High に接続されている場合) ことで構成できます。SPI インターフェイスを使用することで、マイコンは追加の診断およびステータス情報の読み取りや、デバイスの構成を行うことができます。

このデバイスには IEC 61000-4-4/5 EFT およびサージ保護機能が内蔵されています。さらに、 $\pm 70V$  の過渡電圧に耐えられるため、アプリケーションでより高いレベルの保護が必要な場合には、より広い範囲の TVS ダイオードを選択できます。これらの内蔵堅牢性機能により、外付け保護回路を低減することで、システム レベルの設計を簡素化できます。

TIOL221 トランシーバは、過電流、過電圧、過熱状態に対する保護機能を実装しています。また、このデバイスは、外付けの抵抗を使用してドライバの出力電流の電流制限設定も提供します。

このデバイスは、内部のリニア レギュレータを介して IO-Link LP 電圧 (公称 24V) から低電圧電源を生成し、ローカル コントローラおよびセンサ回路に電力を供給します。

## 7.2 機能ブロック図

図 7-1. ブロック図

## 7.3 機能説明

### 7.3.1 ウェークアップ検出

TIOL221 の CQ チャネルは、IO-Link モードまたは標準入出力 (SIO) モードで動作できます。CQ チャネルが SIO モードで、IO-link コントローラ ノードがデバイス ノードとの通信を開始する場合、コントローラは CQ ラインを現在の状態とは反対の状態に駆動します。このデバイスは、IO-Link 仕様に準拠した CQ ロジック レベルに応じて、ウェークアップ期間 (通常は 80μs) にわたって電流 ( $\geq 500\text{mA}$ ) をシンクまたはソースします。TIOL221 は、ウェークアップ条件を検出し、 $t_{WUL}$

の間  $\overline{WU}$  ピンを Low にアサートすることで、ローカルマイコンと通信します。IO-Link 通信仕様では、デバイスノードがウェークアップ信号を受信した後、500 $\mu$ s 内で受信モードに切り替えることが要求されます。

**表 7-1. ウェークアップ機能 ( $t_{WU1} < t < t_{WU2}$ )**

| EN1       | TX1       | CQ 電流                                   | WAKE                      | 備考                                                                                                     |

|-----------|-----------|-----------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------|

| L またはオープン | X         | X                                       | $t_{WUL}$ の間 Low にアサートします | RX 出力が $t_{WU1} < t < t_{WU2}$ の間 High から Low、または Low から High に変化した場合、デバイスは $t_{WUL}$ の間 Low にアサートされます |

| H         | H またはオープン | $ I_{(CQ)}  \geq I_{O(LIM)} \text{ mA}$ | $t_{WUL}$ の間 Low にアサートします | デバイスは、IO-Link バスを介して高レベルのウェークアップ要求を受信します                                                               |

| H         | L         | $ I_{(CQ)}  \geq I_{O(LIM)} \text{ mA}$ | $t_{WUL}$ の間 Low にアサートします | デバイスは、IO-Link バスを介して低レベルのウェークアップ要求を受信します                                                               |

有効なウェークアップパルスよりも短いまたは長い過電流状態の場合、WAKE ピンはハイインピーダンス（非アクティブ）状態に維持されます。[図 6-6](#) に、これを示します。

SPI モードでは、 $\overline{WU}$  が Low にアサートされていることに加えて、[WU\\_INT](#) ビットが設定されます。[DEVICE\\_CONFIG](#) レジスタで [WU\\_DIS](#) ビットを 1b に設定することで、SPI モードでウェークアップ信号を無効化できます。ピンモードでは、ウェークアップ検出を無効化することはできません。

TIOL221 の DO チャネルは、ウェークアップパルスを認識しません。DO ピンは過電流制限と検出を行います。

### 7.3.2 電流制限構成

CQ および DO ピンの出力電流を、ピンモードおよび SPI モードで独立して構成できます。

#### 7.3.2.1 ピンモードでの電流制限構成

ピンモードでは、CQ および DO の電流制限は、それぞれ [ILIM\\_ADJ1](#) ピンおよび [ILIM\\_ADJ2](#) ピンの外付け抵抗で構成できます。10k $\Omega$  の外付け抵抗による最大の電流制限設定により、動作温度および電圧範囲全体にわたって最小値 300mA が得られます。CQ および DO ドライバのピンモード構成については、[表 7-2](#) を参照してください。

電流フォルトによる出力ディスエーブルおよび電流フォルト自動回復機能は、[ILIM\\_ADJ1/2](#) ピンをフローティングにすることで無効化できます。ただし、この構成では、電流フォルト通知はアクティブのままであります。この機能は、大きな静電容量を駆動するときに役立ちます。

[ILIM\\_ADJ1/2](#) ピンがグランドに短絡したとき、CQ および DO ドライバは IO-link コントローラモードになるように構成できます。このモードでは、ドライバは最小 500mA をソースまたはシンクして、ウェークアップ要求を生成できます。また、ドライバは、ドライバ出力ピンの 5mA の小さな電流シンク（最小値）を有効にします。このモードでは、電流フォルト表示、出力ディスエーブル、自動回復機能は無効化されます。

**表 7-2. ピンモードでの電流制限構成**

| <a href="#">ILIM_ADJ1/2</a> ピン状態                            | CQ/DO 電流制限（最小値）   | 電流による NFLT1/2 表示 フォルト | 電流フォルト ブランギング時間 (t <sub>sc</sub> ) | 出力ディスエーブルと自動回復 |

|-------------------------------------------------------------|-------------------|-----------------------|------------------------------------|----------------|

| R <sub>SET</sub> 抵抗を L- に接続 (10k $\Omega$ ~ 110k $\Omega$ ) | 変数 (35mA ~ 300mA) | あり                    | 200 $\mu$ s (標準値)                  | あり             |

| L- に接続 (R <sub>SET</sub> 0 ~ 5k $\Omega$ )                  | 500mA             | なし                    | 該当なし                               | なし             |

| オープン                                                        | 260mA             | あり                    | なし（即時フォルト表示）                       | なし             |

#### 7.3.2.2 SPI モードでの電流制限構成

SPI モードにおいて、CQ および DO ドライバの電流制限を SPI を介して設定できます。CQ ドライバは [CQ\\_CURLIM](#) レジスタを使用して設定できます。[CQ\\_CURLIM\[7:5\]](#) レジスタを使用して電流制限を設定できます。

同様に、[DO\\_CURLIM\[7:5\]](#) レジスタを使用して DO ドライバの電流制限を設定できます。

### 7.3.3 CQ 電流フォルト検出、表示、自動回復

CQ の出力電流が、内部で設定された電流制限  $I_{O(LIM)}$  を、電流プランギング時間  $t_{SC}$  より長い時間上回ると、デバイスは過電流フォルトとして検出します。

ピンモードでは、フォルト状態を示すため、INT/NFLT1 ピンがロジック Low に駆動されます。出力を、ターンオフ (自動回復モード) に設定するか、デバイスがサーマル シャットダウンに移行するまで電流供給を継続することができます。動作は、ILIM\_ADJ1 ピンの接続方法によって異なります。[表 7-2](#) を参照してください。自動回復モードでは、ドライバが定期的に再試行することで、出力がまだ過電流状態にあるかどうかを確認します。このモードでは、出力は  $t_{SC}$  の間  $t_{AR}$  間隔でオンになります。ILIM\_ADJ1 = OPEN または GND を設定することで、電流フォルト自動再試行モードを無効化できます。ILIM\_ADJ1 = OPEN のとき、電流フォルト ブランギング時間はゼロになります。詳細については、電流制限インジケータ機能 ( $t > t_{SC}$ ) を参照してください。

SPI モードでは、CQ\_CURLIM レジスタ設定を使用して CQ ドライバの動作を設定できます。[CQ\\_CUR\\_LIM](#) ビットは電流制限値を設定し、[CQ\\_BL\\_TIME](#) および [CQ\\_RETRY\\_TIME](#) はそれぞれ現在のフォルト ブランギング時間と自動回復時間を設定します。[CQ\\_AUTO\\_RETRY\\_EN](#) は自動回復動作を制御します。

ドライバが無効の場合、電流制限インジケータは非アクティブになります。

### 7.3.4 DO 電流フォルト検出、表示、自動回復

DO の出力電流が、内部で設定された電流制限  $I_{O(LIM)}$  を、電流プランギング時間  $t_{SC}$  より長い時間上回ると、デバイスは過電流フォルトとして検出します。

ピンモードでは、SDO/NFLT2 ピンはフォルト状態を示すためにロジック Low に駆動されます。出力を、ターンオフ (自動回復モード) に設定するか、デバイスがサーマル シャットダウンに移行するまで電流供給を継続することができます。この動作は、ILIM\_ADJ2 ピンの接続方法によって異なります。自動回復モードで[表 7-2](#) を参照して、ドライバが定期的に再試行することで、出力がまだ過電流状態にあるかどうかを確認します。このモードでは、出力は  $t_{SC}$  の間  $t_{AR}$  間隔でオンになります。ILIM\_ADJ2 = OPEN または GND を設定することで、電流フォルト自動再試行モードを無効化できます。ILIM\_ADJ2 = OPEN のとき、電流フォルト ブランギング時間はゼロになります。

SPI モードでは、DO\_CURLIM レジスタ設定を使用して DO ドライバの動作を設定できます。[DO\\_CUR\\_LIM](#) ビットは電流制限値を設定し、[DO\\_BL\\_TIME](#) および [DO\\_RETRY\\_TIME](#) はそれぞれ現在のフォルト ブランギング時間と自動回復時間を設定します。[DO\\_RETRY\\_EN](#) は自動回復動作を制御します。

ドライバが無効の場合、電流制限インジケータは非アクティブになります。

### 7.3.5 CQ および DI レシーバ

RX1 は CQ レシーバの出力です。レシーバ出力は CQ 入力の逆ロジックであり、レシーバ機能を表 7-3 にまとめます。ピンモードでは、CQ レシーバは常にオンです。SPI モードでは、RX1 出力に加えて、STATUS レジスタの CQ\_RX\_LEVEL ビットは CQ バス入力レベルのロジックレベルを反映します。SPI モードでは、CQ\_CONFIG レジスタの RX\_DIS ビットを設定することでレシーバを無効化できます。レシーバがディスエーブルのとき、RX1 出力はハイインピーダンスになり、ステータス レジスタの CQ\_RX\_LEVEL ビットは無効です。

**表 7-3. CQ レシーバ機能**

| SPI/PIN                    | CQ 電圧                              | RX1 | CQ_RX_LEVEL ビット | 備考                           |

|----------------------------|------------------------------------|-----|-----------------|------------------------------|

| L または<br>(H && RX_DIS = 0) | $V_{(CQ)} < V_{(THL)}$             | H   | L               | 通常受信モード、入力 Low               |

|                            | $V_{(THL)} < V_{(CQ)} < V_{(THH)}$ | ?   | ?               | 不定の出力は High と Low のいずれかが可能です |

|                            | $V_{(THH)} < V_{(CQ)}$             | L   | H               | 通常受信モード、入力 High              |

|                            | オープン                               | ?   | ?               | 不定の出力は High と Low のいずれかが可能です |

| H && RX_DIS = 1            | X                                  | Z   | Z               | 出力はハイインピーダンスになります            |

RX2 は DI レシーバの出力です。レシーバ出力は DI 入力の逆ロジックであり、レシーバ機能を表 7-3 にまとめます。ピンモードでは、DI レシーバは常にオンです。SPI モードでは、RX2 出力に加えて、STATUS レジスタの DI\_LEVEL ビットは DI 入力のロジックレベルを反映します。SPI モードでは、DI\_CONFIG レジスタの DI\_DIS ビットを設定することでレシーバを無効化できます。レシーバがディスエーブルのとき、RX2 出力はハイインピーダンスになり、ステータス レジスタの DI\_LEVEL ビットは無効です。

**表 7-4. DI レシーバ機能**

| DI<br>電圧                           | RX2 | DI_LEVEL ビット | 備考                           |

|------------------------------------|-----|--------------|------------------------------|

| $V_{(DI)} < V_{(THL)}$             | H   | L            | 通常受信モード、入力 Low               |

| $V_{(THL)} < V_{(DI)} < V_{(THH)}$ | ?   | ?            | 不定の出力は High と Low のいずれかが可能です |

| $V_{(THH)} < V_{(DI)}$             | L   | H            | 通常受信モード、入力 High              |

| オープン                               | ?   | ?            | 不定の出力は High と Low のいずれかが可能です |

### 7.3.6 障害通知

ピン モードでは、CQ ドライバが過電流状態に移行した場合、または CQ ドライバの温度センサが  $T_{(WRN)}$  を超えた場合、NFLT1 ピンは Low に駆動されます。両方のフォルト条件がクリアされると、NFLT1 はハイインピーダンスに戻ります。

同様に、DO ドライバが過電流状態に移行した場合、または DO ドライバの温度センサが  $T_{(WRN)}$  を超えた場合、NFLT2 ピンは Low に駆動されます。両方のフォルト条件がクリアされると、NFLT2 はハイインピーダンスに戻ります。

LP 電源または VOUT 電源が UVLO スレッショルドより低下した場合、RESET ピンが Low になります。LP と VOUT の両方が UVLO スレッショルドを上回ると、RESET ピンが High になります。

注:NFLT1 = [CUR\_OK1 && TMP\_OK1]。LDO にはサーマル センサが搭載されています。センサの温度が  $T_{(SD)}$  に達すると、LDO をオフにし、CQ と DO ドライバの両方をオフにすることができます。

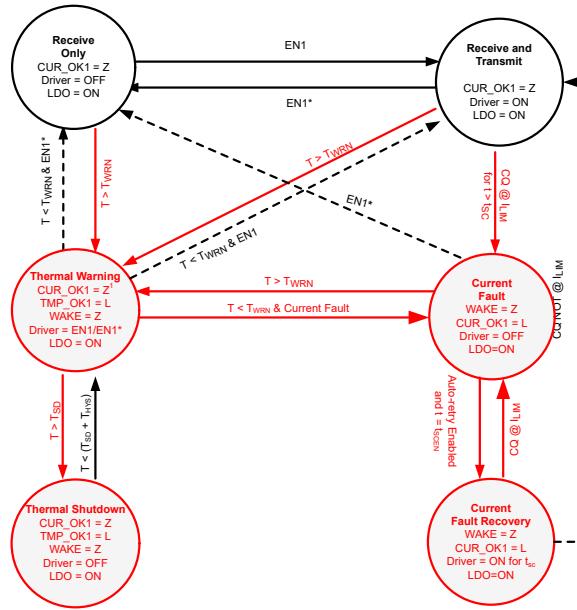

図 7-2. CQ ドライバ状態図

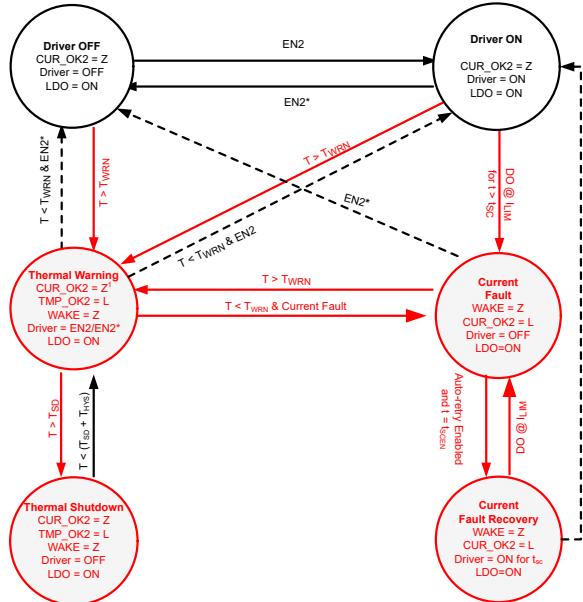

図 7-3. DO ドライバ状態図

### 注

注:NFLT2 = [CUR\_OK2 && TMP\_OK2]。LDO にはサーマル センサが搭載されています。センサの温度が  $T_{(SD)}$  に達すると、LDO をオフにし、CQ と DO ドライバの両方をオフにすることができます。

### 7.3.6.1 サーマル警告、サーマル シャットダウン

TIOL221 には、3 つの個別のサーマル センサが搭載されており、各ドライバに 1 つ、もう 1 つは LDO に接続されます。

CQ ドライバ周囲のダイ温度が  $T_{(WRN)}$  を超えると、NFLT1 フラグが Low に保持され、過熱問題の可能性を示します。 $T_J$  が  $T_{(SDN)}$  を超えると、CQ ドライバは無効になります。LDO と DO ドライバは、それぞれのサーマル センサが  $T_{(SDN)}$  を超えない限り動作します。温度が温度スレッショルドを下回ると（かつ  $T_{(HYS)}$  後）すぐに、EN1 および TX1 ピンの状態に従い、内部回路によってドライバが再度有効になります。

DO ドライバ周囲のダイ温度が  $T_{(WRN)}$  を超えると、NFLT2 フラグが Low に保持され、過熱問題の可能性を示します。 $T_J$  が  $T_{(SDN)}$  を超えると、DO ドライバは無効になります。LDO と CQ ドライバは、それぞれのサーマル センサが  $T_{(SDN)}$  を超えない限り動作します。温度が温度スレッショルドを下回ると（かつ  $T_{(HYS)}$  後）すぐに、EN2 および TX2 ピンの状態に従い、内部回路によってドライバが再度有効になります。

LDO 付近のサーマル センサによって、 $T_{(SDN)}$  を超える温度が検出されます。LDO と両方のドライバがオフになり、RESET が Low に保持されます。温度が温度スレッショルドを下回ると（かつ  $T_{(HYS)}$  後）すぐに、内部回路によって LDO が再度有効になり、VOUT が UVLO スレッショルドを上回った後、ドライバや RESET が解放されます。

### 7.3.7 内蔵電圧レギュレータ (LDO)

TIOL221 にはリニア電圧レギュレータ (LDO) が内蔵されており、外部コンポーネントに電力を供給できます。LDO は最大 20mA を供給できます。LDO 出力レベルは VSEL ピンを使用して設定できます。VSEL が GND に接続されている場合、VOUT は LP で入力電源として 3.3V の出力を供給するように構成されます。VSEL がフローティングのままの場合、VOUT は 3.3V 出力を供給し、V5IN を電源入力として、デバイスの消費電力を低減します。VSEL が VOUT に接続されている場合、VOUT は 5V に設定されます。電源投入時に VSEL ピンのステータスが検出され、VOUT 出力レベルが決定され、次の電源オン サイクルまでラッチされます。

**表 7-5. VSEL ピンを使用した LDO 出力構成**

| VSEL ピン接続 | VOUT             |

|-----------|------------------|

| LM に接続    | 3.3V (LP から供給)   |

| フローティング   | 3.3V (V5IN から供給) |

| VOUT に接続  | 5V               |

5V 出力に構成した場合、電圧レギュレータは LM を基準として 7V ~ 36V の範囲の入力電圧 LP で動作します。3.3V 出力に構成した場合、レギュレータは V5IN 電源 (VSEL がフローティングのとき) または LP 電源 (VSEL が VOUT に接続されている場合) のいずれかで動作できます。

VOUT の 3.3V 出力の電源入力として V5IN を選択すると、オンチップの消費電力を低減できます。VSEL がフローティングに設定されているとき、V5IN 電源が存在しない、または V5IN\_UVLO スレッショルドを下回った場合、VOUT レギュレータはシャットオフされ、RESET 出力はアクティブになります。

LDO は、出力に  $1\mu F$  以上の値の標準的なセラミックコンデンサを使用して安定するように設計されています。温度による値と ESR の変動が最小限に抑えられているため、X5R および X7R タイプのコンデンサが最適です。最大 ESR は  $1\Omega$  未満である必要があります。許容誤差と DC バイアス効果により、出力安定性を確保するための最小容量は  $1\mu F$  です。

電圧レギュレータには、大容量のデカップリング コンデンサや偶発的な短絡状態による初期起動突入電流に対して保護するため、35mA 電流制限が内蔵されています。

### 7.3.8 逆極性保護

逆極性保護回路は、LP、CQ、DO、DI、LM ピンへの誤った逆極性接続からデバイスを保護します。このピンの任意の組み合わせを、最大 65V (max) の DC 電圧に接続できます。いずれかのピン間の最大電圧は、いつでも 65V DC を超えないようにする必要があります。

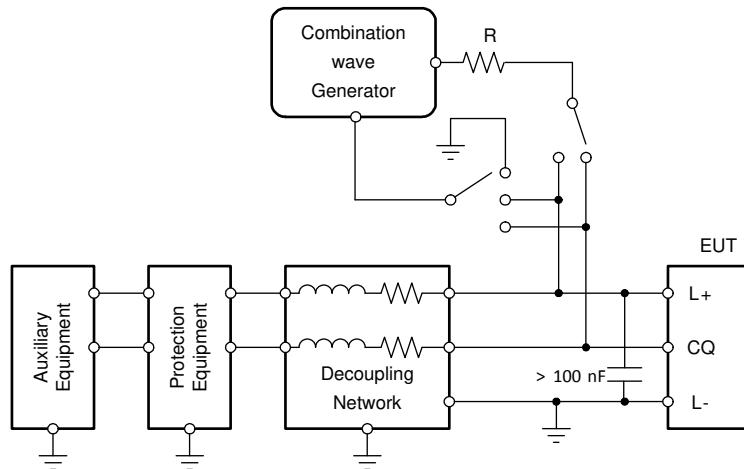

### 7.3.9 サージ保護および過渡波形耐性を内蔵

デバイスの LP、CQ、DO、DI の各ピンは、ソース インピーダンス  $500\Omega$  で最大  $1.2\text{kV}$  の  $1.2/50 - 8/20\mu\text{s}$  IEC 61000-4-5 サージに耐えられます。サージテストは、LP と LM の間に最低  $100\text{nF}$  の電源デカップリング コンデンサを使用し、VOUT と LM の間に最低  $1\mu\text{F}$  を使用して実施する必要があります。

より高い過渡保護レベルが必要な場合、外付け TVS ダイオードが必要になることがあります。システム設計者は、目的の電流レベルで、外部ダイオードの最大クランプ電圧が  $65\text{V}$  未満であることを確認する必要があります。このデバイスは、最大  $\pm 70\text{V}$  の過渡パルス  $< 100\mu\text{s}$  に耐えられます。

$1.2/50 - 8/20\mu\text{s}$  CWG

$R = 500\Omega$

図 7-4. サージ テスト設定

### 7.3.10 低電圧誤動作防止(UVLO)

LP 電圧または VOUT 電源のいずれかがそれぞれの UVLO スレッショルドを下回ると、デバイスは UVLO に移行します。電源が UVLO スレッショルドを下回ると、ただちに  $\overline{\text{RESET}}$  が Low になり、ドライバ (CQ および DO) はディスエーブル (ハイインピーダンス) になります。このモードではレシーバの性能は規定されていません。

電源が立ち上がりスレッショルドより高くなると、 $\overline{\text{RESET}}$  ピンは High になります。 $t_{(\text{UVLO})}$  遅延後にドライバ出力がオンになります。

### 7.3.11 割り込み機能

この割り込みは、SPI モードで **INT** ピンを介して一部の重要なイベントをマイコンに通知するために使用されます。SPI モードでは、**INT** ピンはプッシュプル出力段です。割り込み生成イベントが発生すると、**INT** ピンは **Low** になります。

以下のイベントが割り込みを生成でき、割り込みレジスタに対応するビットが設定されます。

- サーマル シャットダウン (TSD\_INT)

- CQ で有効なウェークアップ パルスを受信 (WU\_INT)

- DO 出力過電流フォルト (DO\_FAULT\_INT)

- CQ 出力過電流フォルト (CQ\_FAULT\_INT)

- LP が警告スレッショルドを下回る (LPW\_INT)

- V5IN が UVLO スレッショルドを下回る (UV\_V5\_INT)

- 温度が過熱警告スレッショルドを上回る (TEMP\_WARN)

個別の割り込みイベントを **INT\_MASK** レジスタでマスクできます。割り込みがマスクされている場合、その特定のイベントは **INT** ピンを有効にしません。ただし、割り込み生成イベントが発生すると、割り込みビットが設定されます。

割り込み生成イベントが存在しなくなった場合でも、割り込みビットは自動的にクリアされません。マイコンにより割り込みビットを明示的にクリアする必要があります。マイコンによってすべての割り込みビットがクリアされ（読み取り時にクリア）、そのイベントが持続しない場合、**INT** ピンが **High** になります。また、すべての割り込みビットがマスクされている場合、**INT** ピンも **High** になります。割り込みビットがマスクされておらず、割り込みビットのいずれかがまだ設定されている場合、**INT** ピンは再び **Low** になります。

## 7.4 デバイスの機能モード

このデバイスは 2 つのモード (ピン モードまたは SPI モード) で動作できます。SPI/PIN ピンが Low の場合、デバイスはピン モードで動作します。SPI/PIN ピンが High の場合、デバイスは SPI モードで動作します。

いずれかのモードでの CQ ドライバ制御については、表 7-6 を参照してください。DO ドライバ制御については、表 7-7 を参照してください。さらに、SPI モードを使用する場合、CQ と DO ドライバの両方を互いに接続して、より大きな負荷電流を駆動できます。この構成の設定については、表 7-8 および [CQ および DO トラッキング モード](#) で説明します。ドライバモード、電流制限、過電流ブランкиング時間など、ドライバ構成設定を変更する前に、ドライバをディスエーブル状態にすることを推奨します。

**表 7-6. CQ 制御**

| SPI/PIN | EN1       | TX1 | CQ_TX_MODE = 11<br>(CQ ディスエーブル) | CQ_Q | NPN モード | PNP モード | プッシュプル モード |

|---------|-----------|-----|---------------------------------|------|---------|---------|------------|

| L       | L またはオープン | L   | X                               | X    | Z       | Z       | Z          |

|         |           | H   | X                               | X    | Z       | Z       | Z          |

|         | H         | L   | X                               | X    | Z       | H       | H          |

|         |           | H   | X                               | X    | L       | Z       | L          |

| H       | L         | L   | 0                               | 0    | Z       | Z       | Z          |

|         |           | H   |                                 |      | Z       | Z       | Z          |

|         |           | L   |                                 | 1    | Z       | H       | H          |

|         |           | H   |                                 |      | Z       | H       | H          |

|         | H         | L   |                                 | 0    | Z       | H       | H          |

|         |           | H   |                                 |      | L       | Z       | L          |

|         |           | L   |                                 | 1    | Z       | H       | H          |

|         |           | H   |                                 |      | Z       | H       | H          |

|         | X         | X   | 1                               | X    | Z       | Z       | Z          |

**表 7-7. DO 制御**

DO と CQ がトラック (DO\_CQ\_TRACK が 1b に設定) に設定されている場合、表 7-8 を参照してください。

| SPI/PIN | EN2       | TX2 | DO_MODE = 11<br>(DO ディスエーブル) | DO_Q | NPN モード | PNP モード | プッシュプル モード |

|---------|-----------|-----|------------------------------|------|---------|---------|------------|

| L       | L またはオープン | L   | X                            | X    | Z       | Z       | Z          |

|         |           | H   | X                            | X    | Z       | Z       | Z          |

|         | H         | L   | X                            | X    | Z       | H       | H          |

|         |           | H   | X                            | X    | L       | Z       | L          |

| H       | L         | L   | 0                            | 0    | Z       | Z       | Z          |

|         |           | H   |                              |      | Z       | Z       | Z          |

|         |           | L   |                              | 1    | Z       | H       | H          |

|         |           | H   |                              |      | Z       | H       | H          |

|         | H         | L   |                              | 0    | Z       | H       | H          |

|         |           | H   |                              |      | L       | Z       | L          |

|         |           | L   |                              | 1    | Z       | H       | H          |

|         |           | H   |                              |      | Z       | H       | H          |

|         | X         | X   | 1                            | X    | Z       | Z       | Z          |

**表 7-8. DO 制御 (DO\_CQ\_TRACK = 1b の場合)**

DO と CQ をトラック (DO\_CQ\_TRACK を 1b に設定) に設定している場合、DO ドライバは CQ 構成に従い、ドライバ モード、電流制限、ドライバ設定を含む DO 構成は無視されます。

| SPI/PIN | DO_CQ_TRACK<br>ACK = 1b | EN2/TX2/<br>DO_MODE/<br>DO_CQ | EN1 | TX1 | CQ_TX_MO<br>DE = 11<br>(CQ ディスエ<br>ーブル) | CQ_Q | NPN モード<br>(CQ 構成単<br>位) | PNP モード<br>(CQ 構成単<br>位) | プッシュプル<br>モード (CQ<br>構成単位) |

|---------|-------------------------|-------------------------------|-----|-----|-----------------------------------------|------|--------------------------|--------------------------|----------------------------|

| H       | 1b                      | X                             | L   | L   | 0                                       | 0    | Z                        | Z                        | Z                          |

|         |                         |                               |     | H   |                                         |      | Z                        | Z                        | Z                          |

|         |                         |                               |     | L   |                                         | 1    | Z                        | H                        | H                          |

|         |                         |                               |     | H   |                                         |      | Z                        | H                        | H                          |

|         |                         |                               | H   | L   |                                         | 0    | Z                        | H                        | H                          |

|         |                         |                               |     | H   |                                         |      | L                        | Z                        | L                          |

|         |                         |                               |     | L   |                                         | 1    | Z                        | H                        | H                          |

|         |                         |                               |     | H   |                                         |      | Z                        | H                        | H                          |

|         |                         |                               | X   | X   | 1                                       | X    | Z                        | Z                        | Z                          |

**表 7-9. ピンモードでの NPN、PNP、およびプッシュプル モードの選択**

| SPI/PIN | CS/PP | SDI/NPN | CQ および DO ドライバ モード                          |

|---------|-------|---------|---------------------------------------------|

| L       | L     | L       | PNP                                         |

|         | L     | H       | NPN                                         |

|         | H     | X       | プッシュ プル                                     |

| H       | X     | X       | SPI インターフェイス経由で選択さ<br>れた CQ および DO ドライバ モード |

#### 7.4.1 CQ および DO トラッキング モード

SPI モードでは、[DO\\_CQ\\_TRACK](#) ビット設定を使用して、TX1 のみを入力として、EN1 をイネーブル ピンとして使用して、CQ および DO 出力ドライバを互いに同期するように設定できます。このビットがイネーブルになると、両方のドライバは TX1 を入力として受け取り、EN1 イネーブル ピンによって制御されます。[DO\\_CQ\\_TRACK](#) ビットが設定されている場合、以下の構成が有効になります。

- DO 構成設定は無視され、CQ 構成設定が使用されます (過電流、ブランкиング時間、自動再試行、CQ\_Q は両方のドライバに影響を及ぼします)

- TX2 および EN2 入力ピンは無視されます

- 一方のドライバが過電流または過熱フォルトに移行すると、両方のドライバがオフになります。

- フォルト状態に移行するドライバのみの割り込みおよびステータス ビットが設定されます

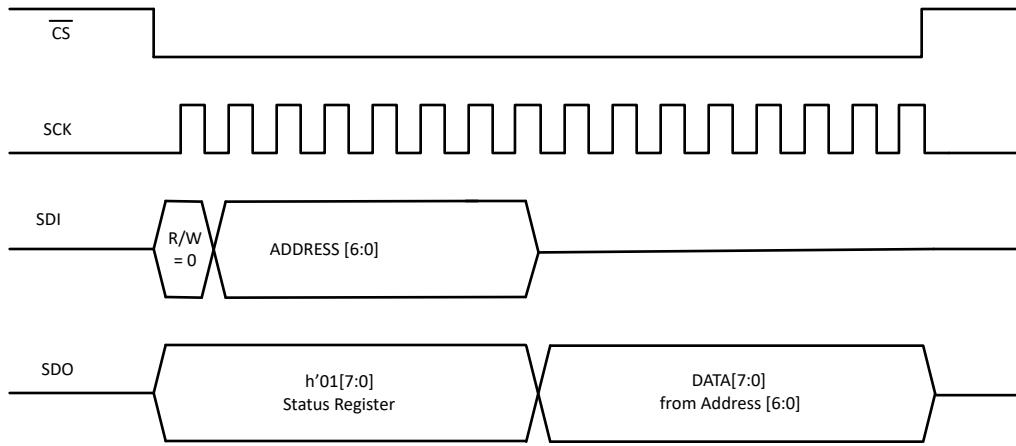

#### 7.5 SPI のプログラミング

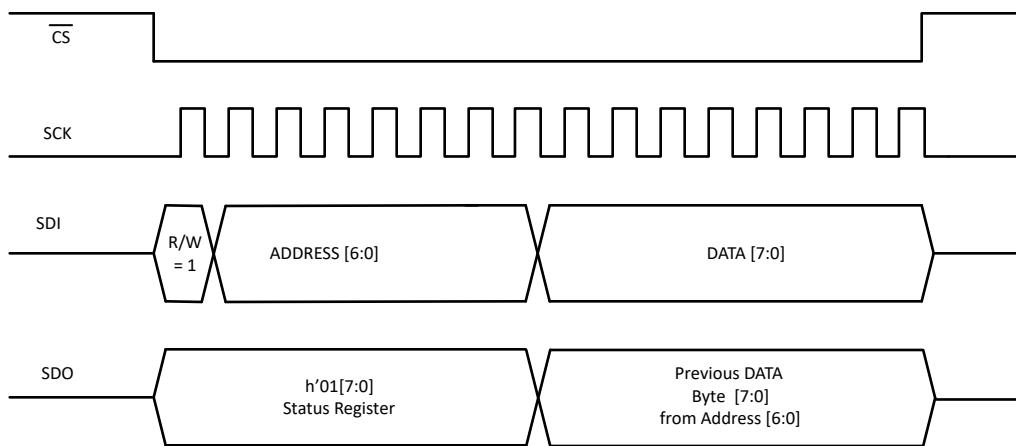

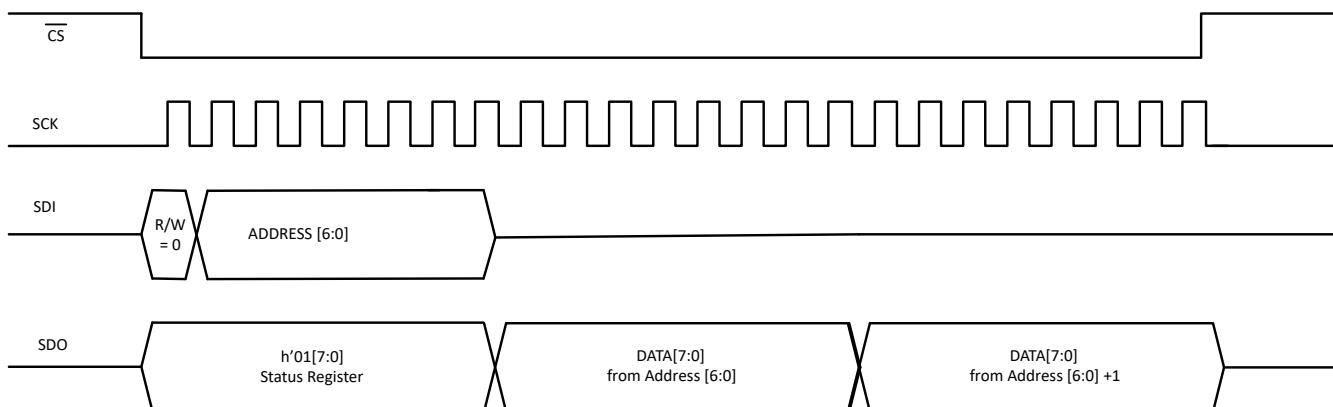

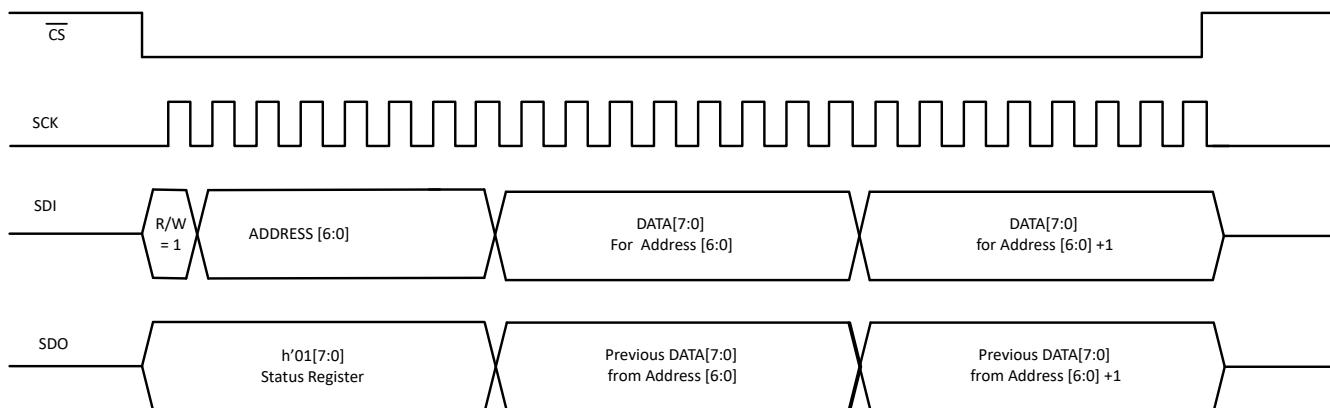

SPI/PIN が High に設定される場合、TIOL221 は SPI モードで動作します。SPI 通信では、標準の SPI を使用します。物理的なデジタル インターフェイス ピンは、[CS/PP](#) (チップ セレクト アクティブ Low)、SDI/NPN (SPI データ入力)、SDO/NFLT2 (SPI データ出力)、および SCK (SPI クロック) です。各 SPI トランザクションは、R/W ビットが付いた 7 ビットアドレスによって開始されます。トランザクションで SDO ピンからシフトアウトされるデータは、常にステータス レジスタであるレジスタ [8'h01\[7:0\]](#) から始まります。このレジスタは、デバイスの高レベルのステータス情報を提供します。アドレスおよび R/W バイトに対する「応答」であるデータ バイトが、その後にシフト アウトされます。非バースト モードに対応する SPI 読み取りおよび書き込みフレーム図については、[図 7-6](#) および [図 7-5](#) を参照してください。バースト モードに対応する SPI 読み取りおよび書き込みフレーム図については、[図 7-8](#) および [図 7-7](#) を参照してください。

SPI コントローラは、TIOL221 と通信するために、SPI MODE0 (クロック極性 CPOL = 0 およびクロック位相 CPHA = 0) でクロック信号とデータ信号を生成する必要があります。SDI 上の SPI 入力データは、SCK の low エッジから high エッジでサンプリングされます。SDO 上の SPI 出力データは、SCK の high エッジから low エッジに変更されます。

図 7-5. SPI 読み取り (シングル バイト)

図 7-6. SPI 書き込み (シングル バイト)

図 7-7. SPI 読み取り (バースト モード)

図 7-8. SPI 書き込み (バースト モード)

## 8 TIOL221 のレジスタ

TIOL221 レジスタのメモリマップされたレジスタを、表 8-1 に示します。表 8-1 にないレジスタ オフセット アドレスはすべて予約済みと見なします。レジスタの内容は変更してはいけません。

表 8-1. TIOL221 のレジスタ

| アドレス | 略称            | レジスタ名        | セクション |

|------|---------------|--------------|-------|

| 0h   | INT           | 割り込み         | 表示    |

| 1h   | STATUS        | ステータス        | 表示    |

| 2h   | DEVICE_CONFIG | デバイス設定       | 表示    |

| 3h   | CQ_CURLIM     | CQ ドライバの電流制限 | 表示    |

| 4h   | CQ_CONFIG     | CQ の構成       | 表示    |

| 5h   | DIO_CONFIG    | DIO の構成      | 表示    |

| 6h   | DO_CURLIM     | DO ドライバの電流制限 | 表示    |

| 7h   | DEVICE_ID     | デバイス ID      | 表示    |

| 8h   | INT_MASK      | 割り込みマスク      | 表示    |

| 9h   | RESET_CONFIG  | リセットピン構成レジスタ | 表示    |

表の小さなセルに収まるように、複雑なビット アクセス タイプを記号で表記しています。表 8-2 に、このセクションでアクセスタイプに使用しているコードを示します。

表 8-2. TIOL221 のアクセス タイプ コード

| アクセスタイプ       | コード    | 説明               |

|---------------|--------|------------------|

| 読み取りタイプ       |        |                  |

| R             | R      | 読み出し             |

| RC            | R<br>C | 読み出し後<br>クリア     |

| 書き込みタイプ       |        |                  |

| W             | W      | 書き込み             |

| リセットまたはデフォルト値 |        |                  |

| -n            |        | リセット後の値またはデフォルト値 |

## 8.1 INT レジスタ (アドレス = 0h) [リセット = 00h]

図 8-1 に、INT を示し、表 8-3 に、その説明を示します。

概略表に戻ります。

割り込みレジスタは、各種の故障状態の現在のステータスを反映します。�ルトがクリアされた後も、割り込みレジスタは自動的にクリアされません。故障状態が存在しない場合、読み取り時にレジスタがクリアされます

**図 8-1. INT レジスタ**

| 7       | 6      | 5             | 4             | 3       | 2    | 1         | 0         |

|---------|--------|---------------|---------------|---------|------|-----------|-----------|

| TSD_INT | WU_INT | DO_FAULT_IN_T | CQ_FAULT_IN_T | LPW_INT | 予約済み | UV_V5_INT | TEMP_WARN |

| RC-0b   | RC-0b  | RC-0b         | RC-0b         | RC-0b   | R-0b | RC-0b     | RC-0b     |

**表 8-3. INT レジスタ フィールドの説明**

| ビット | フィールド        | タイプ | リセット | 説明                                                                                                                                                    |

|-----|--------------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|