# CC2755x10 SimpleLink 2.4GHz 高性能ワイヤレスマイコンファミリ

## 1 特長

### ワイヤレス MCU 処理素子

- Arm® Cortex®-M33 プロセッサ、(96MHz) FPU (浮動小数点ユニット)、TrustZone®-M サポート、機械学習アクセラレーション向けの CDE (カスタム データパス拡張機能) 搭載

- アルゴリズム処理ユニット (APU) (96MHz)

- 効率的なベクトル演算と行列演算のための数学アクセラレータ

- IFFT 用 Bluetooth® チャネル サウンディング後処理のサポートや、MUSIC (Multiple Signal Classification) などの高度な超高分解能アルゴリズム

### ワイヤレス MCU メモリ

- 最大 1MB のインシステム プログラマブル フラッシュ

- 最大 162KB の SRAM

- セキュア ブート信頼済みのルート (RoT) およびシリアル (SPI/UART) ブートローダー付きの 32KB のシステム ROM

- シリアル ワイヤ デバッグ (SWD)

### MCU 周辺機器

- 23 の GPIO、デジタル ペリフェラルを複数の GPIO に配線可能:

- 2 つの SWD IO パッド、GPIO と多重化

- 2 つの LFXT IO パッド、GPIO と多重化

- 19 の DIO (アナログまたはデジタル IO)

- すべての GPIO に、ウェークアップおよび割り込み機能付き

- 3 × 16 ビットおよび 1 × 32 ビットの汎用タイマ、直交デコード モードをサポート

- リアルタイム クロック (RTC)

- ウォッチドッグ タイマ

- Bluetooth® チャネル サウンディング後処理に使用する、無線、RTOS、アプリケーション動作用システム タイマ

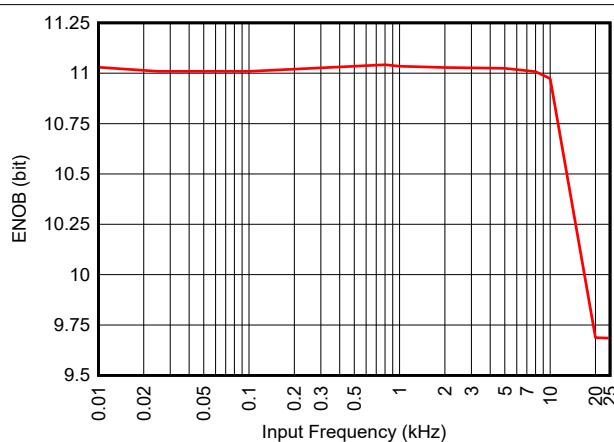

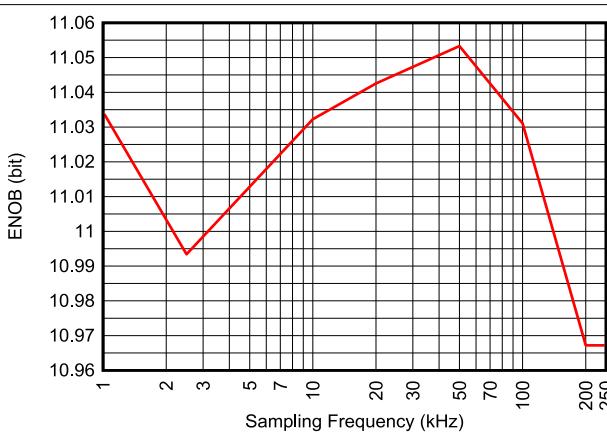

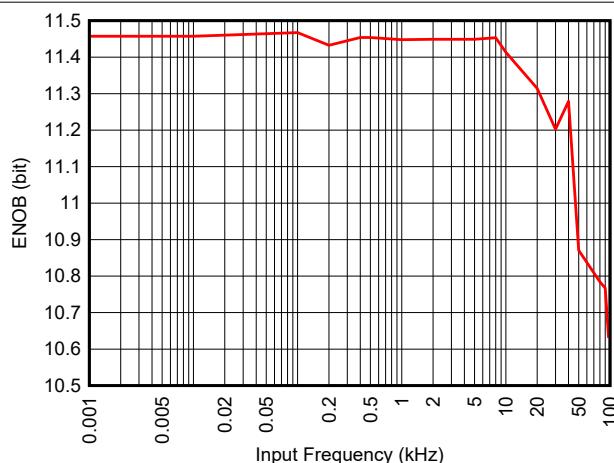

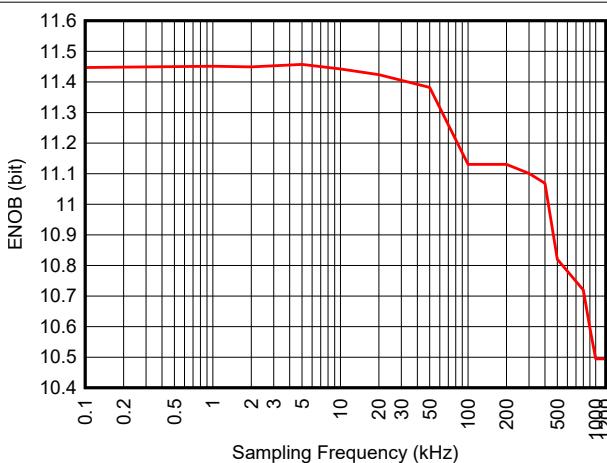

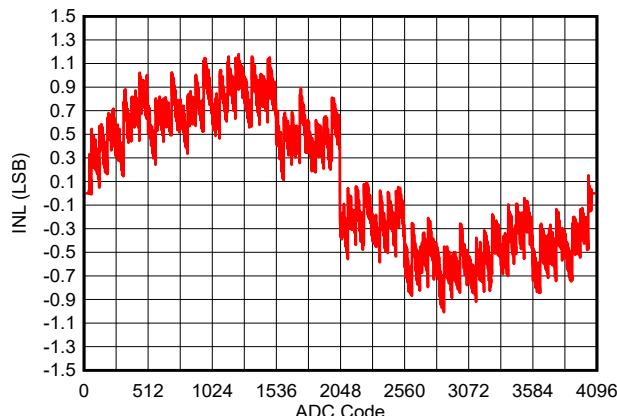

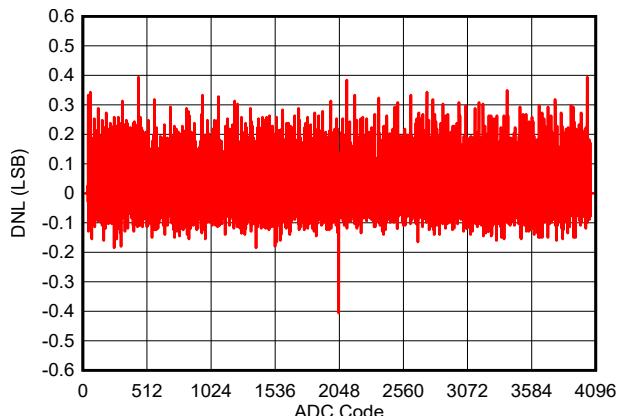

- 12 ビット ADC、最大 1.2MSPS、8 個の外部入力

- 温度センサとバッテリ モニタ

- 1 つの低消費電力コンパレータ

- LIN 機能を搭載した 2 つの UART

- 2 つの SPI

- 1 つの I<sup>2</sup>C

- 1 つの I<sup>2</sup>S

### セキュリティイネーブラ (実現機能)

- 暗号化アクセラレーション動作とセキュア キーストライジをサポートする独自のコントローラと専用メモリを搭載したハードウェア セキュリティ モジュール (HSM):

- AES (最大 256 bit) 暗号化アクセラレータ

- ECC (最大 521 ビット)、RSA (最大 3072 ビット) 公開鍵アクセラレータ

- SHA-2 (最大 512 ビット) アクセラレータ

- 真の乱数ジェネレータ

- HSM フームウェア アップデートのサポート

- AES と ECC のための差動電力解析 (DPA) 対策

- 遅延の制約が厳しいリンクレイヤ動作向けための、個別の AES 128 ビット暗号化アクセラレータ (LAES)

- セキュア ブートとセキュアなファームウェア更新

- セキュア ブート信頼の基点 (RoT)

- Cortex®-M33 TrustZone-M、MPU、ソフトウェア分離用メモリ ファイアウォール

- 電圧グリッチモニタ (VGM)

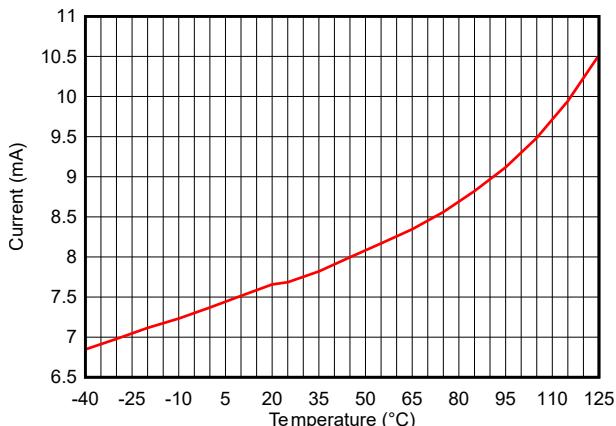

### 低消費電力 (VDDS 3.3V)

- オンチップの降圧型 DC/DC コンバータ

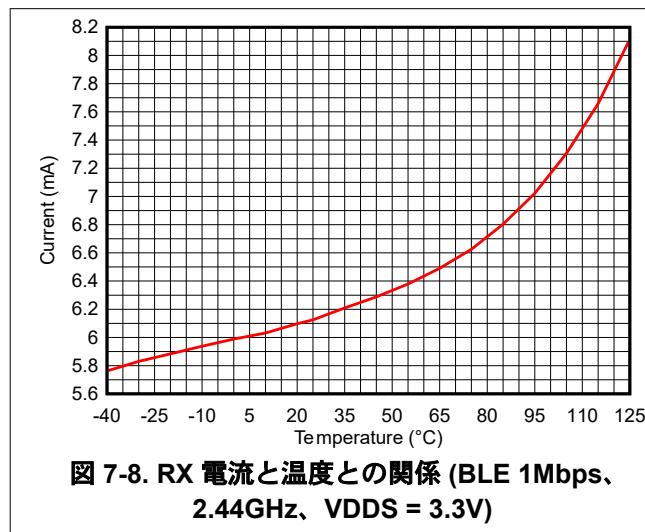

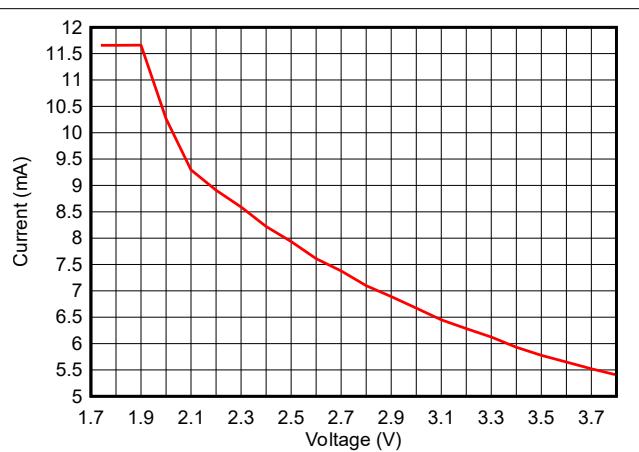

- RX 電流: 6.1mA

- 0dBm での TX 電流: 7.7mA

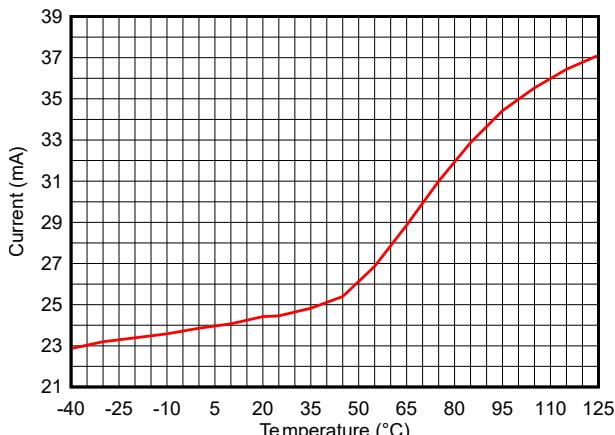

- +10dBm での TX 電流: 24.5mA (R バリエント)

- +20dBm での TX 電流: 143mA (P バリエント)

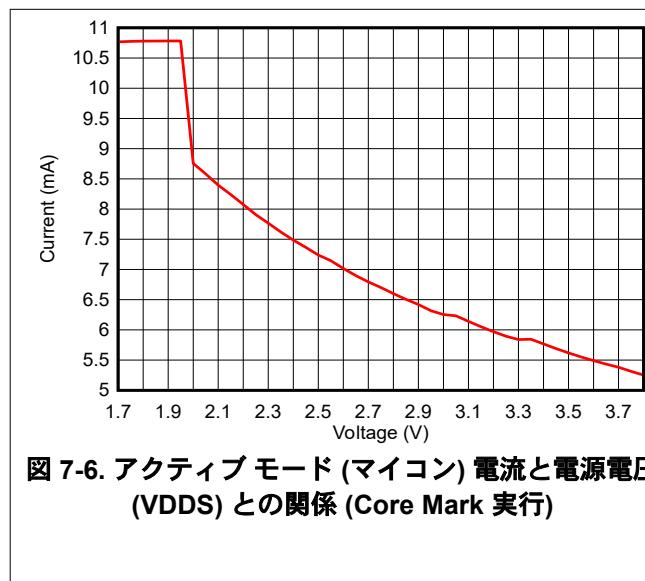

- アクティブ モードの MCU 96MHz (CoreMark®): 6.8mA

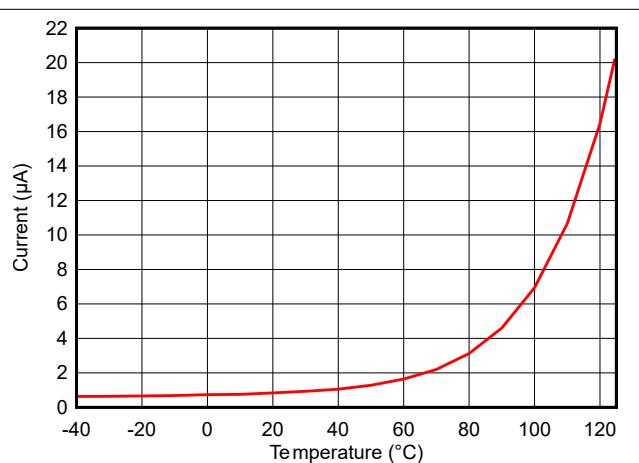

- スタンバイ: 0.9μA (低電力モード、RTC オン、SRAM データ完全保持)

- シャットダウン: 160nA

### 無線プロトコルのサポート

- Bluetooth® Core 6.0 認定済み

- Bluetooth® チャネル サウンディングに対応 (高精度距離測定)

- Matter

- Zigbee® 3.0 認証

- Thread

- 独自システム

- マルチ プロトコル

### 高性能の無線

- Bluetooth® Low Energy 仕様および IEEE 802.15.4 仕様と互換性のある 2.4GHz RF トランシーバ

- 最大 +10dBm の出力電力 (R バリエント)

- 最大 +20dBm の出力電力 (P バリエント)

- BALUN 内蔵

- RF スイッチを内蔵

- レシーバ感度:

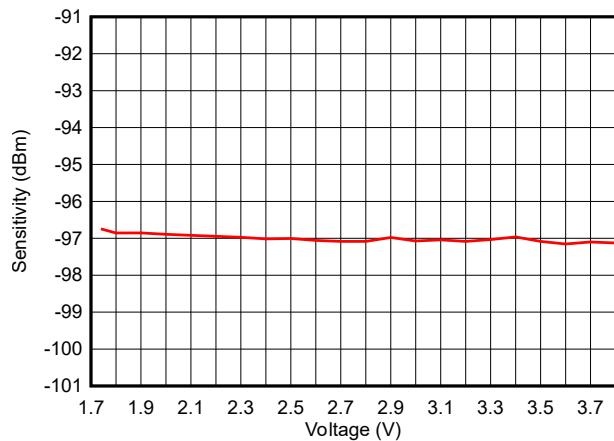

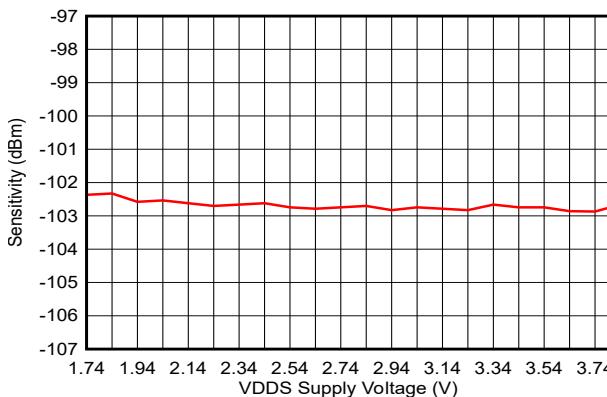

- Bluetooth® LE 125kbps: -103.5dBm

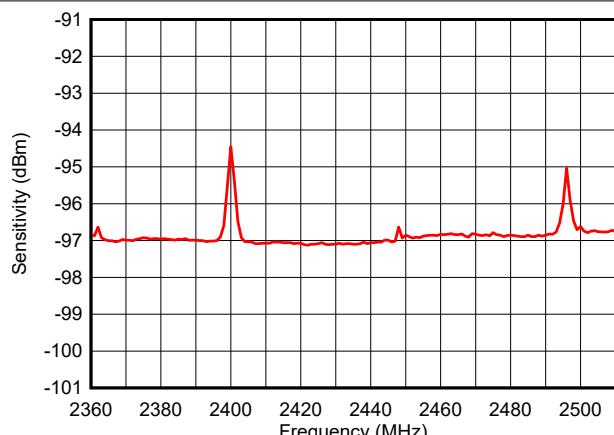

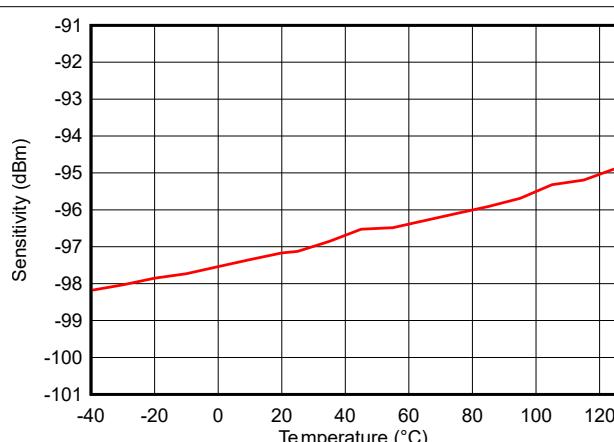

- Bluetooth® LE 1Mbps: -97dBm

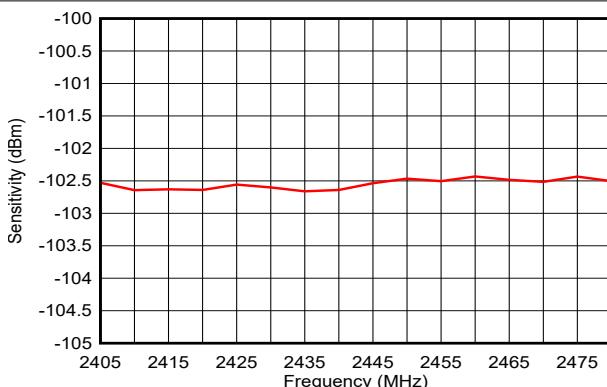

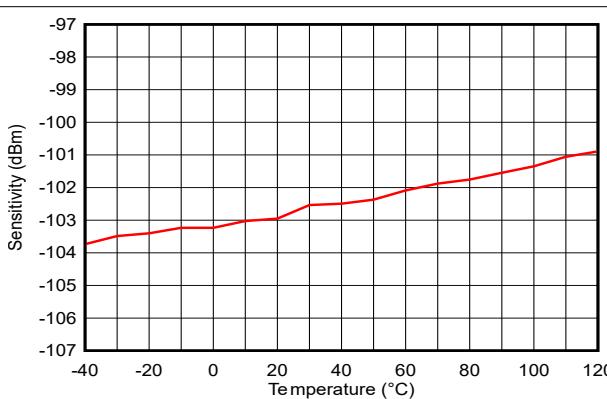

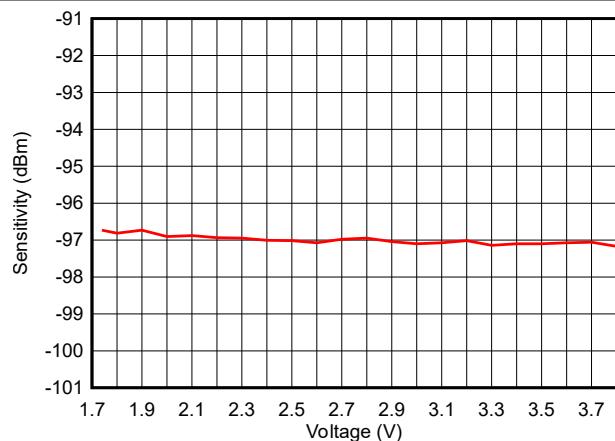

- IEEE 802.15.4 (2.4GHz): -103dBm

## 法規制の順守

- 國際的な無線周波数規制への準拠を目標としたシステム向けに設計

- EN 300 328 (ヨーロッパ)

- FCC CFR47 Part 15 (米国)

- ARIB STD-T66 (日本)

## 開発ツールとソフトウェア

- LP-EM-CC2745R10-Q1 LaunchPad™ 開発キット

- SimpleLink™ Low Power F3 ソフトウェア開発キット (SDK)

- SDK の、完全認定済み Bluetooth® ソフトウェアプロトコル スタック

- 最大 32 の同時マルチロール接続

- Bluetooth® Low Energy 6.0 サポート

- Bluetooth® LE スタックなどの SDK コンポーネントに関する、Automotive SPICE (ASPICE) 準拠

- SysConfig システム コンフィギュレーション ツール

- SmartRF™ Studio による簡素な無線構成

## 動作範囲

- 接合部温度、 $T_J$ : -40°C ~ 125°C

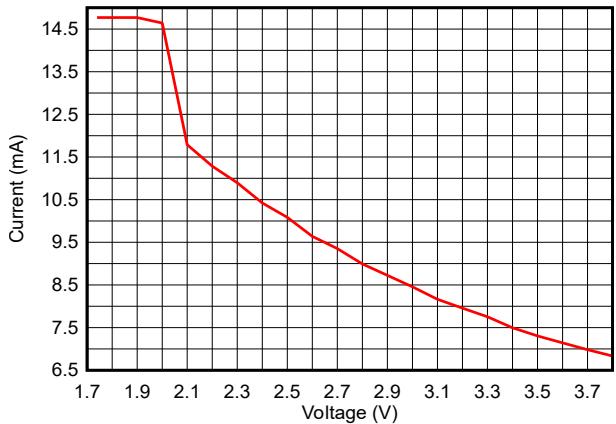

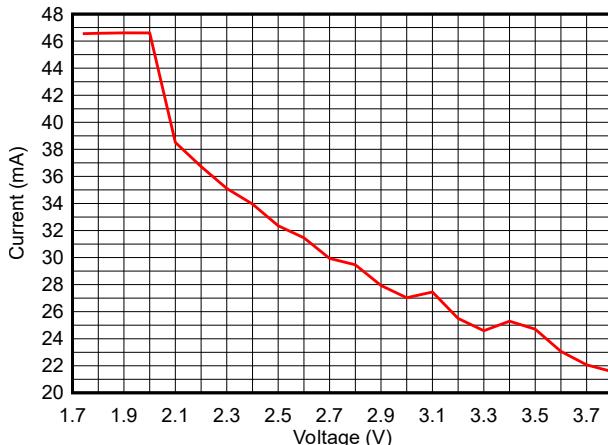

- 広い電源電圧範囲: 1.71V ~ 3.8V

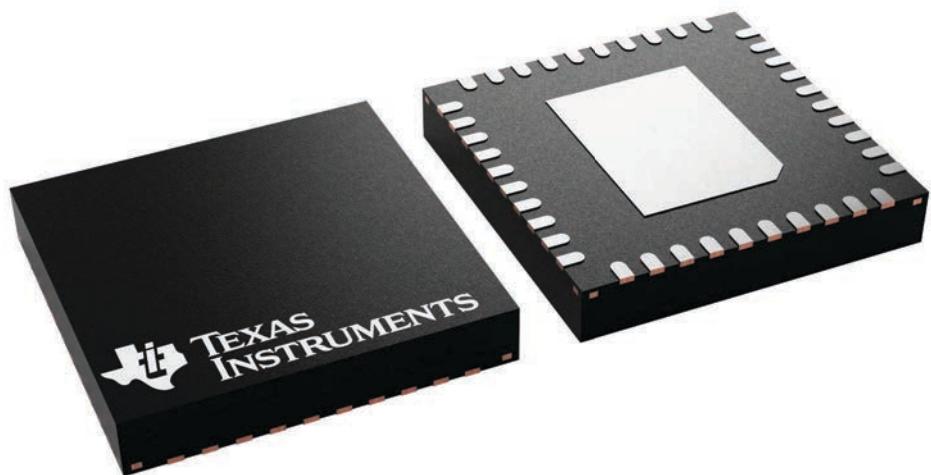

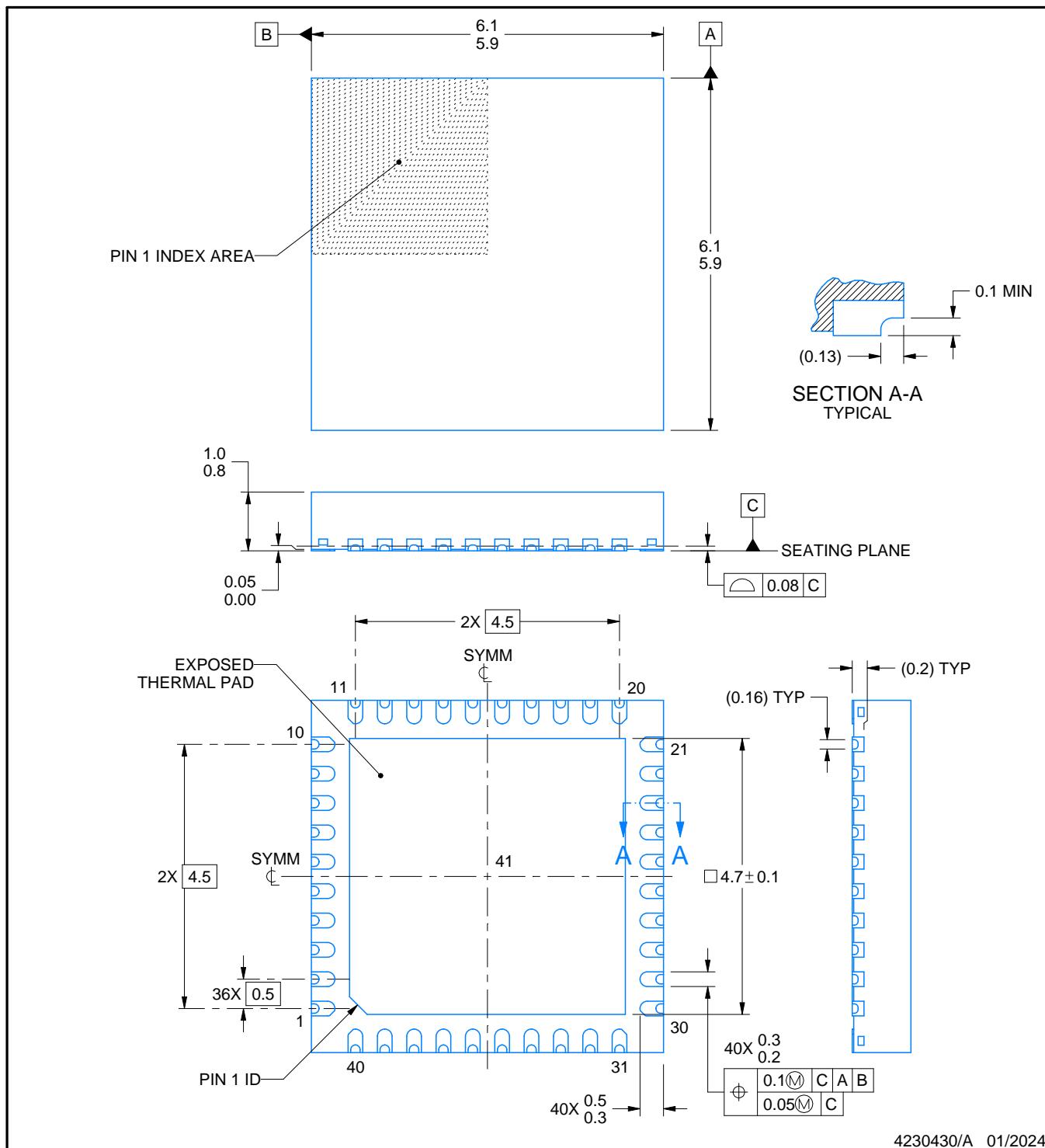

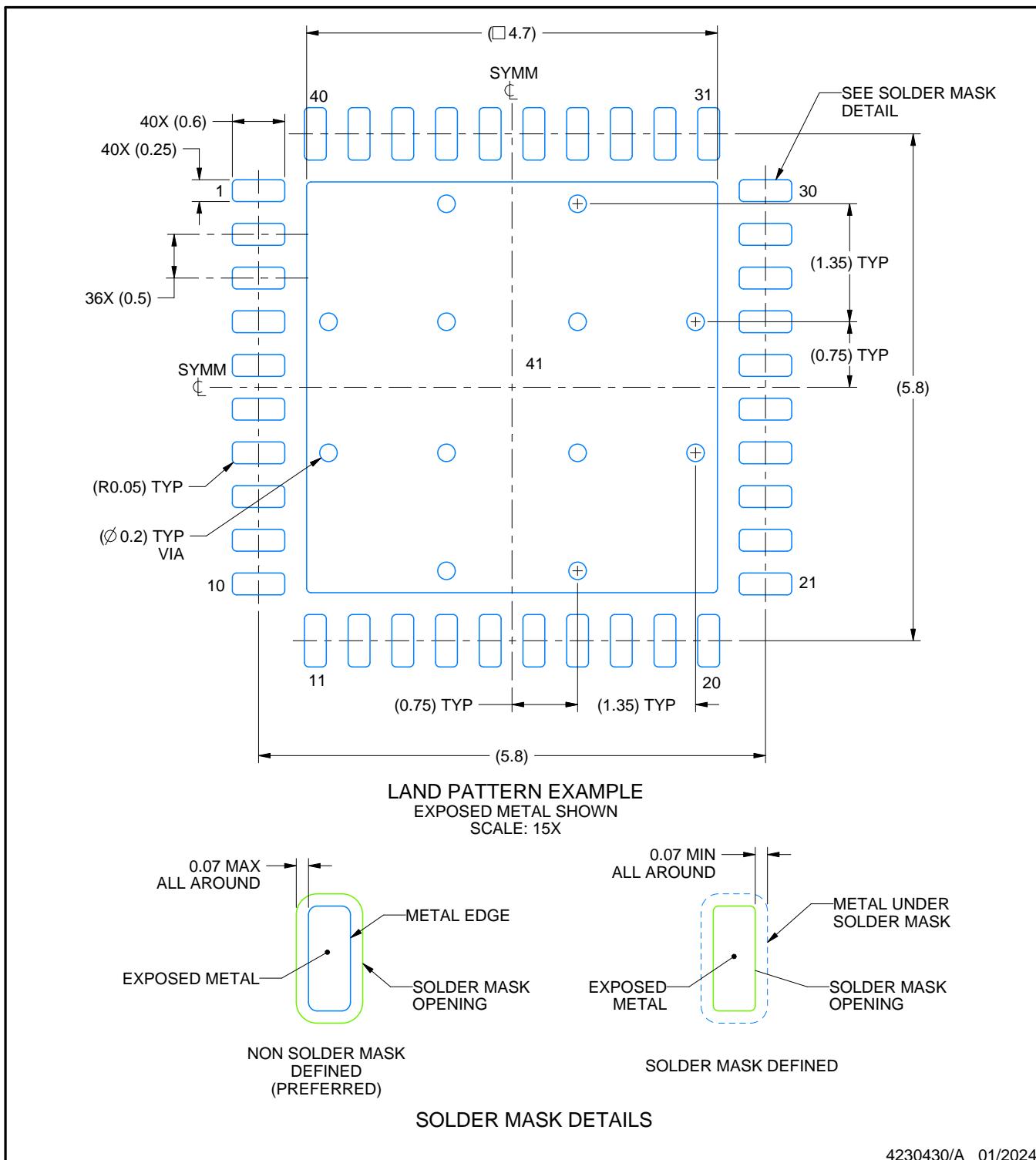

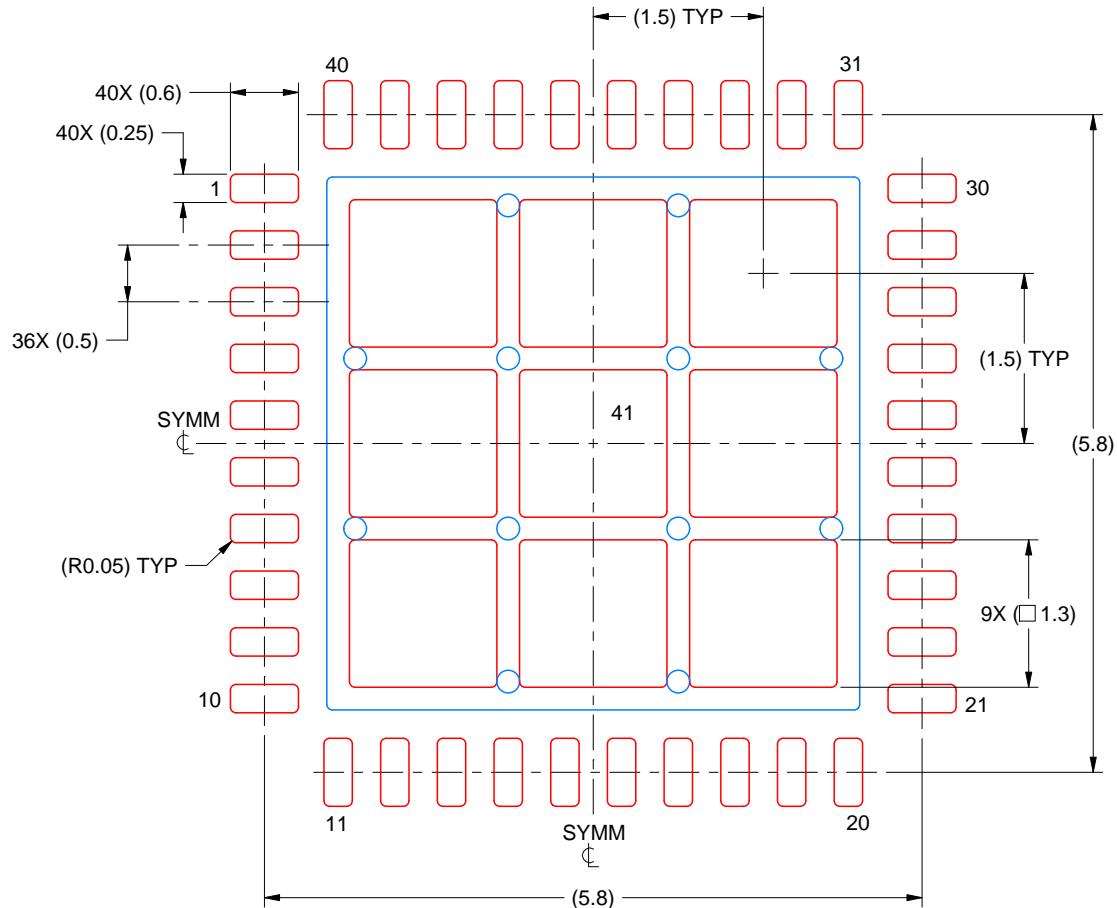

## パッケージ

- ウェッタブル フランク付きの 6mm × 6mm QFN40 パッケージ

- 3.5mm × 3.4mm WCSP (プレビュー)

## 2 アプリケーション

- 医療用

- 家庭用ヘルスケア - 血糖値測定器、血圧計、CPAP 機器、電子体温計

- 患者の監視と診断 - 医療用センサ パッチ

## 3 説明

SimpleLink™ CC2755R および CC2755P デバイス ファミリは 2.4GHz ワイヤレス マイコン (MCU) です。Bluetooth® Low Energy (6.x 以降のバージョン)、Zigbee (3.0 以降)、Thread (1.3 以降)、Matter (1.2 以降) および独自の 2.4GHz アプリケーションを対象としています。これらのデバイスは、ビルディング オートメーション (ワイヤレス センサ、照明制御、ビーコン)、家電製品、アセット トラッキング、医療、パーソナル エレクトロニクス (玩具、HID、スタイルス ペン) の市場における、*OAD* (Over the Air Download) サポートによる、低消費電力のワイヤレス通信に最適化されています。このデバイスの主な機能は次のとおりです。

- Bluetooth® 6.0 およびそれ以前のバージョンの機能に対応:

- LE Coded PHY (長距離)、LE 2Mbit PHY (高速)、アドバタイズ拡張機能、複数のアドバタイズメント セット、CSA#2 の他、以前の Bluetooth® Low Energy 仕様との後方互換性。

- Bluetooth® チャネル サウンディング技術のサポートおよびアルゴリズム処理ユニット (APU) による、高精度、低コスト、セキュアな位相ベースのレンジング メカニズムを用いた距離推定

- APU を使用すると、FFT を含む距離レンジング信号処理アルゴリズムや、MUSIC (MUltiple Signal Classification) などの超高分解能複雑アルゴリズム、またニューラル ネットワーク アルゴリズムも、レイテンシと電力効率に優れた方法で実行できます。

- 機械学習アクセラレーション用の Arm® CDE (Custom Data Extension) 命令のサポート

- SimpleLink™ Low Power F3 ソフトウェア開発キット (SDK) に、完全認定済み Bluetooth® ソフトウェア プロトコルスタックを搭載

- SimpleLink™ Low Power F3 ソフトウェア開発キット (SDK) で Zigbee® プロトコル スタックをサポート

- SIMPLELINK TI OPENTHREAD SDK で Thread プロトコル スタックをサポート

- SIMPLELINK MATTER SDK で Matter スタックをサポート

- コネクテッド ワイヤレス マイコン向けの高度なセキュリティ機能:

- 暗号化アクセラレーションおよび乱数生成操作を処理する専用コントローラを備えた、絶縁型 HSM 環境

- 変更不可能なシステム ROM がもたらす信頼の基点による、セキュア ブートとファームウェア更新

- Arm® Cortex M33 TrustZone-M ベースの信頼できる実行環境のサポート

- HSM と TrustZone-M によるセキュア キー ストレージのサポート

- 電圧グリッチ インジェクションなど、低コスト、低労力、非侵襲的な物理的攻撃の脅威を軽減するハードウェア障害センサ。

- 専用の AES-128 HW アクセラレータにより、タイミング クリティカルなリンクレイヤの暗号化 / 復号化動作を処理

- RTC が動作し、162KB SRAM を完全に保持した状態でのスタンバイ電流が極めて小さいので、特にスリープ期間が長いアプリケーションでバッテリ寿命を大幅に延長可能

- 最小のスタンバイ電流で拡張した温度範囲をサポート

- 内蔵のバランと RF スイッチにより、P バージョンでも同じ RF ピンで送信および受信動作をサポート、またこれにより基板レイアウトの部品表 (BOM) を削減

- Bluetooth® Low Energy に対応する優れた無線感度および堅牢性 (選択度、ブロッキング)

CC2755R および CC2755P デバイスは SimpleLink™ MCU プラットフォームに属しており、シングル コア ソフトウェア開発キット (SDK) と豊富なツール セットを備えた共通の使いやすい開発環境を共有する Wi-Fi®、Bluetooth® Low Energy、Thread、Zigbee、Sub1GHz MCU、ホスト MCU で構成されています。SimpleLink™ プラットフォームは一度で統合を実現でき、製品ラインアップのどのデバイスの組み合わせでも設計に追加できるので、設計要件変更の際もコードの 100% 再利用が可能です。詳細については、[SimpleLink™ MCU プラットフォーム](#)を参照してください。

#### 製品情報

| 部品番号                            | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------------------------------|----------------------|--------------------------|

| CC2755R105E0WRHAR               | QFN40                | 6.0mm × 6.0mm            |

| CC2755R105E0YCJR <sup>(3)</sup> | WCSP                 | 3.5mm × 3.4mm            |

| CC2755P105E0WRHAR               | QFN40                | 6.0mm × 6.0mm            |

(1) 詳細については、「メカニカル、パッケージ、および注文情報」を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

(3) 製品レビューのみ

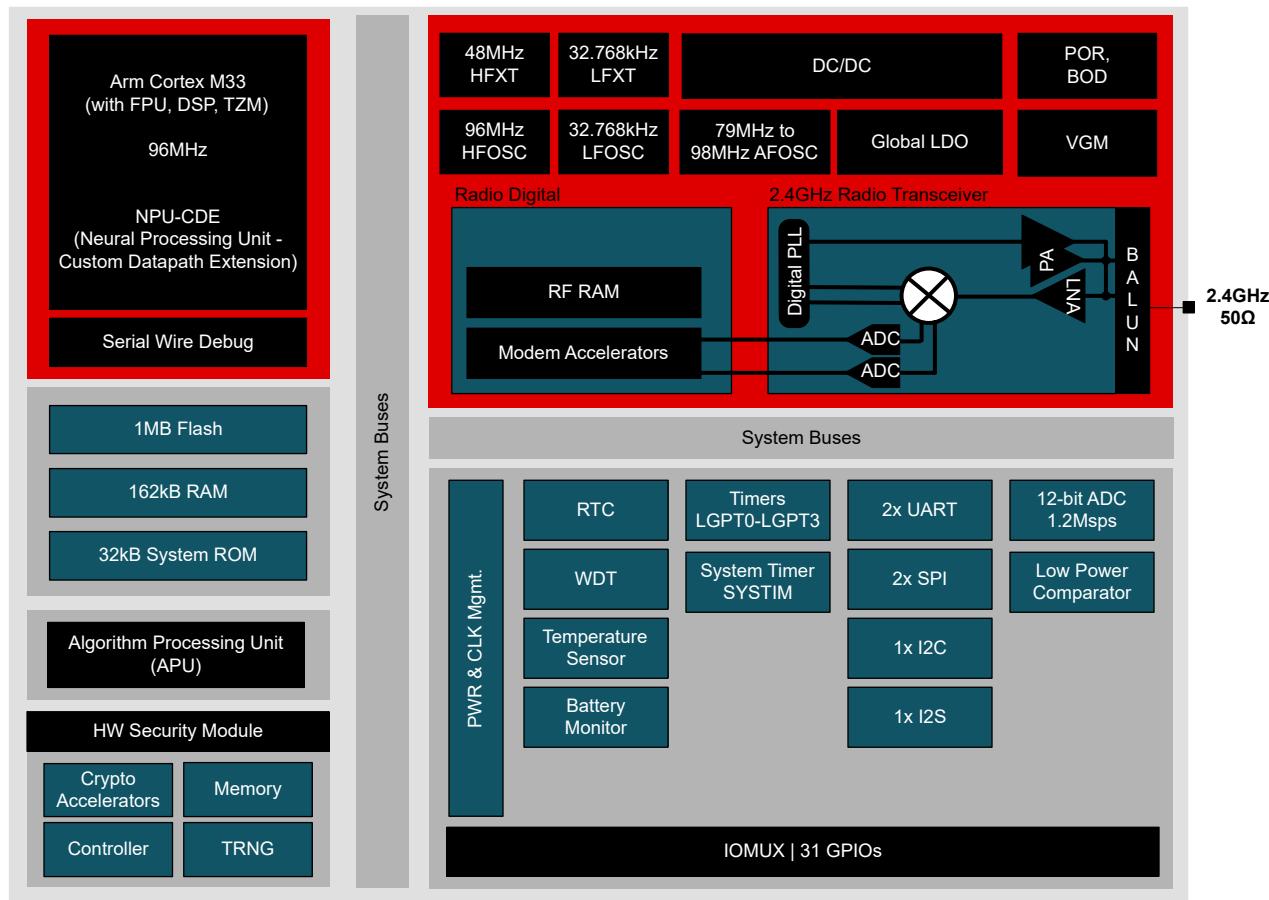

## 4 機能ブロック図

図 4-1. 機能ブロック図

## 目次

|                                           |    |                                                  |    |

|-------------------------------------------|----|--------------------------------------------------|----|

| 1 特長                                      | 1  | 7.22 ペリフェラルのスイッチング特性                             | 50 |

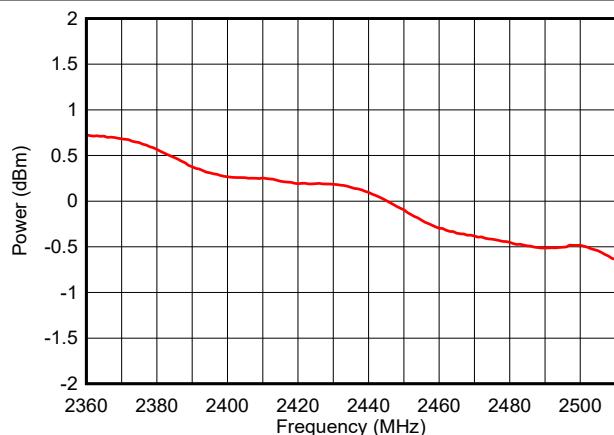

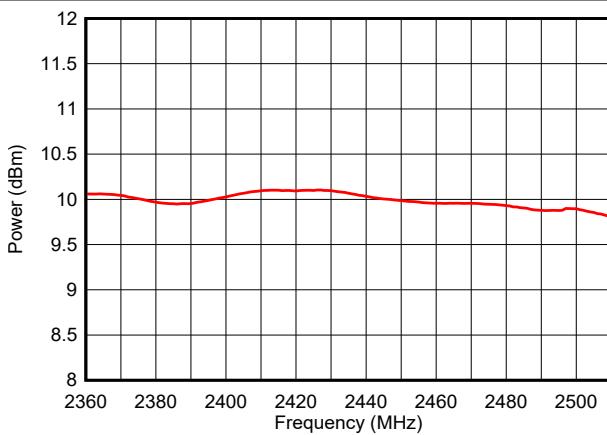

| 2 アプリケーション                                | 2  | 7.23 代表的特性                                       | 59 |

| 3 説明                                      | 2  | 8 詳細説明                                           | 67 |

| 4 機能ブロック図                                 | 4  | 8.1 概要                                           | 67 |

| 5 デバイスの比較                                 | 6  | 8.2 システム CPU                                     | 67 |

| 6 ピン構成および機能                               | 7  | 8.3 無線 (RF コア)                                   | 68 |

| 6.1 ピン配置図                                 | 7  | 8.4 メモリ                                          | 68 |

| 6.2 信号の説明                                 | 10 | 8.5 ハードウェア セキュリティ モジュール (HSM)                    | 69 |

| 6.3 未使用ピンおよびモジュールの接続                      | 13 | 8.6 暗号化                                          | 70 |

| 6.4 ペリフェラル ピン割り当て                         | 14 | 8.7 タイマ                                          | 70 |

| 6.5 ペリフェラル信号の説明                           | 24 | 8.8 アルゴリズム処理ユニット (APU)                           | 72 |

| 7 仕様                                      | 37 | 8.9 シリアル ペリフェラルと I/O                             | 72 |

| 7.1 絶対最大定格                                | 37 | 8.10 バッテリと温度の監視                                  | 73 |

| 7.2 ESD および MSL 定格                        | 37 | 8.11 電圧グリッチモニタ (VGM) と電磁的フォルトインジエクション (EMFI) センサ | 73 |

| 7.3 推奨動作条件                                | 37 | 8.12 μDMA                                        | 73 |

| 7.4 DC/DC                                 | 38 | 8.13 デバッグ                                        | 73 |

| 7.5 GLDO                                  | 38 | 8.14 パワー マネージメント                                 | 74 |

| 7.6 電源およびモジュール                            | 38 | 8.15 クロック システム                                   | 75 |

| 7.7 バッテリ モニタ                              | 38 | 8.16 ネットワーク プロセッサ                                | 75 |

| 7.8 BATMON 温度センサ                          | 38 | 8.17 バラン内蔵、大電力 PA (パワーアンプ)                       | 76 |

| 7.9 消費電力 - 電力モード                          | 39 | 9 アプリケーション、実装、およびレイアウト                           | 77 |

| 7.10 消費電力 - 無線モード (R バリアント)               | 40 | 9.1 リファレンス デザイン                                  | 77 |

| 7.11 消費電力 - 無線モード (P バリアント)               | 40 | 9.2 接合部温度の計算                                     | 78 |

| 7.12 不揮発性 (フラッシュ) メモリの特性                  | 42 | 10 デバイスおよびドキュメントのサポート                            | 79 |

| 7.13 熱抵抗特性                                | 42 | 10.1 デバイスの命名規則                                   | 79 |

| 7.14 RF 周波数帯域                             | 42 | 10.2 ツールとソフトウェア                                  | 79 |

| 7.15 Bluetooth Low Energy - 受信 (RX)       | 43 | 10.3 ドキュメントのサポート                                 | 81 |

| 7.16 Bluetooth Low Energy - 送信 (TX)       | 45 | 10.4 サポート・リソース                                   | 81 |

| 7.17 Bluetooth チャネル サウンディング               | 45 | 10.5 商標                                          | 82 |

| 7.18 Zigbee と Thread - IEEE 802.15.4-2006 |    | 10.6 静電気放電に関する注意事項                               | 82 |

| 2.4GHz (OQPSK DSSS1:8, 250kbps) - RX      | 46 | 10.7 用語集                                         | 82 |

| 7.19 Zigbee と Thread - IEEE 802.15.4-2006 |    | 11 改訂履歴                                          | 82 |

| 2.4GHz (OQPSK DSSS1:8, 250kbps) - TX      | 46 | 12 メカニカル、パッケージ、および注文情報                           | 84 |

| 7.20 2.4GHz RX/TX CW                      | 47 |                                                  |    |

| 7.21 タイミングおよびスイッチング特性                     | 48 |                                                  |    |

## 5 デバイスの比較

| IP                                                    | CC2755P10           | CC2755R10           | CC2755R10 WCSP      |

|-------------------------------------------------------|---------------------|---------------------|---------------------|

| CM33 (MCU)                                            | ✓                   | ✓                   | ✓                   |

| CDE (カスタムデータパス拡張)<br>(機械学習アクセラレーション)                  | ✓                   | ✓                   | ✓                   |

| APU (アルゴリズム処理ユニット)<br>(Bluetooth チャネル サウンディング<br>後処理) | ✓                   | ✓                   | ✓                   |

| HSM                                                   | ✓                   | ✓                   | ✓                   |

| VGM                                                   | ✓                   | ✓                   | ✓                   |

| 2 つの UART、2 つの SPI、1 つの<br>I2C、1 つの I2S               | ✓                   | ✓                   | ✓                   |

| +10dBm PA                                             | ✓                   | ✓                   | ✓                   |

| +20dBm PA                                             | ✓                   |                     |                     |

| ADC12                                                 | ✓                   | ✓                   | ✓                   |

| フラッシュ (KB)                                            | 1024 <sup>(1)</sup> | 1024 <sup>(1)</sup> | 1024 <sup>(1)</sup> |

| SRAM (KB)                                             | 162                 | 162                 | 162                 |

| GPIO                                                  | 23                  | 23                  | 31                  |

| QFN パッケージ・サイズ (mm×mm)                                 | 6 × 6               | 6 × 6               | 利用できません             |

| WCSP パッケージ・サイズ<br>(mm×mm)                             | 利用できません             | 利用できません             | 3.5×3.4             |

(1) デバイス フラッシュ メモリの 96KB は、IHSM ファームウェア用に予約されています。

## 6 ピン構成および機能

### 6.1 ピン配置図

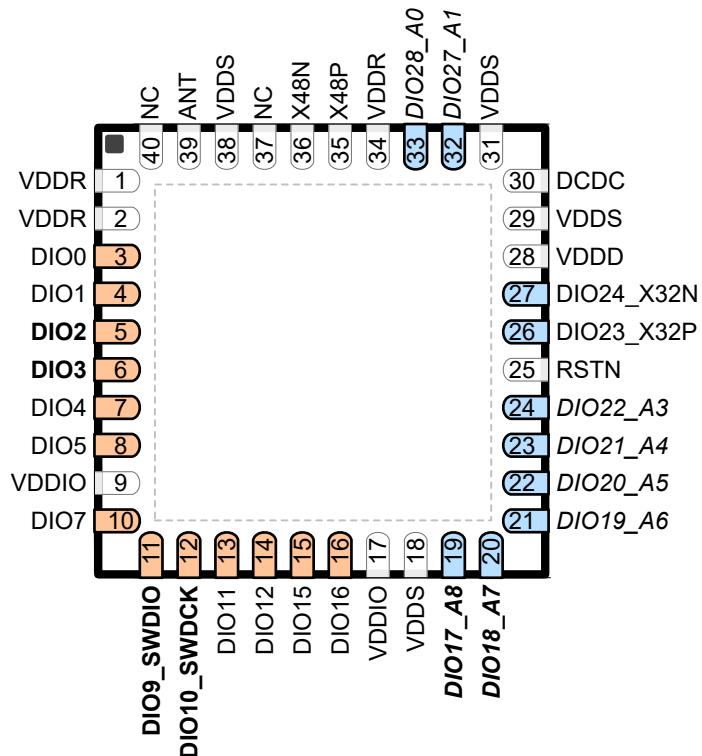

#### 6.1.1 ピン配置図 - RHA パッケージ

図 6-1. RHA (6mm × 6mm) ピン配置、0.5mm ピッチ (上面図)

図 6-1 で太字で示されている次の I/O ピンは、高ドライブ能力を備えています。

- ピン 5、DIO2

- ピン 6、DIO3

- ピン 11、DIO9\_SWDIO

- ピン 12、DIO10\_SWDCK

- ピン 19、DIO17\_A8

- ピン 20、DIO18\_A7

図 6-1 で傾体で示されている次の I/O ピンは、アナログ能力を備えています。

- ピン 19、DIO17\_A8

- ピン 20、DIO18\_A7

- ピン 21、DIO19\_A6

- ピン 22、DIO20\_A5

- ピン 23、DIO21\_A4

- ピン 24、DIO22\_A3

- ピン 32、DIO27\_A1

- ピン 33、DIO28\_A0

図 6-1 に「オレンジ色」で示されている以下の I/O ピンは、VDDIO から供給されます。

- ピン 3、DIO0

- ピン 4、DIO1

- ピン 5、DIO2

- ピン 6、DIO3

- ピン 7、DIO4

- ピン 8、DIO5

- ピン 10、DIO7

- ピン 11、DIO9\_SWDIO

- ピン 12、DIO10\_SWDCK

- ピン 13、DIO11

- ピン 14、DIO12

- ピン 15、DIO15

- ピン 16、DIO16

図 6-1 に「青色」で示されている以下の I/O ピンは、VDDS から供給されます。

- ピン 19、DIO17\_A8

- ピン 20、DIO18\_A7

- ピン 21、DIO19\_A6

- ピン 22、DIO20\_A5

- ピン 23、DIO21\_A4

- ピン 24、DIO22\_A3

- ピン 26、DIO23\_X32P

- ピン 27、DIO24\_X32N

- ピン 32、DIO27\_A1

- ピン 33、DIO28\_A0

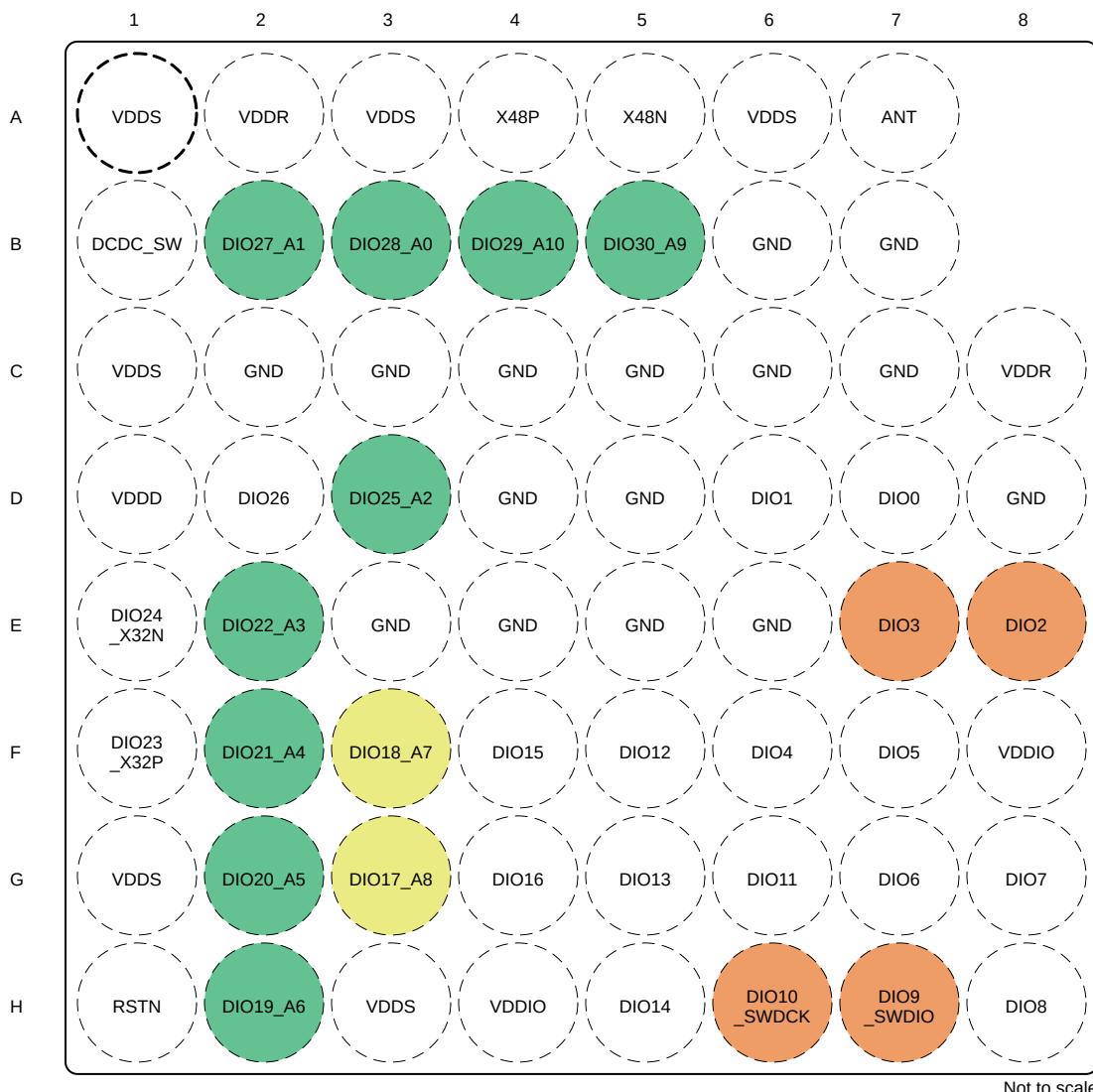

### 6.1.2 ピン配置図 - YCJ パッケージ

図 6-2. YCJ WCSP ピン配置プレビュー (上面図)

表 6-1. 凡例

| 凡例             |

|----------------|

| 高駆動能力          |

| アナログ能力         |

| アナログ能力および高駆動能力 |

以下の I/O ピンは、高駆動能力を備えています。

- E8, DIO2

- E7, DIO3

- H7, DIO9\_SWDIO

- H6, DIO10\_SWDCK

- G3, DIO17\_A8

- F3、DIO18\_A7

以下の I/O ピンは、アナログ能力を備えています。

- G3、DIO17\_A8

- F3、DIO18\_A7

- H2、DIO19\_A6

- G2、DIO20\_A5

- F2、DIO21\_A4

- E2、DIO22\_A3

- D3、DIO25\_A2

- B2、DIO27\_A1

- B3、DIO28\_A0

- B4、DIO29\_A10

- B5、DIO30\_A9

**表 6-2. DIO 電圧ドメイン**

| VDDS       | VDDIO       |

|------------|-------------|

| DIO17_A8   | DIO0        |

| DIO18_A7   | DIO1        |

| DIO19_A6   | DIO2        |

| DIO20_A5   | DIO3        |

| DIO21_A4   | DIO4        |

| DIO22_A3   | DIO5        |

| DIO23_X32P | DIO6        |

| DIO24_X32N | DIO7        |

| DIO25_A2   | DIO8        |

| DIO26      | DIO9_SWDIO  |

| DIO27_A1   | DIO10_SWDCK |

| DIO28_A0   | DIO11       |

| DIO29_A10  | DIO12       |

| DIO30_A9   | DIO13       |

|            | DIO14       |

|            | DIO15       |

|            | DIO16       |

## 6.2 信号の説明

### 6.2.1 信号の説明 - RHA パッケージ

**表 6-3. 信号の説明 - RHA パッケージ**

| ピン   |    | I/O | タイプ  | 説明                                                                     |

|------|----|-----|------|------------------------------------------------------------------------|

| 名称   | 番号 |     |      |                                                                        |

| VDDR | 1  | —   | 電源   | 内部電源には、内部 DC/DC コンバータまたは GLDO から電源を供給する必要があります <sup>(1) (2) (3)</sup>  |

| VDDR | 2  | —   | 電源   | 内部電源には、内部 DC/DC コンバータまたは内部 LDO から電源を供給する必要があります <sup>(1) (2) (3)</sup> |

| DIO0 | 3  | I/O | デジタル | GPIO                                                                   |

| DIO1 | 4  | I/O | デジタル | GPIO                                                                   |

| DIO2 | 5  | I/O | デジタル | GPIO、高駆動能力                                                             |

| DIO3 | 6  | I/O | デジタル | GPIO、高駆動能力                                                             |

**表 6-3. 信号の説明 - RHA パッケージ (続き)**

| ピン          |    | I/O | タイプ         | 説明                                                                                                  |

|-------------|----|-----|-------------|-----------------------------------------------------------------------------------------------------|

| 名称          | 番号 |     |             |                                                                                                     |

| DIO4        | 7  | I/O | デジタル        | GPIO                                                                                                |

| DIO5        | 8  | I/O | デジタル        | GPIO                                                                                                |

| VDDIO       | 9  | —   | 電源          | 1.71V ~ 3.8V 分割レール I/O 電源 <sup>(4)</sup>                                                            |

| DIO7        | 10 | I/O | デジタル        | GPIO                                                                                                |

| DIO9_SWDIO  | 11 | I/O | デジタル        | GPIO, SWD インターフェイス: モード選択または SWDIO、高駆動機能                                                            |

| DIO10_SWDCK | 12 | I/O | デジタル        | GPIO, SWD インターフェイス:シリアル ワイヤ クロック、高駆動能力                                                              |

| DIO11       | 13 | I/O | デジタル        | GPIO                                                                                                |

| DIO12       | 14 | I/O | デジタル        | GPIO                                                                                                |

| DIO15       | 15 | I/O | デジタル        | GPIO                                                                                                |

| DIO16       | 16 | I/O | デジタル        | GPIO                                                                                                |

| VDDIO       | 17 | —   | 電源          | 1.71V ~ 3.8V 分割レール I/O 電源 <sup>(4)</sup>                                                            |

| VDDS        | 18 | —   | 電源          | 1.71V ~ 3.8V 電源 <sup>(4)</sup>                                                                      |

| DIO17_A8    | 19 | I/O | デジタルまたはアナログ | GPIO、アナログ能力、高駆動能力                                                                                   |

| DIO18_A7    | 20 | I/O | デジタルまたはアナログ | GPIO、アナログ能力、高駆動能力                                                                                   |

| DIO19_A6    | 21 | I/O | デジタルまたはアナログ | GPIO、アナログ機能                                                                                         |

| DIO20_A5    | 22 | I/O | デジタルまたはアナログ | GPIO、アナログ機能                                                                                         |

| DIO21_A4    | 23 | I/O | デジタルまたはアナログ | GPIO、アナログ機能                                                                                         |

| DIO22_A3    | 24 | I/O | デジタルまたはアナログ | GPIO、アナログ機能                                                                                         |

| RSTN        | 25 | I   | デジタル        | リセット入力、アクティブ Low 内部プルアップ抵抗なし                                                                        |

| DIO23_X32P  | 26 | I/O | デジタルまたはアナログ | GPIO, 32kHz 水晶発振器ピン 1、オプションの TCXO 入力                                                                |

| DIO24_X32N  | 27 | I/O | デジタルまたはアナログ | GPIO, 32kHz 水晶発振器ピン 2                                                                               |

| VDDD        | 28 | —   | 電源          | 内部 1.32V レギュレーション済みコア電源。外部 1μF デカップリング コンデンサを接続します。 <sup>(1)</sup>                                  |

| VDDS        | 29 | —   | 電源          | 1.71V ~ 3.8V 電源 <sup>(4)</sup>                                                                      |

| DCDC        | 30 | —   | 電源          | 内部 DC/DC コンバータのスイッチング ノード <sup>(4)</sup>                                                            |

| VDDS        | 31 | —   | 電源          | 1.71V ~ 3.8V 電源。外部 10μF デカップリング コンデンサを接続します。 <sup>(4)</sup>                                         |

| DIO27_A1    | 32 | I/O | デジタルまたはアナログ | GPIO、アナログ機能                                                                                         |

| DIO28_A0    | 33 | I/O | デジタルまたはアナログ | GPIO、アナログ機能                                                                                         |

| VDDR        | 34 | —   | 電源          | 内部電源には、内部 DC/DC コンバータまたは内部 LDO から電源を供給する必要があります。外部 10μF デカップリング コンデンサを接続します。 <sup>(1) (2) (3)</sup> |

| X48P        | 35 | —   | アナログ        | 48MHz 水晶発振器ピン 1                                                                                     |

| X48N        | 36 | —   | アナログ        | 48MHz 水晶発振器ピン 2                                                                                     |

| NC          | 37 | —   | —           | 接続なし                                                                                                |

| VDDS        | 38 | —   | 電源          | 1.71V ~ 3.8V 電源 <sup>(4)</sup>                                                                      |

| ANT         | 39 | —   | RF          | 2.4GHz TX, RX                                                                                       |

| NC          | 40 | —   | —           | 接続なし <sup>(6)</sup>                                                                                 |

| EGP         | —  | —   | GND         | グランド – 露出グランド パッド <sup>(5)</sup>                                                                    |

(1) このピンには外部回路を供給しないでください。

(2) VDDR ピン 1, 2, 34 は、PCB 上で互いに接続する必要があります。

(3) 内部 DC/DC および LDO からの出力は、1.5V に調整されています。

(4) 詳細については、「ドキュメント サポート」に記載されている『テクニカル リファレンス マニュアル』を参照してください。

(5) ESP は、本デバイスの唯一のグランド接続です。デバイスを適切に動作させるには、プリント基板 (PCB) 上のデバイスのグランドに対する良好な電気的接続が不可欠です。

(6) このピンは、ダイには接続されていません。LP-EM-CC2745R10-Q1、リファレンス デザインでは、このピンをグランドに接続して、アンテナ パスのシールド性能を向上させています。

## 6.2.2 信号の説明 - YCJ パッケージ

表 6-4. 信号の説明 - YCJ パッケージ プレビュー

| ピン          |    | I/O | タイプ         | 説明                                                                                                           |

|-------------|----|-----|-------------|--------------------------------------------------------------------------------------------------------------|

| 名称          | 番号 |     |             |                                                                                                              |

| VDDR        | C8 | —   | 電源          | 内部電源には、内部 DC/DC コンバータまたは内部 LDO から電源を供給する必要があります。 <a href="#">(1)</a> <a href="#">(2)</a> <a href="#">(3)</a> |

| VDDR        | A2 | —   | 電源          | 内部電源には、内部 DC/DC コンバータまたは内部 LDO から電源を供給する必要があります。 <a href="#">(1)</a> <a href="#">(2)</a> <a href="#">(3)</a> |

| DIO0        | D7 | I/O | デジタル        | GPIO                                                                                                         |

| DIO1        | D6 | I/O | デジタル        | GPIO                                                                                                         |

| DIO2        | E8 | I/O | デジタル        | GPIO、高駆動能力                                                                                                   |

| DIO3        | E7 | I/O | デジタル        | GPIO、高駆動能力                                                                                                   |

| DIO4        | F6 | I/O | デジタル        | GPIO                                                                                                         |

| DIO5        | F7 | I/O | デジタル        | GPIO                                                                                                         |

| DIO6        | G7 | I/O | デジタル        | GPIO                                                                                                         |

| VDDIO       | F8 | —   | 電源          | 1.71V ~ 3.63V 分割レール I/O 電源                                                                                   |

| DIO7        | G8 | I/O | デジタル        | GPIO                                                                                                         |

| DIO8        | H8 | I/O | デジタル        | GPIO                                                                                                         |

| DIO9_SWDIO  | H7 | I/O | デジタル        | GPIO、SWD インターフェイス: モード選択または SWDIO、高駆動機能                                                                      |

| DIO10_SWDCK | H6 | I/O | デジタル        | GPIO、SWD インターフェイス: クロック、高駆動機能                                                                                |

| DIO11       | G6 | I/O | デジタル        | GPIO、高駆動能力                                                                                                   |

| DIO12       | F5 | I/O | デジタル        | GPIO、高駆動能力                                                                                                   |

| DIO13       | G5 | I/O | デジタル        | GPIO                                                                                                         |

| DIO14       | H5 | I/O | デジタル        | GPIO                                                                                                         |

| DIO15       | F4 | I/O | デジタル        | GPIO                                                                                                         |

| DIO16       | G4 | I/O | デジタル        | GPIO                                                                                                         |

| VDDIO       | H4 | —   | 電源          | 1.71V ~ 3.63V 分割レール I/O 電源                                                                                   |

| VDDS        | H3 | —   | 電源          | 1.71V ~ 3.63V を供給                                                                                            |

| VDDS        | G1 | —   | 電源          | 1.71V ~ 3.63V を供給                                                                                            |

| DIO17_A8    | G3 | I/O | デジタルまたはアナログ | GPIO、アナログ能力、高駆動能力                                                                                            |

| DIO18_A7    | F3 | I/O | デジタルまたはアナログ | GPIO、アナログ能力、高駆動能力                                                                                            |

| DIO19_A6    | H2 | I/O | デジタルまたはアナログ | GPIO、アナログ機能                                                                                                  |

| DIO20_A5    | G2 | I/O | デジタルまたはアナログ | GPIO、アナログ機能                                                                                                  |

| DIO21_A4    | F2 | I/O | デジタルまたはアナログ | GPIO、アナログ機能                                                                                                  |

| DIO22_A3    | E2 | I/O | デジタルまたはアナログ | GPIO、アナログ機能                                                                                                  |

| RSTN        | H1 | I   | デジタル        | リセット入力、アクティブ Low 内部プルアップ抵抗なし                                                                                 |

| DIO23_X32P  | F1 | I/O | デジタルまたはアナログ | GPIO、32kHz 水晶発振器ピン 1、オプションの TCXO 入力                                                                          |

| DIO24_X32N  | E1 | I/O | デジタルまたはアナログ | GPIO、32kHz 水晶発振器ピン 2                                                                                         |

| DIO25_A2    | D3 | I/O | デジタル        | GPIO                                                                                                         |

| DIO26       | D2 | I/O | デジタル        | GPIO                                                                                                         |

| DIO29_A10   | B4 | I/O | デジタル        | GPIO                                                                                                         |

| DIO30_A9    | B5 | I/O | デジタル        | GPIO                                                                                                         |

| VDDD        | D1 | —   | 電源          | 内部 1.28V レギュレーション済みコア電源のデカップリング用。外部 1 $\mu$ F デカップリング コンデンサを接続します。 <a href="#">(1)</a>                       |

| VDDS        | C1 | —   | 電源          | 1.71V ~ 3.63V 電源。外部 10 $\mu$ F デカップリング コンデンサを接続します。                                                          |

| DCDC_SW     | B1 | —   | 電源          | 内部 DC/DC コンバータのスイッチング ノード                                                                                    |

| VDDS        | A1 | —   | 電源          | 1.71V ~ 3.63V を供給                                                                                            |

| VDDS        | A3 | —   | 電源          | 1.71V ~ 3.63V を供給                                                                                            |

| DIO27_A1    | B2 | I/O | デジタルまたはアナログ | GPIO、アナログ機能                                                                                                  |

| DIO28_A0    | B3 | I/O | デジタルまたはアナログ | GPIO、アナログ機能                                                                                                  |

**表 6-4. 信号の説明 - YCJ パッケージ プレビュー (続き)**

| ピン   |    | I/O | タイプ  | 説明                                                                                                             |

|------|----|-----|------|----------------------------------------------------------------------------------------------------------------|

| 名称   | 番号 |     |      |                                                                                                                |

| VDDR | A2 | —   | 電源   | 内部電源には、内部 DC/DC コンバータまたは内部 LDO から電源を供給する必要があります。外部 $10\mu\text{F}$ デカップリング コンデンサを接続します。 <sup>(1) (2) (3)</sup> |

| X48P | A4 | —   | アナログ | 48MHz 水晶発振器ピン 1                                                                                                |

| X48N | A5 | —   | アナログ | 48MHz 水晶発振器ピン 2                                                                                                |

| VDDS | A6 | —   | 電源   | 1.71V ~ 3.63V を供給                                                                                              |

| ANT  | A7 | I/O | RF   | 2.4GHz TX, RX                                                                                                  |

| GND  | E3 | —   | GND  | グランド                                                                                                           |

| GND  | E4 | —   | GND  | グランド                                                                                                           |

| GND  | E5 | —   | GND  | グランド                                                                                                           |

| GND  | E6 | —   | GND  | グランド                                                                                                           |

| GND  | D4 | —   | GND  | グランド                                                                                                           |

| GND  | D5 | —   | GND  | グランド                                                                                                           |

| GND  | D8 | —   | GND  | グランド                                                                                                           |

| GND  | C2 | —   | GND  | グランド                                                                                                           |

| GND  | C3 | —   | GND  | グランド                                                                                                           |

| GND  | C4 | —   | GND  | グランド                                                                                                           |

| GND  | C5 | —   | GND  | グランド                                                                                                           |

| GND  | C6 | —   | GND  | グランド                                                                                                           |

| GND  | C7 | —   | GND  | グランド                                                                                                           |

| GND  | B6 | —   | GND  | グランド                                                                                                           |

| GND  | B7 | —   | GND  | グランド                                                                                                           |

(1) VDDR ピンは、PCB 上で互いに接続する必要があります。

(2) 内部 DC/DC および LDO からの出力は、1.5V に調整されています。

(3) 詳細については、「ドキュメント サポート」に記載されている『テクニカル リファレンス マニュアル』を参照してください。

## 6.3 未使用ピンおよびモジュールの接続

### 6.3.1 未使用ピンおよびモジュールの接続 - RHA パッケージ

**表 6-5. 未使用ピンの接続 - RHA パッケージ**

| 機能                         | 信号名         | ピン番号               | 許容される処置 <sup>(1)</sup> | 好ましい方法 <sup>(1)</sup> |

|----------------------------|-------------|--------------------|------------------------|-----------------------|

| GPIO (デジタル)                | DION        | 3–8<br>10<br>13–16 | NC、GND、または VDDS        | NC                    |

| SWD                        | DIO9_SWDIO  | 11                 | NC、GND、または VDDS        | NC <sup>(3)</sup>     |

|                            | DIO10_SWDCK | 12                 | NC、GND、または VDDS        | NC <sup>(4)</sup>     |

| GPIO (デジタルまたはアナログ)         | DION_Am     | 19–24<br>32–33     | NC、GND、または VDDS        | NC                    |

| 32.768kHz の水晶振動子           | DIO23_X32P  | 26                 | NC または GND             | NC                    |

|                            | DIO24_X32N  | 27                 |                        |                       |

| DC/DC コンバータ <sup>(2)</sup> | DCDC        | 30                 | NC                     | NC                    |

|                            | VDDS        | 18、29、31、38        | VDDS                   | VDDS                  |

| 分割レール I/O 電源               | VDDIO       | 9、17               | VDDS                   | VDDS                  |

(1) NC = 接続なし

(2) DC/DC コンバータを使用しない場合は、DCDC と VDDR の間のインダクタを取り除くことができます。VDDR は必ず接続したままにしてください。また  $10\mu\text{F}$  のデカップリング コンデンサは必ず VDDR ネットに配置したままにしてください。

(3) デフォルトでは、SWDIO で内部プルアップが有効になっています。

(4) デフォルトでは、SWDCK の内部プルダウンが有効になっています。

### 6.3.2 未使用ピンおよびモジュールの接続 - YCJ パッケージ

表 6-6. 未使用ピンの接続 - RKP パッケージ

| 機能                         | 信号名         | ピン番号                                                  | 許容される処置 <sup>(1)</sup> | 好ましい方法 <sup>(1)</sup> |

|----------------------------|-------------|-------------------------------------------------------|------------------------|-----------------------|

| GPIO (デジタル)                | DION        | D7、D6、E8、E7、F6、F7、G8、H7、H6、G6、F5、F4、G4、G7、H8、G5、H5、D2 | NC、GND、または VDDS        | NC                    |

| SWD                        | DIO9_SWDIO  | H7                                                    | NC、GND、または VDDS        | GND または VDD           |

|                            | DIO10_SWDCK | H6                                                    | NC、GND、または VDDS        | GND または VDD           |

| GPIO (デジタルまたはアナログ)         | DION_Am     | G3、F3、H2、G2、F2、E2、B2、B3、D3、B4、B5                      | NC、GND、または VDDS        | NC                    |

| 32.768-kHz 水晶振動子           | DIO23_X32P  | F1                                                    | NC または GND             | NC                    |

|                            | DIO24_X32N  | E1                                                    |                        |                       |

| DC/DC コンバータ <sup>(2)</sup> | DCDC_SW     | B1                                                    | NC                     | NC                    |

|                            | VDDS        | H3、G1、C1、A1、A3、A6                                     | VDDS                   | VDDS                  |

| 分割レール I/O 電源               | VDDIO       | F8、H4                                                 | VDDS                   | VDDS                  |

(1) NC = 接続なし

(2) DC/DC コンバータを使用しない場合は、DCDC と VDDR の間のインダクタを取り除くことができます。VDDR は引き続き接続し、10 $\mu$ F DCDC コンデンサを VDDR ネットに維持する必要があります。

## 6.4 ペリフェラル ピン割り当て

### 6.4.1 RHA ペリフェラル ピン割り当て

表 6-7. RHA (QFN40) ペリフェラル ピン割り当て

| ピン番号  | ピン名  | 信号名      | 信号のタイプ <sup>(1)</sup> | PIN MUX エンコード | 信号の方向 |

|-------|------|----------|-----------------------|---------------|-------|

| QFN40 |      |          |                       |               |       |

| 1     | VDDR | VDDR     | —                     | 該当なし          | 該当なし  |

| 2     | VDDR | VDDR     | —                     | 該当なし          | 該当なし  |

| 3     | DIO0 | GPIO0    | I/O                   | 0             | I/O   |

|       |      | T0C0     |                       | 1             | I/O   |

|       |      | T1F      |                       | 2             | O     |

|       |      | T3C0N    |                       | 3             | O     |

|       |      | LPC0     |                       | 4             | O     |

|       |      | T1C0     |                       | 5             | I/O   |

| 4     | DIO1 | GPIO1    | I/O                   | 0             | I/O   |

|       |      | T1C0     |                       | 2             | I/O   |

|       |      | T2C0     |                       | 3             | I/O   |

|       |      | UART0TXD |                       | 4             | O     |

|       |      | T1C1     |                       | 5             | I/O   |

|       |      | DTB15    |                       | 7             | O     |

**表 6-7. RHA (QFN40) ペリフェラル ピン割り当て (続き)**

| ピン番号 | ピン名        | 信号名      | 信号のタイプ <sup>(1)</sup> | PIN MUX エンコード | 信号の方向 |

|------|------------|----------|-----------------------|---------------|-------|

|      |            | QFN40    |                       |               |       |

| 5    | DIO2       | GPIO2    | I/O                   | 0             | I/O   |

|      |            | T1C1     |                       | 2             | I/O   |

|      |            | T0PE     |                       | 3             | O     |

|      |            | UART0RXD |                       | 4             | I     |

|      |            | T1C2     |                       | 5             | I/O   |

|      |            | DTB14    |                       | 7             | O     |

| 6    | DIO3       | GPIO3    | I/O                   | 0             | I/O   |

|      |            | SPI0SCLK |                       | 1             | I/O   |

|      |            | I2S0SCLK |                       | 2             | I/O   |

|      |            | T2PE     |                       | 3             | O     |

|      |            | UART1TXD |                       | 4             | O     |

|      |            | T2C0     |                       | 5             | I/O   |

|      |            | DTB13    |                       | 7             | O     |

| 7    | DIO4       | GPIO4    | I/O                   | 0             | I/O   |

|      |            | SPI0PICO |                       | 1             | I/O   |

|      |            | SPI0POCI |                       | 2             | I/O   |

|      |            | T1C2     |                       | 3             | I/O   |

|      |            | UART1RXD |                       | 4             | I     |

|      |            | T2C1     |                       | 5             | I/O   |

|      |            | DTB12    |                       | 7             | O     |

| 8    | DIO5       | GPIO5    | I/O                   | 0             | I/O   |

|      |            | SPI0POCI |                       | 1             | I/O   |

|      |            | SPI0PICO |                       | 2             | I/O   |

|      |            | T2C1     |                       | 3             | I/O   |

|      |            | T3C1N    |                       | 4             | O     |

|      |            | T2C2     |                       | 5             | I/O   |

|      |            | DTB11    |                       | 7             | O     |

| 9    | VDDIO      | VDDIO    | —                     | 該当なし          | 該当なし  |

| 10   | DIO7       | GPIO7    | I/O                   | 0             | I/O   |

|      |            | SPI0CSN  |                       | 1             | I/O   |

|      |            | T2C2     |                       | 2             | I/O   |

|      |            | I2S0WS   |                       | 3             | I/O   |

|      |            | T3C2N    |                       | 4             | O     |

|      |            | DTB10    |                       | 7             | O     |

| 11   | DIO9_SWDIO | GPIO9    | I/O                   | 0             | I/O   |

|      |            | T0C1     |                       | 1             | I/O   |

|      |            | T2C0N    |                       | 2             | O     |

|      |            | I2S0SD0  |                       | 3             | I/O   |

|      |            | T0PE     |                       | 4             | O     |

|      |            | I2C0SCL  |                       | 5             | I/O   |

表 6-7. RHA (QFN40) ペリフェラル ピン割り当て (続き)

| ピン番号 | ピン名         | 信号名      | 信号のタイプ <sup>(1)</sup> | PIN MUX エンコード | 信号の方向 |

|------|-------------|----------|-----------------------|---------------|-------|

|      |             | QFN40    |                       |               |       |

| 12   | DIO10_SWDCK | GPIO10   | I/O                   | 0             | I/O   |

|      |             | T0C2     |                       | 1             | I/O   |

|      |             | T2C1N    |                       | 2             | O     |

|      |             | I2S0SD1  |                       | 3             | I/O   |

|      |             | T2PE     |                       | 4             | O     |

|      |             | I2C0SDA  |                       | 5             | I/O   |

| 13   | DIO11       | GPIO11   | I/O                   | 0             | I/O   |

|      |             | SPI1POCI |                       | 1             | I/O   |

|      |             | SPI1PICO |                       | 2             | I/O   |

|      |             | SWO      |                       | 3             | O     |

|      |             | T3C0     |                       | 4             | I/O   |

|      |             | T1F      |                       | 5             | O     |

|      |             | DTB9     |                       | 7             | O     |

| 14   | DIO12       | GPIO12   | I/O                   | 0             | I/O   |

|      |             | SPI1PICO |                       | 1             | I/O   |

|      |             | SPI1POCI |                       | 2             | I/O   |

|      |             | T2C2N    |                       | 3             | O     |

|      |             | T3C1     |                       | 4             | I/O   |

|      |             | T3C2     |                       | 5             | I/O   |

|      |             | DTB8     |                       | 7             | O     |

| 15   | DIO15       | GPIO15   | I/O                   | 0             | I/O   |

|      |             | SPI1SCLK |                       | 1             | I/O   |

|      |             | T3C2     |                       | 2             | I/O   |

|      |             | T1C0N    |                       | 3             | O     |

|      |             | LPCO     |                       | 4             | O     |

|      |             | T3C1     |                       | 5             | I/O   |

| 16   | DIO16       | GPIO16   | I/O                   | 0             | I/O   |

|      |             | I2S0MCLK |                       | 1             | O     |

|      |             | SPI1CSN  |                       | 2             | I/O   |

|      |             | EXTCI    |                       | 3             | I     |

|      |             | T1F      |                       | 4             | I     |

|      |             | T3C0     |                       | 5             | I/O   |

|      |             | DTB7     |                       | 7             | O     |

| 17   | VDDIO       | VDDIO    | —                     | 該当なし          | 該当なし  |

| 18   | VDDS        | VDDS     | —                     | 該当なし          | 該当なし  |

| 19   | DIO17_A8    | GPIO17   | I/O                   | 0             | I/O   |

|      |             | I2S0SCLK |                       | 1             | I/O   |

|      |             | UART0RTS |                       | 2             | O     |

|      |             | T0C0     |                       | 4             | I/O   |

|      |             | LRFDO    |                       | 5             | O     |

|      |             | ADC8     |                       | 6             | I     |

|      |             | DTB6     |                       | 7             | O     |

**表 6-7. RHA (QFN40) ペリフェラル ピン割り当て (続き)**

| ピン番号 | ピン名      | 信号名            | 信号のタイプ <sup>(1)</sup> | PIN MUX エンコード | 信号の方向 |

|------|----------|----------------|-----------------------|---------------|-------|

|      |          | QFN40          |                       |               |       |

| 20   | DIO18_A7 | GPIO18         | I/O                   | 0             | I/O   |

|      |          | I2S0WS         |                       | 1             | I/O   |

|      |          | UART0CTS       |                       | 2             | I     |

|      |          | T0C1           |                       | 4             | I/O   |

|      |          | LRFD1          |                       | 5             | O     |

|      |          | ADC7           |                       | 6             | I     |

|      |          | DTB5           |                       | 7             | O     |

| 21   | DIO19_A6 | GPIO19         | I/O                   | 0             | I/O   |

|      |          | SPI0CSN        |                       | 1             | I/O   |

|      |          | UART0TXD       |                       | 2             | O     |

|      |          | UART0RXD       |                       | 3             | I     |

|      |          | I2S0SD0        |                       | 4             | I/O   |

|      |          | LRFD2          |                       | 5             | O     |

|      |          | ADC6/LPC+      |                       | 6             | I     |

|      |          | DTB4           |                       | 7             | O     |

| 22   | DIO20_A6 | GPIO20         | I/O                   | 0             | I/O   |

|      |          | SPI0SCLK       |                       | 1             | I/O   |

|      |          | UART0RXD       |                       | 2             | I     |

|      |          | UART0TXD       |                       | 3             | O     |

|      |          | I2S0SD1        |                       | 4             | I/O   |

|      |          | LRFD3          |                       | 5             | O     |

|      |          | ADC5/LPC+/LPC- |                       | 6             | I     |

|      |          | DTB3           |                       | 7             | O     |

| 23   | DIO21_A4 | GPIO21         | I/O                   | 0             | I/O   |

|      |          | SPI0PICO       |                       | 1             | I/O   |

|      |          | UART1TXD       |                       | 2             | O     |

|      |          | I2C0SCL        |                       | 3             | I/O   |

|      |          | T1C1N          |                       | 4             | O     |

|      |          | LRFD4          |                       | 5             | O     |

|      |          | ADC4/LPC+/LPC- |                       | 6             | I     |

|      |          | DTB2           |                       | 7             | O     |

| 24   | DIO22_A3 | GPIO22         | I/O                   | 0             | I/O   |

|      |          | SPI0POCI       |                       | 1             | I/O   |

|      |          | UART1RXD       |                       | 2             | I     |

|      |          | I2C0SDA        |                       | 3             | I/O   |

|      |          | T1C2N          |                       | 4             | O     |

|      |          | LRFD5          |                       | 5             | O     |

|      |          | ADC3           |                       | 6             | I     |

|      |          | DTB1           |                       | 7             | O     |

| 25   | RTSN     | RSTN           | —                     | 該当なし          | 該当なし  |

表 6-7. RHA (QFN40) ペリフェラル ピン割り当て (続き)

| ピン番号 | ピン名        | 信号名        | 信号のタイプ <sup>(1)</sup> | PIN MUX エンコード | 信号の方向 |

|------|------------|------------|-----------------------|---------------|-------|

|      |            | QFN40      |                       |               |       |

| 26   | DIO23_X32P | GPIO23     | I/O                   | 0             | I/O   |

|      |            | SPI1CSN    |                       | 1             | I/O   |

|      |            | UART1RTS   |                       | 2             | O     |

|      |            | LFCI       |                       | 3             | I     |

|      |            | T0C2       |                       | 4             | I/O   |

|      |            | T1C0       |                       | 5             | I/O   |

|      |            | LFXT_P     |                       | 6             | I     |

| 27   | DIO24_X32N | GPIO24     | I/O                   | 0             | I/O   |

|      |            | SPI1SCLK   |                       | 1             | I/O   |

|      |            | UART1CTS   |                       | 2             | I     |

|      |            | T0C0N      |                       | 3             | O     |

|      |            | LPCO       |                       | 4             | O     |

|      |            | T0C0       |                       | 5             | I/O   |

|      |            | LFXT_N     |                       | 6             | I     |

| 28   | VDDD       | VDDD       | —                     | 該当なし          | 該当なし  |

| 29   | VDDS       | VDDS       | —                     | 該当なし          | 該当なし  |

| 30   | DCDC       | DCDC       | —                     | 該当なし          | 該当なし  |

| 31   | VDDS       | VDDS       | —                     | 該当なし          | 該当なし  |

| 32   | DIO27_A1   | GPIO27     | I/O                   | 0             | I/O   |

|      |            | SPI1PICO   |                       | 1             | I/O   |

|      |            | I2C0SCL    |                       | 2             | I/O   |

|      |            | CKMIN      |                       | 3             | I     |

|      |            | T0C1N      |                       | 4             | O     |

|      |            | LRFD6      |                       | 5             | O     |

|      |            | ADC1/AREF+ |                       | 6             | I     |

|      |            | DTB0       |                       | 7             | O     |

| 33   | DIO28_A0   | GPIO28     | I/O                   | 0             | I/O   |

|      |            | SPI1POCI   |                       | 1             | I/O   |

|      |            | I2C0SDA    |                       | 2             | I/O   |

|      |            | T3C0N      |                       | 3             | O     |

|      |            | T0C2N      |                       | 4             | O     |

|      |            | LRFD7      |                       | 5             | O     |

|      |            | ADC0/AREF- |                       | 6             | I     |

| 34   | VDDR       | VDDR       | —                     | 該当なし          | 該当なし  |

| 35   | X48P       | X48P       | —                     | 該当なし          | 該当なし  |

| 36   | X48N       | X48N       | —                     | 該当なし          | 該当なし  |

| 37   | NC         | NC         | —                     | 該当なし          | 該当なし  |

| 38   | VDDS       | VDDS       | —                     | 該当なし          | 該当なし  |

| 39   | ANT        | ANT        | —                     | 該当なし          | 該当なし  |

| 40   | NC         | NC         | —                     | 該当なし          | 該当なし  |

| —    | EGP        | GND        | —                     | 該当なし          | 該当なし  |

(1) 信号タイプ:I = 入力、O = 出力、I/O = 入力または出力。

### 6.4.2 YCJ ペリフェラル ピン割り当て

**表 6-8. YCJ (WCSP) ペリフェラル ピン割り当てプレビュー**

| ピン番号<br>WCSP | ピン名  | 信号名      | 信号のタイプ <sup>(1)</sup> | PIN MUX エンコード | 信号の方向 |

|--------------|------|----------|-----------------------|---------------|-------|

| C8           | VDDR | VDDR     | —                     | 該当なし          | 該当なし  |

| D7           | DIO0 | GPIO0    | I/O                   | 0             | I/O   |

|              |      | T0C0     |                       | 1             | I/O   |

|              |      | T1F      |                       | 2             | O     |

|              |      | T3C0N    |                       | 3             | O     |

|              |      | LPC0     |                       | 4             | O     |

|              |      | T1C0     |                       | 5             | I/O   |

| D6           | DIO1 | GPIO1    | I/O                   | 0             | I/O   |

|              |      | T1C0     |                       | 2             | I/O   |

|              |      | T2C0     |                       | 3             | I/O   |

|              |      | UART0TXD |                       | 4             | O     |

|              |      | T1C1     |                       | 5             | I/O   |

|              |      | DTB15    |                       | 7             | O     |

| E8           | DIO2 | GPIO2    | I/O                   | 0             | I/O   |

|              |      | T1C1     |                       | 2             | I/O   |

|              |      | T0PE     |                       | 3             | O     |

|              |      | UART0RXD |                       | 4             | I     |

|              |      | T1C2     |                       | 5             | I/O   |

|              |      | DTB14    |                       | 7             | O     |

| E7           | DIO3 | GPIO3    | I/O                   | 0             | I/O   |

|              |      | SPI0SCLK |                       | 1             | I/O   |

|              |      | I2S0SCLK |                       | 2             | I/O   |

|              |      | T2PE     |                       | 3             | O     |

|              |      | UART1TXD |                       | 4             | O     |

|              |      | T2C0     |                       | 5             | I/O   |

| F6           | DIO4 | DTB13    | I/O                   | 7             | O     |

|              |      | GPIO4    |                       | 0             | I/O   |

|              |      | SPI0PICO |                       | 1             | I/O   |

|              |      | SPI0POCI |                       | 2             | I/O   |

|              |      | T1C2     |                       | 3             | I/O   |

|              |      | UART1RXD |                       | 4             | I     |

| F7           | DIO5 | T2C1     | I/O                   | 5             | I/O   |

|              |      | DTB12    |                       | 7             | O     |

|              |      | GPIO5    |                       | 0             | I/O   |

|              |      | SPI0POCI |                       | 1             | I/O   |

|              |      | SPI0PICO |                       | 2             | I/O   |

|              |      | T2C1     |                       | 3             | I/O   |

表 6-8. YCJ (WCSP) ペリフェラル ピン割り当てプレビュー (続き)

| ピン番号 | ピン名         | 信号名      | 信号のタイプ <sup>(1)</sup> | PIN MUX エンコード | 信号の方向 |

|------|-------------|----------|-----------------------|---------------|-------|

| WCSP |             |          |                       |               |       |

| G7   | DIO6        | GPIO6    | I/O                   | 0             | I/O   |

|      |             | I2S0MCLK |                       | 1             | I/O   |

|      |             | T0C0N    |                       | 2             | I/O   |

|      |             | T1F      |                       | 3             | I     |

|      |             | LPC0     |                       | 4             | O     |

| F8   | VDDIO       | VDDIO    | —                     | 該当なし          | 該当なし  |

| G8   | DIO7        | GPIO7    | I/O                   | 0             | I/O   |

|      |             | SPI0CSN  |                       | 1             | I/O   |

|      |             | T2C2     |                       | 2             | I/O   |

|      |             | I2S0WS   |                       | 3             | I/O   |

|      |             | T3C2N    |                       | 4             | O     |

|      |             | DTB10    |                       | 7             | O     |

| H8   | DIO8        | GPIO8    | I/O                   | 0             | I/O   |

|      |             | SPI1SCLK |                       | 1             | I/O   |

|      |             | T3C2     |                       | 2             | I/O   |

|      |             | T1C0N    |                       | 3             | I     |

|      |             | LPC0     |                       | 4             | O     |

|      |             | T3C1     |                       | 5             | O     |

| H7   | DIO9_SWDIO  | GPIO9    | I/O                   | 0             | I/O   |

|      |             | T0C1     |                       | 1             | I/O   |

|      |             | T2C0N    |                       | 2             | O     |

|      |             | I2S0SD0  |                       | 3             | I/O   |

|      |             | T0PE     |                       | 4             | O     |

|      |             | I2C0SCL  |                       | 5             | I/O   |

| H6   | DIO10_SWDCK | GPIO10   | I/O                   | 0             | I/O   |

|      |             | T0C2     |                       | 1             | I/O   |

|      |             | T2C1N    |                       | 2             | O     |

|      |             | I2S0SD1  |                       | 3             | I/O   |

|      |             | T2PE     |                       | 4             | O     |

|      |             | I2C0SDA  |                       | 5             | I/O   |

| G6   | DIO11       | GPIO11   | I/O                   | 0             | I/O   |

|      |             | SPI1POCI |                       | 1             | I/O   |

|      |             | SPI1PICO |                       | 2             | I/O   |

|      |             | SWO      |                       | 3             | O     |

|      |             | T3C0     |                       | 4             | I/O   |

|      |             | T1F      |                       | 5             | O     |

|      |             | DTB9     |                       | 7             | O     |

| F5   | DIO12       | GPIO12   | I/O                   | 0             | I/O   |

|      |             | SPI1PICO |                       | 1             | I/O   |

|      |             | SPI1POCI |                       | 2             | I/O   |

|      |             | T2C2N    |                       | 3             | O     |

|      |             | T3C1     |                       | 4             | I/O   |

|      |             | T3C2     |                       | 5             | I/O   |

|      |             | DTB8     |                       | 7             | O     |

**表 6-8. YCJ (WCSP) ペリフェラル ピン割り当てプレビュー (続き)**

| ピン番号<br>WCSP | ピン名      | 信号名      | 信号のタイプ <sup>(1)</sup> | PIN MUX エンコード | 信号の方向 |

|--------------|----------|----------|-----------------------|---------------|-------|

| G5           | DIO13    | GPIO13   | I/O                   | 0             | I/O   |

|              |          | UART0TXD |                       | 2             | I/O   |

|              |          | UART1TXD |                       | 3             | I     |

|              |          | T0C1N    |                       | 4             | O     |

| H5           | DIO14    | GPIO14   | I/O                   | 0             | I/O   |

|              |          | UART0RXD |                       | 2             | I/O   |

|              |          | UART1RXD |                       | 3             | I     |

|              |          | T0C2N    |                       | 4             | O     |

| F4           | DIO15    | GPIO15   | I/O                   | 0             | I/O   |

|              |          | SPI1SCLK |                       | 1             | I/O   |

|              |          | T3C2     |                       | 2             | I/O   |

|              |          | T1C0N    |                       | 3             | O     |

|              |          | LPCO     |                       | 4             | O     |

|              |          | T3C1     |                       | 5             | I/O   |

| G4           | DIO16    | GPIO16   | I/O                   | 0             | I/O   |

|              |          | I2S0MCLK |                       | 1             | O     |

|              |          | SPI1CSN  |                       | 2             | I/O   |

|              |          | EXTCI    |                       | 3             | I     |

|              |          | T1F      |                       | 4             | I     |

|              |          | T3C0     |                       | 5             | I/O   |

|              |          | DTB7     |                       | 7             | O     |

| H4           | VDDIO    | VDDIO    | —                     | 該当なし          | 該当なし  |

| H3           | VDDS     | VDDS     | —                     | 該当なし          | 該当なし  |

| G1           | VDDS     | VDDS     | —                     | 該当なし          | 該当なし  |

| G3           | DIO17_A8 | GPIO17   | I/O                   | 0             | I/O   |

|              |          | I2S0SCLK |                       | 1             | I/O   |

|              |          | UART0RTS |                       | 2             | O     |

|              |          | T0C0     |                       | 4             | I/O   |

|              |          | LRFD0    |                       | 5             | O     |

|              |          | ADC8     |                       | 6             | I     |

|              |          | DTB6     |                       | 7             | O     |

| F3           | DIO18_A7 | GPIO18   | I/O                   | 0             | I/O   |

|              |          | I2S0WS   |                       | 1             | I/O   |

|              |          | UART0CTS |                       | 2             | I     |

|              |          | T0C1     |                       | 4             | I/O   |

|              |          | LRFD1    |                       | 5             | O     |

|              |          | ADC7     |                       | 6             | I     |

|              |          | DTB5     |                       | 7             | O     |

表 6-8. YCJ (WCSP) ペリフェラル ピン割り当てプレビュー (続き)

| ピン番号<br>WCSP | ピン名        | 信号名            | 信号のタイプ <sup>(1)</sup> | PIN MUX エンコード | 信号の方向 |

|--------------|------------|----------------|-----------------------|---------------|-------|

| H2           | DIO19_A6   | GPIO19         | I/O                   | 0             | I/O   |

|              |            | SPI0CSN        |                       | 1             | I/O   |

|              |            | UART0TXD       |                       | 2             | O     |

|              |            | UART0RXD       |                       | 3             | I     |

|              |            | I2S0SD0        |                       | 4             | I/O   |

|              |            | LRFD2          |                       | 5             | O     |

|              |            | ADC6/LPC+      |                       | 6             | I     |

|              |            | DTB4           |                       | 7             | O     |

| G2           | DIO20_A5   | GPIO20         | I/O                   | 0             | I/O   |

|              |            | SPI0SCLK       |                       | 1             | I/O   |

|              |            | UART0RXD       |                       | 2             | I     |

|              |            | UART0TXD       |                       | 3             | O     |

|              |            | I2S0SD1        |                       | 4             | I/O   |

|              |            | LRFD3          |                       | 5             | O     |

|              |            | ADC5/LPC+/LPC- |                       | 6             | I     |

|              |            | DTB3           |                       | 7             | O     |

| F2           | DIO21_A4   | GPIO21         | I/O                   | 0             | I/O   |

|              |            | SPI0PICO       |                       | 1             | I/O   |

|              |            | UART1TXD       |                       | 2             | O     |

|              |            | I2C0SCL        |                       | 3             | I/O   |

|              |            | T1C1N          |                       | 4             | O     |

|              |            | LRFD4          |                       | 5             | O     |

|              |            | ADC4/LPC+/LPC- |                       | 6             | I     |

|              |            | DTB2           |                       | 7             | O     |

| E2           | DIO22_A3   | GPIO22         | I/O                   | 0             | I/O   |

|              |            | SPI0POCI       |                       | 1             | I/O   |

|              |            | UART1RXD       |                       | 2             | I     |

|              |            | I2C0SDA        |                       | 3             | I/O   |

|              |            | T1C2N          |                       | 4             | O     |

|              |            | LRFD5          |                       | 5             | O     |

|              |            | ADC3           |                       | 6             | I     |

|              |            | DTB1           |                       | 7             | O     |

| H1           | RTSN       | RSTN           | —                     | 該当なし          | 該当なし  |

| F1           | DIO23_X32P | GPIO23         | I/O                   | 0             | I/O   |

|              |            | SPI1CSN        |                       | 1             | I/O   |

|              |            | UART1RTS       |                       | 2             | O     |

|              |            | LFCI           |                       | 3             | I     |

|              |            | T0C2           |                       | 4             | I/O   |

|              |            | T1C0           |                       | 5             | I/O   |

|              |            | LFXT_P         |                       | 6             | I     |

**表 6-8. YCJ (WCSP) ペリフェラル ピン割り当てプレビュー (続き)**

| ピン番号<br>WCSP | ピン名        | 信号名        | 信号のタイプ <sup>(1)</sup> | PIN MUX エンコード | 信号の方向 |

|--------------|------------|------------|-----------------------|---------------|-------|

| E1           | DIO24_X32N | GPIO24     | I/O                   | 0             | I/O   |

|              |            | SPI1SCLK   |                       | 1             | I/O   |

|              |            | UART1CTS   |                       | 2             | I     |

|              |            | T0C0N      |                       | 3             | O     |

|              |            | LPCO       |                       | 4             | O     |

|              |            | T0C0       |                       | 5             | I/O   |

|              |            | LFXT_N     |                       | 6             | I     |

| D3           | DIO25_A2   | GPIO25     | I/O                   | 0             | I/O   |

|              |            | SPI0CSN    |                       | 1             | I/O   |

|              |            | SPI1SCLK   |                       | 2             | I/O   |

|              |            | I2C0SCL    |                       | 3             | I     |

|              |            | I2S0SCLK   |                       | 4             | O     |

|              |            | T1C0N      |                       | 5             | O     |

|              |            | ADC2       |                       | 6             | I     |

| D2           | DIO26      | GPIO26     | I/O                   | 0             | I/O   |

|              |            | SPI0POCI   |                       | 1             | I/O   |

|              |            | SPI1PICO   |                       | 2             | I/O   |

|              |            | I2C0SDA    |                       | 3             | I     |

|              |            | I2S0WS     |                       | 4             | O     |

|              |            | T1C1N      |                       | 5             | O     |

| D1           | VDDD       | VDDD       | —                     | 該当なし          | 該当なし  |

| C1           | VDDS       | VDDS       | —                     | 該当なし          | 該当なし  |

| B1           | DCDC       | DCDC       | —                     | 該当なし          | 該当なし  |

| A1           | VDDS       | VDDS       | —                     | 該当なし          | 該当なし  |

| A3           | VDDS       | VDDS       | —                     | 該当なし          | 該当なし  |

| B2           | DIO27_A1   | GPIO27     | I/O                   | 0             | I/O   |

|              |            | SPI1PICO   |                       | 1             | I/O   |

|              |            | I2C0SCL    |                       | 2             | I/O   |

|              |            | CKMIN      |                       | 3             | I     |

|              |            | T0C1N      |                       | 4             | O     |

|              |            | LRFD6      |                       | 5             | O     |

|              |            | ADC1/AREF+ |                       | 6             | I     |

|              |            | DTB0       |                       | 7             | O     |

| B3           | DIO28_A0   | GPIO28     | I/O                   | 0             | I/O   |

|              |            | SPI1POCI   |                       | 1             | I/O   |

|              |            | I2C0SDA    |                       | 2             | I/O   |

|              |            | T3C0N      |                       | 3             | O     |

|              |            | T0C2N      |                       | 4             | O     |

|              |            | LRFD7      |                       | 5             | O     |

|              |            | ADC0/AREF- |                       | 6             | I     |

表 6-8. YCJ (WCSP) ペリフェラル ピン割り当てプレビュー (続き)

| ピン番号<br>WCSP | ピン名       | 信号名      | 信号のタイプ <sup>(1)</sup> | PIN MUX エンコード | 信号の方向 |

|--------------|-----------|----------|-----------------------|---------------|-------|

| B4           | DIO29_A10 | GPIO29   | I/O                   | 0             | I/O   |

|              |           | SPI0SCLK |                       | 1             | I/O   |

|              |           | SPI1CSN  |                       | 2             | I/O   |

|              |           | I2C0SCL  |                       | 3             | I     |

|              |           | I2S0SD0  |                       | 4             | O     |

|              |           | T1C2N    |                       | 5             | O     |

|              |           | ADC10    |                       | 6             | I     |

| B5           | DIO30_A9  | GPIO30   | I/O                   | 0             | I/O   |

|              |           | SPI0PICO |                       | 1             | I/O   |

|              |           | SPI1POCI |                       | 2             | I/O   |

|              |           | I2C0SDA  |                       | 3             | I     |

|              |           | I2S0SD1  |                       | 4             | O     |

|              |           | ADC9     |                       | 6             | I     |

| A2           | VDDR      | VDDR     | —                     | 該当なし          | 該当なし  |

| A4           | X48P      | X48P     | —                     | 該当なし          | 該当なし  |

| A5           | X48N      | X48N     | —                     | 該当なし          | 該当なし  |

| A6           | VDDS      | VDDS     | —                     | 該当なし          | 該当なし  |

| A7           | ANT       | ANT      | —                     | 該当なし          | 該当なし  |

## 6.5 ペリフェラル信号の説明

### 6.5.1 RHA ペリフェラル信号の説明

表 6-9. RHA (QFN40) ペリフェラル信号の説明

| 機能         | 信号名   | ピン番号  | ピンのタイプ | 信号の方向 | 説明                                                       |

|------------|-------|-------|--------|-------|----------------------------------------------------------|

|            |       | QFN40 |        |       |                                                          |

| ADC        | ADC0  | 33    | I/O    | I     | ADC チャネル 0 入力                                            |

|            | ADC1  | 32    |        |       | ADC チャネル 1 入力                                            |

|            | ADC3  | 24    |        |       | ADC チャネル 3 入力                                            |

|            | ADC4  | 23    |        |       | ADC チャネル 4 入力                                            |

|            | ADC5  | 22    |        |       | ADC チャネル 5 入力                                            |

|            | ADC6  | 21    |        |       | ADC チャネル 6 入力                                            |

|            | ADC7  | 20    |        |       | ADC チャネル 7 入力                                            |

|            | ADC8  | 19    |        |       | ADC チャネル 8 入力                                            |

| ADC リファレンス | AREF+ | 32    | I/O    | I     | ADC 外部電圧リファレンス、正端子                                       |

|            | AREF- | 33    |        |       | ADC 外部電圧リファレンス、負端子                                       |

| クロック       | X32P  | 26    | I/O    | I     | 32kHz 水晶発振器ピン 1                                          |

|            | X32N  | 27    | I/O    | I     | 32kHz 水晶発振器ピン 2                                          |

|            | X48P  | 35    | —      | I     | 48MHz 水晶発振器ピン 1、オプションの TCXO 入力                           |

|            | X48N  | 36    | —      | I     | 48MHz 水晶発振器ピン 2                                          |

|            | CKMIN | 32    | I/O    | I     | HFOSC トランシーバー ループ基準クロック入力                                |

|            | LFCI  | 26    | I/O    | I     | 低周波クロック入力 (ピンからの LFXT バイパスクロック) またはオプションの TCXO の GPIO 入力 |

**表 6-9. RHA (QFN40) ペリフェラル信号の説明 (続き)**

| 機能          | 信号名   | ピン番号  | ピンのタイプ | 信号の方向 | 説明               |

|-------------|-------|-------|--------|-------|------------------|

|             |       | QFN40 |        |       |                  |

| コンパレータ      | LPCO  | 3     | I/O    | O     | 低消費電力コンパレータ出力    |

|             |       | 15    |        |       |                  |

|             |       | 27    |        |       |                  |

|             | LPC+  | 21    |        | I     | 低消費電力コンパレータ正入力端子 |

|             |       | 22    |        |       |                  |

|             |       | 23    |        |       |                  |

|             | LPC-  | 22    |        | I     | 低消費電力コンパレータ負入力端子 |

|             |       | 23    |        |       |                  |

| デジタル テスト バス | DTB0  | 32    | I/O    | O     | デジタル テスト バス出力 0  |

|             | DTB1  | 24    |        |       | デジタル テスト バス出力 1  |

|             | DTB2  | 23    |        |       | デジタル テスト バス出力 2  |

|             | DTB3  | 22    |        |       | デジタル テスト バス出力 3  |

|             | DTB4  | 21    |        |       | デジタル テスト バス出力 4  |

|             | DTB5  | 20    |        |       | デジタル テスト バス出力 5  |

|             | DTB6  | 19    |        |       | デジタル テスト バス出力 6  |

|             | DTB7  | 16    |        |       | デジタル テスト バス出力 7  |

|             | DTB8  | 14    |        |       | デジタル テスト バス出力 8  |

|             | DTB9  | 13    |        |       | デジタル テスト バス出力 9  |

|             | DTB10 | 10    |        |       | デジタル テスト バス出力 10 |

|             | DTB11 | 8     |        |       | デジタル テスト バス出力 11 |

|             | DTB12 | 7     |        |       | デジタル テスト バス出力 12 |

|             | DTB13 | 6     |        |       | デジタル テスト バス出力 13 |

|             | DTB14 | 5     |        |       | デジタル テスト バス出力 14 |

|             | DTB15 | 4     |        |       | デジタル テスト バス出力 15 |

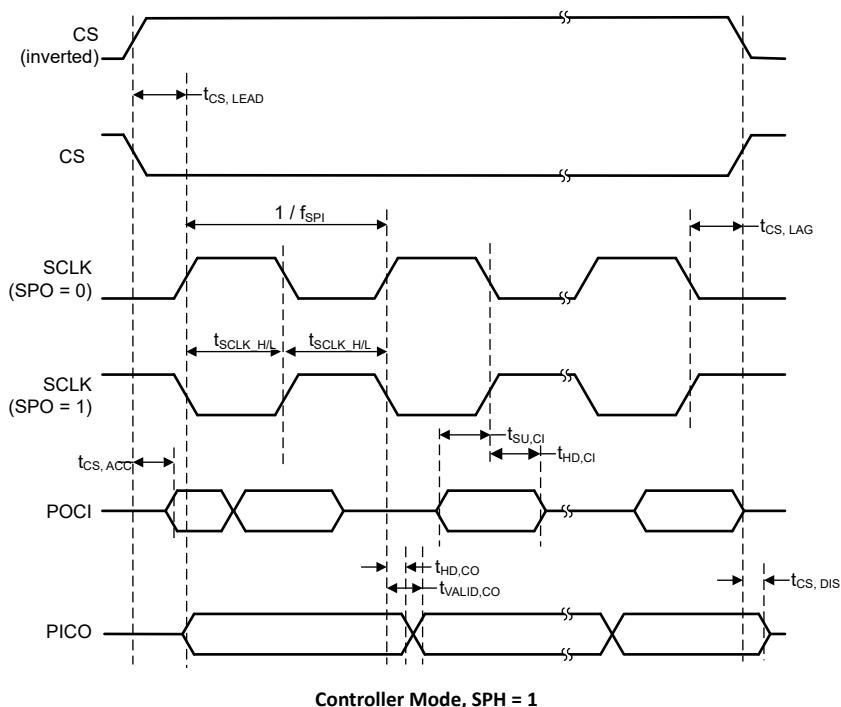

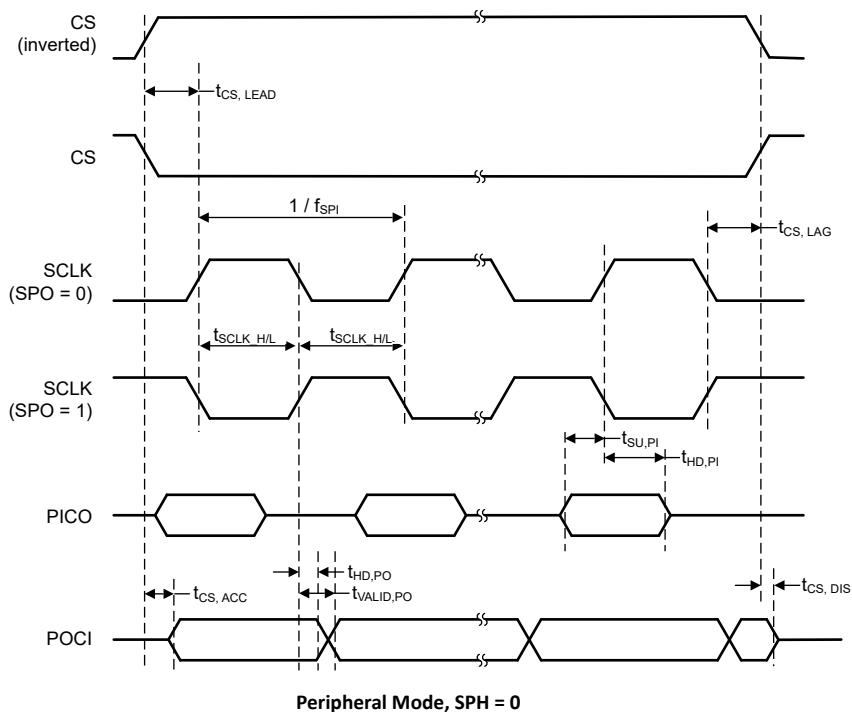

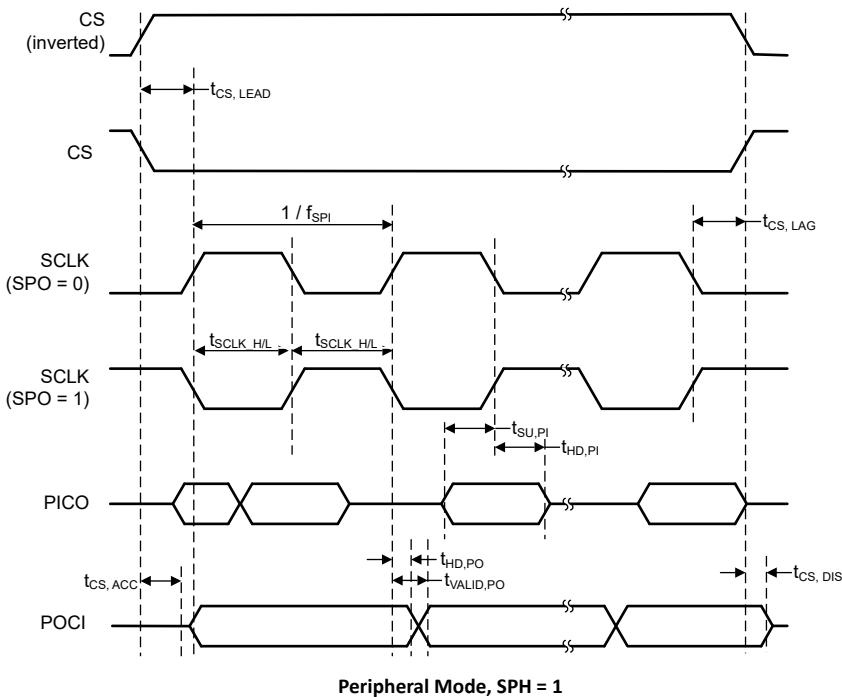

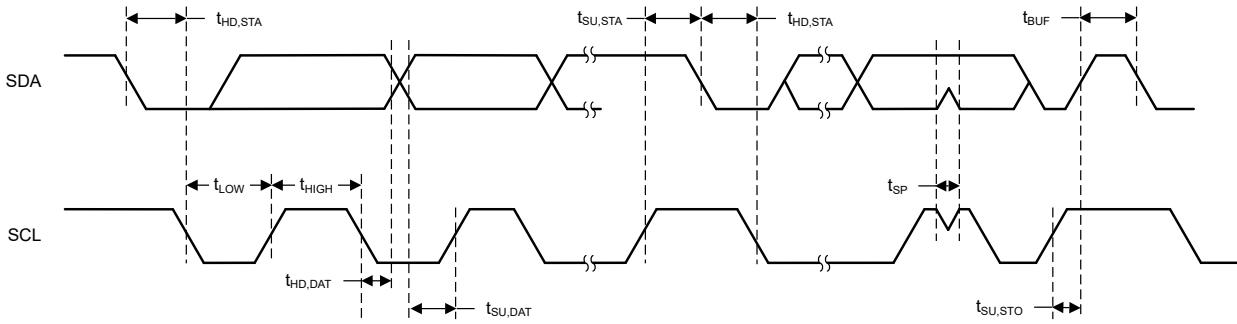

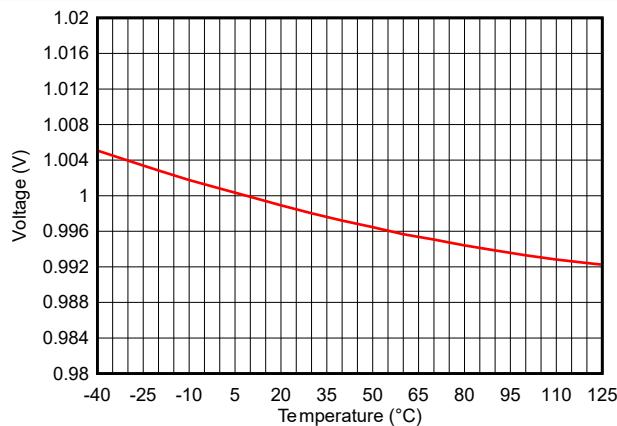

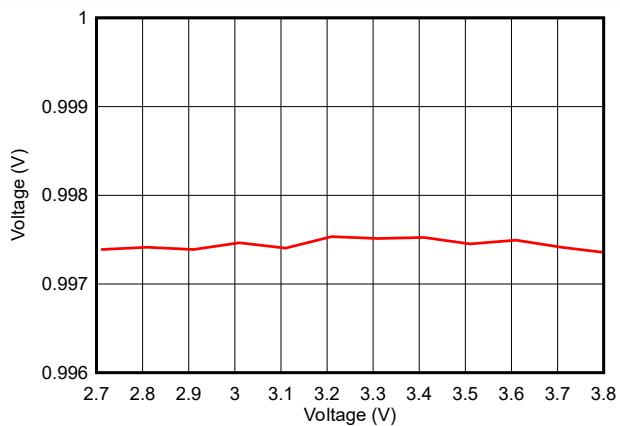

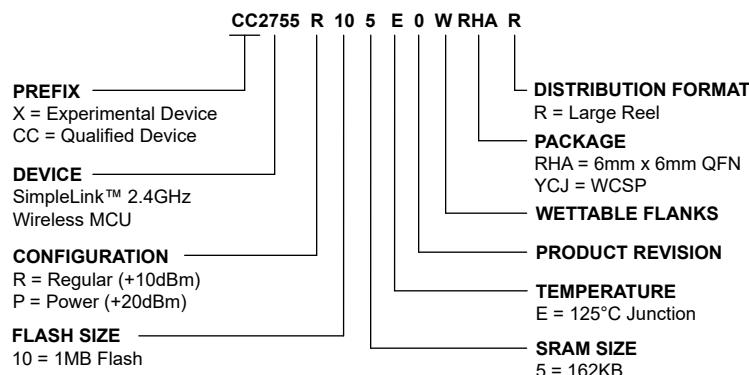

表 6-9. RHA (QFN40) ペリフェラル信号の説明 (続き)