## TPS54202x 4.5V ~ 30V、2A、EMI 対応、同期整流降圧コンバータ

### 1 特長

- 多様なアプリケーションに適した構成

- 入力電圧範囲: 4.5V ~ 30V

- 選択可能な可変出力 (TPS542021)、5V 固定出力 (TPS542025)

- 最大 2A の連続出力電流

- 基準電圧: 0.6V ± 1.5% (25°C)

- 低ドロップアウトモードをサポート

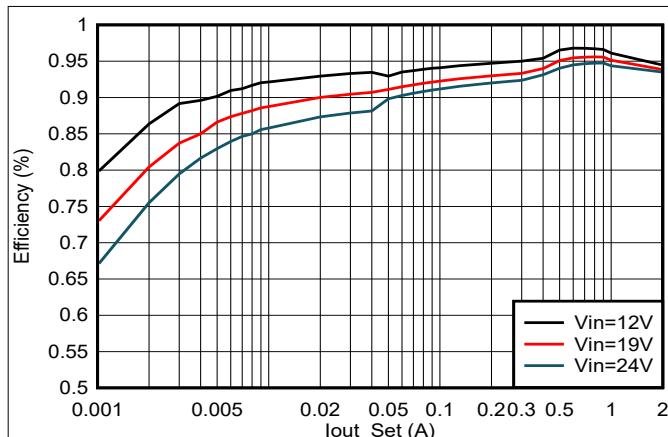

- 高効率

- MOSFET 内蔵: 100mΩ および 60mΩ

- 低いシャットダウン時電流 2μA、静止電流 26μA

- パルス周波数変調 (PFM) による軽負荷時の効率向上

- 使いやすさ

- 内部ループ補償付きピーク電流モード制御

- 固定スイッチング周波数: 500kHz

- 内部ソフトスタート: 5ms

- 周波数スペクトラム拡散により EMI を低減

- ヒップアップモード保護による 2 つの MOSFET の過電流保護

- ラッチ保護機能なしの過熱保護 (OTP)、過電流保護 (OCP)、過電圧保護 (OVP)、低電圧誤動作防止 (UVLO)

- TPS54202 を使用した P2P、B2B

- SOT-23 (6)、SOT-563 パッケージ

### 2 アプリケーション

- 12V、24V の分散パワーバス電源

- 産業用アプリケーション

- 白物家電

- コンシューマーアプリケーション

- セットトップボックス (STB)、デジタルテレビ (DTV)

- プリンタ

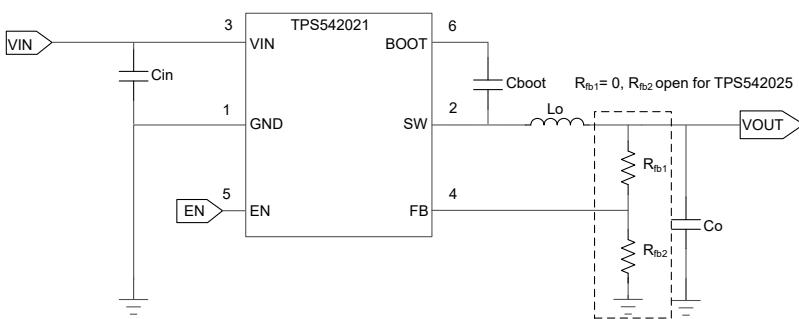

TPS54202x の概略回路図

### 3 説明

TPS54202x は、入力電圧範囲 4.5V ~ 30V、2A 出力の同期整流降圧コンバータです。このデバイスには 2 つの内蔵スイッチング FET、内部的なループ補償、および 5ms の内部ソフトスタートが搭載されているため、部品数を減らすことができます。

TPS54202x には MOSFET が内蔵され、高い電力密度を実現し、PCB 上でわずかな面積しか占有しません。TPS542025 は 5V 固定出力を供給し、FB (フィードバック) 抵抗をさらに減らすことによって BOM (部品表) を節減します。TPS542021 は、FB 抵抗構成を変えることで出力電圧を調整できます。

TPS54202x は、パルス周波数変調で動作することで、軽負荷時の効率をより向上させ、電力損失を低減します。電磁干渉 (EMI) 低減の目的で周波数スペクトラム拡散動作を採用しています。

両方のハイサイド MOSFET でサイクル単位の電流制限を行い、過負荷の状況でコンバータを保護します。また、ローサイド MOSFET の電流制限を自由に設定でき、電流暴走を防止することで、さらに保護が強化されています。あらかじめ設定された時間を超えて過電流の状態が続いた場合、ヒップアップモード保護が作動します。

#### 製品情報

| 部品番号      | パッケージ (1)           | パッケージ サイズ(2)    |

|-----------|---------------------|-----------------|

| TPS542021 | DDC (SOT-23-THN, 6) | 2.9mm × 2.8mm   |

|           | DRL (SOT-563, 6)    | 1.60mm × 1.60mm |

| TPS542025 | DDC (SOT-23-THN, 6) | 2.9mm × 2.8mm   |

|           | DRL (SOT-563, 6)    | 1.60mm × 1.60mm |

(1) 詳細については、セクション 10 を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

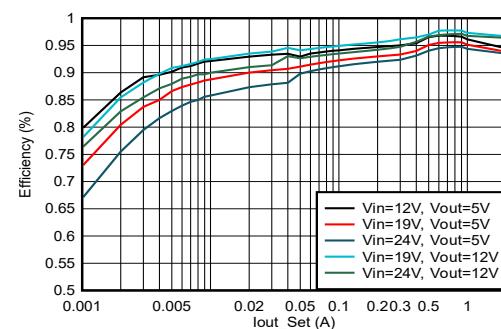

効率と出力電流との関係

## 目次

|                     |    |                             |    |

|---------------------|----|-----------------------------|----|

| 1 特長.....           | 1  | 7 アプリケーションと実装.....          | 14 |

| 2 アプリケーション.....     | 1  | 7.1 アプリケーション情報.....         | 14 |

| 3 説明.....           | 1  | 7.2 代表的なアプリケーション.....       | 14 |

| 4 ピン構成および機能.....    | 3  | 7.3 電源に関する推奨事項.....         | 21 |

| 5 仕様.....           | 4  | 7.4 レイアウト.....              | 21 |

| 5.1 絶対最大定格.....     | 4  | 8 デバイスおよびドキュメントのサポート.....   | 22 |

| 5.2 ESD 定格.....     | 4  | 8.1 デバイス サポート.....          | 22 |

| 5.3 推奨動作条件.....     | 4  | 8.2 ドキュメントのサポート.....        | 22 |

| 5.4 熱に関する情報.....    | 4  | 8.3 ドキュメントの更新通知を受け取る方法..... | 22 |

| 5.5 電気的特性.....      | 5  | 8.4 サポート・リソース.....          | 22 |

| 5.6 代表的特性.....      | 7  | 8.5 商標.....                 | 22 |

| 6 詳細説明.....         | 8  | 8.6 静電気放電に関する注意事項.....      | 22 |

| 6.1 概要.....         | 8  | 8.7 用語集.....                | 22 |

| 6.2 機能ブロック図.....    | 9  | 9 改訂履歴.....                 | 23 |

| 6.3 機能説明.....       | 9  | 10 メカニカル、パッケージ、および注文情報..... | 23 |

| 6.4 デバイスの機能モード..... | 13 |                             |    |

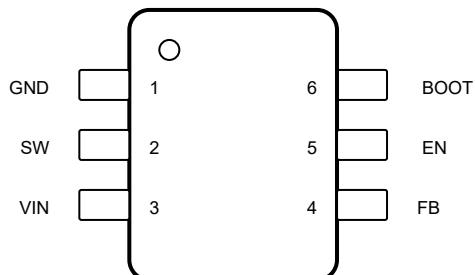

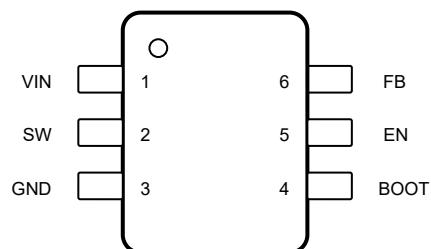

## 4 ピン構成および機能

図 4-1. 6 ピン SOT-23 DDC パッケージ (上面図)

図 4-2. 6 ピン SOT-563 DRL パッケージ (上面図)

表 4-1. ピンの機能

| 名称   | ピン     |         | タイプ <sup>(1)</sup> | 説明                                                                                          |

|------|--------|---------|--------------------|---------------------------------------------------------------------------------------------|

|      | SOT-23 | SOT-563 |                    |                                                                                             |

| BOOT | 6      | 4       | O                  | ハイサイド NFET ゲート駆動回路に電源を入力。BOOT ピンと SW ピンの間に $0.1\mu F$ コンデンサを接続します。                          |

| EN   | 5      | 5       | I                  | デバイス出力のイネーブル制御。5V に接続するか、このピンをフローティングのままにすると、デバイス出力がイネーブルになります。このデバイス出力を無効化するには、GND に接続します。 |

| FB   | 4      | 6       | I                  | コンバータの帰還入力。TPS542021 では帰還抵抗デバイダを用いて出力電圧に接続し、TPS542025 では固定 5V 出力を得るために出力コンデンサに接続します。        |

| GND  | 1      | 3       | —                  | グラウンドピン。                                                                                    |

| SW   | 2      | 2       | O                  | ハイサイド NFET およびローサイド NFET 用のスイッチ ノード接続。                                                      |

| VIN  | 3      | 1       | —                  | 入力電源電圧ピン。                                                                                   |

(1) O = 出力、I = 入力

## 5 仕様

### 5.1 絶対最大定格

特に記述のない限り、動作時接合部温度の推奨範囲である  $-40^{\circ}\text{C} \sim +150^{\circ}\text{C}$  にわたります<sup>(1)</sup>

|                                  |               | 最小値  | 最大値 | 単位                 |

|----------------------------------|---------------|------|-----|--------------------|

| 入力電圧範囲、 $V_I$                    | VIN           | -0.3 | 32  | V                  |

|                                  | EN            | -0.3 | 7   | V                  |

|                                  | FB            | -0.3 | 7   | V                  |

| 出力電圧範囲、 $V_O$                    | BOOT SW 間     | -0.3 | 7   | V                  |

|                                  | SW            | -0.3 | 32  | V                  |

|                                  | SW (20ns の過渡) | -5   | 32  | V                  |

| 動作時の接合部温度 <sup>(2)</sup> 、 $T_J$ |               | -40  | 150 | $^{\circ}\text{C}$ |

| 保管温度範囲、 $T_{stg}$                |               | -65  | 150 | $^{\circ}\text{C}$ |

- (1) 「絶対最大定格」外での操作は、デバイスに恒久的な損傷を引き起こす可能性があります。「絶対最大定格」は、これらの条件、または「推奨動作条件」に示された値を超える他のいかなる条件下においても、本デバイスが正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能性、性能に影響を及ぼし、デバイスの寿命を短縮する可能性があります。

- (2) 接合部温度が  $150^{\circ}\text{C}$  を超える動作は可能ですが、デバイスの寿命が短くなります。

### 5.2 ESD 定格

|                  |                                                                   | 値          | 単位 |

|------------------|-------------------------------------------------------------------|------------|----|

| $V_{(ESD)}$ 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>              | $\pm 2500$ | V  |

|                  | 荷電デバイス モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | $\pm 1500$ |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                |           | 最小値  | 最大値 | 単位                 |

|----------------|-----------|------|-----|--------------------|

| $V_I$ 入力電圧範囲   | VIN       | 4.5  | 30  | V                  |

|                | EN        | -0.1 | 5.5 | V                  |

|                | FB        | -0.1 | 5.5 | V                  |

| $V_O$ 出力電圧範囲   | BOOT SW 間 | -0.1 | 5.5 | V                  |

|                | SW        | -0.1 | 30  | V                  |

| $T_J$ 動作時接合部温度 |           | -40  | 150 | $^{\circ}\text{C}$ |

### 5.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>        |                     | TPS54202x            |                    | 単位                          |  |

|-----------------------------|---------------------|----------------------|--------------------|-----------------------------|--|

|                             |                     | DDC (SOT-23-THN、6)   |                    |                             |  |

|                             |                     | JEDEC <sup>(2)</sup> | EVM <sup>(3)</sup> |                             |  |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗        | 118.6                | 該当なし               | $^{\circ}\text{C}/\text{W}$ |  |

| $R_{\theta JC(\text{top})}$ | 接合部からケース (上面) への熱抵抗 | 63.6                 | 該当なし               | $^{\circ}\text{C}/\text{W}$ |  |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗        | 34.4                 | 該当なし               | $^{\circ}\text{C}/\text{W}$ |  |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ    | 18.5                 | 該当なし               | $^{\circ}\text{C}/\text{W}$ |  |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ    | 33.7                 | 該当なし               | $^{\circ}\text{C}/\text{W}$ |  |

| 熱評価基準 <sup>(1)</sup> |                              | TPS54202x            |                    | 単位   |  |

|----------------------|------------------------------|----------------------|--------------------|------|--|

|                      |                              | DDC (SOT-23-THN, 6)  |                    |      |  |

|                      |                              | JEDEC <sup>(2)</sup> | EVM <sup>(3)</sup> |      |  |

| R <sub>θJA_EVM</sub> | 接合部から周囲への熱抵抗(オフィシャル EVM ボード) | 該当なし                 | 57.2               | °C/W |  |

- (1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションノートを参照してください。

(2) この表に示す R<sub>θJA</sub> の値は他のパッケージとの比較にのみ有効であり、設計目的に使用することはできません。これらの値は、標準的な JEDEC ボードでシミュレーションされました。これらの値は、実際のアプリケーションで得られた性能を表すものではありません。

(3) 実際の R<sub>θJA</sub> は、TI の評価基板でテスト済みです。

## 5.5 電気的特性

ここで規定される電気的定格は、特に記述のない限り、このドキュメント内のすべての仕様に適用されます。標準値は T<sub>J</sub> = 25°C、V<sub>IN</sub> = 12V に対応します。最小値と最大値の制限は、T<sub>J</sub> = -40°C～+150°C、V<sub>IN</sub> = 4.5V～30V (特に記述がない限り)。

| パラメータ                               |                                   | テスト条件                                                                                          | 最小値   | 標準値  | 最大値   | 単位  |

|-------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------|-------|------|-------|-----|

| <b>電源</b>                           |                                   |                                                                                                |       |      |       |     |

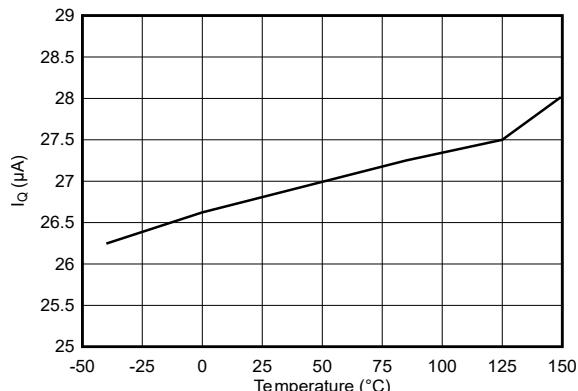

| I <sub>Q(VIN)</sub>                 | エコモードでの V <sub>IN</sub> 静止電流      | 非スイッチング、V <sub>IN</sub> = 12V、V <sub>EN</sub> = 5V、V <sub>FB</sub> = 1V、I <sub>OUT</sub> = 0mA | 26    |      |       | μA  |

| I <sub>SD(VIN)</sub>                | V <sub>IN</sub> のシャットダウン時消費電流     | V <sub>IN</sub> = 12V、V <sub>EN</sub> = 0V                                                     | 3     |      |       | μA  |

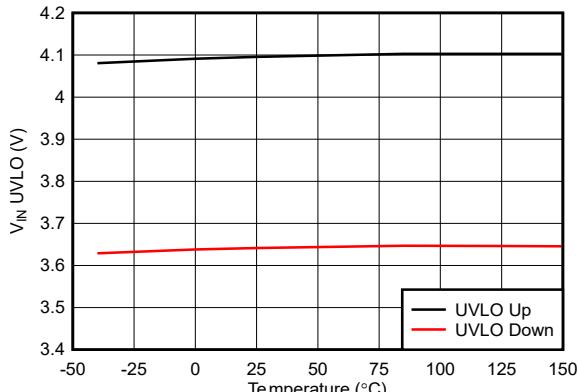

| <b>UVLO</b>                         |                                   |                                                                                                |       |      |       |     |

| V <sub>UVLO(R)</sub>                | V <sub>IN</sub> UVLO 立ち上がりスレッショルド | V <sub>IN</sub> 立ち上がり                                                                          | 3.9   | 4.2  | 4.4   | V   |

| V <sub>UVLO(F)</sub>                | V <sub>IN</sub> UVLO 立ち下がりスレッショルド | V <sub>IN</sub> 立ち下がり                                                                          | 3.4   | 3.7  | 3.9   | V   |

| V <sub>UVLO(H)</sub>                | V <sub>IN</sub> UVLO ヒステリシス       |                                                                                                | 400   | 480  | 560   | mV  |

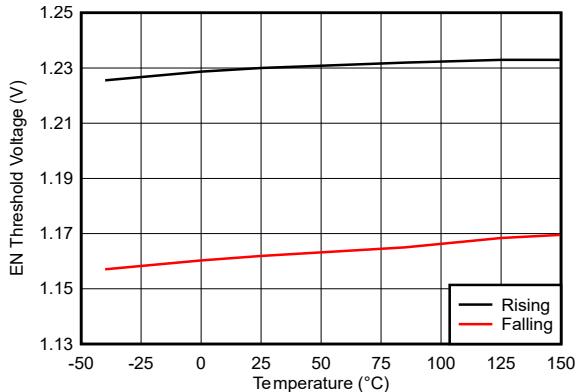

| <b>イネーブル</b>                        |                                   |                                                                                                |       |      |       |     |

| V <sub>EN(R)</sub>                  | EN 電圧立ち上がりスレッショルド                 | EN 立ち上がり、スイッチングはイネーブル                                                                          | 1.21  | 1.28 |       | V   |

| V <sub>EN(F)</sub>                  | EN 電圧立ち下がりスレッショルド                 | EN 立ち下がり、スイッチングはディスエーブル                                                                        | 1.1   | 1.19 |       | V   |

| I <sub>EN(P)</sub>                  | EN ピン ソース電流                       | V <sub>EN</sub> = 1.1 V                                                                        | 0.7   |      |       | μA  |

| I <sub>EN(H)</sub>                  | EN ピンのソース電流ヒステリシス                 | V <sub>EN</sub> = 1.5 V                                                                        | 1.55  |      |       | μA  |

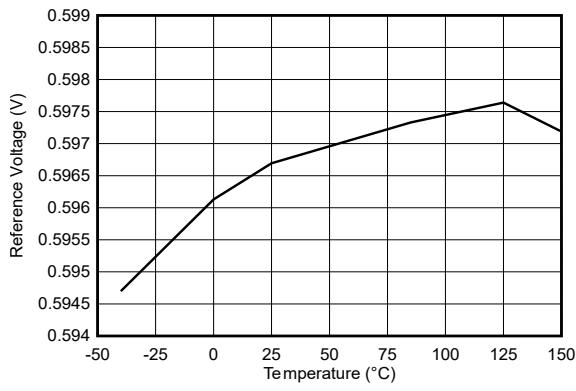

| <b>リファレンス電圧</b>                     |                                   |                                                                                                |       |      |       |     |

| V <sub>FB</sub>                     | FB 電圧 TPS542025                   | T <sub>J</sub> = 25°C                                                                          | 4.925 | 5    | 5.075 | V   |

|                                     |                                   | T <sub>J</sub> = 0°C～85°C                                                                      |       | 5    |       |     |

|                                     |                                   | T <sub>J</sub> = -40°C～150°C                                                                   | 4.9   | 5    | 5.1   | V   |

| V <sub>FB</sub>                     | FB 電圧 TPS542021                   | T <sub>J</sub> = 25°C                                                                          | 590   | 596  | 602   | mV  |

| V <sub>FB</sub>                     | FB 電圧 TPS542021                   | T <sub>J</sub> = 0°C～85°C                                                                      |       | 596  |       | mV  |

| V <sub>FB</sub>                     | FB 電圧 TPS542021                   | T <sub>J</sub> = -40°C～150°C                                                                   | 587   | 596  | 605   | mV  |

| <b>スタートアップ</b>                      |                                   |                                                                                                |       |      |       |     |

| t <sub>SS</sub>                     | 内部固定ソフトスタート時間                     | 0.1 × V <sub>OUT</sub> から 0.9 × V <sub>OUT</sub> まで                                            |       | 5    |       | ms  |

| <b>スイッチング周波数</b>                    |                                   |                                                                                                |       |      |       |     |

| <b>電力段</b>                          |                                   |                                                                                                |       |      |       |     |

| R <sub>DSON(HS)</sub>               | ハイサイド MOSFET オン抵抗                 | V <sub>BOOT-SW</sub> = 5V                                                                      | 100   |      |       | mΩ  |

| R <sub>DSON(LS)</sub>               | ローサイド MOSFET オン抵抗                 |                                                                                                | 60    |      |       | mΩ  |

| f <sub>SW</sub>                     | スイッチング周波数                         |                                                                                                | 390   | 500  | 630   | kHz |

| t <sub>ON(min)</sub> <sup>(1)</sup> | 最小 ON パルス幅                        |                                                                                                | 70    |      |       | ns  |

| <b>過電流保護</b>                        |                                   |                                                                                                |       |      |       |     |

| I <sub>HS(OC)</sub>                 | ハイサイド ピーク電流制限 2A                  | HS MOSFET のピーク電流制限                                                                             | 2.5   | 3.2  | 3.9   | A   |

| I <sub>LS(OC)</sub>                 | ローサイド バレー電流制限 2A                  | LS MOSFET のバレー電流制限                                                                             | 2     | 3    | 4.3   | A   |

| I <sub>LPEAK(min)</sub>             | パワー セーブ モードのピーク インダクタ電流スレッショルド    |                                                                                                | 0.75  |      |       | A   |

## 5.5 電気的特性 (続き)

ここで規定される電気的定格は、特に記述のない限り、このドキュメント内のすべての仕様に適用されます。標準値は  $T_J = 25^\circ\text{C}$ 、 $V_{IN} = 12\text{V}$  に対応します。最小値と最大値の制限は、 $T_J = -40^\circ\text{C} \sim +150^\circ\text{C}$ 、 $V_{IN} = 4.5\text{V} \sim 30\text{V}$  (特に記述がない限り)。

| パラメータ               | テスト条件                     | 最小値   | 標準値          | 最大値 | 単位   |

|---------------------|---------------------------|-------|--------------|-----|------|

| <b>出力 OVP と UVP</b> |                           |       |              |     |      |

| $V_{OVP}$           | $V_{FB}$ 立ち上がり            | 108   | %            |     |      |

|                     | OVP ヒステリシス                | 4     | %            |     |      |

| $t_{HIC(WAIT)}$     | ヒカップに移行する前の待機時間           | 512   |              |     | サイクル |

| $t_{HIC(RE)}$       | 再起動前のヒカップ時間               | 16384 |              |     | サイクル |

| <b>サーマル シャットダウン</b> |                           |       |              |     |      |

| $T_{J(SD)}^{(1)}$   | サーマル シャットダウンのスレッショルド      | 160   |              |     | °C   |

| $T_{J(HYS)}^{(1)}$  | サーマル シャットダウン ヒステリシス       | 10    |              |     | °C   |

| $t_{HICCUP}$        | ヒカップ時間                    | 32768 |              |     | サイクル |

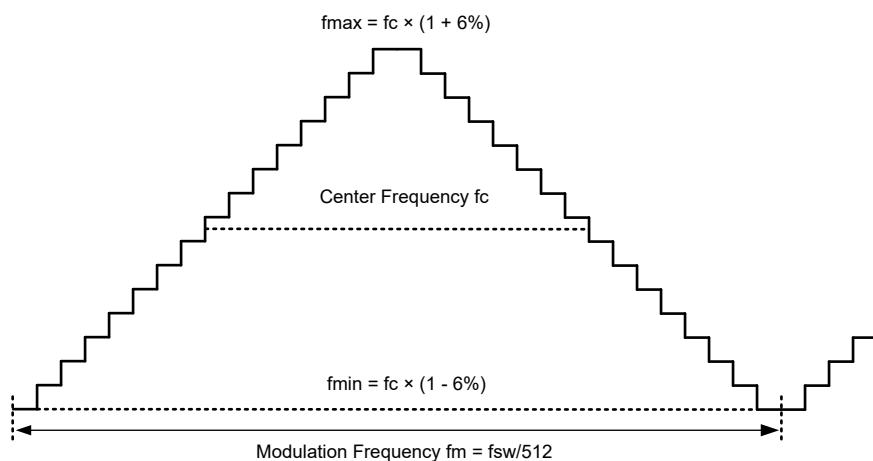

| <b>周波数スペクトラム拡散</b>  |                           |       |              |     |      |

| $F_{FSS}$           | スイング周波数                   |       | $f_{SW}/512$ |     | kHz  |

| $f_{SPREAD}$        | スペクトラム拡散を有効にした場合の内部発振器の拡散 |       | ±6           |     | %    |

(1) 量産では検査していません。

## 5.6 代表的特性

$V_{IN} = 12V$ 、 $T_A = 25^\circ C$  (特に指定のない限り)。

図 5-1.  $V_{IN}$  UVLO スレッショルド

図 5-2. EN スレッショルド

図 5-3. 非スイッチング  $I_Q$

図 5-4. 基準電圧

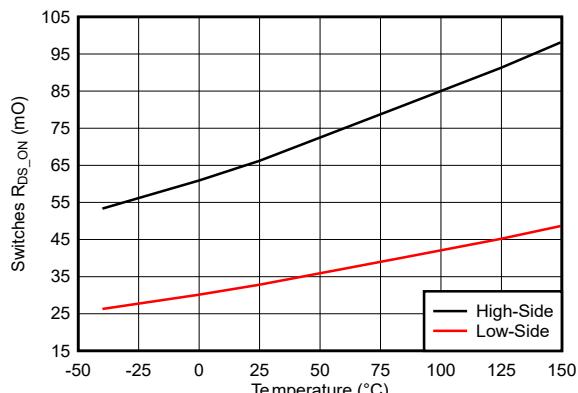

図 5-5. ハイサイドおよびローサイドスイッチの  $R_{DS\_ON}$

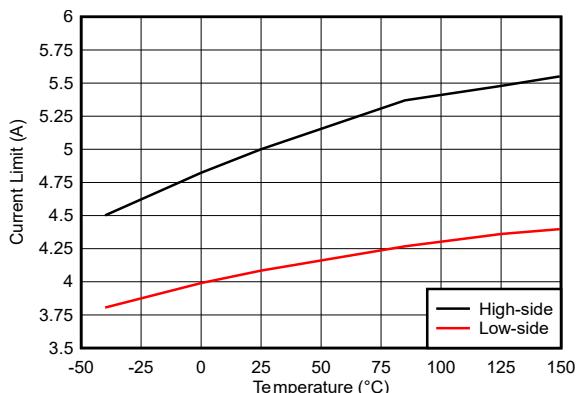

図 5-6. ハイサイドおよびローサイド電流制限

## 6 詳細説明

### 6.1 概要

TPS54202x ファミリのデバイスは、2 つの N チャネル MOSFET を内蔵した、4.5V ~ 30V、2A 出力の同期整流降圧(バック)コンバータです。ラインおよび負荷の過渡状態における性能を向上させるため、本デバイスは一定周波数のピーケ電流モード制御で出力キャパシタンスを低減します。これらのデバイスは、パルス周波数変調で動作することで、軽負荷時の効率をより向上させ、電力損失を低減します。スイッチング周波数は、500kHz に固定されています。TPS542025 は 5V 固定出力ですが、TPS542021 は可変出力です。最適化された内部補償回路により外付け部品数を最小限に抑え、制御ループ設計の簡素化を実現します。

本デバイスは、 $V_{IN} = 4.5V$  のときにスイッチングを開始します。無負荷で非スイッチング時の動作時電流は、標準値  $26\mu A$  です。デバイスがディスエーブル時の電源電流の標準値は  $2\mu A$  です。

$100m\Omega$  のハイサイド MOSFET、 $60m\Omega$  の MOSFET を内蔵しており、最大 2A の連続出力電流で高効率の電源を設計できます。

本デバイスはブート再充電ダイオードを内蔵しているため外付け部品数を削減できます。内蔵ハイサイド MOSFET のバイアス電圧は、BOOT ピンから PH ピンの間の外付けコンデンサによって供給されます。このブートコンデンサ電圧は UVLO 回路によって監視され、標準値  $2.1V$  のプリセットされたスレッショルドを下回ると、ハイサイド MOSFET がオフになります。

電磁干渉(EMI)低減の目的で周波数スペクトラム拡散動作を採用しています。

本デバイスは、過電圧コンパレータを利用して、過度の出力過電圧を最小限に抑えています。レギュレートされた出力電圧が公称電圧の  $108\%$  を超えると、過電圧コンパレータが作動してハイサイド MOSFET がオフになり、出力電圧が  $104\%$  を下回るまでオンになりません。

本デバイスは  $5ms$  のソフトスタート時間を内蔵し、突入電流を最小限に抑えます。

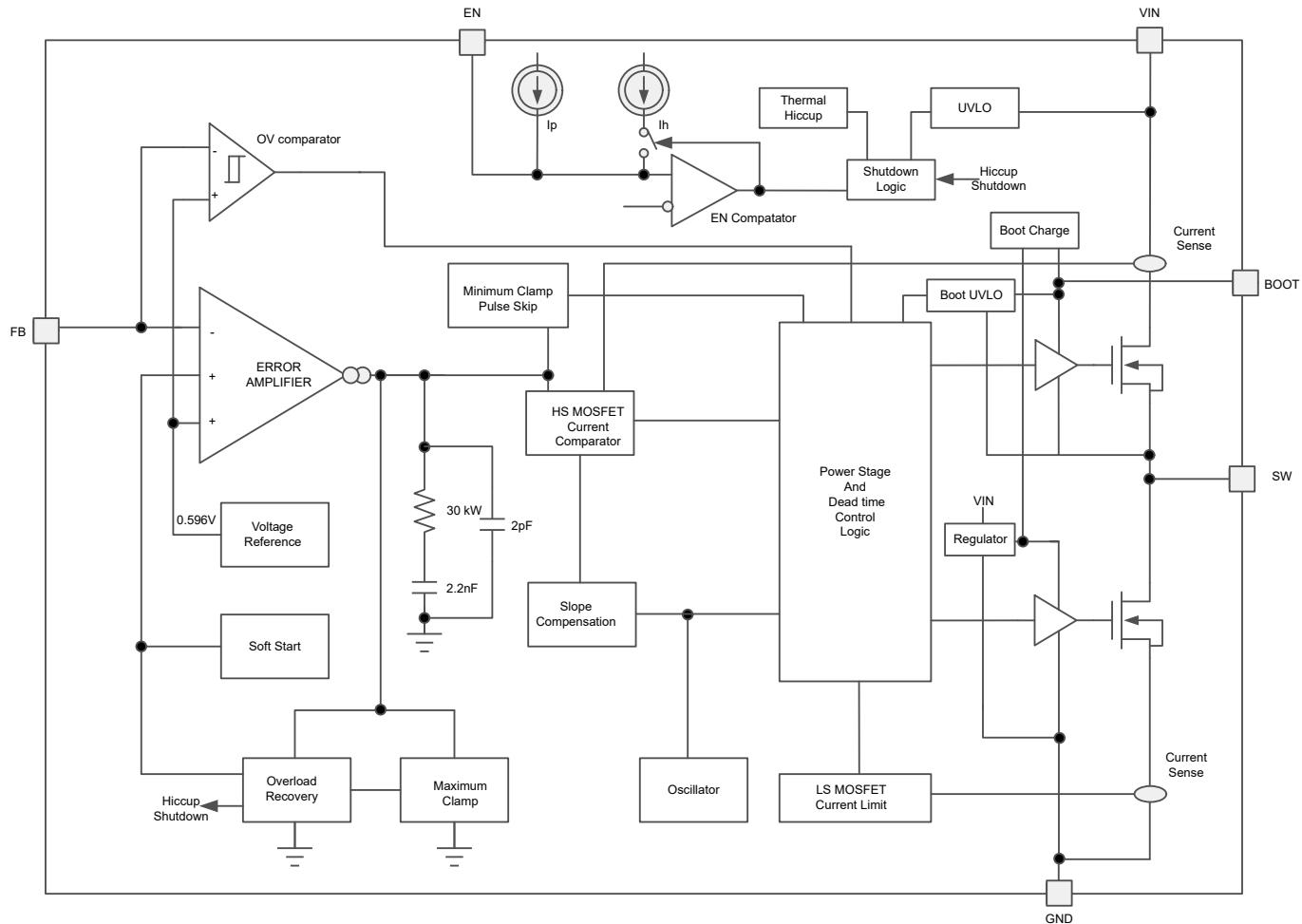

## 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 固定周波数 PWM 制御

本デバイスは、固定周波数のピーク電流モード制御を使用します。TPS542025 の場合、FB ピンを Vout に接続することで、出力電圧は 5V に固定されます。TPS542021 は、エラー アンプにより、出力電圧が FB ピンの外付け抵抗を介して内部電圧リファレンスと比較されます。電圧帰還ループを使用して、電圧オフセットに基づいてピーク電流コマンドを調整することにより、DC 電圧を正確にレギュレートします。ピーク インダクタ電流を HS スイッチからセンスし、ピーク電流スレッショルドと比較することで、HS スイッチのオン時間を制御します。電圧帰還ループは内部補償されているため、外付け部品を減らすことができ、設計が容易になり、出力コンデンサの組み合わせをほとんど自由に選んでも安定した動作が得られます。

TPS54202x は、制御されたデューティサイクルでハイサイドおよびローサイドの NMOS スイッチをオンにすることにより、出力電圧の安定化を実現します。ハイサイド スイッチがオンしている間、SW ピンの電圧は最大で  $V_{IN}$  まで上昇し、インダクタ電流  $i_L$  は  $(V_{IN} - V_{OUT})/L$  の直線勾配で増加します。制御ロジックにより HS スイッチがオフされると、アンチシャットスルーのデッドタイムの後、LS スイッチがオンします。インダクタ電流は、ローサイド スイッチを通して  $-V_{OUT}/L$  の割合で放電されます。降圧コンバータの制御パラメータは、デューティサイクル  $D = t_{ON}/t_{SW}$  と定義されます。ここで、 $t_{ON}$  はハイサイド スイッチオン時間、 $t_{SW}$  はスイッチング周期です。コンバータ制御ループは、デューティサイクル  $D$  を調整することにより、出力電圧を一定に維持します。損失を無視できるような理想的な降圧コンバータでは、次の式のように、 $D$  は出力電圧に比例し、入力電圧に反比例します。 $D = V_{OUT}/V_{IN}$ .

### 6.3.2 パルス周波数変調

TPS54202x デバイスは、軽負荷時の効率を向上させるため、負荷電流が小さいときにはパルス周波数モードで動作するよう設計されています。ピーク インダクタ電流が標準値 750mA を下回ると、デバイスはパルス周波数変調 (PFM) モードに入ります。

PFM モードでは、負荷とともにスイッチング周波数が低下するため、軽負荷時にスイッチング損失を最小限に抑えます。本デバイスの PFM モードでは、エラー アンプの出力電圧がクランプされ、ハイサイド内蔵 MOSFET のスイッチングを防ぎます。

### 6.3.3 エラー アンプ

このデバイスには、エラー アンプとしてトランス コンダクタンス アンプが搭載されています。エラー アンプは、FB 端子の電圧を、内部ソフトスタート電圧または内部の 0.596V 電圧リファレンスのいずれか低い方と比較します。エラー アンプの相互コンダクタンス標準値は 240 $\mu$ A/V です。周波数補償部品は、エラー アンプの出力とグランドの間に内部的に配置されます。

### 6.3.4 スロープ補償と出力電流

本デバイスは、スイッチ電流の信号に補償ランプを追加します。このスロープ補償により、高いデューティ サイクルでの低調波発振を防いでいます。使用可能なピーク インダクタ電流は、デューティ サイクルの全範囲にわたって一定です。

### 6.3.5 イネーブルと低電圧誤動作防止の調整

EN ピンは、本デバイスの電気的オン / オフ制御に使用できます。EN ピンの電圧がスレッショルド電圧を超えると、デバイスが動作を開始します。EN ピンの電圧がスレッショルド電圧よりも低くなると、レギュレータはスイッチングを停止し、低静止 (IQ) 状態になります。

EN ピンには内部プルアップ電流ソースがあり、ユーザは EN ピンをフローティングにしてデバイスを有効にできます。アプリケーションで EN ピンの制御が必要な場合は、ピンとのインターフェイスに、オープンドレインまたはオープンコレクタ出力ロジックを使用してください。

本デバイスでは、VIN ピンの内部低電圧誤動作防止 (UVLO) 回路が実装されています。VIN ピンの電圧が内部の VIN UVLO スレッショルドを下回ると、本デバイスはディスエーブルになります。内部 VIN UVLO スレッショルドには、480mV のヒステリシスがあります。

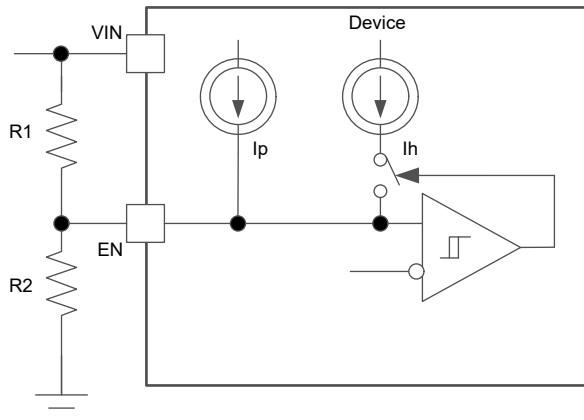

アプリケーションで、より高い UVLO スレッショルドを VIN ピンに必要とする場合、EN ピンを 図 6-1 のように構成できます。外部 UVLO 機能を使用する際には、500mV 以上の値にヒステリシスを設定することを推奨します。

EN ピンの持つ小さなプルアップ電流「Ip」が、外部部品を接続しないときのピンのデフォルト状態を有効に設定します。またこのプルアップ電流は、EN ピンがイネーブル スレッショルドを超過すると Ih だけ増加するため、UVLO 機能の電圧ヒステリシスの制御にも使用されます。式 1 と 式 2 を使用して、指定された UVLO スレッショルドに対する R4 と R5 の値を計算します。

図 6-1. 可変の VIN 低電圧誤動作防止

$$R_4 = \frac{\frac{V_{ENfalling}}{V_{ENrising}} \times V_{START} - V_{STOP}}{I_p \times \left(1 - \frac{V_{ENfalling}}{V_{ENrising}}\right) + I_h} \quad (1)$$

$$R_5 = \frac{R_4 \times V_{ENfalling}}{V_{STOP} - V_{ENfalling} + (I_h + I_p) \times R_4} \quad (2)$$

ここで:

- $I_p = 0.7\mu A$

- $I_h = 1.55\mu A$

- $V_{ENfalling} = 1.19V$

- $V_{ENrising} = 1.22V$

### 6.3.6 プリバイアス出力への安全なスタートアップ

このデバイスは、ローサイド MOSFET がプリバイアス出力を放電しないように設計されています。単調なプリバイアス スタートアップ中は、内部のソフトスタート電圧が FB ピンの電圧を超えるまで、ハイサイドおよびローサイド MOSFET はオンになりません。

### 6.3.7 電圧リファレンス

電圧リファレンス システムは、温度の安定したバンドギャップ回路出力をスケーリングすることで、 $\pm 2\%$  の高精度電圧リファレンス過熱を生成します。標準の電圧リファレンスは、0.596V に設計されています。

### 6.3.8 出力電圧調整

出力電圧は、出力ノードと FB ピンとの間の抵抗分圧回路によって設定されます。TI 推奨の分圧抵抗は公差 1% 以内です抵抗デバイダの上限判定基準値  $100k\Omega$  から開始し、式 3 を使用して出力電圧を計算します。軽負荷時の効率向上させるには、より大きな値の抵抗の使用を検討します。値が大きすぎると、レギュレータがノイズの影響を受けやすくなり、FB 入力電流からの電圧誤差が目立つようになります。

$$V_{OUT} = V_{ref} \times \left( \frac{R_2}{R_3} + 1 \right) \quad (3)$$

### 6.3.9 内部ソフトスタート

TPS54202x は、内部ソフトスタート機能を使用しています。内部ソフトスタート時間の標準値は 5ms に設定されています。

### 6.3.10 ブートストラップ電圧(BOOT)

TPS54202x にはブートレギュレータが内蔵され、ハイサイド MOSFET のゲート駆動電圧を供給するために、BOOT ピンと SW ピンの間に  $0.1\mu\text{F}$  のセラミックコンデンサが必要です。温度および電圧に対して安定した特性を持つため、X7R または X5R クラスの誘電体を持つセラミックコンデンサを推奨します。ドロップアウト改善のため、本デバイスは BOOT と SW ピン間の電圧が標準 2.1V 以上であれば、100% のデューティサイクルで動作します。

### 6.3.11 過電流保護

デバイスは、ハイサイド MOSFET とローサイド MOSFET の両方でサイクル毎に電流を制限することで、過電流状態から保護されます。

#### 6.3.11.1 ハイサイド MOSFET の過電流保護

本デバイスに実装された電流モードコントロールは、内部 COMP 電圧を用いることでハイサイド MOSFET のオフとローサイド MOSFET のオンをサイクル毎に制御します。各サイクルでは、スイッチ電流と内部 COMP 電圧による電流リファレンスが比較されます。ピークスイッチ電流が電流リファレンスを超えた場合、ハイサイドスイッチがオフになります。

#### 6.3.11.2 ローサイド MOSFET の過電流保護

ローサイド MOSFET がオンの間、内部回路が導通電流を監視します。通常動作中は、ローサイド MOSFET が負荷への電流ソースとなります。各クロックサイクルの終わりに、ローサイド MOSFET のソース電流が、内部で設定されたローサイドソース電流制限と比較されます。インダクタのバレー電流がローサイドソース電流制限を超えると、ハイサイド MOSFET はオフにならず、ローサイド MOSFET が次のサイクルにわたってオフに保持されます。サイクル開始時にインダクタバレー電流がローサイドソース電流制限を下回っている場合、ハイサイド MOSFET が再度オフになります。

さらに、出力過負荷状態が 512 スイッチングサイクルに設定されたヒカッピ待機時間よりも長く続いた場合には、デバイスがシャットダウンされ、16384 サイクルのヒカッピ時間の経過後に再起動されます。このヒカッピモードは、大きな過電流の発生時にデバイスの消費電力を低減するために役立ちます。

### 6.3.12 スペクトラム拡散

EMI 低減のため、TPS54202x では周波数スペクトラム拡散を導入しています。ジッタリングスパンは、 $1/512$  スイング周波数においてスイッチング周波数の  $\pm 6\%$  です。スペクトラム拡散の目的は、一定の周波数で動作する代わりに、特定の周波数のピーク放射をより広い範囲の周波数に拡散することで、ピーク放射を除去することです。

図 6-2. 周波数スペクトラム拡散図

### 6.3.13 出力過電圧保護(OVP)

TPS54202x には、出力故障状態からの復帰や強い無負荷過渡で発生する出力電圧オーバーシュートを最小限に抑える、過電圧過渡保護(OVTP)回路が組み込まれています。OVP 回路には、FB ピン電圧を内部スレッショルドと比較する

過電圧コンパレータが内蔵されています。FB ピンの電圧が  $108\% \times V_{ref}$  を上回ると、ハイサイド MOSFET が強制的にオフになります。FB ピンの電圧が  $104\% \times V_{ref}$  を下回ると、ハイサイド MOSFET が再度有効になります。

### 6.3.14 サーマル シャットダウン

接合部温度が標準  $160^{\circ}\text{C}$  を超えると内部のサーマル シャットダウン回路がデバイスのスイッチングを強制停止します。接合部温度が標準  $150^{\circ}\text{C}$  を下回ると内部のサーマルヒップ タイマがカウントを開始します。設定済みの過熱シャットダウンヒップ時間 (32768 サイクル) が経過した後で、デバイスはパワーアップ シーケンスを再開します。

## 6.4 デバイスの機能モード

### 6.4.1 通常動作

入力電圧が UVLO スレッショルドを上回ると、TPS54202x は通常のスイッチング モードで動作可能です。インダクタのピーク電流が  $0\text{A}$  を上回ると、通常の連続導通モード (CCM) が発生します。CCM では、デバイスは固定周波数で動作します。

### 6.4.2 Eco モード動作

これらのデバイスは、軽負荷時には高効率のパルス スキッピング モードで動作する設計です。スイッチ電流が  $0\text{A}$  に低下すると、パルススキップを開始します。パルススキップ中は、スイッチ電流が  $0\text{A}$  に低下するとローサイド FET がオフになります。スイッチング ノード (SW ピン) の波形は、不連続導通モード (DCM) 動作の特性を帶びているため、見かけ上のスイッチング周波数が低下します。出力電流が減少すると、スイッチング パルス間の時間は増加します。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インストルメンツの製品仕様に含まれるものではなく、テキサス・インストルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

TPS542021 デバイスは通常、5V ~ 30V の入力電圧を 5V の固定出力電圧に変換するための降圧コンバータとして使用されます。

### 7.2 代表的なアプリケーション

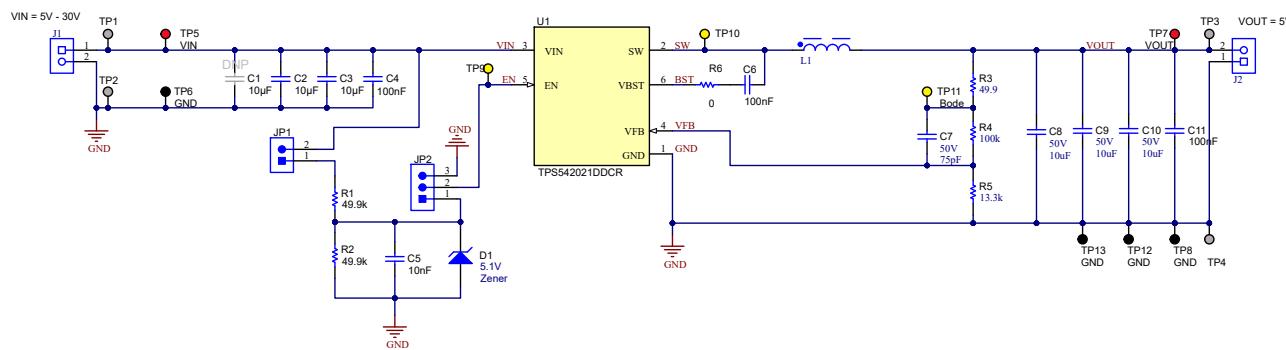

#### 7.2.1 TPS542021 5V ~ 30V 入力、5V 出力コンバータ

図 7-1. 5V/2A リファレンス デザイン

#### 7.2.2 設計要件

この設計例では、次の表に記載されているパラメータを使用します。

表 7-1. 設計パラメータ

| パラメータ           | 値                          |

|-----------------|----------------------------|

| 入力電圧範囲          | 5V ~ 30V                   |

| 出力電圧            | 5V                         |

| 出力電流            | 2A                         |

| 過渡応答、2A の負荷ステップ | $\Delta V_{OUT} = \pm 5\%$ |

| 出力電圧リップル        | 10mVpp                     |

| スイッチング周波数       | 500kHz                     |

## 7.2.3 詳細な設計手順

### 7.2.3.1 入力コンデンサの選択

デバイスには、入力デカッピング コンデンサと、アプリケーションによってはバルク キャパシタが必要となります。デカッピング コンデンサに  $10\mu\text{F}$  よりもセラミック コンデンサをお勧めします。VIN ~ GND 間の  $0.1\mu\text{F}$  コンデンサ (C4) 追加オプションにより、追加の高周波数フィルタリングを提供可能です。コンデンサの電圧定格は、最大入力電圧よりも大きい必要があります。

次の式を使用して、入力リップル電圧 ( $\Delta V_{IN}$ ) を計算します。

$$\Delta V_{IN} = \frac{I_{OUT(MAX)} \times 0.25}{C_{BULK} \times f_{SW}} + I_{OUT(MAX)} \times ESR_{MAX} \quad (4)$$

ここで

- $C_{BULK}$  はバルク キャパシタの値

- $f_{SW}$  はスイッチング周波数

- $I_{OUT(MAX)}$  は最大負荷電流

- $ESR_{MAX}$  はバルク キャパシタの最大直列抵抗

最大 RMS (実効値) リップル電流も確認する必要があります。ワーストケース条件については、式 5 を使用して  $I_{CIN(RMS)}$  を計算します。

$$I_{CIN(RMS)} = \frac{I_{OUT(MAX)}}{2} \quad (5)$$

実際の入力電圧リップルは、レイアウトに関連する寄生成分と、電圧ソースの出力インピーダンスの影響を大きく受けます。「設計要件」に示されたこの回路の実際の入力電圧リップルは、計算値よりも大きくなっています。入力コンデンサ両端の最大電圧は  $VIN(MAX) + \Delta V_{IN}/2$  です。選択したバイパス コンデンサは定格が  $50\text{V}$ 、リップル電流キャパシティが  $2\text{A}$  以上です。どちらの値も十分なマージンを提供します。どのような環境であっても、電圧と電流の最大定格を超えないようにすることが重要です。

### 7.2.3.2 ブートストラップ コンデンサの選定

適切な動作のためには、BOOT ピンと SW ピンの間に  $0.1\mu\text{F}$  のセラミック コンデンサを接続する必要があります。TI はセラミック コンデンサの使用を推奨します。

### 7.2.3.3 出力電圧の設定ポイント

TPS542021 デバイスの出力電圧は、抵抗デバイダ回路を使用して外部で調整可能です。分圧回路は R4 および R5 で構成されます。出力電圧と抵抗デバイダの関係を計算するには、次の式を使用します。

$$R_5 = \frac{R_4 \times V_{ref}}{V_{OUT} - V_{ref}} \quad (6)$$

$$V_{OUT} = V_{ref} \times \left( \frac{R_4}{R_5} + 1 \right) \quad (7)$$

R4 の値として、約  $100\text{k}\Omega$  を選択します。R5 をわずかに増加または減少させると、標準の値の抵抗を使用するときに、より近い出力電圧マッチングが得られる場合があります。この設計では、 $R4 = 100\text{k}\Omega$ 、 $R5 = 13.3\text{k}\Omega$  であるため、出力電圧は  $5\text{V}$  になります。 $49.9\Omega$  抵抗 R3 は、安定性テストで制御ループを切断するための便利な場所として用意されています。

### 7.2.3.4 低電圧誤動作防止設定点

低電圧ロックアウト (UVLO) 設定ポイントは、R1 と R2 の外部電圧デバイダ回路により調整可能です。TPS542021 デバイスの VIN ピンと EN ピンの間に R1 を接続します。EN ピンと GND ピンの間に R2 を接続します。UVLO には 2 つのスレッショルドがあり、1 つは入力電圧の立ち上がり時のパワー アップ中に適用され、もう 1 つは入力電圧の立ち下がり時

のパワー ダウンまたはブラウン アウト中に適用されます。[式 2](#) および [式 1](#) を使用して、R1 と R2 の上限および下限判定基準抵抗値を計算します。

### 7.2.3.5 出力フィルタ部品

出力フィルタには、出力インダクタ ( $L_O$ ) と  $C_O$  の 2 つのコンポーネントを選択する必要があります。

#### 7.2.3.5.1 インダクタの選択

出力インダクタの最小値 ( $L_{MIN}$ ) を計算するには、次の式を使用します。

$$L_{MIN} = \frac{V_{OUT} \times [V_{IN(MAX)} - V_{OUT}]}{V_{IN(MAX)} \times K_{IND} \times I_{OUT} \times f_{SW}} \quad (8)$$

ここで：

$K_{IND}$  は、最大出力電流に対するインダクタのリップル電流の量を示す係数です。

一般に、 $K_{IND}$  の値は設計者の裁量で決定しますが、以下のガイドラインに従うことができます。セラミックなどの低 ESR 出力コンデンサを使用した設計では、最大  $K_{IND} = 0.3$  の値を使用できます。

この設計例では、 $K_{IND} = 0.3$  を選択します。インダクタの最小値は  $13.7\mu H$  と計算できます。この設計では、 $L_{MIN}$  に最も近い標準値として  $15\mu H$  を選択しています。

出力フィルタ インダクタについては、RMS 電流および飽和電流の定格を超えてはいけません。次の式を使用して、RMS インダクタ電流 ( $I_{L(RMS)}$ ) を計算します。

$$I_{L(MAX)} = \sqrt{I_{OUT(MAX)}^2 + \frac{1}{12} \times \left[ \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times L_O \times f_{SW} \times 0.8} \right]^2} \quad (9)$$

次の式を使用して、ピーク インダクタ電流 ( $I_{L(PK)}$ ) を計算します。

$$I_{L(PK)} = I_{OUT(MAX)} + \frac{V_{OUT} \times [V_{IN(MAX)} - V_{OUT}]}{V_{IN(MAX)} \times L_O \times f_{SW} \times 1.6} \quad (10)$$

他の設計要件を満足していれば、設計者が許容するリップル電流の大きさに合わせて、これより小さい値や大きい値のインダクタを使用できます。インダクタの値が大きいと AC 電流が小さくなり、出力電圧リップルが減少します。インダクタの値が小さいと、AC 電流および出力電圧リップルが増加します。

#### 7.2.3.5.2 出力コンデンサの選択

出力コンデンサの値を選択するときは、3 つの主要な要因を考慮します。出力コンデンサは、変調回路の極、出力電圧リップル、および負荷電流の大きな変化に対するレギュレータの応答を決定します。出力容量は、これら 3 つの条件のうち最も厳しいものに基づいて選択する必要があります。

最初の条件は、負荷電流の大きな変化に対して求められる応答です。レギュレータが電流を供給できないときには、出力コンデンサが負荷に電流を供給する必要があります。この状況は、レギュレータに対して所望のホールドアップ時間が存在する場合に発生します。この場合、入力電力の除去後、出力コンデンサは指定された時間だけ、出力電圧を一定のレベルよりも高く保持する必要があります。また、無負荷から全負荷への遷移など、負荷の電流要件に大きく高速な変化が発生すると、レギュレータは一時的に十分な出力電流を供給できなくなります。通常、レギュレータでは、制御ループが負荷電流および出力電圧の変化を検知して、その変化に合わせてデューティサイクルを調整するまでに、2 クロック サイクル以上を必要とします。出力コンデンサのサイズは、制御ループが負荷の変化に応答するまでの間、負荷に追加の電流を供給できるように決定する必要があります。出力容量は、出力電圧の降下を許容範囲内に抑えながら、2 クロック サイクルにわたって電流の差分を供給するのに十分な大きさでなければなりません。次の式を使用して、必要な最小出力キャパシタンスを計算します。

$$C_0 = \frac{2 \times \Delta I_{OUT}}{f_{SW} \times \Delta V_{OUT}} \quad (11)$$

ここで

- $\Delta I_{OUT}$  は出力電流の変化量

- $f_{SW}$  はレギュレータのスイッチング周波数です。

- $\Delta V_{(OUT)b}$  は出力電圧の許容変化量

この例では、負荷過渡応答が、1.5A の負荷ステップに対する出力電圧  $V_{OUT}$  の 5% の変化として規定されています。この例では、 $\Delta I_{OUT} = 1.5A$ 、 $\Delta V_{OUT} = 0.05 \times 5 = 0.25V$  です。これらの値を使用すると、最小キャパシタンスは  $24\mu F$  になります。この値は、出力電圧の変化における出力コンデンサの ESR を考慮していません。セラミックコンデンサの場合、ESR は通常十分に小さいため、この計算では無視できます。

式 12 で、出力電圧リップル仕様を満たすために必要な最小出力容量を計算します。この場合、最大出力電圧リップルは 30mV です。この要件下で、式 12 により  $4.56\mu F$  と算出されます。

$$C_0 = \frac{1}{8 \times f_{SW}} \times \frac{1}{V_{OUTtripple}} \quad (12)$$

ここで

- $f_{SW}$  はスイッチング周波数です

- $V_{(OUTtripple)}$  は最大許容出力電圧リップル

- $I_{(ripple)}$  はインダクタリップル電流

式 13 を使用して、出力電圧リップル仕様を満足するために出力コンデンサに許容される最大 ESR を計算します。式 13 は ESR が  $54.8m\Omega$  よりも小さい必要があることを示しています。この場合、セラミックコンデンサの ESR は  $54.8m\Omega$  よりはるかに小さくなります。

$$R_{ESR} < \frac{V_{OUTtripple}}{I_{ripple}} \quad (13)$$

出力コンデンサは、クロスオーバー周波数  $f_0$  に影響を及ぼす可能性があります。ループ安定性と内部寄生パラメータの影響を考慮して、フィードフォワードコンデンサを考慮せずに、40kHz より低いクロスオーバー周波数を選択します。式 14 に、フィードフォワードコンデンサ C6 を使用しないときのクロスオーバー周波数を簡単に見積もる式を示します。C<sub>OUT</sub> の ESR は小さいと仮定しています。

$$f_0 = \frac{3.95}{V_{OUT} \times C_{OUT}} \quad (14)$$

経年劣化、温度、および DC バイアスに対して、追加の静電容量ディレイティングを考慮する必要があるため、この最小値は増加します。この例では、22uF 25V、X7R セラミックコンデンサを 2 つ使用しています。一般に、コンデンサでは、障害や過熱を発生させずにコンデンサが処理できるリップル電流の大きさに制限があります。インダクタリップル電流に対して対応可能な出力コンデンサを指定する必要があります。一部のコンデンサのデータシートでは、最大リップル電流の RMS 値が指定されています。式 15 を使用して、出力コンデンサで処理できる必要のある RMS リップル電流を計算します。このアプリケーションでは、式 15 が各コンデンサの 79mA を生成します。

$$I_{COUT(RMS)} = \frac{1}{\sqrt{12}} \times \left[ \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{V_{IN(MAX)} \times L_0 \times f_{SW} \times N_C} \right] \quad (15)$$

### 7.2.3.5.3 フィードフォワードコンデンサ

場合によっては、R<sub>FBT</sub> の両端にフィードフォワードコンデンサを接続して、負荷過渡応答やループ位相マージンを改善できます。この方法は 100kΩ より大きい R<sub>FBT</sub> を使用する場合に特に有効です。R<sub>FBT</sub> の値が大きいと、FB ピンの寄生

容量との組み合わせにより、小さな信号極が形成されてループの安定性に影響を与える可能性があります。 $C_{FF}$  は、この影響を緩和するのに役立ちます。 $C_{FF}$  コンデンサを使用することで、何らかの利点が得られるかどうかを判断するには、より低い値を使用します。

『[内部的に補正される、フィードフォワード コンデンサを持つ DC-DC コンバータの過渡応答の最適化』アプリケーション レポート](#)は、フィードフォワード コンデンサの実験に役立ちます。

**表 7-2. 推奨部品値**

| V <sub>OUT</sub> (V) | L (μH) | C <sub>OUT</sub> (μF) | R2 (kΩ) | R3 (kΩ) | C6 (pF) |

|----------------------|--------|-----------------------|---------|---------|---------|

| 1.8                  | 5.6    | 66                    | 100     | 49.9    | 47      |

| 2.5                  | 8.2    | 44                    | 100     | 31.6    | 33      |

| 3.3                  | 10     | 44                    | 100     | 22.1    | 56      |

| 5                    | 15     | 44                    | 100     | 13.3    | 75      |

| 12                   | 22     | 44                    | 100     | 5.23    | 100     |

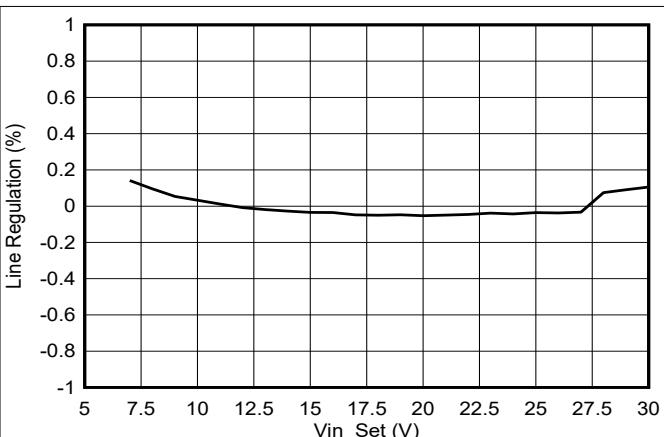

### 7.2.4 アプリケーション曲線

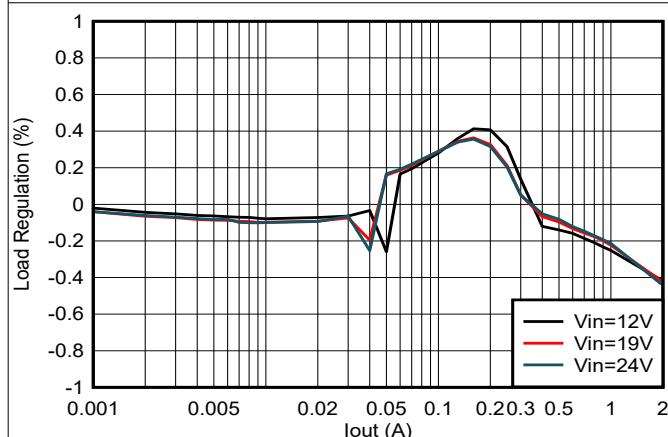

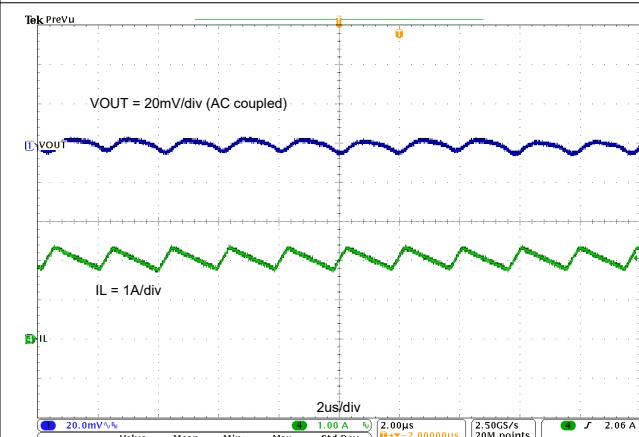

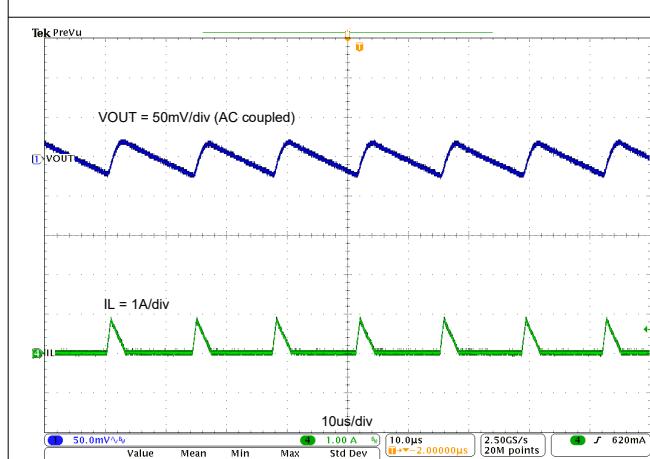

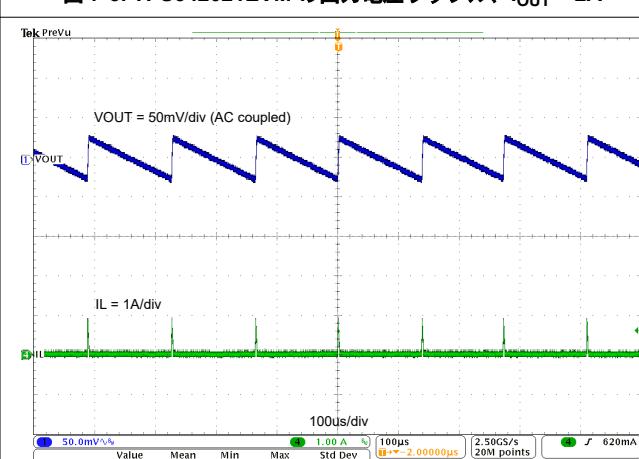

特に記述のない限り、以下のデータは  $V_{IN} = 24V$ 、 $V_{OUT} = 5V$ 、 $T_A = 25^\circ C$  でテストされています。

図 7-2. TPS542021EVM の効率

図 7-3. TPS542021EVM ライン レギュレーション、 $I_{OUT} = 2A$

図 7-4. TPS542021EVM ロード レギュレーション

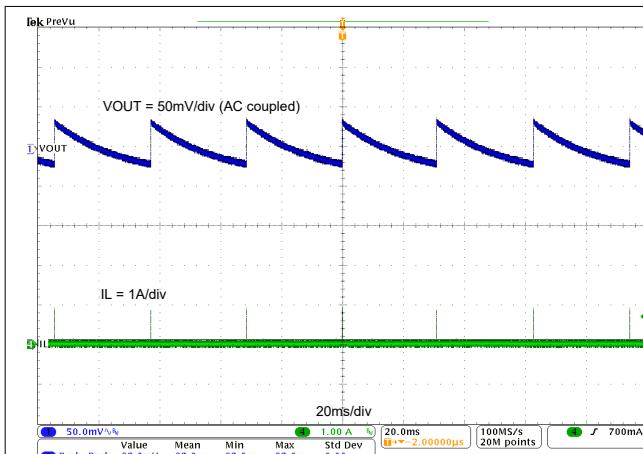

図 7-5. TPS542021EVM の出力電圧リップル、 $I_{OUT} = 2A$

図 7-6. TPS542021EVM の出力電圧リップル、 $I_{OUT} = 0.1A$

図 7-7. TPS542021EVM の出力電圧リップル、 $I_{OUT} = 0.01A$

### 7.2.4 アプリケーション曲線(続き)

特に記述のない限り、以下のデータは  $V_{IN} = 24V$ 、 $V_{OUT} = 5V$ 、 $T_A = 25^\circ C$  でテストされています。

図 7-8. TPS542021EVM の出力電圧リップル、 $I_{OUT} = 0A$

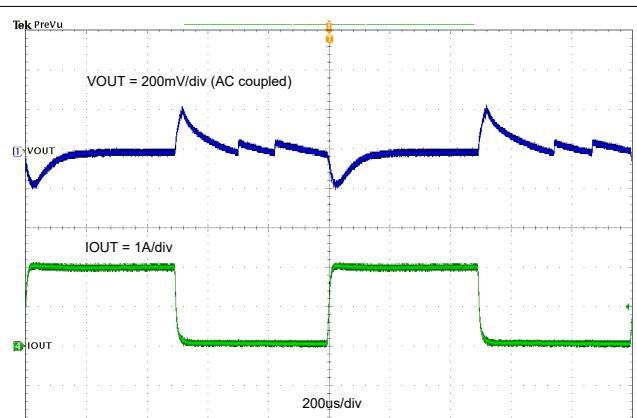

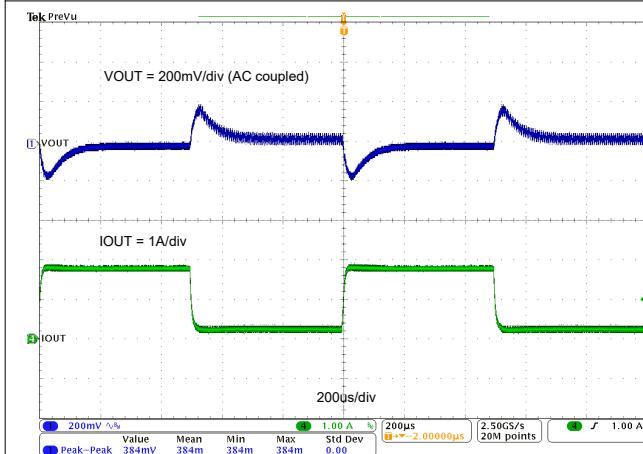

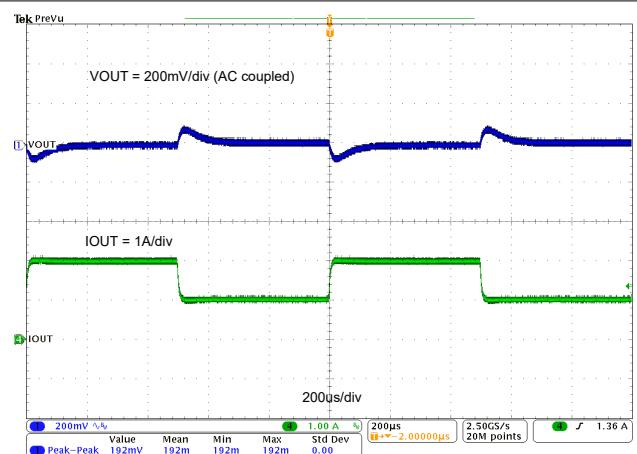

図 7-9. TPS542021EVM の負荷過渡応答、0A ~ 2A 間負荷ステップ

図 7-10. TPS542021EVM の負荷過渡応答、0.2A ~ 1.8A 間負荷ステップ

図 7-11. TPS542021EVM の負荷過渡応答、1A ~ 2A 間負荷ステップ

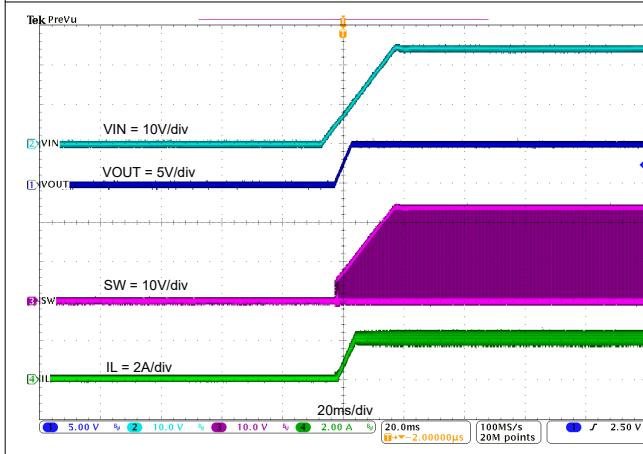

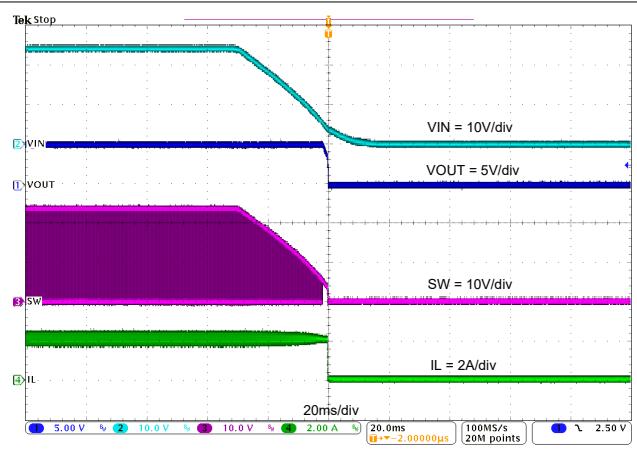

図 7-12.  $V_{IN}$  に対する TPS542021EVM のスタートアップ

図 7-13.  $V_{IN}$  に関する TPS542021EVM のシャットダウン

## 7.3 電源に関する推奨事項

デバイスは、4.5V~30V の入力電源電圧範囲で動作するように設計されています。この入力電源には適切なレギュレーションが行われる必要があります。入力電源がデバイスまたはコンバータから数インチ以上離れている場合は、セラミックバイパスコンデンサに加えて追加のバルクキャパシタンスが必要となることがあります。通常は、 $47\mu\text{F}$  の電解コンデンサを使用します。

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

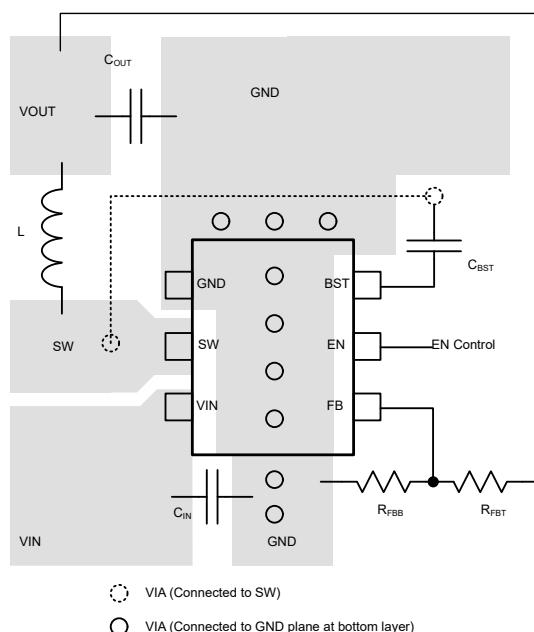

- VIN および GND のパターンは、パターンインピーダンス低減のためにできるだけ幅広くしてください。面積を広くすることには、放熱の観点からも利点があります。

- パターンインピーダンスを最小限に抑えるために、入力コンデンサおよび出力コンデンサを、デバイスにできるだけ近づけて配置します。

- 入力コンデンサおよび出力コンデンサに対して十分な数のビアを用意してください。

- 放射を最小限に抑えるために、SW のパターンは実用的な範囲でできるだけ短く、幅広くしてください。

- デバイスの下をスイッチング電流が流れないようにしてください。

- 個別の VOUT パスを上側帰還抵抗に接続します。

- フィードバックパスの GND ピンにはケルビン接続を使用します。

- 電圧帰還ループは、高電圧のスイッチングパターンから離して配置し、できればグランドシールドを使用してください。

- ノイズ結合を避けるため、VFB ノードのパターンは最小限にしてください。

- 出力コンデンサと GND ピンの間の GND パターンは、パターンインピーダンス低減のためにできるだけ幅広くしてください。

### 7.4.2 レイアウト例

図 7-14. 基板レイアウト

## 8 デバイスおよびドキュメントのサポート

### 8.1 デバイス サポート

#### 8.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 8.2 ドキュメントのサポート

#### 8.2.1 関連資料

関連資料については、以下を参照してください。

テキサス インスツルメンツ、『[フィードフォワード コンデンサ付き内部補正 DC/DC コンバータの過渡応答の最適化](#)』アプリケーション レポート

### 8.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 8.5 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 8.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.7 用語集

[テキサス・インスツルメンツ用語集](#)

この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision A (April 2025) to Revision B (December 2025)</b> | <b>Page</b> |

|---------------------------------------------------------------------------|-------------|

| • ドキュメントのステータスを「事前情報」から「量産データ」に変更.....                                    | 1           |

| • 電気特性の $I_{SD(VIN)}$ 標準値を $2\mu A$ から $3\mu A$ に変更.....                  | 5           |

| • 電気特性に $V_{FB}$ の $25^\circ C$ における温度変化を追加.....                          | 5           |

| • 「電気的特性」に $t_{ON\_MIN}$ の仕様を追加.....                                      | 5           |

| • 「電気的特性」に OVP スレッショルドを追加.....                                            | 5           |

| • 「電気的特性」に $f_{FSS}$ の値を追加.....                                           | 5           |

| • 「電気的特性」に $f_{SPREAD}$ の値を追加.....                                        | 5           |

| <b>Changes from Revision * (January 2025) to Revision A (April 2025)</b> | <b>Page</b> |

|--------------------------------------------------------------------------|-------------|

| • SOT-563 パッケージ情報を追加.....                                                | 1           |

| • SOT-563 の情報を追加.....                                                    | 1           |

| • SOT-563 パッケージ情報を追加.....                                                | 3           |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

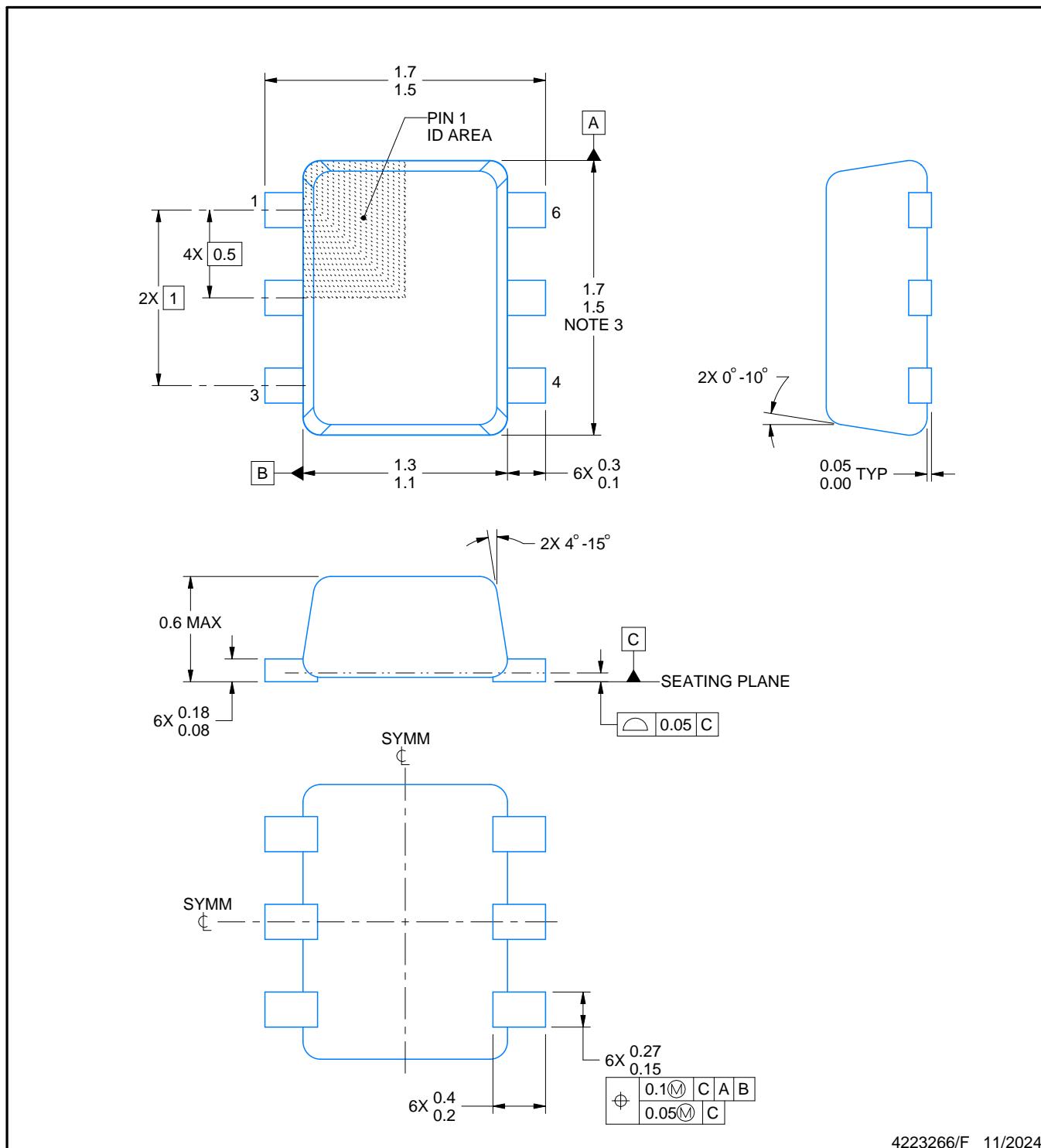

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins        | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| PTPS542021DDCR        | Active        | Preproduction        | SOT-23-THIN (DDC)   6 | 3000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 150   |                     |

| PTPS542021DDCR.A      | Active        | Preproduction        | SOT-23-THIN (DDC)   6 | 3000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 150   |                     |

| PTPS542021DRLR        | Active        | Preproduction        | SOT-5X3 (DRL)   6     | 4000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 150   |                     |

| PTPS542025DDCR        | Active        | Preproduction        | SOT-23-THIN (DDC)   6 | 3000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 150   |                     |

| PTPS542025DDCR.A      | Active        | Preproduction        | SOT-23-THIN (DDC)   6 | 3000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 150   |                     |

| TPS542025DDCR         | Active        | Production           | SOT-23-THIN (DDC)   6 | 3000   LARGE T&R      | -           | SN                                   | Level-1-260C-UNLIM                | -40 to 150   | 025C                |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative

and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

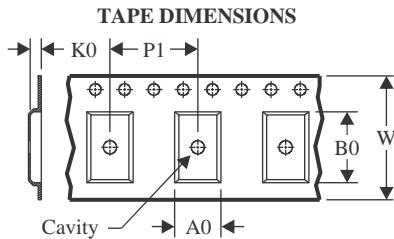

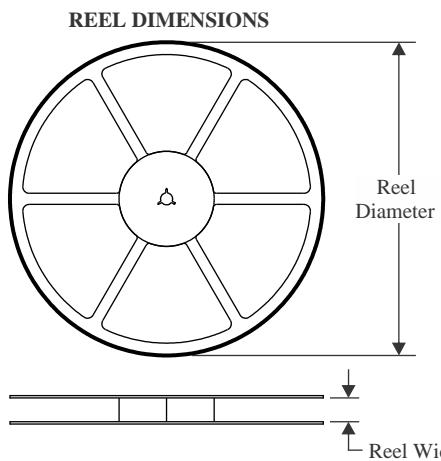

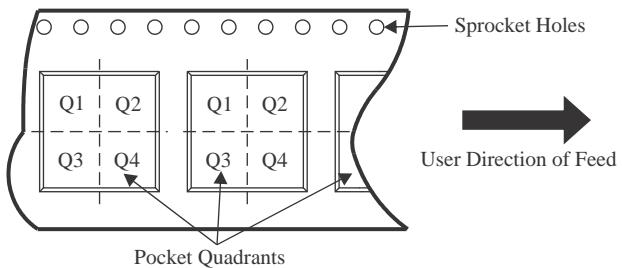

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS542025DDCR | SOT-23-THIN  | DDC             | 6    | 3000 | 180.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS542025DDCR | SOT-23-THIN  | DDC             | 6    | 3000 | 210.0       | 185.0      | 35.0        |

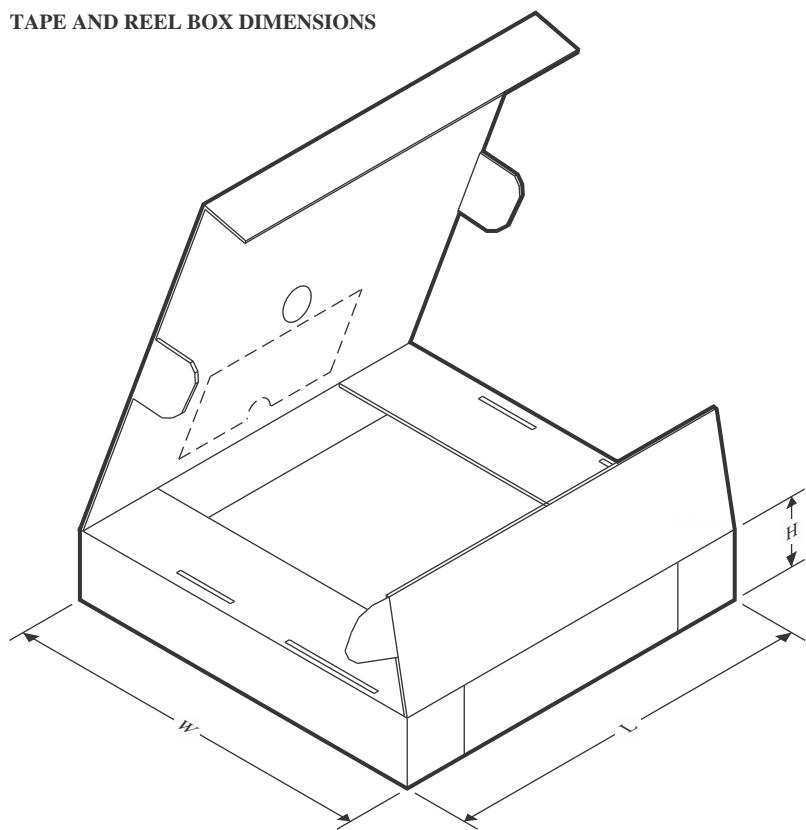

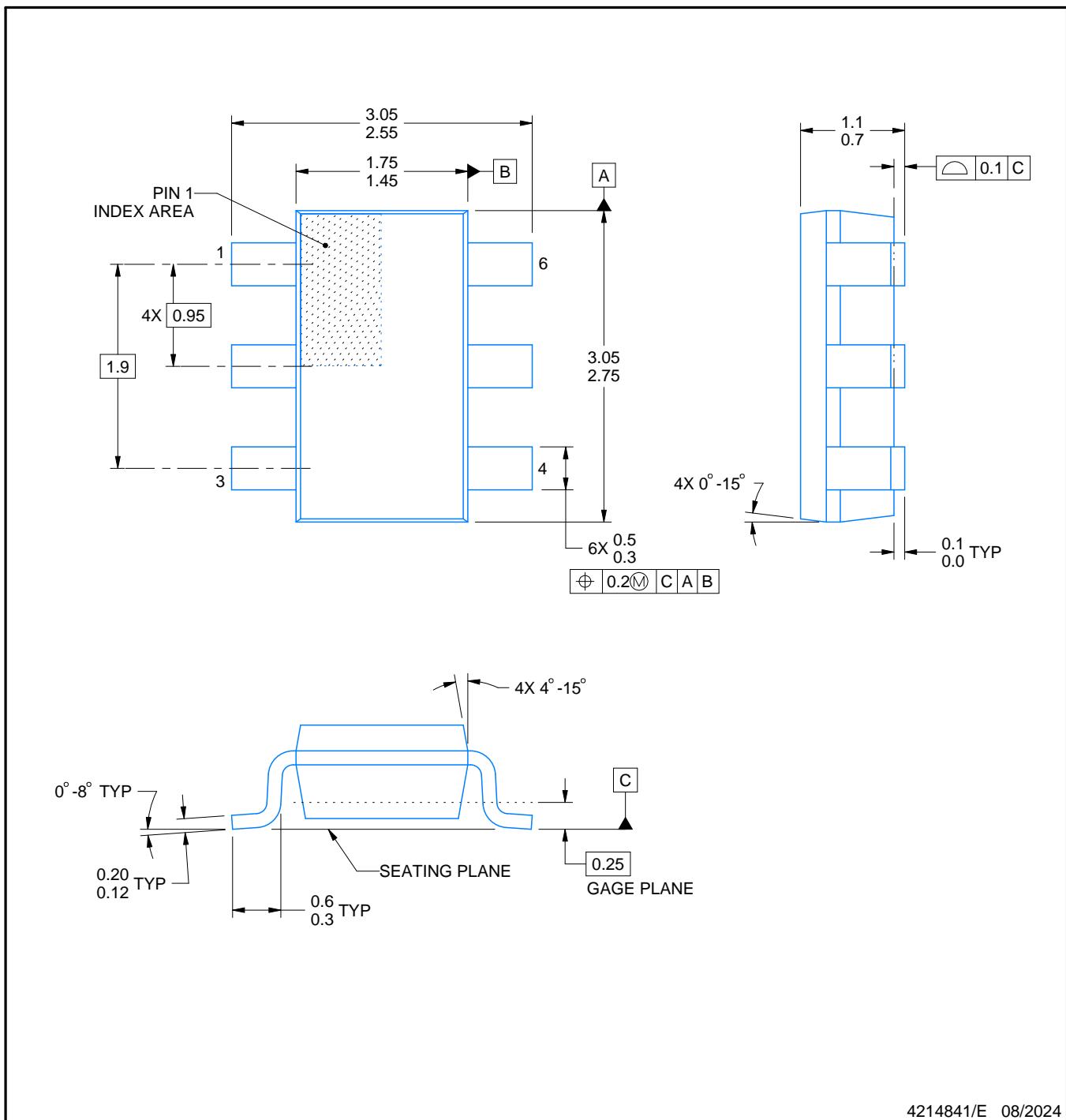

## **PACKAGE OUTLINE**

**DRL0006A**

## SOT - 0.6 mm max height

#### **PLASTIC SMALL OUTLINE**

4223266/F 11/2024

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. Reference JEDEC registration MO-293 Variation UAAD

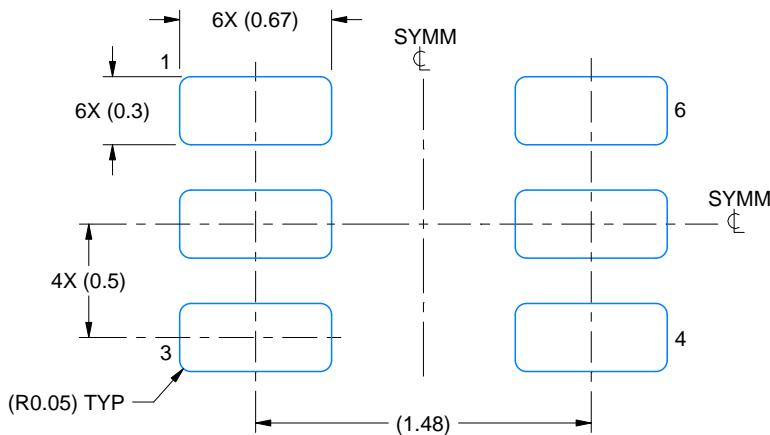

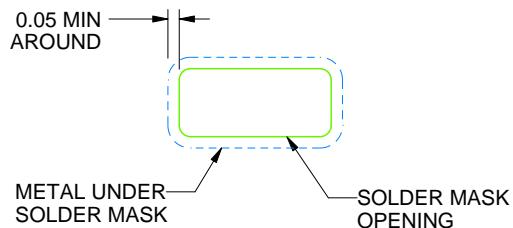

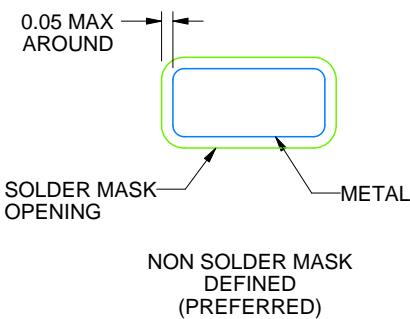

# EXAMPLE BOARD LAYOUT

DRL0006A

SOT - 0.6 mm max height

PLASTIC SMALL OUTLINE

LAND PATTERN EXAMPLE

SCALE:30X

SOLDERMASK DETAILS

4223266/F 11/2024

NOTES: (continued)

5. Publication IPC-7351 may have alternate designs.

6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

7. Land pattern design aligns to IPC-610, Bottom Termination Component (BTC) solder joint inspection criteria.

# EXAMPLE STENCIL DESIGN

DRL0006A

SOT - 0.6 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

BASED ON 0.1 mm THICK STENCIL

SCALE:30X

4223266/F 11/2024

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

# PACKAGE OUTLINE

## SOT-23 - 1.1 max height

DDC0006A

SMALL OUTLINE TRANSISTOR

4214841/E 08/2024

### NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-193.

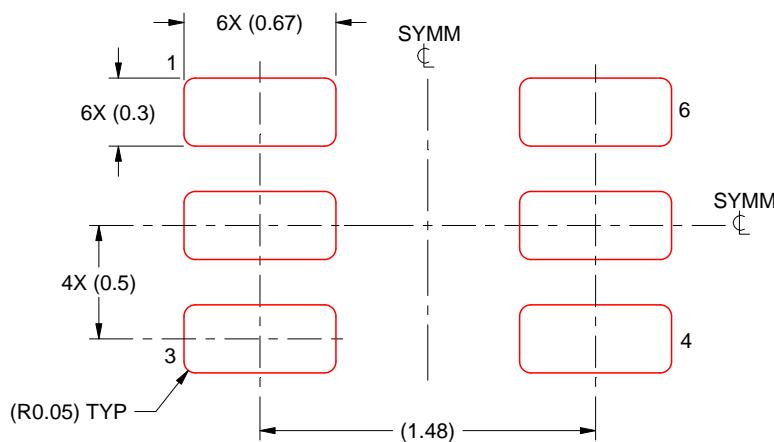

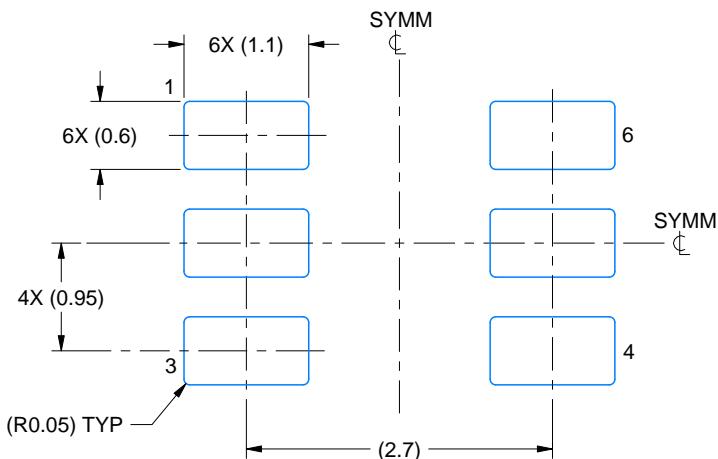

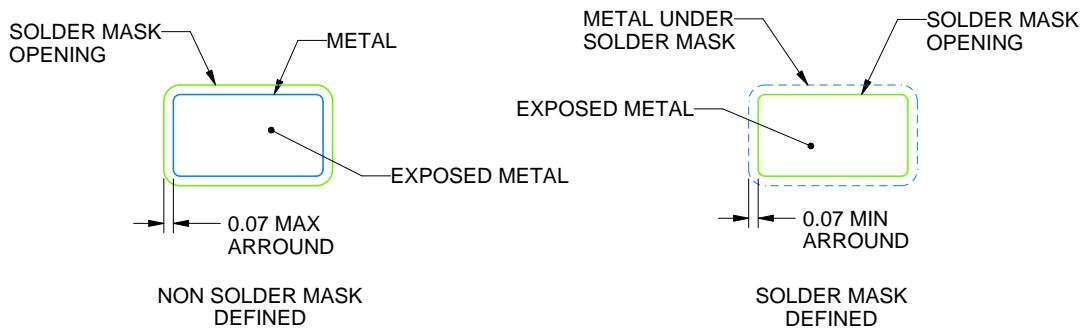

# EXAMPLE BOARD LAYOUT

DDC0006A

SOT-23 - 1.1 max height

SMALL OUTLINE TRANSISTOR

LAND PATTERN EXAMPLE

EXPLODED METAL SHOWN

SCALE:15X

SOLDERMASK DETAILS

4214841/E 08/2024

NOTES: (continued)

4. Publication IPC-7351 may have alternate designs.

5. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

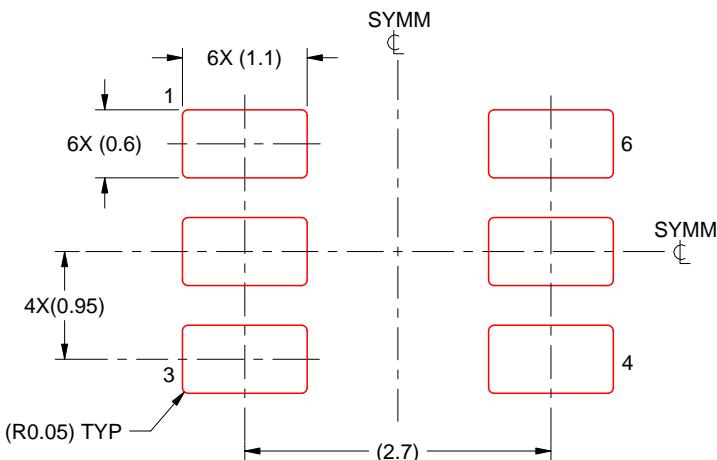

# EXAMPLE STENCIL DESIGN

DDC0006A

SOT-23 - 1.1 max height

SMALL OUTLINE TRANSISTOR

SOLDER PASTE EXAMPLE

BASED ON 0.125 THICK STENCIL

SCALE:15X

4214841/E 08/2024

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

7. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月