SBAU392A July 2022 – January 2023 AFE7950 , TRF1208

- TRF1208-AFE7950-EVM Evaluation Module User's Guide

- Trademarks

- 1EVM Overview

- 2Hardware Setup (TSW14J56 Used as an Example)

- 3Latte Overview

- 4TRF1208-AFE7950-EVM Automatic Configuration

- 5Status Check and Troubleshooting Guidelines

- 6TRF1208-AFE7950-EVM Manual Configuration

- 7Setup the TSW14J5x With the HSDC Pro

- 8Revision History

7.3 ADC Data Capture

The steps to capture the ADC output are as follows:

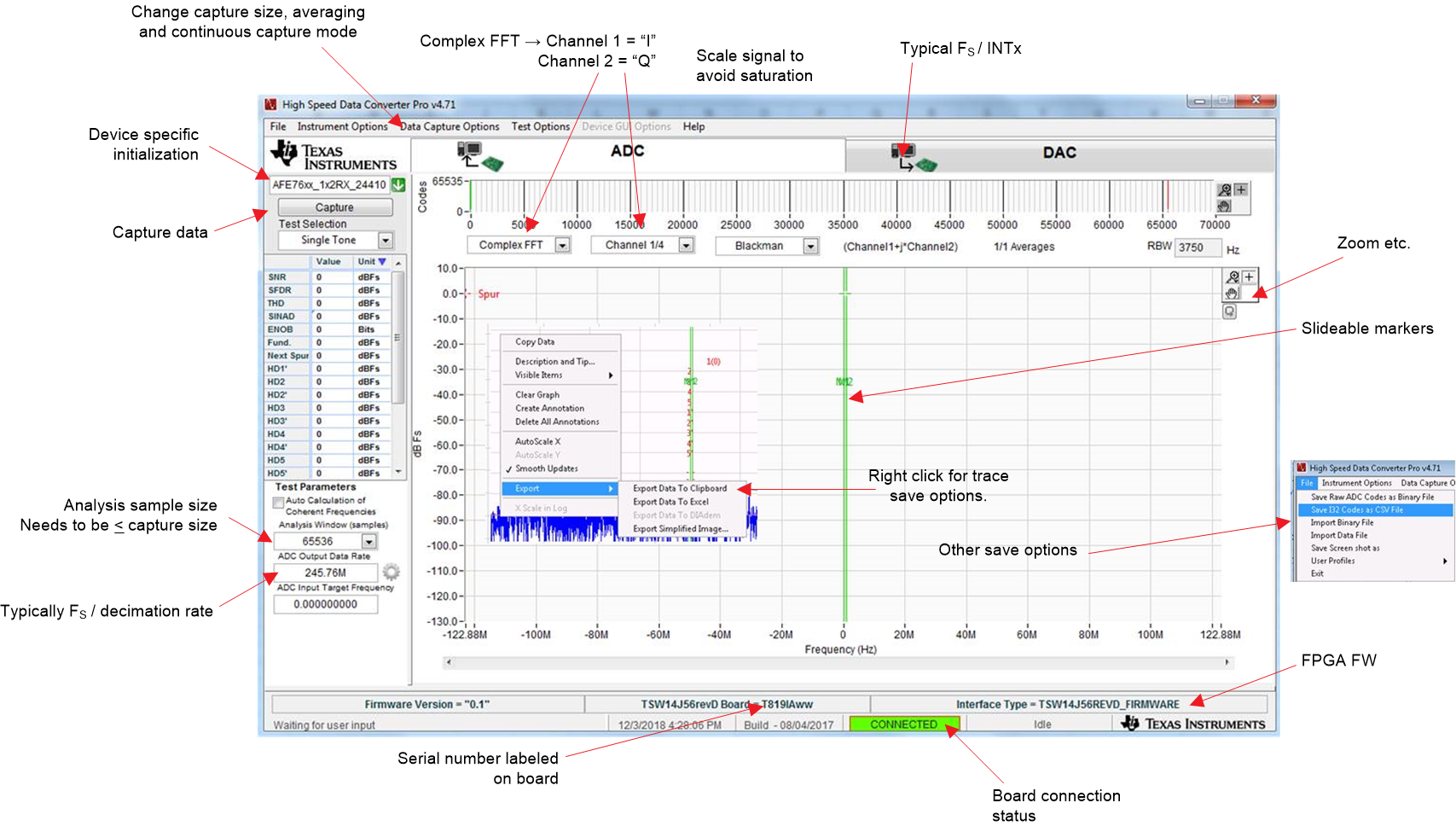

- Click on the HSDC Pro ADC tab. Figure 7-5 shows a brief description of the ADC tab.

Figure 7-5 HSDC Pro ADC Tab Overview

Figure 7-5 HSDC Pro ADC Tab Overview - Select AFE79xx_2x2RX_24410 as the device.

- Go to Data Capture Options in the menu bar and choose the Capture option. Set #samples (per channel) to 16384. Click the OK button.

- Select 16384 in the Analysis window located in the lower left section of the GUI.

- Enter 245.76 M for ADC output data rate.

- Click the Capture button.

The capture size is set to a lower value (such as 16K) because of the limited BRAM memory available in the FPGA.