SLAT161 June 2022 HD3SS3411 , TMUXHS4412

2.2.1 Common Reference Clock

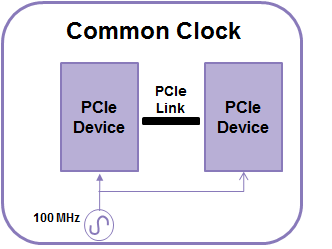

Figure 2-2 shows the common refclk architecture. In the common refclk architecture, the same reference clock is distributed to both transmit (Tx) and receive (Rx) devices, so it does not introduce any difference in clock between the PCIe components. An advantage of this clocking architecture is that it supports spread spectrum clocking (SSC), which can be very useful in reducing EMI.

Figure 2-2 Common Clock

Architecture

Figure 2-2 Common Clock

Architecture